NAND Flash中文版资料

NAND Flash简介

NAND FLASH 的特殊性1.存在壞塊。

由於NAND生產工藝的原因,出廠晶片中會隨機出現壞塊。

壞塊在出廠時已經被初始化,並在特殊區域中標記為不可用,在使用過程中如果出現壞塊,也需要進行標記。

2.易出現位反轉。

NAND FLASH更易出現位反轉的現象,如果位反轉出現在關鍵檔上,會導致系統掛機。

所以在使用NAND FLASH的同時,建議使用ECC/EDC演算法確保可靠性。

3.存在Spare區。

正因為NAND FLASH有著上面的兩項特殊的地方,Spare區就扮演作存放壞塊標誌,ECC值以及晶片資訊和檔資訊的作用。

4.多維的空間結構。

NAND FLASH一般由block,page,sector等結構組成。

所以在有的檔系統中就衍生出各種分區資訊和磁區資訊等。

NAND FLASH 燒錄的複雜性1.處理壞塊。

由於NAND存在壞塊,導致位址空間不是連續的。

所以正確的處理壞塊是保證NAND FLASH燒錄後能夠正常運行的關鍵。

從大的方面來說,處理壞塊常用的最有效的主要為兩種方法:a.跳過;b.替代。

也有部分客戶為了使用方便,並沒有把壞塊處理的概念引入,直接(在壞塊上寫過,這種方法雖然簡單,但容易產生很多不穩定的因素。

目前我們公司在出廠的時候為每一種NAND FLASH配置標準的壞塊處理方式有Skip(跳過),ReservedSamsung的保留替代方案)和直接在壞塊上寫過(一般情況不建議客戶使用)2.計算ECC。

ECC/EDC演算法具有查錯,糾錯的功能,並且在NAND FLASH使用的大多數環境,需要帶有ECC演算法的。

目前廣泛使用的為Samsung的漢明碼(Hamming code),分為512Byte&256W兩種。

還有功能更為強大的4-bit ECC 和Computer ECC。

由於ECC演算法比較多,每個演算法個體又具有比較強的可變性(位元組織,分段計算等),而且在Spare區存放的位置也不能統一,所以無法做成統一的演算法。

nandflash原理

nandflash原理

NAND Flash的工作原理是将电压变化的门极电容器上的电流回到电源中。

当存储器被分为多个分区时,通过门极信号来访问和操作存储空间。

此时,如果将电流沿着多个存储单元传输,就可以建立一个连接,用来将存储单元中的数据传输到计算机中,从而实现数据存储与读取功能。

NAND Flash的物理组成包括存储单元、位线、字线和块等。

每个存储单元以bit的方式保存在存储单元中,通常一个单元中只能存储一个bit。

这些存储单元以8个或者16个为单位,连成bit line,形成所谓的byte(x8)/word(x16),这就是NAND Device 的位宽。

存储结构方面,NAND Flash由块构成,块的基本单元是页。

通常来说,每一个块由多个页组成。

NAND Flash每一个页内包含Data area(数据存储区)和Spare area(备用区)。

每一个页的大小为Data area+Spare area。

这个过程造成了多余的写入和擦除,这就是所谓的写放大。

在存储单元的构造方面,NAND Flash的存储单元为三端器件,与场效应管有相同的名称:源极、漏极和栅极。

栅极与硅衬底之间有二氧化硅绝缘层,用来保护浮置栅极中的电荷不会泄漏。

与场效应管一样,闪存也是一种电压控制型器件。

以上内容仅供参考,如有需要可以查阅相关文献资料或咨询专业人士。

Nand Flash 原理简介

Nand Flash 原理简介NAND flash是东芝公司开发的一种非易失闪存技术,具较高的单元密度,可以达到高存储密度,写入和擦除速度较快。

NAND flash的单元尺寸几乎是NOR器件的一半,可以在给定的模具尺寸内提供更高的容量,具有很快的写入和擦除速度,主要功能是存储资料,目前主要用在数码相机闪存卡和MP3播放机中。

NOR和NAND是现在市场上两种主要的非易失闪存技术。

Intel于1988年首先开发出NOR flash技术,彻底改变了原先由EPROM和EEPROM一统天下的局面。

紧接着,1989年,东芝公司发表了NAND flash 结构,强调降低每比特的成本,更高的性能,并且象磁盘一样可以通过接口轻松升级。

但是经过了十多年之后,仍然有相当多的硬件工程师分不清NOR和NAND闪存。

相“flash存储器”经常可以与相“NOR存储器”互换使用。

许多业内人士也搞不清楚NAND闪存技术相对于NOR技术的优越之处,因为大多数情况下闪存只是用来存储少量的代码,这时NOR闪存更适合一些。

而NAND则是高数据存储密度的理想解决方案。

NOR的特点是芯片内执行(XIP, eXecute In Place),这样应用程序可以直接在flash闪存内运行,不必再把代码读到系统RAM中。

NOR的传输效率很高,在1~4MB的小容量时具有很高的成本效益,但是很低的写入和擦除速度大大影响了它的性能。

NAND结构能提供极高的单元密度,可以达到高存储密度,并且写入和擦除的速度也很快。

应用NAND的困难在于flash的管理和需要特殊的系统接口。

性能比较flash闪存是非易失存储器,可以对称为块的存储器单元块进行擦写和再编程。

任何flash器件的写入操作只能在空或已擦除的单元内进行,所以大多数情况下,在进行写入操作之前必须先执行擦除。

NAND器件执行擦除操作是十分简单的,而NOR则要求在进行擦除前先要将目标块内所有的位都写为0。

nand_flash读写工作原理_概述说明

nand flash读写工作原理概述说明1. 引言1.1 概述NAND Flash是一种非常常见和重要的存储设备,被广泛应用于各种电子产品中。

它的独特设计使得它成为一种高性能、低功耗、擦写可靠且具有较大容量的存储器解决方案。

由于其许多优点,NAND Flash在移动设备、个人电脑、服务器以及其他许多领域都有着广泛的应用。

1.2 文章结构本文将详细介绍NAND Flash的读写工作原理,并探讨其在存储领域中的优势与应用场景。

首先,我们将简要介绍NAND Flash的基本概念和特点,包括其结构和组成部分。

然后,我们将重点讲解NAND Flash进行读操作和写操作时所涉及的工作原理和步骤。

通过对这些原理的详细阐述,读者将能够全面了解NAND Flash如何实现数据的读取和写入。

除此之外,我们还将探讨NAND Flash相对于其他存储设备的优势,并介绍几个典型应用场景。

这些优势包括快速读写速度、低功耗、体积小且轻便、强大的耐久性以及较大的存储容量。

在应用场景方面,我们将重点介绍NAND Flash 在移动设备领域、物联网和服务器等各个行业中的广泛应用。

最后,我们将进行本文的小结,并对NAND Flash未来的发展进行展望。

通过全面了解NAND Flash的工作原理和优势,读者将能够更好地理解其在现代科技领域中的重要性,并对其未来发展趋势有一个清晰的认识。

1.3 目的本文的目的是通过对NAND Flash读写工作原理进行详细说明,使读者能够全面了解NAND Flash是如何实现数据读写操作的。

此外,我们还旨在向读者展示NAND Flash在存储领域中所具有的优势和广泛应用场景,使其意识到这一存储设备在现代科技产业中所扮演的重要角色。

希望通过本文,读者能够加深对NAND Flash技术的理解,并为相关领域或产品的研发与设计提供参考依据。

2. NAND Flash读写工作原理:2.1 NAND Flash简介:NAND Flash是一种非易失性存储器,采用了电子闪存技术。

s3c2440中文手册第6章-nandflash

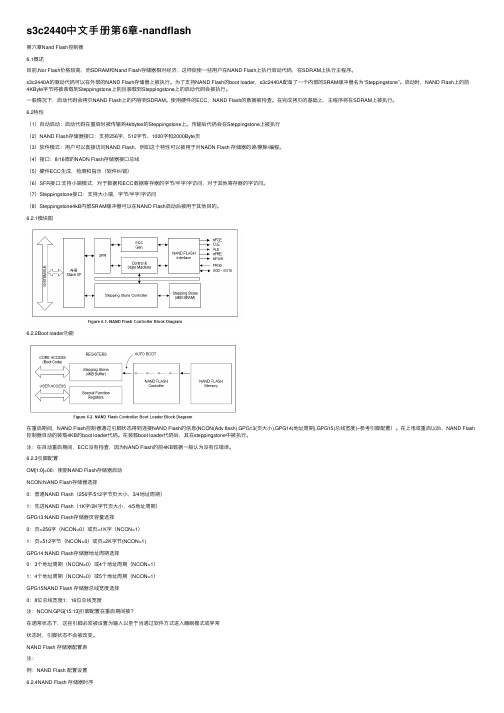

s3c2440中⽂⼿册第6章-nandflash第六章Nand Flash控制器6.1概述⽬前,Nor Flash价格较⾼,⽽SDRAM和Nand Flash存储器相对经济,这样促使⼀些⽤户在NAND Flash上执⾏启动代码,在SDRAM上执⾏主程序。

s3c2440A的驱动代码可以在外部的NAND Flash存储器上被执⾏。

为了⽀持NAND Flash的boot loader,s3c2440A配备了⼀个内部的SRAM缓冲器名为“Steppingstone”。

启动时,NAND Flash上的前4KByte字节将被装载到Steppingstone上别且装载到Steppingstone上的启动代码会被执⾏。

⼀般情况下,启动代码会拷贝NAND Flash上的内容到SDRAM。

使⽤硬件的ECC,NAND Flash的数据被检查。

在完成拷贝的基础上,主程序将在SDRAM上被执⾏。

6.2特性(1)⾃动启动:启动代码在重启时被传输到4kbytes的Steppingstone上。

传输后代码会在Steppingstone上被执⾏(2)NAND Flash存储器接⼝:⽀持256字、512字节、1000字和2000Byte页(3)软件模式:⽤户可以直接访问NAND Flash,例如这个特性可以被⽤于对NADN Flash 存储器的读/擦除/编程。

(4)接⼝:8/16微的NADN Flash存储器接⼝总线(5)硬件ECC⽣成,检测和指⽰(软件纠错)(6)SFR接⼝:⽀持⼩端模式,对于数据和ECC数据寄存器的字节/半字/字访问,对于其他寄存器的字访问。

(7)Steppingstone接⼝:⽀持⼤⼩端,字节/半字/字访问(8)Steppingstone4kB内部SRAM缓冲器可以在NAND Flash启动后被⽤于其他⽬的。

6.2.1模块图6.2.2Boot loader功能在重启期间,NAND Flash控制器通过引脚状态得到连接NAND Flash的信息(NCON(Adv flash),GPG13(页⼤⼩),GPG14(地址周期),GPG15(总线宽度)–参考引脚配置)。

nand_flash -简明自学资料-

编写原因:

各种 nand flash 英文 datasheets 上的内容虽详尽但繁杂,有些业内常识性的 东西没交代清楚,给初学者造成困扰; 不同的 datasheets 都有一些共通的要点(基本架构、指令和符号等) ,了解 这些后再看 datasheet 的操作命令和时序图部分会省力很多。

3

注:1)R/B#信号以及 toggle 模式下的对应读操作的 DQS 信号是外部从 flash 读出的,而

其余引脚信号(包括 toggle 模式下的对应写操作的 DQS 信号)都是由 flash device 以 外的模块产生、输入进而控制其状态的,即分别对应开篇“功能结构抽象图”里的状 态信号和控制信号。 2)以上带“#”的引脚,表示信号低电平时对应功能或状态有效,有的 datasheet 则 用顶部一横杠标示, 如:

2

号,剩下 个 Byte 的高位用于存储 block 编号,如是多层或多芯片等的,再在其中插入 8 相应编号即可,列地址以外的部分称为 Row Address(行地址,即页内偏移地址) 。

k

二 基本操作、时序图部分 *通用引脚符号声明

(1)CE#:芯片使能,表示 flash chip 是否被系统选中为当前操作芯片,低电平表示选中

1、Read—读

(1)Page Read 功能:用于将目标 page 中从指定列地址到页末尾地址的内容顺序读出 指令:00h + Column&Row Addresses+ 30h 过程:先将选定的 page 所有内容拷贝到 page register,再从 page register 复制到 cache, 最后将 cache 中 page 的从 column address 起到页尾的部分依次读出 (2)Cache Read 功能:用于将一个 block 中的多个 page 顺序读出(除首页可输出部分内容外,其它页都 是整页被 I / O 读出) 指令:00h + Column&Row Addresses(首页)+ 30h + 31h + …… + 31h + 3Fh 过程:1)将首页的所有内容复制到 register,完成时接到 31h(Cache Read 指令) ; 2)把 page register 里的内容复制到 cache; 3) 完毕时 page register 可用, 立即开始将下一页拷贝到 page register, 同时, cache 里的内容可被 I / O 读出; 4) 当 page register 的数据已加载好, 且 cache 被读完时, 若又收到 31h, 则返回 2) , 否则接收的是准结束指令 3Fh,转向 5) ; 5)将 page register 里最后一页的内容复制到 cache,然后被 I / O 读出,操作结束。 (3)Random Data Output 功能:当用 Read 指令把 page 内容读到 cache 后,从中读取指定列地址以后的内容 指令:… 05h + Column Addresses + E0h

Nandflash_K9F1208U0B中文学习资料

Nandflash中文资料1. 引脚描述I/O0 ~ I/O7-----data inputs/outputs通过这8个I/O引脚,可以输入命令,地址和数据,也可以在读操作时输出数据。

CLE-----command latch enableCLE输入控制了发送到命令寄存器的命令。

CLE为高电平时激活,在nWE的上升沿,命令通过I/O端口被锁存到命令寄存器中,结合datasheet的相关时序图来理解更为深刻ALE-----address latch enableALE输入控制了地址发送到内部地址寄存器中,在nWE的上升沿和ALE为高电平时,地址被锁存到地址寄存器中。

nCE-----chip enablenCE是设备选择控制引脚。

nWE-----write enable写使能,在nWE的上升沿,命令,地址和数据被锁存。

nWP -----write protect写保护,当此引脚为低电平激活,也即内部高压发生器复位。

R/B-----ready/busy output就绪/忙输出引脚,通过这个引脚可以知道设备操作的状态。

低电平时,表示编程或擦除或随机读操作在进行,并且根据完成情况来返回高状态。

2. K9F1208U0B的存储结构和存储特点2.1 K9F1208U0B的存储结构一片K9F1208U0B总共有4096blocks,每个block包含32pages,每个page包含528bytes,关系如下:1 device = 4096 blocks1 block = 32 pages1 page = 512 Bytes data field + 16 bytes spare field所以一片K9F1208U0B的容量为4096*32*528=66MB,但是事实上每个page上的最后16bytes 是用于存储校验码用的,并不能存放实际的数据,所以实际上我们可以操作的芯片容量为4096*32*512=64MB由上图可知,1个page总共由528 bytes组成,这528 bytes安顺序由上到下以列为单位进行排列(1列代表一个byte,第0行为第0 byte,第1行为第1 byte)。

nandflash原理

nandflash原理NAND Flash是一种非易失性存储器,被广泛应用于各种电子设备和计算机系统中。

NAND Flash的工作原理类似于EEPROM(电可擦写可编程只读存储器),但其编程和清除速度更快,存储密度更高。

NAND Flash由许多存储单元(也称为“页”)组成,每个存储单元包含一个电晕栅结构和一个控制门。

每个存储单元可以存储一个或多个比特的数据。

NAND Flash使用了一种称为“悬浮栅”(Floating Gate)的技术,通过控制栅电流和源/漏电流的关系来存储和读取数据。

NAND Flash的编程操作是通过在栅电流中施加一个较高的电压来实现的。

这个电压会引起电晕栅结构的氧化物内部的电子从源/漏区域流入或流出。

这些额外或缺少的电子会改变栅电极中的电荷量,从而改变存储单元的导通特性。

以这种方式编程的NAND Flash将在页中存储逻辑"0"或"1"。

NAND Flash的擦除操作是通过应用一个更高的电压来实现的。

这个电压将把栅电荷完全释放,使存储单元返回初始状态。

一个存储单元可以被擦除,从而在其中存储的数据被清除,并准备好下一次编程。

NAND Flash存储单元之间相互无关,这使得擦除整个页面或多个页面变得容易。

因此,NAND Flash是一个按块擦除的设备,块的大小通常是64 KB或128 KB。

需要注意的是,每次擦除操作都会减少存储单元的寿命。

为了提高存储密度,NAND Flash还使用了一个称为“多层单元(MLC)”的技术。

MLC意味着在每个存储单元中存储了多个比特的数据。

通过在栅电荷中引入更多的电荷水平,可以实现多个数据位的存储。

然而,MLC技术的使用会导致更大的读取、编程和擦除误差。

NAND Flash的工作原理和EEPROM相比有许多优点。

首先,NANDFlash的存储密度更高,因为NAND Flash使用了一种二进制设计,而EEPROM使用了一种十进制设计。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

NAND Flash 存储器和使用ELNEC编程器烧录NAND Flash技术应用文档Summer 翻译整理深圳市浦洛电子科技有限公司August 2006目录一. 简介 ----------------------------------------------------------------------------------- 1 二. NAND Flash与NOR Flash的区别 -------------------------------------------- 1 三. NAND Flash存储器结构描叙 --------------------------------------------------- 4 四. 备用单元结构描叙 ---------------------------------------------------------------- 6 五. Skip Block method(跳过坏块方式) ------------------------------------------ 8 六. Reserved Block Area method(保留块区域方式)----------------------------- 9 七. Error Checking and Correction(错误检测和纠正)-------------------------- 10 八. 文件系统 ------------------------------------------------------------------------------10 九. 使用ELNEC系列编程器烧录NAND Flash -------------------------------- 10 十. Invalid Block Management drop-down menu -------------------------------- 12 十一. User Area Settings3 -------------------------------------------------------- 13 十二. Solid Area Settings --------------------------------------------------------- 15 十三. Quick Program Check-box ---------------------------------------------- 16 十四. Reserved Block Area Options --------------------------------------------17 十五. Spare Area Usage drop-down menu ------------------------------------18简介NAND Flash 结构最早是在1989年由日本东芝公司引入。

如今, NAND Flash和NOR Flash已经占据了Flash市场的支配地位。

NAND Flash是一种高密度, 低功耗, 低成本, 而且可升级的器件, 它是多媒体产品导入市场的理想选择。

先进的在系统内设计也使得为降低成本, 在传统的设计应用上采用NAND Flash来替代NOR Flash成为可能。

NAND Flash与NOR Flash的区别下表是NAND 与 NOR的主要对比表。

它指出了为什么NAND存储器是高容量数据存储的完美解决方案, 尽管NOR存储器也可被用来做数据存储和执行。

从物理结构上来说, 因为它不一定要下拉整个bit-line, 所以NAND Flash 结构可以使用更小的晶体管。

一条NAND bit line就是一些连续的晶体管, 每一个晶体管只能流过少于总量的电流。

下图介绍了NAND 和 NOR 结构内晶体管是怎样被连接在一起的, 以及他们的单元大小有什么不同。

得益于NAND Flash这种更有效率的结构, 使得它每一单元的大小几乎是NOR单元的一半。

这也使得NAND Flash结构在给定的硬模内提供了更高的密度, 更高的容量, 同样也使得它的生产制程更为简单。

高容量存储应用中, NAND结构相对于NOR结构来说更为节省成本。

正如上面说介绍的, NAND Flash存储器是大容量数据存储的完美解决方案。

(典型应用: MP3播放器, 数码相机)上面所描叙的工艺是众所周知的单极单元(SLC)工艺, 通过电压的“H”或“L”,一个存储器单元保存1bit的信息。

有时候多极单元(SLC)工艺也会被用到。

在这样的应用中, 每一个存储单元能保存2bit或更多bit的信息,通过存储更多位。

相对于基于SLC结构的存储器, MLC存储器传输的速度大大降低了,同时它也产生了更高的功耗。

但是,其实这两种工艺都采用相同的I/O接口和指令。

在NOR Flash中, 所有的存储区域都保证是完好的, 同时也拥有相同的耐久性。

在硬模中专门制成了一个相当容量的扩展存储单元 — 他们被用来修补存储阵列中那些坏的部分,这也是为了保证生产出来的产品全部拥有完好的存储区域。

为了增加产量和降低生产成本, NAND Flash 器件中存在一些随机bad block 。

为了防止数据存储到这些坏的单元中, bad block 在IC烧录前必须先识别。

在一些出版物中, 有人称bad block 为“bad block”, 也有人称bad block 为“invalid block”。

其实他们拥有相同的含义, 指相同的东西。

从实际的应用上来说, NOR Flash与NAND Flash主要的区别在于接口。

NOR Flash 拥有完整的存取-映射访问接口, 它拥有专门的地址线和数据线, 类似与EPROM。

然而在NAND Flash中没有专门的地址线。

它发送指令,地址和数据都通过8/16位宽的总线(I/O接口)到内部的寄存器。

NAND Flash存储器结构描叙NAND Flash存储器由block (块) 构成, block的基本单元是page (页)。

通常来说, 每一个block由16, 32或64个page组成。

大多数的NAND Flash器件每一个page (页)内包含512个字节(或称为256个字)的Data area(数据存储区域)。

每一个page内包含有一个扩展的16字节的 Spare area(备用区域)。

所以每一个page的大小为512+16=528字节。

我们称这样的page为small page。

那些大容量的(1Gbig或更多)的NAND Flash, 它每page的容量就更大, 每page内Dataarea(数据存储区域)的大小为2048字节, Spare area(备用区域)大小为64字节。

NAND Flash的读取和烧录以页为基础, 而NOR却是以字节或字为基础 — 数据I/O寄存器匹配页的大小。

NAND Flash的擦除操作是基于block (块)的。

在NAND Flash上有三种基本的操作:读取一个页, 烧录一个页和擦除一个块。

在一个页的读取操作中, 该页内528字节的数据首先被传输到数据寄存器中, 然后再输出。

在一个页的烧录中, 该页内528字节的数据首先被写进数据寄存器, 然后再存储到存储阵列中。

在一个块的擦除操作中, 一组连续的页在单独操作下被擦除。

通常来说, 器件还提供有更多的扩张功能, 它们是:z厂商ID读取z器件操作状态读取z复位命令z不考虑CEz高速缓冲寄存器操作z OTP区域z自动读取第0页z块加锁/解锁备用单元结构描叙NAND Flash厂商在生产制程中使用Spare area(备用区域)来标识bad block, 所以这些器件被运送到客户手中时已经被标识。

从功能上来说, Spare area(备用区域)内所有的字节都可以像Data area(数据存储区域)内的字节一样被用户用来存储数据。

关于备用字节的使用, 我们推荐使用三星的标准。

Bad block (Invalid block)的管理自从NAND结构被设计用来作为低成本的多媒体存储器, 它的标准规范中是允许存在bad block 的。

只要bad block 的容量小于总容量的2% 那就是允许的。

一个block中如果有坏的存储区域, 那它就会被标识成bad block 。

bad block 列表可以存储在一个芯片中的一个好的block上, 也可以存储在同一系统的另外一颗芯片上。

bad block 列表是被要求的, 这是由于NAND Flash只能执行有限的读和擦除次数。

由于所有的Flash存储器最终都会被磨损而且不能再使用, 这个列表需要被用来跟踪记录那些在使用中发现的bad block 。

允许bad block 的存在有利于提高芯片的产量,同时也降低了成本。

因为每个block是独立的, 而且是被bit lines隔离的, 所以bad block 的存在并不会影响那些其他block的正常工作。

Bad block 的一般分为两种: 生产过程中产生的; 使用过程中产生的。

当block被发现是bad block , 一般是在该块的前两个page (页)的第517字节处用非FF来标识。

一个通用的bad block map building 算法流程如下所示:使用过程中产生的bad block 是没有被工厂标识的, 这些块是在客户处产生的。

因为NAND Flash有一个使用寿命而且它最终会磨损。

每一个块是独立的单元, 每一个块都能被擦除和烧录并且不受其它块寿命的影响。

一个好的块一般能被烧录100000到1000000次。

如果一个块在擦除一个块或烧录一个页时操作失败, 那么此块将被标识成bad block 并且以后不再访问。

如果你对bad block 进行擦除, 那么非“FFh”字节也会被擦除。

如果发生了这样的事情, 在没有对块进行测试的特定条件下, 对那些bad block 进行重新标识是非常困难。

所以如果存储bad block 列表的bad block table丢失, 重新发现并标识那些bad block 是相当困难的。

因此, 在擦除bad block 之前推荐先收集正确的bad block 信息, 在器件擦除后, 那些信息又会被重新标识上去。

在嵌入式系统中对bad block 进行管理必须要求有特殊的软件层。

因此对NAND Flash进行烧录, 必须采用正确的方式进行bad block 的管理, 该方法取决于嵌入式系统中程序的管理方式。

对bad block 的管理有很多种方式, 没有那一种方式被定义成标准方式。