杭电计组实验

杭电计算机组成原理全加器设计实验-参考模板

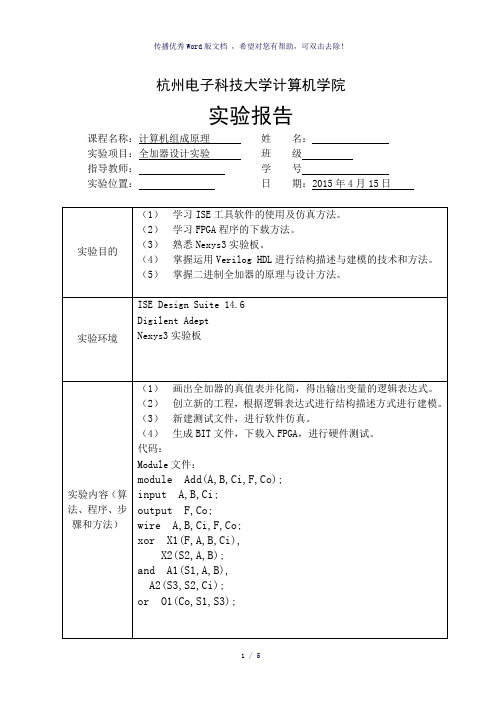

实验报告

课程名称:计算机组成原理

实验项目:全加器设计实验

指导教师:

实验位置:

姓 名:

班 级

学 号

日 期:2015年4月15日

实验目的

(1)学习ISE工具软件的使用及仿真方法。

(2)学习FPGA程序的下载方法。

(3)熟悉Nexys3实验板。

(4)掌握运用Verilog HDL进行结构描述与建模的技术和方法。

指导教师

评议

成绩评定: 指导教师签名:

---精心整理,希望对您有所帮助

endmodule

(接上)

实验内容(算法、程序、步骤和方法)

数据记录和计算

软件方程结果

硬件测试结果:

A

B

Ci

F

Co

0

0

0

0

0

0

0

1

1

0

0

1

0

1

0

0

1

1

0

1

1

0

0

1

0

1

0

1

0

1

1

1

0

0

1

1

1

1

1

1

结论(结果)

经过实验,所设计的全加器输出的结果正确复合逻辑

试验心得与小结

学习了门级元件的使用,而且使用的是结构化建模,而不是行为建模,又是一次提高。

.F(F),

.Co(Co)

);

initial begin

// Initialize Inputs

A = 0;B = 0;Ci = 0;

// Wait 100 ns for global reset to finish

杭电计组实验3-多功能ALU设计实验

杭电计组实验3-多功能ALU设计实验杭州电子科技大学计算机学院实验报告实验项目:课程名称:计算机组成原理与系统结构课程设计姓名: 学号: 同组姓名: 学号: 实验位置(机号):实验日期: 指导教师:一、实验目的(1)学习多功能ALU的工作原理,掌握运算器的设计方法。

(2)掌握运用Verilog HDL进行数据流描述与建模的技巧和方法,掌握运算器的设计方法。

二、实验仪器实验 ISE工具软件内容三、步骤、方法(算(1)启动Xilinx ISE软件,选择File->New Project,输入工程名shiyan2,默认选择后,点法、击Next按钮,确认工程信息后点击Finish按钮,创建一个完整的工程。

程(2)在工程管理区的任意位置右击,选择New Source命令。

弹出New Source Wizard对序、话框,选择Verilog Module,并输入Verilog 文件名shiyan3,点击Next按钮进入下一步,点步骤击Finish完成创建。

和方(3)编辑程序源代码,然后编译,综合;选择Synthesize--XST项中的Check Syntax右击法) 选择Run命令,并查看RTL视图;如果编译出错,则需要修改程序代码,直至正确。

(4)在工程管理区将View类型设置成Simulation,在任意位置右击,选择New Source命令,选择Verilog Test Fixture选项,输入实验名shiyan3_test。

点击Next,点击Finish,完成。

编写激励代码,观察仿真波形,如果验证逻辑有误,则修改代码,重新编译,仿真,直至正确。

(5)由于实验三并未链接实验板,所以后面的链接实验板的步骤此处没有。

一,操作过程实验过程和描述:module shiyan3(ALU_OP,AB_SW,OF,ZF,F);reg [31:0]A,B;input [2:0]ALU_OP;input [2:0]AB_SW;操作 wire OF;过程 reg ZF;及结reg [31:0]F;果 output OF;output ZF;output F;reg C32;always@(*)begincase(AB_SW)3'b000: begin A=32'h0000_0000; B=32'h0000_0000; end3'b001: begin A=32'h0000_0003; B=32'h0000_0607; end3'b010: begin A=32'h8000_0000; B=32'h8000_0000; end3'b011: begin A=32'h7FFF_FFFF; B=32'h7FFF_FFFF; end3'b100: begin A=32'hFFFF_FFFF; B=32'hFFFF_FFFF; end3'b101: begin A=32'h8000_0000; B=32'hFFFF_FFFF; end3'b110: begin A=32'hFFFF_FFFF; B=32'h8000_0000; end3'b111: begin A=32'h1234_5678; B=32'h3333_2222; enddefault: begin A=32'h9ABC_DEF0; B=32'h1111_2222; endendcaseendalways@(*)begincase(ALU_OP)3'b000: F<=A&B;3'b001: F<=A|B;3'b010: F<=A^B;3'b011: F<=A~^B;3'b100: {C32,F}<=A+B;3'b101: {C32,F}<=A-B;3'b110: begin if(A<B) F<=32'h0000_0001; else F<=32'h0000_0000; end 3'b111: begin F<=B<<A; enddefault: F<=32'h0000_0000;endcaseendalways@(*)beginif(F===32'h0000_0000)ZF<=1;elseZF<=0;endassign OF=C32^F[31]^A[31]^B[31]; endmodule仿真代码module shiyan3_test;// Inputsreg [2:0] ALU_OP;reg [2:0] AB_SW;// Outputswire OF;wire ZF;wire [31:0] F;// Instantiate the Unit Under Test (UUT) shiyan3 uut (.ALU_OP(ALU_OP),.AB_SW(AB_SW),.OF(OF),.ZF(ZF),.F(F));initial begin// Initialize InputsALU_OP = 0;AB_SW = 0;// Wait 100 ns for global reset to finish #100;// Add stimulus here #100;ALU_OP = 001;AB_SW = 001; #100;ALU_OP = 010;AB_SW = 010; #100;ALU_OP = 011;AB_SW = 011; #100;ALU_OP = 100;AB_SW = 100; #100;ALU_OP = 101;AB_SW = 101; #100;ALU_OP = 110;AB_SW = 110; #100;ALU_OP = 111;AB_SW = 111;end endmodule RTL图二、结果思考题:(2)经过分析,该ALU不能实现MIPS核心指令集的所有指令。

杭电计组实验四

0000_0003

$00011

7FFF_FFFF

7FFF_FFFF

$00111

7FFF_FFFF

7FFF_FFFF

$01111

0000_0000

0000_0000

$11111

000ቤተ መጻሕፍቲ ባይዱ_0003

0000_0003

$10000

7FFF_FFFF

7FFF_FFFF

$11000

7FFF_FFFF

input [4:0] W_Addr;

input [31:0] W_Data;

input Write_Reg;

input Clk;

input Reset;

output [31:0] R_Data_A;

output [31:0] R_Data_B;

integer i;

reg[31:0] REG_Files[31:0];//定义寄存器

实验报告

2016年4月22日成绩:

姓名

学号

班级

专业

信息安全

课程名称

《计算机组成原理课程设计》

任课老师

曾虹

指导老师

曾虹

机位号

实验序号

实验名称

寄存器堆

实验时间

2016、4、22

实验地点

1教南

实验设备号

一、实验程序源代码

module Reg(LED,RW_SW,AB,Reg_Addr_A,Reg_Addr_B,Write_Reg,clk,rst);

NET "Add[3]" LOC = "V8";

NET "Add[2]" LOC = "U8";

杭电计组实验-存储器设计实验

杭电计组实验-存储器设计实验————————————————————————————————作者:————————————————————————————————日期:实验报告2018 年 5 月 5 日成绩:姓名阳光男学号16041321 班级16052317专业计算机科学与技术课程名称《计算机组成原理与系统结构试验》任课老师张翔老师指导老师张翔老师机位号默认实验序号5实验名称《实验五存储器设计实验》实验时间2018/5/12实验地点1教211实验设备号个人电脑、Nexys3开发板一、实验程序源代码存储器顶层电路代码:module top_RAM_B(Mem_Addr,C,Mem_Write,Clk,LED);input [7:2]Mem_Addr;//开关的3、4、5、6、7、8位input Mem_Write,Clk;//clk为按键C9,读写使能信号为按键C4,0为读,1为写input [1:0]C;//选择写入数据+读操作时选择显示字节,为开关1、2位output reg [7:0]LED;wire [31:0]M_R_Data;//存在存储器里的32位读出数据reg [31:0]M_W_Data;//寄存在暂存器的32位写入数据RAM_B test_ram (.clka(Clk), //输入时钟信号.wea(Mem_Write), //输入读写信号.addra(Mem_Addr[7:2]), //输入5位地址信号.dina(M_W_Data), //写入32位数据.douta(M_R_Data) //读出32位数据);always@(*)beginLED=0;//初始化M_W_Data=0;//初始化if(!Mem_Write)//读操作begincase(C)2'b00:LED=M_R_Data[7:0];//读出数据的0-7位2'b01:LED=M_R_Data[15:8];//读出数据的8-15位2'b10:LED=M_R_Data[23:16];//读出数据的16-23位2'b11:LED=M_R_Data[31:24];//读出数据的24-31位endcaseendelsebegincase(C)2'b00:M_W_Data=32'h0055_7523;//写入第一个数据2'b01:M_W_Data=32'h1234_5678;//写入第二个数据2'b10:M_W_Data=32'h8765_4321;//写入第三个数据2'b11:M_W_Data=32'hffff_ffff;//写入第四个数据endcaseendendendmodule测试代码:module test;// Inputsreg clka;reg [0:0] wea;reg [5:0] addra;reg [31:0] dina;// Outputswire [31:0] douta;// Instantiate the Unit Under Test (UUT)RAM_B uut (.clka(clka),.wea(wea),.addra(addra),.dina(dina),.douta(douta));initial begin// Initialize Inputsclka = 0;wea = 0;addra = 0;dina = 0;// Wait 100 ns for global reset to finish #100;// Add stimulus hereclka = 1;wea = 0;addra = 6'b000001;dina = 32'h0000_0003;#100;clka = 0;wea = 0;addra = 6'b000001;dina = 32'h0000_0607;#100;clka = 1;wea = 1;addra = 6'b000001;dina = 32'hFFFF_FFFF;#100;clka = 0;wea = 1;addra = 6'b000001;dina = 32'hFFFF_FFFF;endendmodule二、仿真波形三、电路图顶层电路模块顶层电路内部结构:四、引脚配置(约束文件)NET "Clk" LOC = C9;NET "LED[4]" LOC = M11;NET "LED[3]" LOC = V15;NET "LED[2]" LOC = U15;NET "LED[1]" LOC = V16;NET "LED[0]" LOC = U16;NET "Mem_Addr[7]" LOC = U8;NET "Mem_Addr[6]" LOC = N8;NET "Mem_Addr[5]" LOC = M8;NET "Mem_Addr[4]" LOC = V9;NET "Mem_Addr[2]" LOC = T10;NET "Mem_Write" LOC = C4;NET "Mem_Addr[3]" LOC = T9;NET "C[1]" LOC = T5;NET "C[0]" LOC = V8;NET "LED[7]" LOC = T11;NET "LED[5]" LOC = N11;NET "LED[6]" LOC = R11;五、思考与探索(1)读操作实验结果记录表存储器地址初始化数据读出数据写入新数据读出数据5’b000000 32’b0000000032’b0000000032'h0055_752332'h0055_7523 5’b000001 32’b0000000132’b0000000132'h0055_752332'h0055_7523 5’b000002 32’b0000000232’b0000000232'h0055_752332'h0055_7523 5’b000003 32’b0000000332’b0000000332'h0055_752332'h0055_7523 5’b000004 32’b0000000432’b0000000432'h0055_752332'h0055_7523 5’b000005 32’b0000000532’b0000000532'h0055_752332'h0055_7523 5’b000006 32’b0000000632’b0000000632'h0055_752332'h0055_7523 5’b000007 32’b0000000732’b0000000732'h0055_752332'h0055_7523 (2)答:这些单元的数据已经被改写了。

杭电计组实验1-全加器设计实验

杭电计组实验1-全加器设计实验杭州电子科技大学计算机学院实验报告实验项目:实验1-全加器设计实验课程名称:计算机组成原理与系统结构课程设计姓名:学号:同组姓名:学号:实验位置(机号):自己的笔记本实验日期:指导教师:实验内容(算法、程序、步骤和方法)一、实验目的(1),学习ISE工具软件的使用及仿真方法(2)学习FPGA程序的下载方法(3)熟悉Nexys3实验板(4)掌握运用VerilogHDL进行结构描述与建模的技巧和方法(5)掌握二进制全加器的原理和设计方法二、实验仪器ISE工具软件三、步骤、方法(1)启动XilinxISE 软件,选择File-NewProject,输入工程名,默认选择后,点击Next按钮,确认工程信息后点击Finish按钮,创建一个完整的工程。

(2)在工程管理区的任意位置右击,选择NewSource命令。

弹出NewSourceWizard对话框,选择VerilogModule,并输入Verilog文件名shiyan1,点击Next按钮进入下一步,点击Finish完成创建。

(3)编辑程序源代码,然后编译,综合;选择Synthesize--XST项中的CheckSyntax右击选择Run命令,并查看RTL视图;如果编译出错,则需要修改程序代码,直至正确。

(4)在工程管理区将View类型设置成Simulation,在任意位置右击,选择NewSource命令,选择VerilogTestFixture选项。

输入文件名shiyan1_test,点击Next,点击Finish,完成。

编写激励代码,观察仿真波形,如果验证逻辑有误,则修改代码,重新编译,仿真,直至正确。

(5)由于实验一并未链接实验板,所以后面的链接实验板的步骤此处没有。

操作过程及结果一、操作过程实验过程和描述:moduleshiyan1(A,B,C,F,Ci);inputA,B,C;outputF,Ci;wireA,B,C,F,Ci;wi reS1,S2,S3;xorXU1(F,A,B,C),XU2(S1,A,B);andAU1(S2,A,B),AU2(S3,S1,C);or OU1(Ci,S2,S3);endmodule仿真代码moduleshiyan1_test;//InputsregA;regB;regC;//OutputswireF;wireCi;/ /InstantiatetheUnitUnderTest(UUT)shiyan1uut(.A(A),.B(B),.C(C),.F(F),. Ci(Ci));initialbegin//InitializeInputsA=0;B=0;C=0;//Wait100nsforgloba lresettofinish#100;//AddstimulushereA=0;B=0;C=0;#100A=0;B=0;C=1;#100A =0;B=1;C=0;#100A=0;B=1;C=1;#100A=1;B=0;C=0;#100A=1;B=0;C=1;#100A=1;B= 1;C=0;#100A=1;B=1;C=1;EndRTL图二、结果思考题:((1)根据查看顶层模块RTL的最外层的输入输出接口,和实验指导书式(14.1)所示电路相比,该电路图的输入输出引脚和这个加法器的引脚图式是相符合的。

杭电计算机组成原理寄存器堆设计实验

杭电计算机组成原理寄存器堆设计实验计算机组成原理是计算机科学与技术的基础课程之一,它涉及到计算机的基本组成部分和原理。

在这门课程中,学生通常需要进行一系列的实验来加深对计算机组成原理的理解和应用。

其中之一是关于寄存器堆的设计实验。

寄存器堆是计算机中重要的组成部分之一,它用于存储、读取和写入数据。

在计算机中,数据通常被存储在寄存器中,然后进行各种操作。

因此,设计一个高效可靠的寄存器堆对于计算机的性能至关重要。

根据实验要求,我们需要设计一个8位的寄存器堆,并实现读取、写入和清零等操作。

以下是针对该实验的设计思路和实施步骤。

首先,我们需要确定寄存器堆的结构。

由于该寄存器堆为8位宽度,我们选择使用一个8x8的存储单元阵列。

每个存储单元都可以存储一个8位的数据。

整个寄存器堆由8个存储单元组成,每个存储单元对应一个地址,即0~7接下来,我们需要设计寄存器堆的读写电路。

对于读操作,我们需要通过地址线来选择要读取的存储单元,并将其输出到数据线。

对于写操作,我们同样需要通过地址线来选择要写入的存储单元,并将数据线上的数据写入该存储单元。

为了实现这些操作,我们需要使用多路选择器和数据解码器。

在设计中,我们还需要考虑到时钟信号的输入,以确保读写操作在时钟的上升沿或下降沿进行。

此外,我们还需要添加清零功能,以便将寄存器堆的值重置为零。

为实现清零功能,我们可以将一个额外的输入线与所有存储单元的清零输入连接。

在实施阶段,我们需要使用Verilog或其他硬件描述语言来实现设计。

在代码中,我们首先声明一个8位宽的存储单元阵列作为寄存器堆的基本组成部分。

然后,我们定义读写电路,包括地址线、数据线、多路选择器和数据解码器。

最后,我们添加时钟信号和清零功能。

在完成设计后,我们可以通过仿真工具进行验证。

通过输入不同的数据和地址,观察输出结果是否符合预期。

如果存在问题,我们可以进行调试并进行必要的修改。

一旦仿真结果正确无误,我们就可以开始进行硬件实验了。

杭电计算机组成原理寄存器堆设计实验-4

杭州电子科技大学计算机学院实验报告课程名称:计算机组成原理姓实验项目:寄存器堆设计实验班级:指导教师学号:实验位置:日期:2015年5月7日A=0;B=0;LED=O;W_Data=O;if(!Write_Reg)beginif(!C2)beginA=Addr;case(C1)2'b00:LED=R_Data_A[7:0];2'bO1:LED=R_Data_A[15:8];2'b10:LED=R_Data_A[23:16];2'b11:LED=R_Data_A[31:24];endcaseendelsebeginB=Addr;case(C1)2'b00:LED=R_Data_B[7:0];2'bO1:LED=R_Data_B[15:8];2'b10:LED=R_Data_B[23:16];2'b11:LED=R_Data_B[31:24];endcaseendendelsebegincase(C1)2'b00:W_Data=32'h0000_0003;2'b01:W_Data=32'h0000_0607;2'b10:W_Data=32'hFFFF_FFFF;2'b11:W_Data=32'h1111_1234;endcaseendenden dmodule按照实验的要求,一步步的进行操作。

能够正确的进行 Wire_Reg 写操作,进行读操 作时LED 灯的显示,利用选择A, B 操作读出信号,已经Reset 进行清零信号的操作, 都能顺利的进行,本实验多次失败,收获不小。

(接 上) 实验 内容 (算 法、 程 序、 步骤NET "Addr[0]" LOC =M8; NET "Addr[1]" LOC =N8; NET "Addr[2]" LOC =U8;NET "Addr[3]" LOC =V8; NET "Addr[4]" LOC =T5; NET "C1[0]" LOC = T10; NET "C1[1]" LOC = T9; NET "C2" LOC = B8; NET "Clk" LOC = C 9; NET "LED[0]" LOC =U16; NET "LED[1]" LOC =V16; NET "LED[2]" LOC =U15; NET "LED[3]" LOC =V15; NET "LED[4]" LOC =M11;NET "LED[5]" LOC = N11; NET "LED[6]" LOC = R11; NET "LED[7]" LOC = T11; NET "Reset" LOC = D9; NET "Write_Reg" LOC = V9; 数据 记录 和计结论 (结 果)3.管脚配置实验仿真波形:n n <: Q 电卡p r FWT 尹尸科pi 通 T r n ►卢1叫卜靳 "iz。

杭电计组实验十

output [31:0] PC_new;

output ZF;

output OF;

output Write_Reg;//是否写入

output [31:0] W_Data;

output rd_rt_s; //控制那个作为目的寄存器

output [4:0]W_Addr;//目的操作数地址

endcase

end

//------------------处理I型立即寻址指令------------------------

if(inst[31:29]==3'b001)

begin

imm=inst[15:0];rtinst[20:16];//rt

rs=inst[25:21];//rs

Mem_Write=0;//是否写入数据存储器

.dina(dina), // input [31 : 0] dina

.douta(douta) // output [31 : 0] douta

);

always@(posedge rst or negedge clka)

begin

if(rst)

PC<=32'h00000000;

else

begin

case(PC_s)

.imm_data(imm_data),

.address(address)

//解析指令

);

analysis_inst analysis_inst(

.inst(inst),

.ALU_OP(ALU_OP),

.rs(rs),

.rt(rt),

.rd(rd),

.Write_Reg(Write_Reg),

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

assign PC_new=PC+4;

always@( negedge clkor posedge rst)

begin

if(rst)

PC=32'h0000_0000;

else

PC={24'h000000,PC_new[7:0]};

end

endmodule

Inst_ROM文件:

memory_initialization_radix=16;

2016年5月10日 成绩:

姓名

学号

班级

专业

计算机科学与技术

课程名称

《计算机组成原理课程设计》

任课老师

章复嘉

指导老师

章复嘉

机位号

实验序号

5,6,7

实验名称

寄存器堆设计实验,MIPS汇编器与模拟器实验取,指令与译指令

实验时间

第6周~第14周

实验地点

一教225

实验设备号

一、实验程序源代码

实验五

module main(

input [0:0] wea,

input [7:2] addra,

output [31:0] douta,

input Clk,Reset,

input Write_Reg,

input [4:0] W_Addr,

input [31:0] W_Data,

input [4:0] R_Addr_A,R_Addr_B,

output [31:0] R_Data_A,R_Data_B

);

RAM A1(

.clka(Clk), ea(wea), ddra(addra[7:2]), ina(R_Data_A), outa(douta) lk(Clk),

.Reset(Reset),

.Write_Reg(Write_Reg),

六、意见和建议

.W_Addr(W_Addr),

.W_Data(W_Data),

.R_Addr_A(R_Addr_A),

.R_Addr_B(R_Addr_B),

.R_Data_A(R_Data_A),

.R_Data_B(R_Data_B)

);

endmodule

module RAM(

input clka,

input [0:0] wea,

input [7:2] addra,

input [31:

RAM_B your_instance_name (

.clka(clka), ea(wea), ddra(addra[7:2]), ina(dina), outa(douta)ddra(PC[7:2]),lka(clk), outa(Inst_Code) // output [31 : 0] douta

二、仿真波形

实验五

实验六

实验七:

三、电路图

实验5

实验7

四、引脚配置(约束文件)

五、思考与探索

实验5:

(3)设计实现一个ROM,常规存储器是单端口存储器,每次只接收一个地址,访问一个存储单元,从中读取或写入一个字节或字。主存储器是信息交换的中心,一方面CPU频繁地与主存交换信息,另一方面外设也较频繁地与主存交换信息,而单端口存储器每次只能接受一个访存者,或是读或是写,这就影响到存储器的整体工作速度。?

memory_initialization_vector=00000827,0001102b,00421820,00622020,00832820,00a33020,00463804,00a64820,01264004,00284826,01215020,01075822,00e86022,012c6820,012c7025,00c77825,00a78027,00e38820,02289004,02239804,00f3a004,0034a822,0255b025,0296b820,0253c022,0272c822,0032d026,02d4d82b,0354e02b,02c2e822,0282f020,017af820;