基于VerilogHDL的出租车计费器的实现

推荐-基于FPGA出租车计费系统的设计 精品

南京大学金陵学院本科毕业院系信息科学与工程系专业电子信息科学与技术题目基于FPGA出租车计费系统的设计提交日期20XX年6月3 日摘要通过出租车计费系统的设计,详细介绍了如何使用硬件描述语言Verilog HDL设计复杂逻辑电路的步骤和过程,以及应用美国ALTERA公司的Quartus II 9.0软件进行系统设计、仿真和下载实现的方法。

通过设计,可以看到在EDA平台上用CPLD器件构成该数字系统的设计思想和实现过程。

论述了计费模块、时钟模块、动态显示模块、计费形式判断模块、控制模块等的设计方法和技巧。

关键词:CPLD/FPGA; 电子自动化设计; Verilog HDL硬件描述语言; 出租车计费器; Quartus II 9.0软件ABSTRACTTaxi billing system through the design, details how to use the hardwaredes-cription language Verilog HDL design plexity and the process logic and the applicatio-n of the U.S. pany's Quartus II 9.0 ALTERA software system design, simulation, anddownload the realization of the method. By design, you can see in the EDA platform usi-ng CPLD devices constitute the digital system design and implementation process. Discuss-es the billing module, clock module, dynamic display module, billing forms to judge mod-ule, control module and other design methods and techniques.Keywords: CPLD/FPGA; EDA; Verilog HDL; Taxi Billing Machine; Quartus II 9.0目录第一章引言随着科技日新月异的发展,科技带来的改变无处不在。

基于Verilog_HDL设计的出租车计价器(DOC)

华北水利水电大学EDA课程设计题目:出租车计价器专业:通信工程年级:2011级学生:李高飞学号:201114715指导教师:司孝平完成日期: 2013 年 12月 27日摘要:本文介绍了一种采用可编程逻辑器件(FPGA/CPLD)进行出租车计费器的设计思想以及实现方法。

本设计实现了出租车计费器所需的一些基本功能,计费金额包括起步价、里程计费、等待计时计费等。

该设计采用模块化设计,在Quartus II9.0软件平台下,采用Verilog HDL 硬件描述语言描述和模拟仿真了分频模块、计程模块、计费模块、计时模块,译码以及动态扫描显示模块,完成了出租车计费器仿真设计和硬件电路的实现。

关键词:FPGA,出租车计费器,Quartus,Verilog HDLAbstract:This article describes the design ideas and methods of the taximeter, through the programmable logic device (FPGA/CPLD).The design of a taximeter to achieve the required basic functions,The total of billing included the starting price, metered, and wait for time billing.Through the Quartus II 9.0 Software Platform,Using Verilog HDL language completed the description and simulation of frequency module, the meter module, Billing module, timing modules, decoding, dynamic scanning display module. IT It has completed the taxi meter simulation and the hardware circuit.Keywords:FPGA, Taximeter, Quartus, Verilog HDL目录1.前言 (1)2.总体方案设计 (2)2.1 设计要求 (2)2.2 方案论证与选择 (2)2.3 设计思想及原理 (3)3.单元模块设计 (5)3.1 分频模块 (5)3.1.1 计数器分频模块 (5)3.1.2 计数器分频模块仿真结果 (5)3.1.3 数码管分频模块 (6)3.2 计程模块 (6)3.2.1 计程模块电路 (6)3.2.2 计程模块仿真结果 (7)3.3 计时模块 (7)3.3.1 计时模块电路 (7)3.3.2 计时模块的仿真结果 (7)3.4 控制模块 (8)3.4.1 控制模块电路 (8)3.4.2 计时模块的仿真结果 (9)3.5 计费模块 (10)3.5.1 控制模块电路 (10)3.5.2 计费模块的仿真结果 (10)2.6 数码管显示模块 (11)4.整体顶层模块设计 (12)4.1 整体顶层模块电路 (12)5.系统功能仿真及调试 (13)5.1 系统仿真及调试 (13)6.总结与体会 (16)致谢 (17)参考文献 (17)附录A: 单元模块Verilog HDL源代码 (18)A.1 计数器的分频模块VerilogHDL源代码 (18)A.2数码管的分频模块VerilogHDL源代码 (18)A.3 计程模块VerilogHDL源代码 (19)A.4 计时模块VerilogHDL源代码 (20)A.5 控制模块VerilogHDL源代码 (21)A.6 计费模块VerilogHDL源代码 (21)A.7 数码管显示模块VerilogHDL源代码 (21)A.8整体顶层模块VerilogHDL源代码 (23)附录B: 整体顶层电路图 (24)2.总体方案设计2.1 设计要求该出租车计价器实现功能:1、行程≤4公里,且等待累计时间≤2分钟,起步费为8.0元。

基于FPGA的出租车计价系统设计

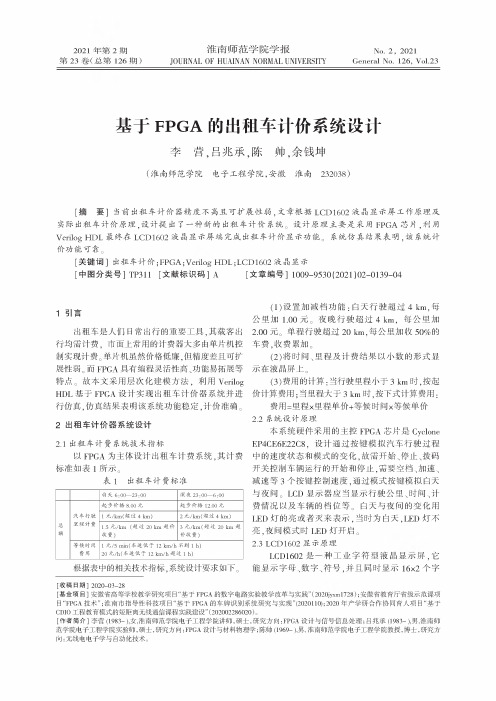

2021年 2期第23卷(总第126期)No. 2, 2021General No. 126, Vol.23淮南师范学院学报JOURNAL OF HUAINAN NORMAL UNIVERSITY基于FPGA 的出租车计价系统设计李营,吕兆承,陈帅,余钱坤(淮南师范学院电子工程学院,安徽淮南232038)[摘要]当前出租车计价器精度不高且可扩展性弱,文章根据LCD1602液晶显示屏工作原理及实际出租车计价原理,设计提出了一种新的出租车计价系统。

设计原理主要是采用FPGA 芯片,利用Verilog HDL 最终在LCD1602液晶显示屏端完成出租车计价显示功能。

系统仿真结果表明,该系统计价功能可靠。

[关键词]出租车计价;FPGA ;Verilog HDL ;LCD1602液晶显示[中图分类号]TP311 [文献标识码]A [文章编号]1009-9530(2021)02-0139-041引言出租车是人们日常出行的重要工具,其载客出 行均需计费,市面上常用的计费器大多由单片机控 制实现计费。

单片机虽然价格低廉,但精度差且可扩展性弱。

而FPGA 具有编程灵活性高、功能易拓展等 特点。

故本文采用层次化建模方法,利用Verilog HDL 基于FPGA 设计实现出租车计价器系统并进 行仿真,仿真结果表明该系统功能稳定,计价准确。

2出租车计价器系统设计2.1出租车计费系统技术指标以FPGA 为主体设计出租车计费系统,其计费 标准如表1所示。

表1出租车计费标准根据表中的相关技术指标,系统设计要求如下。

白天 6:00—23:00深夜 23:00—6:00总额汽车行驶 里程计费起步价格8.00元起步价格12.00元1元/km (超过4 km )2元/km (超过4 km )1.5元/km (超过20 km 超价 收费)3元/km (超过20 km 超价收费 )等候时间 费用1元/5 min (车速低于12 km/h 不到1 h) 20元/h (车速低于12 km/h 超过1 h)(1) 设置加减档功能:白天行驶超过4 km ,每公里加1.00元。

基于Verilog HDL的出租车计费器设计

李明洪基于Verilog HDL的出租车计费器设计基于Verilog HDL的出租车计费器设计学生姓名:李明洪指导老师:肖红光摘要本次课程设计主要是基于FPGA芯片,使用硬件描述语言Veriloh HDL,采用“自顶向下”的设计方法,编写一个出租车计费器芯片,并使用Max+Plus II软件仿真平台。

本文主要描述了出租车计费器的设计思路与模块划分。

把出租车计费器划分为五大模块,共同实现了出租车计费以及预置和模拟汽车启动、停止、暂停等功能,并动态扫描显示车费数目。

最后,使用Max+Plus II仿真平台对每个模块和主程序分别进行了仿真,并对仿真出来的波形作了分析。

关键词出租车计费;Verilog HDL;Max+Plus II;仿真The design of taxi meter based onVerilog HDLAbstract The course design is mainly based on FPGA chip, the use of hardware description language Veriloh HDL, using "top down " design method, the preparation of a taxi meter chip, and use the Max + Plus II software simulation platform. This paper describes the design idea of the taxi meter and module division. The taxi meter is divided into five modules together to achieve a taxi and analog auto billing and pre-start, stop, pause function, and dynamic scan showed the number of fare. Finally, using Max + Plus II simulation platform and the main program for each module were simulated, and the simulation from an analysis of the waveform.Keywords Taxi charges;Verilog HDL;Max+Plus II;Simulation1 引言随着中国城市化的快速发展,人们出行的选择也会越来越多样化,但是出租车作为一种重要的交通工具,也越来越多的被人们所选择,虽然在大中城市,出租车已经相当普及,但是在一些小的城市,出租车行业也因为城市化进程的加快而快速发展。

最新-基于CPLD/FPGA的出租车计费器 精品

基于CPLD/FPGA的出租车计费器

摘要介绍了出租车计费器系统的组成及工作原理,简述了在平台上用单片器件构成该数字系统的设计思想和实现过程。

论述了车型调整模块、计程模块、计费模块、译码动态扫描模块等的设计方法与技巧。

关键词/硬件描述语言出租车计费器+软件数字系统

随着技术的高速发展,电子系统的设计技术和工具发生了深刻的变化,大规模可编程逻辑器件/的出现,给设计人员带来了诸多方便。

利用它进行产品开发,不仅成本低、周期短、可靠性高,而且具有完全的知识产权。

本文介绍了一个以公司可编程逻辑芯片712884-15为控制核心、附加一定外围电路组成的出租车计费器系统。

1系统组成

基于/的出租车计费器的组成如图1所示。

各部分主要功能如下1计数器对车轮传感器送来的脉冲信号进行计数每转一圈送一个脉冲。

不同车型的车轮直径可能不一样,通过设置1对车型做出选择,以实现对不同车轮直径的车进行调整。

2计数器对百米脉冲进行累加,并输出实际公里数的码给译码动态扫描模块。

每计满500送出一个脉冲给计数器。

设置2实现起步公里数预制。

3计数器实现步长可变即单价可调的累加计数,每500米计费一次。

设置3用来完成超价加费、起步价预制等。

4译码/动态扫描将路程与费用的数值译码后用动态扫描的方式驱动数码管。

5数码管显示将公里数和计费金额均用四位数码管显示三位整数,1位小数。

2功能模块设计

出租车计费器由车型调整模块、计程模块、计费模块、译码动态及扫描等模块组成,整个系统采用模块化设计,首先用编写功能模块,然后用顶层原理图将。

基于VerilogHDL设计的出租车计价器之欧阳音创编

西华年夜学课程设计说明书题目:出租车计价器专业:信息工程年级:级学生:潘帅学号:3308020****指导教师:林竞力完成日期: 6月6 日摘要:本文介绍了一种采取可编程逻辑器件(FPGA/CPLD)进行出租车计费器的设计思想以及实现办法。

本设计实现了出租车计费器所需的一些基本功能,计费金额包含起步价、里程计费、等待计时计费等。

该设计采取模块化设计,在QuartusII9.0软件平台下,采取Verilog HDL 硬件描述语言描述和模拟仿真了分频模块、计程模块、计费模块、计时模块,译码以及静态扫描显示模块,完成了出租车计费器仿真设计和硬件电路的实现。

关键词:FPGA,出租车计费器,Quartus,Verilog HDL Abstract:This article describes the design ideas and methods of the taximeter,through the programmable logic device(FPGA/CPLD).The design of a taximeter to achieve the required basic functions,The total of billingincluded the starting price, metered, and wait for time billing.Through the Quartus II 9.0 Software Platform,Using Verilog HDL language completed the description and simulation of frequency module, the meter module, Billing module, timing modules, decoding, dynamic scanning display module.ITIt has completed the taxi meter simulation and the hardware circuit. Keywords:FPGA, Taximeter, Quartus, Verilog HDL目录1.前言12.总体计划设计32.1 设计要求32.2 计划论证与选择32.3 设计思想及原理43.单位模块设计63.1 分频模块63.1.1计数器分频模块63.1.2 计数器分频模块仿真结果73.1.3 数码管分频模块73.2 计程模块73.2.1 计程模块电路73.2.2 计程模块仿真结果83.3 计时模块83.3.1 计时模块电路83.3.2 计时模块的仿真结果93.4 控制模块103.4.1 控制模块电路103.4.2 计时模块的仿真结果103.5 计费模块113.5.1 控制模块电路113.5.2 计费模块的仿真结果122.6 数码管显示模块124.整体顶层模块设计134.1 整体顶层模块电路135.系统功能仿真及调试145.1 系统仿真及调试146.总结与体会17致谢19参考文献19附录A:单位模块Verilog HDL源代码20A.1 计数器的分频模块VerilogHDL源代码20A.2数码管的分频模块VerilogHDL源代码20A.3 计程模块VerilogHDL源代码21A.4 计时模块VerilogHDL源代码22A.5 控制模块VerilogHDL源代码23A.6 计费模块VerilogHDL源代码23A.7 数码管显示模块VerilogHDL源代码24A.8整体顶层模块VerilogHDL源代码25附录B:整体顶层电路图271.前言随着出租车行业的成长,对出租车计费器的要求也越来越高。

基于VHDL_的出租车计费器的设计

基于VHDL 的出租车计费器的设计目前以硬件描述语言(Verilog 或VHDL)所完成的电路设计,可以经过简单的综合与布局,快速的烧录至FPGA 上进行测试,是现代IC 设计验证的技术主流。

这些可编辑元件可以被用来实现一些基本的逻辑门电路(比如AND、OR、XOR、NOT)或者更复杂一些的组合功能比如解码器或数学方程式。

在大多数的FPGA里面,这些可编辑的元件里也包含记忆元件例如触发器(Flip-flop)或者其他更加完整的记忆块。

系统设计师可以根据需要通过可编辑的连接把FPGA内部的逻辑块连接起来,就好像一个电路试验板被放在了一个芯片里。

一个出厂后的成品FPGA的逻辑块和连接可以按照设计者而改变,所以FPGA可以完成所需要的逻辑功能。

本设计是一种采用FPGA芯片进行出租车计费器,主要分为分频模块、计量模块、计费模块、控制模块等模块,利用FPGA的可编程性,简洁又多变的设计方法,缩短了研发周期。

主要采用了FPGA芯片,使用VHDL语言进行编程,使其具有了更强的移植性,更加利于产品的升级。

一、设计任务与要求(1)、能够实现计费功能费用的计算是按行驶里程收费,设出租车的起步价是5.00元,当里程小于3km里时,按起步价收费;当里程大于3km时每公里按1.3元计费。

等待累计时间超过2min,按每分钟1.5元计费。

所以总费用按下式计算:总费用=起步价+(里程-3km)*里程单价+等候时间*等候单价(2)、能够实现显示功能●显示汽车行驶里程:用四位数字显示,显示方式为“XXXX”,单价为km。

计程范围为0~99km,计程分辨率为1km。

●显示等候时间:用两位数字显示分钟,显示方式为“XX”。

计时范围为0~59min,计时分辨率为1min。

●显示总费用:用四位数字显示,显示方式为“XXX.X”,单位为元。

计价范围为999.9元,计价分辨率为0.1元。

二、设计原理根据设计要求,系统的输入信号clk,计价开始信号Start,等待信号Stop,里程脉冲信号fin。

课程设计(论文)基于fpga的出租车计价器设计

基于FPGA的出租车计价器设计摘要介绍了出租车计费器系统的组成及工作原理,简述了在EDA平台上用FPGA 器件构成该数字系统的设计思想和实现过程。

论述了计程模块,计费模块,计时模块,译码动态扫描模块等的设计方法与技巧。

1.引言随着EDA技术的高速发展,电子系统的设计技术发生了深刻的变化,大规模可编程逻辑器件CPLD/FPGA的出现,给设计人员带来了诸多方便。

利用它进行产品开发,不仅成本低、周期短、可靠性高,而且具有完全的知识产权。

本文介绍了一个以Altera公司可编程逻辑芯片cyclone2系列的EP2C5T144C8的FPGA 芯片为控制核心、附加一定外围电路组成的出租车计费器系统。

随着社会的不断进步,人们生活水平的不断提高,出租车逐渐成为人们日常生活不可缺少的交通工具。

而计价器作为出租车的一个重要组成部分,关系着出租车司机和乘客双方利益,起着重要的作用,因而出租车计价器的发展非常迅猛。

2.出租车计费系统的实验任务及要求2.1技术要求(1)掌握较复杂逻辑的设计、调试。

(2)进一步掌握用VHDL语言设计数字逻辑电路。

(3)掌握用Max+pulsII软件的原理图输入的设计方法。

2.2功能要求基本功能:(1)按行驶里程收费,起步价为9.00元,并在车行3公里后再按3元/公里计算车费。

(2)实现模拟功能:能模拟汽车启动、停止。

(3)设计动态扫描电路:将车费、里程、等待时间动态的显示出来。

(4)用VHDL语言设计符合上述功能要求的出租车计费器,并用层次化设计方法设计该电路。

(5)各计数器的计数状态用功能仿真的方法验证,并通过有关波形确认电路设计是否正确。

附加功能:(1)增加了晚上计费功能和等待功能。

晚上起步价为12.00元,并在车行3公里后再按4元/公里计算车费。

车白天停止超过三分钟后按1元/分钟计算,晚上超过3分钟按2元/分钟计算。

(2)实现预置功能:能预置起步费、每公里收费、等待加费时间。

(3)实现模拟功能:白天、黑夜;等待、行驶状态。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

基于VerilogHDL的出租车计费器的实现

摘要本文介绍了出租车计费器系统的组成及工作原理,采用自顶而下的设计方法,设计了一种基于

硬件描述语言的出租车自动计费器,在CPLD芯片EPM3256ATC144-7上实现了其功能,并论述了显示模

块、主控模块、计费模块等实现方法。

关键词CPLD;硬件描述语言;出租车计费器

随着CPLD/FPGA等数字可编程器件的出现,他们可以解决传统电子设计不能完成的任务。

利用CPLD来实现出租车计费器,可行性很高,而且电路简单,大大减少外围器件,可以用软件完全仿真,灵活度高,可以设计一些复杂的系统,而且编好的系统可以在不同的FPGA或CPLD芯片上通用。

1 Mars-EDA-S实验主板

本设计采用了Mars-EDA-S实验主板,其核心芯片是Altera公司的EPM3256ATC144-7芯片。

板上具有如下资源:主芯片:EPM3256ATC144-7,有源晶振:40MHz;复位芯片:STC811,支持复位手动输入,支持JTAG下载模式。

核心板可以作为原型板,用户可以根据自己需要自行扩展。

2 出租车计费器系统设计概述

基于CPLD设计的出租车自动计费器,计费包括起步价、行车里程计费、等待时间计费3部分,用三位数码管显示总金额,最大值为99.9元。

起步价为 5.0元,3km之内按起步价计费,超过3km的,每1km增加1元,等待时间单价为每分钟0.1元。

用两位数码管显示总里程,最大值为99km,用两位数码管等待时间,最大值为99min。

系统框图如图1所示。

2.1 分频模块

由于EPM3256ATC144-7芯片的时钟频率为40MHz,而主控模块所用频率为1Hz,必须经过分频才能使得EPM3256ATC144-7芯片与程序匹配。

//分频

/*信号定义:

clk_in:输入时钟信号:大小为40MHz;

clk:输出时钟信号;大小为1Hz;*/

module clock_send(clk_in,clk);

input clk_in;

output clk;

reg clock;

reg clk;

reg[24:0] cnt;

always@(posedge clk_in)

begin

cnt<=cnt+1;

if(cnt==25’d1*******)

begin

cnt<=0;

clock=~clock;

end

clk<=clock;

end

endmodule

2.2 主控模块

在主控模块中,设置拨码开关m控制led灯使系统显示出租车的当前状态,当led灯亮时开始计程,计费显示起步价5元,3km之内为起步价,即300个clk之内为起步价,以后每1km增加1元,即每10个clk增加0.1元;led灯灭时开始记等待时间,每分钟计费增加0.1元,即每60个clk增加0.1元。

2.3 系统顶层设计

整个系统采用自顶向下,模块化设计理念,将整个系统设计为3个模块,分别为分频模块(clock_send)、显示模块(sel)、主控模块(ntaxi)。

最底层子模块用Verilog HDL编写,在MAX+plusⅡ环境下对每个底层模块程序进行编译,仿真,然后再将各个模块连接起来,图形法逐级形成顶层模块,最终的整个系统顶层。

该设计在Mars—EDA—S实验板上用到了七位数码管、一个拨码开关和一个led灯和复位键。

用三位数码管显示计费金额,用两位数码管显示等待时间,用两位数码管显示行驶里程。

当拨码开关处于on状态时,led灯亮,出租车计费器开始计程和计费。

当拨码开关处于off状态时,led灯灭,出租车计费器开始计等待时间和计费。

按下复位键计费器显示起步价。

3 需改进的地方

此出租车计费器能够实现计程、计等待时间和计费功能,还可以实现以下功能:

1)增加计价标准设定功能。

通过设计此功能模块可以使得计价标准设计更加灵活,体现目前出租车行业发展的需要,白天和黑夜可实行不同的计费标准,不同车型的出租车也可执行不同的计费标准,并可根据油价的变化实行适当地改变计费标准。

2)限速功能。

如果出租车超速发出报警声,提示司机减速行驶。

3)静态显示计时功能,空车使用点阵显示“空”字。

4 结论

采用传统的电路原理图输出法进行设计时,具有设计周期长,需要专门的设计工具,以及手工布线等缺陷。

与之相比,使用语言描述的形式,则大大缩短了开发周期,减少了开发难度,总之,Verilog HDL有着类似C语言的风格,易于学习和掌握,用Verilog HDL等硬件描述语文进行数字系统的设计是当前EDA发展的趋势,也是一种具有广阔前景的集成电路开发工具。

在具体的EDA教学过程中,除了要培养学生在电路功能实现方而的能力,还需要培养工程实用问题的解决能力。

参考文献

[1]侯继红,李向东.EDA实用技术教程.中国电力出版社, 2004.

[2]李洋.EDA技术实用教程.机械工业出版社,2004.

[3]刘艳萍,高振斌,李志军.EDA实用技术及应用.国防工业出版社,2006.。