数字逻辑电路课件第7-8章

第08章 门电路与组合逻辑电路 PPT课件

逻辑与 A 0 0 A1 A A A A A A 0

一、逻辑代数基础

1.逻辑代数运算法则

反演律 AB A B A B A B

吸收律 A AB A

A(A B) A

A AB A B (A B) (A C) A BC

遵守交换律、结合律、分配律 反演律(摩根律) 、吸收律等

(2)CMOS传输门电路

相当于理想开关

传输门的开通与关断取决于控制信号C和 C ,在 C 输入端加了符号“○”,C 喻意C 低电平有效,即C =0就允许信号传输。

低电平 有效

高电平 有效

3.集成门电路使用的一些实际问题

TTL门电路多余输入端的处理

①接高电平;②接低电平;③并联;④剪短悬空

与门, 与非门

双极型 三极管 半导体集成门电路:

单极型 场效应管

1.TTL门电路 Transistor-transistor Logic

属于双极型集成门 电路,主要以TTL 与非门电路为基础

典型TTL与非门电路的结构、功能和逻辑符号

Y A BC

C1

T1:多发射极晶体 管,构成与门电路

TTL与非门工作原理

与逻辑真值表

表达式:Y=A·B N A B Y

1

0

000 0 101 0

0

A&

210 0

Y 311 1

B

2.或逻辑和或门电路

或逻辑(OR logic):当决定某 一事情的几个条件中,只要有一 个或一个以上条件具备,这件事 就会发生。

A

+

Y-

B

“1”—接通或灯亮; “0”—断开或灯灭

或逻辑真值表 NAB Y 000 0 101 1 210 1 311 1

数字逻辑电路PPT课件

正负逻辑转换举例 正逻辑(与非门) AB Y 001 011 101 110

负逻辑(或非门) AB Y

11 0 10 0 01 0 00 1

第32页/共97页

1.2.4 基本定律和规则 1. 逻辑函数的相等

设有两个逻辑:F1=f1(A1,A2,…,An) F2=f2(A1,A2,…,An)

如果对于A1,A2,…,An 的任何一组取值(共2n组), F1 和 F2均相等,则称F1和 F2相等.

4. 二进制数与十进制数之间的转换 (1)二进制数转换为十进制数(按权展开法)

例:

(1011.101) 1 23 1 21 1 20 1 21 1 23 2

8 2 1 0.5 0.125

第8页/共97页

(2)十进制数转换为二进制数(提取2的幂法)

例: (45.5)10 32 8 4 1 0.5 1 25 0 24 1 23 1 22 0 21 1 20 1 2-1 (101101.1)2

· + 0 1 原变量 反变量

+ · 1 0 反变量 原变量 则所得新的逻辑式即为F的反函数,记为F。

例 已知 F=A B + A B, 根据上述规则可得: F=(A+B)(A+B)

第37页/共97页

例 已知 F=A+B+C+D+E, 则 F=A B C D E

由F求反函数注意: 1)保持原式运算的优先次序; 2)原式中的不属于单变量上的非号不变;

00

0

01

1

10

1

11

1

第20页/共97页

A

≥1

B

或门逻辑符号

F=A+B

或门的逻辑功能概括为: 1) 有“1”出“1”; 2) 全“0” 出“0”.

数字逻辑电路 PPT课件

在一个实际的数字系统中,往往需要能实现多种

多样逻辑功能的门电路,只有一种与非门作为基本单 元使用起来显然是不方便的。在TTL门电路的系列产 品中,常用的还有或非门、与或非门、与门、或门等 等。虽然门电路的种类很多,但它们或者是由与非门 稍加改动得到的,或者是由与非门中的若干部分组合 成的,有的就是与非门的一部分。如,与非门只有一 个输入端时成了非门;在与非门后再连一个非门成了 与门;在与非门前面对于每个输入端各接一个非门成 了或门。可以说与非门可以完成一切逻辑运算。因此, 只要掌握与非门典型电路的工作原理和分析方法,就 不难对其它形式的门电路进行分析了。

2. 或门电路 上图为简单的具有两个输入端的二极管或门电路、常用

逻辑符号、逻辑表达式及真值表。 其中A、B分别为两个输入端,F为输出端。这种电路之

所以能实现或运算,是因为输出端的电平被最高电平的输入 端钳位,只要输入端有一个高电平时,输出就是高电平。也 就是说输入有一个为1时,输出即为1。输入端全为0时,输 出才为0。

阐述逻辑控制、脉冲计数和数字显示的基本原 理,介绍常用的计数器和A/D、D/A转换器。

主要内容

第一节 基本逻辑电路 第二节 双稳态触发器 第三节 脉冲的计数和显示 第四节 数模和模数转换

第一节 基本逻辑电路

所谓逻辑是指“条件”与“结果”的 关系。逻辑电路(logic circuit)是用电路的 输入信号反映“条件”,用电路的输出信 号反映“结果”。电路的输出与输入之间 构成一定的逻辑关系。

组合逻辑电路7、8、9节

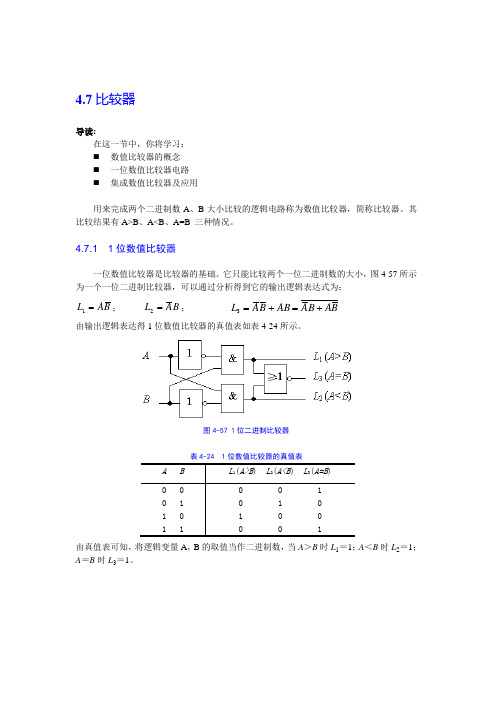

4.7比较器导读:在这一节中,你将学习:⏹数值比较器的概念⏹一位数值比较器电路⏹集成数值比较器及应用用来完成两个二进制数A、B大小比较的逻辑电路称为数值比较器,简称比较器。

其比较结果有A>B、A<B、A=B 三种情况。

4.7.1 1位数值比较器一位数值比较器是比较器的基础。

它只能比较两个一位二进制数的大小,图4-57所示为一个一位二进制比较器,可以通过分析得到它的输出逻辑表达式为:BA L=1;BAL=2;BABAABBAL+=+=3由输出逻辑表达得1位数值比较器的真值表如表4-24所示。

图4-57 1位二进制比较器表4-24 1位数值比较器的真值表由真值表可知,将逻辑变量A,B的取值当作二进制数,当A>B时L1=1;A<B时L2=1;A=B时L3=1。

4.7.2 集成数值比较器多位数值比较器的设计原则是先从高位比起,高位不等时,数值的大小由高位确定。

若高位相等,则再比较低位数,比较结果由低位的比较结果决定。

常用的集成数值比较器有4位数值比较器74LS85,其功能表如表4-25所示,从表4-25中可看出:表4-25 74LS85功能表真值表中的输入变量包括八个比较输入端A 3、B 3、A 2、B 2、A 1、B 1 、A 0、B 0和三个级联输入端A '>B '、A '<B '和A '=B '。

级联输入端是为了便于输入低位数比较结果,是为了能与其它数值比较器连接,以便组成更多位数的数值比较器。

3个输出信号 L 1(A >B )、L 2(A >B )、和L 3(A =B )分别表示本级的比较结果。

74LS85的逻辑图和引脚图如图4-58所示。

图4-58 74LS85的逻辑图和引脚图4.7.3 集成数值比较器应用举例数值比较器就是比较两个二进制数的大小,如果二进制数的位数比较多,就需将几片数值比较器连接进行扩展,数值比较器的扩展方式有并联和串联两种。

图4-59为两片四位二进制数值比较器串联扩展为八位数值比较器。

逻辑门电路及组合逻辑电路PPT课件

例8-15 某工厂有A、B、C三个车间和一个自备电站,站内有两台发电机G1和G2。 G1的容量是G2的两倍。如果一个车间开工,只需G2运行即可满足要求;如果两个 车间开工,只需G1运行;若三个车间同时开工,则G1和G2均需运行。试画出控制 G1和G2运行的逻辑图。

解 用A、B、C分别表示三个车间的开工状态:开工为1,不开工为0;G1和G2运行 为1,停机为0。

① 根据题意列出逻辑真值表。

第6页/共39页

第八章 逻辑门电路及组合逻辑电路 8.1 逻辑代数及逻辑门电路

三、逻辑代数运算法则

1.基本运算法则

0·A=0

1·A=A

A·A=A 0+A=A

AA 0 1+A=1

A+A=A A A 1

AA 2.交换律

AB=BA A+B=B+A 3.结合律 ABC=(AB)C=A(BC)

A+B+C=A+(B+C)=(A+B)+C 4.分配律 A(B+C)=AB+AC

10

非逻辑的逻辑表达式为:F=A

可用逻辑非门实现这种运算,非门的逻辑符号为:

1

A

F

非门的波形为: A

非门

F

第4页/共39页

第八章 逻辑门电路及组合逻辑电路 8.1 逻辑代数及逻辑门电路

(二)复合逻辑运算及其复合门

用两个以上基本运算构成的逻辑运算。包括与非、或非、与或非、异 或和同或运算。和三个基本运算一样,它们都有集成门电路与之对应。

第13页/共39页

第八章 逻辑门电路及组合逻辑电路 8.2 组合逻辑电路

例8-12 分析如图所示电路的逻辑功能。

AB

数字逻辑电路大全PPT课件(2024版)

第6页/共48页

Rb1 4kΩ

Rc 2 1.6kΩ

Vc 2

1

+VCC( +5V) Rc4 130Ω

3

T2 4

1

3

A

31

2T2

D Vo

B

T1

C

Ve 2

1

3

2T 3

Re2

1kΩ

输入级

中间级

输出级

第7页/共48页

2.TTL与非门的逻辑关系

(1)输入全为高电平3.6V时。

T2、T3导通,VB1=0.7×3=2.1(V ),

列。 6 . 74AS 系 列 —— 为 先 进 肖 特 基 系

列, 它是74S系列的后继产品。 7.74ALS系列——为先进低 功耗肖特基系列, 是74LS系列的后继产品。

第30页/共48页

2.3

一、 NMOS门电路 1.NMOS非门

MOS逻辑门电路

VDD (+12V)

VDD (+12V)

VDD (+12V)

0.4V

高 电 平 噪 声 容 限 第1V5页NH/共=48V页OH ( min ) - VON = 2.4V-2.0V =

四、TTL与非门的带负载能力

1.输入低电平电流IIL与输入高电平电流IIH (1)输入低电平电流IIL——是指当门电路的输入端

接低电平时,从门电路输入端流出的电流。

& Vo G0

呈 现 高 阻 , 称 为 高 阻 态 , 或 禁 止 态+V。CC

Rc2

Rc4

Rb1

Vc2 1

3

T2 4

A

&

B

L

EN

数字逻辑第7章 触发器

《数字逻辑》 假设门传输延时时间为t pd

四、最高时钟频率

2S

VCC 4S 4R 4Q 3SA 3SB 3R 3Q

VDD 4S 4R 1Q 2R 2S 3Q 2Q

16 15 14 13 12 11 10 9 74LS279

12345678

16 15 14 13 12 11 10 9 CC4044

12345678

1R 1SA 1SB 1Q 2R 2S 2Q GND (a) 74LS279 的引脚图

···

《数字逻辑》

一、电路结构和工作原理 1、用两个电平触发D触发器组成的边沿触发器

利用CMOS传输门的边沿触发器

《数字逻辑》

(4)列出真值表

CLK D Q Q *

XXXQ 0 X0 1 X1

(1)clk

0时,T

TG1通,TG2断 G3断,TG4通

Q Q保持,

D, Q随着D而变化 反馈通路接通,自锁

Q’

SR

Q*

《数字逻辑》

10

0

01

1

1 1 保持

0 0 不定

置1 保持 置1 置0 置1 不允许 置1

二、动作特点 在任何时刻,输入都能直接改变输出的状态。

《数字逻辑》

例:

SD和RD同时为0 Q,Q同为1

三、由或非门构成的锁存器

《数字逻辑》

《数字逻辑》

1.工作原理

SD RD Q Q *

两个或非门接成反馈,引出输入端用来置0,1 0 0 0 0

R

Q’m

Q’

CLK

Q 0时,只允许J 1的信号进入主触发器

Q 1时,只允许K 1的信号进入主触发器

《数字逻辑》

《数字逻辑设计》第7章 数据选择器及译码器

P1

P2

P9

P3

P8

Gnd P4

P7 P6

P5

扩展

W=(P8•P9)’ Y=(P2•P3•P6•P7)’

X=(P4•P5•P6•P7)’ Z=(P1•P3•P5•P7•P9)’

X

Y

Z

&

&

&

&

1. 二进制编码器——例:4线-2线编码器

Example

4:2编码器

计算机配有四个外部设备:声卡(A0),硬盘驱动器 (A1),鼠标(A2),网卡(A3),B0、B1为编码输出。

g

CD

AB 00 01 11 10 00 1 1 0 0 01 0 0 1 0 11 × × × × 10 0 0 × ×

g=A+CD+BC+BC

编码器(Encoders)

编码器——

♦ 特点:多输入、多输出的组合逻辑电路 ♦ 功能:将二进制码按照一定规律编排,使其具有特定含义

(如:8421BCD码用1000 代表数字8),与译码器互逆。

0 1 0 0 0 1 1 001 1 4

0 1 0 1 1 0 1 101 1 5

0 1 1 0 1 0 1 111 1 6

0 1 1 1 1 1 1 000 0 7

1 0 0 0 1 1 1 111 1 8

1 0 0 1 1 1 1 101 1 9

七段数码管

f g COM a b

a

f

b

g

e

c

d

e d COM c

A1

A0

典型应用——实现常规逻辑函数

A

D0

D1

D2

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

4X2 PROM的逻辑阵列图

连接符号

用PROM实现半加器

这些存储单元的值?

半加器逻辑表达式

0 0 0 1 0 1 1 0

(PROM) PLD的问题?

只能用于组合逻辑 输入变量的增加,存储容量按2的幂次增加

不适合很多输入变量的组合逻辑电路实现

原因

?

与阵列 不可编程; 或阵列 可编程。

EPROM( Erasable PROM) 存储的数据可以擦除重写

UVEPROM( Ultraviolet Erasable PROM) 紫外线擦除;在器件的封装上装有透明的 石英盖板,写好数据后应用不透明的胶带 将其盖住,以防止数据丢失; E2PROM( Electrically Erasable PROM) 电信号擦除;速度快;

解决办法? PLA

PLA的结构

与或阵列均可编程

PLA与PROM的比较

地址

PROM

000 001 010 011 100 101 110 111

PLA

PLA的问题

需要简化的逻辑函数表达式。

多输入输出时,简化算法复杂。 运行速度下降。 已经淘汰,现主要用于全定制ASIC芯片中

PAL的结构

数据寄存器

地址译码

11 1 1 1 1 0 0

1 1 1 ⑶ 0 数据总线 0 1 1 1

⑴

地址总线

⑵ 读 (1) 地址码011--对应地址3; (2)读取数据; (3)地址3的数据由数据总线传输至数据寄存器

二、ROM

ROM( read-only memory ) 只能从ROM中读取数据,但不能进行写 操作; 断电后,信息不会丢失;

SRAM( Static RAM) DRAM( Dynamic RAM)

第八章

可编程逻辑器件概述

PLD-Programmable

Logic Devices)是一种由 用户根据自己要求来构造逻辑功能的数字集 成电路; 用户构造逻辑功能

1 可编程逻辑器件概述

1970:

PROM结构的PLD 70年代中期: PLA ( Programmable Logic Array ) 70年代末期: AMD公司推出PAL ( Programmable Array Logic )

数据总线

⑶ 写 (1) 地址码101--对应地址5; (2)将要存放的数据放在数据总线上; (3)数据存放在地址5的存储单元, 覆盖原值

地址寄存器 0 11

读操作

0 1 2 3 4 4 5 6 7

1 0 1 1 0 1 1 0 0 0 0 1 0 0 1 0 1 1 0 1 0 0 1 0 0 0 0 1 0 0 1 0 1 1 0 1 0 1 1 1 1 0 0 1 1 1 1 1 1 0 0 0 1 0 1 1

16K=16*1024=16,384=214

存储器的地址和容量

1 2 3 4 5 6 7 8

1 2 3 4 5 6 7 8

每一个小格能够 存储1或0; 可以用行和列来 确定其位置;

1 2 3 4 5 6 7 8

1 2 3 4 5 6 7 8

1 2 3 4 5 6 7 8

1 2 3 4 5 6 7 8

EPROM( Erasable PROM) 存储的数据可以擦除重写

Flash Memory(快闪存储器) 存储容量大、信息不易丢失、在系统读/写、 操作速度快、成本高

三、RAM

RAM( random-access memory ) 任意时候都可以对某一地址进行读/写 操作; 断电后信息后丢失; 分类

5行、4列

3行

存储器的基本操作

写:将数据放入存储器指定的地址; 读:将存储器指定地址的数据拷贝出来;

写: 将数据放入存储器指定的地址; 读: 将存储器指定地址的数据拷贝出来;

数 据 总 线

地 址 输 入

地址 译码

存储 矩阵

读 写

二维存储矩阵

地址寄存器 1 01

数据寄存器

地址译码

0 1 2 3 4 4 5 6 7

目前流行可编程器件的特点

大规模 低功耗 模拟可编程 含多种专用端口和附加功能模块的FPGA

2 PLD器件的基本结构

输入项 乘积项 或项

逻辑可编程

3 PLD的分类

简单可编程逻辑器件(SPLD)

PROM、PLA、PAL、GAL

复杂可编程逻辑器件(CPLD) 现场可编程门阵列(FPGA) 在系统可编程(ISP)逻辑器件

或阵列 固定

等价表达

与阵列 可编程

GAL的原理

和PAL基本一样,差别是:

吸收了浮栅技术,并与CMOS的静态RAM结合,

形成了E2PROM技术,可电擦写、可重复编程。 可设密码; 输出端增加了可编程输出逻辑宏单元(OLMC) 存储单元采用E2CMOS技术,可重复擦写。

GAL器件的问题?

现场可编程门阵列(FPGA)

FPGA是一种可由用户自行定义配置的高密 度专用集成电路; 采用CMOS-SRAM工艺制作,内部由许多独 立的可编程逻辑模块组成;

1.

2. 3. 4.

规模太小 计算器资源太少,不能构成复杂时序电路。 I/O不够灵活,限制了片内资源的利用率。 需要专用编程工具

解决: CPLD的出现

复杂可编程逻辑器件(CPLD)

CPLD为逻辑板块编程,即以逻辑宏单元为 基础,加上内部的与或阵列和外围的输入、 输出模块,不但实现了除简单逻辑控制之外 的时序控制,又扩大了在整个系统中的应用 范围和扩展性。

半导体存储器

存储器的基本知识 ROM RAM

一、存储器的基本知识

二进制数据的单位

bit,Byte,Word

存储器的地址和容量 存储器的基本(位):二进制数据的最小单位 Byte(字节):8-bit Word(字):一个或多个Byte 1024为1K

80年代初 Lattice公司的GAL 80年代中期 Altera公司EPLD(Erasable PLD) Xilinx公司FPGA(Field Progammable Gate Array) 80年代末期,Lattice公司提出在线可编程ISP技 术(In System Programmable)

二、ROM

种类

ROM

掩膜ROM

PROM

EPROM

UV EPROM

E2PROM

Flash Memory

掩模ROM( Mask ROM )

存储的数据是由制作过程中使用的掩模板 决定的;

可编程ROM( Programmable ROM )

PROM采用一种熔丝工艺,出厂时是未写 入程序的,设计人员可以将所需内容自行 写入PROM

写操作

1 0 1 1 0 1 1 0 0 0 0 1 0 0 1 0 1 1 0 1 0 0 1 0 0 0 0 1 0 0 1 0 1 1 0 1 0 1 1 1 1 0 0 1 1 1 1 1 1 0 0 0 1 0 1 1 1 1 1 0 0 1 1 1

10 0 0 1 1 0 1

⑴

地址总线

⑵