CITCAT Constructing Instruction Traces from Cache-filtered Address Traces

计算机系统结构课后习题答案

第1章计算机系统结构的基本概念1.1 解释下列术语层次机构:按照计算机语言从低级到高级的次序,把计算机系统按功能划分成多级层次结构,每一层以一种不同的语言为特征。

这些层次依次为:微程序机器级,传统机器语言机器级,汇编语言机器级,高级语言机器级,应用语言机器级等。

虚拟机:用软件实现的机器。

翻译:先用转换程序把高一级机器上的程序转换为低一级机器上等效的程序,然后再在这低一级机器上运行,实现程序的功能。

解释:对于高一级机器上的程序中的每一条语句或指令,都是转去执行低一级机器上的一段等效程序。

执行完后,再去高一级机器取下一条语句或指令,再进行解释执行,如此反复,直到解释执行完整个程序。

计算机系统结构:传统机器程序员所看到的计算机属性,即概念性结构与功能特性。

在计算机技术中,把这种本来存在的事物或属性,但从某种角度看又好像不存在的概念称为透明性。

计算机组成:计算机系统结构的逻辑实现,包含物理机器级中的数据流和控制流的组成以及逻辑设计等。

计算机实现:计算机组成的物理实现,包括处理机、主存等部件的物理结构,器件的集成度和速度,模块、插件、底板的划分与连接,信号传输,电源、冷却及整机装配技术等。

系统加速比:对系统中某部分进行改进时,改进后系统性能提高的倍数。

Amdahl定律:当对一个系统中的某个部件进行改进后,所能获得的整个系统性能的提高,受限于该部件的执行时间占总执行时间的百分比。

程序的局部性原理:程序执行时所访问的存储器地址不是随机分布的,而是相对地簇聚。

包括时间局部性和空间局部性。

CPI:每条指令执行的平均时钟周期数。

测试程序套件:由各种不同的真实应用程序构成的一组测试程序,用来测试计算机在各个方面的处理性能。

存储程序计算机:冯·诺依曼结构计算机。

其基本点是指令驱动。

程序预先存放在计算机存储器中,机器一旦启动,就能按照程序指定的逻辑顺序执行这些程序,自动完成由程序所描述的处理工作。

系列机:由同一厂家生产的具有相同系统结构、但具有不同组成和实现的一系列不同型号的计算机。

《操作系统概念》第六版作业解答

makes the most efficient use of memory?

First fit

->500288

->600183

->288

->none

initially empty:

a. for int j = 0; j < 100; j++

for int i = 0; i < 100; i++

Aij = 0;

b. for int i = 0; i < 100; i++

for int j = 0; j < 100; j++

Aij = 0;

a. 100x50

of I/O; the process table and page table are updated and

the instruction is restarted.

10-cont.

10.6 Consider the following page-replacement algorithms. Rank

schemes could be used successfully with this hardware?

a. Bare machine

b. Single-user system

c. Multiprogramming with a fixed number of processes

Cortex-M3 权威指南

Cortex-M3权威指南J oseph Yiu 著宋岩译热心网友校对网络版初稿的译序我接触ARM的历史约4年,早期是很欣赏这类处理器,到了后来切身使用它们的机会越来越多,慢慢地有了感觉,也更加喜欢了。

在偶然听说Cortex-M3后,我就冥冥地感到它不寻常。

只是因为其它工作一直没有去了解它,直到今年初才进一步学习,很快就觉得相知恨晚。

当时只能看ARM官方的重量级资料,在看到这本书的英文原稿后,更感觉被电到了一样,于是突然有了把它翻译成中文的冲动。

经过累计约150个小时的奋战,终于有了此译稿。

在翻译过程中,我始终采用下列指导思想:1.尽量使用短句,并且把句子口语化。

我认为高深的道理不一定要用高级的语法句型才能表达。

想想看,即使是几位博士互相聊天讨论一个课题,也还是使用口语吧,而且火花往往就是在这种讨论中产生呢!2.多用修辞方法,并且常常引用表现力强的词汇——甚至包括网络用语和脍炙人口的歌词。

另外,有时会加工句子,使得风格像是对话。

这样做的目的是整个文风更鲜活——有点像为写出高分作文而努力的样子。

这点可能与很多学术著作的“严肃、平实”文风不同,也是一次大胆的尝试。

还希望读者不吝给予反馈。

3.在“宏观”上直译,在“微观”上意译。

英语不仅单一句子的语法和汉语不同,并且句子的连贯方式也与汉语不同。

因此在十几个到几十个单词的范围内,我先把它们翻译成脑子里的“中间语言”,再把中间语言翻译成汉语。

这样,就最大地避免了贻笑大方的“英式汉语”。

4.有些术语名词不方便翻译成汉语,或者目前的翻译方式不统一,或者与其它术语翻译的结果很接近,如error和fault,就只能用英语意会。

此时我就保留英文单词,相信这样比硬生生地翻译成汉语还好。

这些词汇主要是:retarget, fault, region等。

另外,英文中有一个很能精练表达“两者都”意思的单词及其用法:”both”,我也常常保留之。

5.图表对颜色的使用比较丰满,尤其是比较大型的插图,相信这样能帮助读者分析和理解。

memory test 项目介绍

MemTest86 Test AlgorithmsMemTest86 uses two algorithms that provide a reasonable approximation of the ideal test strategy above. The first of these strategies is called moving inversions. The moving inversion test works as follows:1. Fill memory with a pattern2. Starting at the lowest addresso check that the pattern has not changedo write the patterns complemento increment the addresso repeat3. Starting at the highest addresso check that the pattern has not changedo write the patterns complemento decrement the addresso repeatThis algorithm is a good approximation of an ideal memory test but there are some limitations. Most high density chips today store data 4 to 16 bits wide. With chips that are more than one bit wide it is impossible to selectively read or write just one bit. This means that we cannot guarantee that all adjacent cells have been tested for interaction. In this case the best we can do is to use some patterns to insure that all adjacent cells have at least been written with all possible one and zero combinations.It can also be seen that caching, buffering and out of order execution will interfere with the moving inversions algorithm and make less effective. It is possible to turn off cache but the memory buffering in new high performance chips can not be disabled. To address this limitation a new algorithm I call Modulo-X was created. This algorithm is not affected by cache or buffering. The algorithm works as follows:1. For starting offsets of 0 - 20 doo write every 20th location with a patterno write all other locations with the patterns complemento repeat above one or more timeso check every 20th location for the patternThis algorithm accomplishes nearly the same level of adjacency testing as moving inversions but is not affected by caching or buffering. Since separate write passes (1a, 1b) and the read pass (1c) are done for all of memory we can be assured that all of the buffers and cache have been flushedbetween passes. The selection of 20 as the stride size was somewhat arbitrary. Larger strides may be more effective but would take longer to execute. The choice of 20 seemed to be a reasonable compromise between speed and thoroughness.Individual Test DescriptionsMemTest86 executes a series of numbered test sections to check for errors. These test sections consist of a combination of test algorithm, data pattern and cache setting. The execution order for these tests were arranged so that errors will be detected as rapidly as possible. A description of each of the test sections follows:Test 0 [Address test, walking ones, no cache]Tests all address bits in all memory banks by using a walking ones address pattern.Test 1 [Address test, own address, Sequential]Each address is written with its own address and then is checked for consistency. In theory previous tests should have caught any memory addressing problems. This test should catch any addressing errors that somehow were not previously detected. This test is done sequentially with each available CPU.Test 2 [Address test, own address, Parallel]Same as test 1 but the testing is done in parallel using all CPUs and using overlapping addresses. Test 3 [Moving inversions, ones&zeros, Parallel]This test uses the moving inversions algorithm with patterns of all ones and zeros. Cache is enabled even though it interferes to some degree with the test algorithm. With cache enabled this test does not take long and should quickly find all "hard" errors and some more subtle errors. This is done in parallel using all CPUs.Test 4 [Moving inversions, 8 bit pattern]This is the same as test 3 but uses a 8 bit wide pattern of "walking" ones and zeros. This test will better detect subtle errors in "wide" memory chips.Test 5 [Moving inversions, random pattern]Test 5 uses the same algorithm as test 4 but the data pattern is a random number and it's complement. This test is particularly effective in finding difficult to detect data sensitive errors. The random number sequence is different with each pass so multiple passes increase effectiveness.Test 6 [Block move, 64 moves]This test stresses memory by using block move (movsl) instructions and is based on Robert Redelmeier's burnBX test. Memory is initialized with shifting patterns that are inverted every 8 bytes. Then 4mb blocks of memory are moved around using the movsl instruction. After the moves are completed the data patterns are checked. Because the data is checked only after the memory moves are completed it is not possible to know where the error occurred. The addresses reported are only for where the bad pattern was found. Since the moves are constrained to a 8mb segment of memory the failing address will always be less than 8mb away from the reported address. Errors from this test are not used to calculate BadRAM patterns.Test 7 [Moving inversions, 32 bit pattern]This is a variation of the moving inversions algorithm that shifts the data pattern left one bit for each successive address. The starting bit position is shifted left for each pass. To use all possible data patterns 32 passes are required. This test is quite effective at detecting data sensitive errors but the execution time is long.Test 8 [Random number sequence]This test writes a series of random numbers into memory. By resetting the seed for the random number the same sequence of number can be created for a reference. The initial pattern is checked and then complemented and checked again on the next pass. However, unlike the moving inversions test writing and checking can only be done in the forward direction.Test 9 [Modulo 20, Random pattern]Using the Modulo-X algorithm should uncover errors that are not detected by moving inversions due to cache and buffering interference with the algorithm.Test 10 [Bit fade test, 2 patterns]The bit fade test initializes all of memory with a pattern and then sleeps for a few minutes. Then memory is examined to see if any memory bits have changed. All ones and all zero patterns are used.Test 11 [Random number sequence, 64-bit]This test is the same as Test 8, but native 64-bit instructions are used.Test 12 [Random number sequence, 128-bit]This test is the same as Test 8, but native SIMD (128-bit) instructions are used.Test 13 [Hammer Test]The row hammer test exposes a fundamental defect with RAM modules 2010 or later. This defect can lead to disturbance errors when repeatedly accessing addresses in the same memory bank but different rows in a short period of time. The repeated opening/closing of rows causes charge leakage in adjacent rows, potentially causing bits to flip.This test 'hammers' rows by alternatively reading two addresses in a repeated fashion, then verifying the contents of other addresses for disturbance errors. For more details on DRAM disturbance errors, see Flipping Bits in Memory Without Accessing Them: An Experimental Study of DRAM Disturbance Errors by Yoongu Kim et al.Starting from MemTest86 v6.2, potentially two passes of row hammer testing are performed. On the first pass, address pairs are hammered at the highest possible rate. If errors are detected on the first pass, errors are not immediately reported and a second pass is started. In this pass, address pairs are hammered at a lower rate deemed as the worst case scenario by memory vendors (200K accesses per 64ms). If errors are also detected in this pass, the errors are reported to the user as normal. However, if only the first pass produces an error, a warning message is instead displayed to the user.。

address sanitizer 参数

Address Sanitizer(简称ASan 或AddressSanitizer)是一个用于检测内存错误的开源工具,主要包括以下几种参数:1. --address-sanitizer:启用AddressSanitizer 功能。

2. --no-address-sanitizer:禁用AddressSanitizer 功能。

3. --address-sanitizer-coverage:启用AddressSanitizer 覆盖率报告。

4. --no-address-sanitizer-coverage:禁用AddressSanitizer 覆盖率报告。

5. --address-sanitizer-verify:启用AddressSanitizer 验证模式,该模式会检查程序中的内存访问是否符合预期。

6. --no-address-sanitizer-verify:禁用AddressSanitizer 验证模式。

7. --address-sanitizer-detect-leaks:启用AddressSanitizer 泄漏检测功能。

8. --no-address-sanitizer-detect-leaks:禁用AddressSanitizer 泄漏检测功能。

9. --address-sanitizer- conservative:启用AddressSanitizer 保守模式,该模式会降低误报率,但可能导致检测速度较慢。

10. --no-address-sanitizer-conservative:禁用AddressSanitizer 保守模式。

11. --address-sanitizer-log-path:指定AddressSanitizer 日志文件的路径。

12. --no-address-sanitizer-log-path:指定不生成AddressSanitizer 日志文件。

13. --address-sanitizer-symbol-prefix:设置AddressSanitizer 符号前缀,用于标识检测到的内存错误。

计算机系统结构(第2版(课后习题答案

word 文档下载后可自由复制编辑你计算机系统结构清华第 2 版习题解答word 文档下载后可自由复制编辑1 目录1.1 第一章(P33)1.7-1.9 (透明性概念),1.12-1.18 (Amdahl定律),1.19、1.21 、1.24 (CPI/MIPS)1.2 第二章(P124)2.3 、2.5 、2.6 (浮点数性能),2.13 、2.15 (指令编码)1.3 第三章(P202)3.3 (存储层次性能), 3.5 (并行主存系统),3.15-3.15 加 1 题(堆栈模拟),3.19 中(3)(4)(6)(8)问(地址映象/ 替换算法-- 实存状况图)word 文档下载后可自由复制编辑1.4 第四章(P250)4.5 (中断屏蔽字表/中断过程示意图),4.8 (通道流量计算/通道时间图)1.5 第五章(P343)5.9 (流水线性能/ 时空图),5.15 (2种调度算法)1.6 第六章(P391)6.6 (向量流水时间计算),6.10 (Amdahl定律/MFLOPS)1.7 第七章(P446)7.3 、7.29(互连函数计算),7.6-7.14 (互连网性质),7.4 、7.5 、7.26(多级网寻径算法),word 文档下载后可自由复制编辑7.27 (寻径/ 选播算法)1.8 第八章(P498)8.12 ( SISD/SIMD 算法)1.9 第九章(P562)9.18 ( SISD/多功能部件/SIMD/MIMD 算法)(注:每章可选1-2 个主要知识点,每个知识点可只选 1 题。

有下划线者为推荐的主要知识点。

)word 文档 下载后可自由复制编辑2 例 , 习题2.1 第一章 (P33)例 1.1,p10假设将某系统的某一部件的处理速度加快到 10倍 ,但该部件的原处理时间仅为整个运行时间的40%,则采用加快措施后能使整个系统的性能提高多少?解:由题意可知: Fe=0.4, Se=10,根据 Amdahl 定律S n To T n1 (1Fe )S n 1 10.6 0.4100.64 Fe Se 1.56word 文档 下载后可自由复制编辑例 1.2,p10采用哪种实现技术来求浮点数平方根 FPSQR 的操作对系统的性能影响较大。

MBIST_TsingHua课件讲义

Memory Cell Array

Y Decoder

• •

Transparent Serial Data-MUX

c c

SO

D

Q

Source: Nadeau-Dostie et al., IEEE D&T, Apr. 1990

m05bist5.04

Cheng-Wen Wu, NTHU

m05bist5.04

Cheng-Wen Wu, NTHU

14

Typical RAM BIST Approaches

• Methodology

− Processor-based BIST ∗ Programmable − Hardwired BIST ∗ Fast ∗ Compact − Hybrid

38,180 39,844

49,396 143,668 631,222 77.3 27.7 13

m05bist5.04

Cheng-Wen Wu, NTHU

9

Exercise

1. If the word length is 16, how do you design the signature analyzer based on 24-bit MISR? 2. If the word length is 40, how do you design the signature analyzer based on 24-bit MISR? 3. How do you perform diagnosis under the MISRbased ROM BIST scheme? Do you have a better ROM BIST approach so far as diagnosis is concerned? 4. How do you deal with multiple heterogeneous ROM cores (considering test time and hardware cost)? 5. How do you perform diagnosis under the BIST scheme?

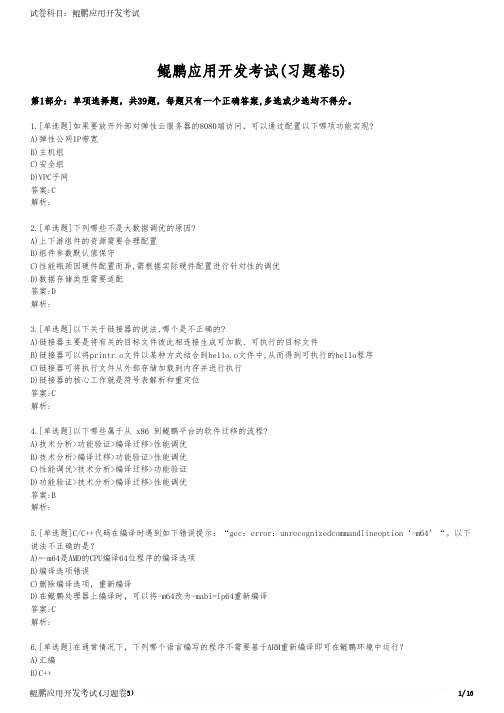

鲲鹏应用开发考试(习题卷5)

鲲鹏应用开发考试(习题卷5)第1部分:单项选择题,共39题,每题只有一个正确答案,多选或少选均不得分。

1.[单选题]如果要放开外部对弹性云服务器的8080端访问,可以通过配置以下哪项功能实现?A)弹性公网IP带宽B)主机组C)安全组D)VPC子网答案:C解析:2.[单选题]下列哪些不是大数据调优的原因?A)上下游组件的资源需要合理配置B)组件参数默认值保守C)性能瓶颈因硬件配置而异,需根据实际硬件配置进行针对性的调优D)数据存储类型需要适配答案:D解析:3.[单选题]以下关于链接器的说法,哪个是不正确的?A)链接器主要是将有关的目标文件彼此相连接生成可加载、可执行的目标文件B)链接器可以将printr.o文件以某种方式结合到he11o.o文件中,从而得到可执行的he11o程序C)链接器可将执行文件从外部存储加载到内存并进行执行D)链接器的核心工作就是符号表解析和重定位答案:C解析:4.[单选题]以下哪些属于从 x86 到鲲鹏平台的软件迁移的流程?A)技术分析>功能验证>编译迁移>性能调优B)技术分析>编译迁移>功能验证>性能调优C)性能调优>技术分析>编译迁移>功能验证D)功能验证>技术分析>编译迁移>性能调优答案:B解析:5.[单选题]C/C++代码在编译时遇到如下错误提示:“gcc:error:unrecognizedcommandlineoption‘-m64’“。

以下说法不正确的是?A)=-m64是AMD的CPU编译64位程序的编译选项B)编译选项错误C)删除编译选项,重新编译D)在鲲鹏处理器上编译时,可以将-m64改为-mabi=lp64重新编译答案:C解析:6.[单选题]在通常情况下,下列哪个语言编写的程序不需要基于ARM重新编译即可在鲲鹏环境中运行?A)汇编B)C++答案:D解析:7.[单选题]CLI 方式进行代码分析,那些参数是必须选择的()A)sourceB)compilerC)toolsD)tk答案:A解析:8.[单选题]rpmbuild工具的作用是什么?A)构建源码工程B)生成rpm源码文件C)构建rpm包D)发布rpm源码包答案:C解析:9.[单选题]NUMA-Aware亲和性资源优化主要是为了?A)减少网卡中断B)减少磁盘1/0C)减少内存使用量D)减少内存访问时延答案:D解析:10.[单选题]Suse 操作系统是从哪个版本开始处于 Kunpeng 920 的 OS 生态圈?A)SLES 12.3B)SLES 12.4C)SLES 15D)SLES 15.1答案:D解析:11.[单选题]在使用man查看一个命令的帮助信息时,下列说法正确的是?A)在命令使用格式中, . . .表示的是同类内容可以有多个B)在命令使用格式中,< >表示的是可选内容C)通常情况下,--help比man查看的命令帮助信息更多D)在命令使用格式中,[]表示的是必选内容答案:A解析:12.[单选题]列选项中, 哪项不是华为云提供的鲲鹏云服务?A)鲲鹏容器服务B)鲲鹏SQL server 服务C)鲲鹏应用运维服务D)鲲鹏云硬盘服务答案:B13.[单选题]如下哪项功能不是态势感知服务提供的?A)威胁告警实时监控B)安全风险分析C)安全事件自动化处理D)态势大屏呈现答案:C解析:14.[单选题]以下哪项不属于NUNA架构的特点?A)非统一内存访问B)不同的核访问不同内存的时间不同C)内存在物理上是分布式的D)每个核都是对等的,所有的核通过总线访问所有内存答案:D解析:15.[单选题]在鲲鹏平台中进行编译时,定义编译生成的应用程序为 64 位使用的参数是什么?A)-m32B)-mabi=1p64C)-mabi=1p32D)-m64答案:B解析:16.[单选题]以下哪个方法不属于 CPU/内存调优手段?A)调整内存大小B)开启或关闭 CPU 预取C)修改文件系统参数D)减少跨 NUMA 访问内存答案:C解析:17.[单选题]谁是Linux之父?A)Linus TorvaldsB)Richard MatthewC)Sta11manBi11 GatesD)Andrew Morton答案:A解析:18.[单选题]在CentOS系统中,以下哪个命令可以用于安装软件包?A)yumupgradeB)apt-getinstallC)yuminstallD)apt-getupgrade答案:C解析:19.[单选题]由C语言开发的hel1o.c,从源码到可执行程序过程中需要进行一系列转换,各个阶段都有输出,下列输出文件哪个是二进制?A)hello.pyB)hello.iC)he11o.oD)hello.s答案:C解析:20.[单选题]于 numastat命令的回显信息描述中,错误的是哪一项?A)numa_miss的值应当越低越好B)node指的是 CPU coreC)muma_hit表示节点内CPU核访间本地内存的次数D)numa_miss表示节点内核访问其他节点内存的次数答案:B解析:在NUMA架构中,每一颗CPU被称为一个node,每个node之间的内存使用的独立的。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

CONSTRUCTING INSTRUCTION TRACES

fromCACHE-FILTERED ADDRESS TRACES (CITCAT)

Charlton D. RoseJ. Kelly Flanagansharky@byu.edukelly@cs.byu.edu

Performance Evaluation Laboratoryhttp://pel.cs.byu.eduDepartment of Computer ScienceBrigham Young University

AbstractInstruction traces are useful tools for studying manyaspects of computer systems, but they are difficult togather without perturbing the systems being traced.In the past, researchers have collected instructiontraces through various techniques, including single-stepping, instruction inlining, hardware monitoring,and processor simulation. These approaches,however, fail to produce accurate traces becausethey interfere with the processor’s normal execution.

Because processors are deterministic machines,hypothetical components to real-world demands,their behavior can be predicted if their initial statesand external inputs are known. We have developeda technique, called “CITCAT,” which exploits thisfact to generate nearly perfect instruction tracesthrough trace-driven simulation. CITCAT combinesthe best features of instruction inlining, hardwaremonitoring, and processor simulation to producelong, accurate instruction traces without perturbingthe system being traced. Because CITCATinstruction traces are computed, rather than stored,this hybrid technique delivers not just accuratetraces, but also an extremely efficient tracecompression algorithm.

1.introduction

When studying a component of a computersystem in order to see how it can be improved, itis often useful to make the system perform aspecific task while recording the activities of thecomponent. If the recorded data, called a“trace,” contains enough information to

reproduce the component’s behavior in asoftware-based simulator, then that same datacan also be used to simulate the activities ofcomponents which are functionally identical butimplemented differently.Using trace data to subject a simulatedcomponent to the same sequence of demandsexperienced by a real component is called “trace-driven simulation.” Because trace-drivensimulation makes it possible to subject

it is an extremely useful tool for evaluatingchanges to systems before they are implemented.Computer systems have many traceablecomponents, but one of the most interesting andworthwhile components to trace is the CPU. Aninstruction trace enables researchers to modeland study many aspects of computer systems.For example, processor-internal caches can besimulated, instruction-level parallelism measured,branch prediction algorithms tested, and dynamicinstruction counts generated. Completeinstruction traces also contain enough data toconstruct additional traces, such as memoryactivity and disk I/O traces.In this paper, we will review severaltraditional methods that researchers have used tocollect instruction traces. We will describeseveral problems associated with these methodsand explain why they have failed, in our opinion,to produce perfect instruction traces.We will then describe CITCAT, a techniqueinterrupts can be used to follow — and hencethrough which three of these traditionalrecord — the processor’s instruction execution.approaches, instruction inlining, hardwareWhen these interrupts occur, the interruptmonitoring, and processor simulation, can behandler records information about thecombined to construct nearly perfect instructioninstructions being executed and then returnstraces. After discussing the pros and cons of ourprocessor control to the point where thehybrid approach, we will conclude with aexception was raised.statement about past success, work in progress,This strategy is useful for generating user-and future research goals related to thiscode instruction traces, but it has severaltechnique.significant limitations. First of all, the overhead

2.traditional instruction trace-gathering techniques

Ironically, one of the most useful traces of acomputer system to have is also one of the mostdifficult to collect. Many researchers arefrustrated by the fact that if you disturb acomputer system in order to measure it, thevalidity of the measurements becomes uncertainbecause they are taken from a perturbed system.This problem is especially prominent when itcomes to gathering perfect instruction traces.We define a perfect instruction trace as acontinuous record of CPU instruction execution,including operating system code and contextswitches, that has been gathered from anunperturbed system and is long enough to bestatistically useful. Although many techniqueshave been attempted, including single-stepping,instruction inlining, hardware monitoring, andprocessor simulation, all of these approacheshave fallen short of producing perfect instructiontraces. They were either too difficult toimplement correctly or caused unacceptableperturbations in the system being measured.