IDT72T1875L6-7BBI中文资料

ATTINY28L-4PC,ATTINY28L-4PI,ATTINY28L-4AC,ATTINY28L-4AU,ATTINY28L-4AI,规格书,Datasheet 资料

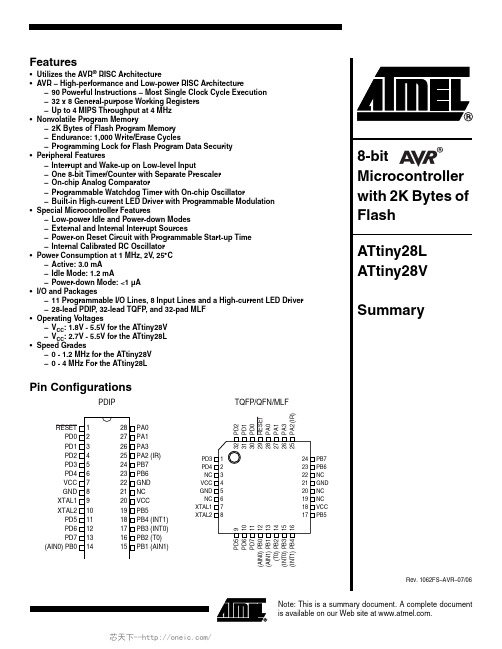

1Features•Utilizes the AVR ® RISC Architecture•AVR – High-performance and Low-power RISC Architecture–90 Powerful Instructions – Most Single Clock Cycle Execution –32 x 8 General-purpose Working Registers –Up to 4 MIPS Throughput at 4 MHz •Nonvolatile Program Memory–2K Bytes of Flash Program Memory –Endurance: 1,000 Write/Erase Cycles–Programming Lock for Flash Program Data Security •Peripheral Features–Interrupt and Wake-up on Low-level Input–One 8-bit Timer/Counter with Separate Prescaler –On-chip Analog Comparator–Programmable Watchdog Timer with On-chip Oscillator–Built-in High-current LED Driver with Programmable Modulation •Special Microcontroller Features–Low-power Idle and Power-down Modes –External and Internal Interrupt Sources–Power-on Reset Circuit with Programmable Start-up Time –Internal Calibrated RC Oscillator •Power Consumption at 1 MHz, 2V , 25°C –Active: 3.0 mA –Idle Mode: 1.2 mA–Power-down Mode: <1 µA •I/O and Packages–11 Programmable I/O Lines, 8 Input Lines and a High-current LED Driver –28-lead PDIP , 32-lead TQFP , and 32-pad MLF •Operating Voltages–V CC : 1.8V - 5.5V for the ATtiny28V –V CC : 2.7V - 5.5V for the ATtiny28L •Speed Grades–0 - 1.2 MHz for the ATtiny28V –0 - 4 MHz For the ATtiny28LPin ConfigurationsPDIPTQFP/QFN/MLF8-bit Microcontroller with 2K Bytes of ATtiny28L ATtiny28V SummaryNote: This is a summary document. A complete documentis available on our Web site at .2ATtiny28L/V1062FS–AVR–07/06DescriptionThe ATtiny28 is a low-power CMOS 8-bit microcontroller based on the AVR RISC archi-tecture. By executing powerful instructions in a single clock cycle, the ATtiny28 achieves throughputs approaching 1 MIPS per MHz, allowing the system designer to optimize power consumption versus processing speed. The AVR core combines a rich instruction set with 32 general-purpose working registers. All the 32 registers are directly con-nected to the Arithmetic Logic Unit (ALU), allowing two independent registers to be accessed in one single instruction executed in one clock cycle. The resulting architec-ture is more code efficient while achieving throughputs up to ten times faster than conventional CISC microcontrollers.Block DiagramFigure 1. The ATtiny28 Block DiagramThe ATtiny28 provides the following features: 2K bytes of Flash, 11 general-purpose I/O lines, 8 input lines, a high-current LED driver, 32 general-purpose working registers, an 8-bit timer/counter, internal and external interrupts, programmable Watchdog Timer with internal oscillator and 2 software-selectable power-saving modes. The Idle Mode stops the CPU while allowing the timer/counter and interrupt system to continue functioning.The Power-down mode saves the register contents but freezes the oscillator, disabling all other chip functions until the next interrupt or hardware reset. The wake-up or inter-3ATtiny28L/V1062FS–AVR–07/06rupt on low-level input feature enables the ATtiny28 to be highly responsive to external events, still featuring the lowest power consumption while in the power-down modes.The device is manufactured using Atmel’s high-density, nonvolatile memory technology.By combining an enhanced RISC 8-bit CPU with Flash on a monolithic chip, the Atmel ATtiny28 is a powerful microcontroller that provides a highly flexible and cost-effective solution to many embedded control applications. The ATtiny28 AVR is supported with a full suite of program and system development tools including: macro assemblers, pro-gram debugger/simulators, in-circuit emulators and evaluation kits.Pin DescriptionsVCC Supply voltage pin.GNDGround pin.Port A (PA3..PA0)Port A is a 4-bit I/O port. PA2 is output-only and can be used as a high-current LED driver. At V CC = 2.0V, the PA2 output buffer can sink 25 mA. PA3, PA1 and PA0 are bi-directional I/O pins with internal pull-ups (selected for each bit). The port pins are tri-stated when a reset condition becomes active, even if the clock is not running.Port B (PB7..PB0)Port B is an 8-bit input port with internal pull-ups (selected for all Port B pins). Port B pins that are externally pulled low will source current if the pull-ups are activated.Port B also serves the functions of various special features of the ATtiny28 as listed on page 27. If any of the special features are enabled, the pull-up(s) on the corresponding pin(s) is automatically disabled. The port pins are tri-stated when a reset condition becomes active, even if the clock is not running.Port D (PD7..PD0)Port D is an 8-bit I/O port. Port pins can provide internal pull-up resistors (selected for each bit). The port pins are tri-stated when a reset condition becomes active, even if the clock is not running.XTAL1Input to the inverting oscillator amplifier and input to the internal clock operating circuit.XTAL2Output from the inverting oscillator amplifier.pulses longer than 50 ns will generate a reset, even if the clock is not running. Shorter pulses are not guaranteed to generate a reset.4ATtiny28L/V1062FS–AVR–07/06Notes:1.For compatibility with future devices, reserved bits should be written to zero if accessed. Reserved I/O memory addressesshould never be written.2.Some of the status flags are cleared by writing a logical “1” to them. Note that the CBI and SBI instructions will operate on allbits in the I/O register, writing a one back into any flag read as set, thus clearing the flag. The CBI and SBI instructions work with registers $00 to $1F only.Register SummaryAddressNameBit 7Bit 6Bit 5Bit 4Bit 3Bit 2Bit 1Bit 0Page$3F SREG ITHSVNZCpage 6$3E Reserved ...Reserved $20Reserved $1F Reserved $1E Reserved $1D Reserved $1C Reserved $1B PORTA ----PORTA3PORTA2PORTA1PORTA0page 32$1A PACR ----DDA3PA2HCDDA1DDA0page 32$19PINA ----PINA3-PINA1PINA0page 32$18Reserved $17Reserved $16PINB PINB7PINB6PINB5PINB4PINB3PINB2PINB1PINB0page 32$15Reserved $14Reserved $13Reserved $12PORTD PORTD7PORTD6PORTD5PORTD4PORTD3PORTD2PORTD1PORTD0page 33$11DDRD DDD7DDD6DDD5DDD4DDD3DDD2DDD1DDD0page 33$10PIND PIND7PIND6PIND5PIND4PIND3PIND2PIND1PIND0page 33$0F Reserved $0E Reserved $0D Reserved $0C Reserved $0B Reserved $0A Reserved $09Reserved $08ACSR ACD -ACO ACI ACIE -ACIS1ACIS0page 44$07MCUCS PLUPB -SE SM WDRF -EXTRF PORF page 19$06ICR INT1INT0LLIE TOIE0ISC11ISC10ISC01ISC00page 22$05IFR INTF1INTF0-TOV0----page 23$04TCCR0FOV0--OOM01OOM00CS02CS01CS00page 35$03TCNT0Timer/Counter0 (8-bit)page 36$02MODCR ONTIM4ONTIM3ONTIM2ONTIM1 ONTIM0MCONF2MCONF1MCONF0page 43$01WDTCR ---WDTOEWDEWDP2WDP1WDP0page 37$00OSCCALOscillator Calibration Registerpage 95ATtiny28L/V1062FS–AVR–07/06Instruction Set SummaryMnemonicOperandsDescriptionOperationFlags# ClocksARITHMETIC AND LOGIC INSTRUCTIONSADD Rd, Rr Add Two RegistersRd ← Rd + Rr Z,C,N,V,H 1ADC Rd, Rr Add with Carry Two Registers Rd ← Rd + Rr + C Z,C,N,V,H 1SUB Rd, Rr Subtract Two Registers Rd ← Rd - Rr Z,C,N,V,H 1SUBI Rd, K Subtract Constant from Register Rd ← Rd - K Z,C,N,V,H 1SBC Rd, Rr Subtract with Carry Two Registers Rd ← Rd - Rr - C Z,C,N,V,H 1SBCI Rd, K Subtract with Carry Constant from Reg.Rd ← Rd - K - C Z,C,N,V,H 1AND Rd, Rr Logical AND RegistersRd ← Rd • Rr Z,N,V 1ANDI Rd, K Logical AND Register and Constant Rd ← Rd • K Z,N,V 1OR Rd, Rr Logical OR RegistersRd ← Rd v Rr Z,N,V 1ORI Rd, K Logical OR Register and Constant Rd ← Rd v K Z,N,V 1EOR Rd, Rr Exclusive OR Registers Rd ← Rd ⊕ Rr Z,N,V 1COM Rd One’s Complement Rd ← $FF - Rd Z,C,N,V 1NEG Rd Two’s Complement Rd ← $00 - Rd Z,C,N,V,H 1SBR Rd, K Set Bit(s) in Register Rd ← Rd v K Z,N,V 1CBR Rd, K Clear Bit(s) in Register Rd ← Rd • (FFh - K)Z,N,V 1INC Rd Increment Rd ← Rd + 1Z,N,V 1DEC Rd DecrementRd ← Rd - 1 Z,N,V 1TST Rd Test for Zero or Minus Rd ← Rd • Rd Z,N,V1CLR Rd Clear Register Rd ← Rd ⊕ Rd Z,N,V 1SER Rd Set Register Rd ← $FF None 1BRANCH INSTRUCTIONSRJMP k Relative JumpPC ← PC + k + 1None 2RCALL kRelative Subroutine Call PC ← PC + k + 1None 3RET Subroutine Return PC ← STACK None 4RETI Interrupt Return PC ← STACKI 4CPSE Rd, Rr Compare, Skip if Equal if (Rd = Rr) PC ← PC + 2 or 3None 1/2CP Rd, Rr CompareRd - Rr Z,N,V,C,H 1CPC Rd, Rr Compare with CarryRd - Rr - C Z,N,V,C,H 1CPI Rd, K Compare Register with Immediate Rd - KZ N,V,C,H 1SBRC Rr, b Skip if Bit in Register Cleared if (Rr(b) = 0) PC ← PC + 2 or 3None 1/2SBRS Rr, b Skip if Bit in Register is Set if (Rr(b) = 1) PC ← PC + 2 or 3None 1/2SBIC P, b Skip if Bit in I/O Register Cleared if (P(b) = 0) PC ← PC + 2 or 3None 1/2SBIS P, b Skip if Bit in I/O Register is Set if (P(b) = 1) PC ← PC + 2 or 3None 1/2BRBS s, k Branch if Status Flag Set if (SREG(s) = 1) then PC ← PC + k + 1None 1/2BRBC s, k Branch if Status Flag Cleared if (SREG(s) = 0) then PC ← PC + k + 1None 1/2BREQ k Branch if Equal if (Z = 1) then PC ← PC + k + 1None 1/2BRNE k Branch if Not Equal if (Z = 0) then PC ← PC + k + 1None 1/2BRCS k Branch if Carry Set if (C = 1) then PC ← PC + k + 1None 1/2BRCC k Branch if Carry Cleared if (C = 0) then PC ← PC + k + 1None 1/2BRSH k Branch if Same or Higher if (C = 0) then PC ← PC + k + 1None 1/2BRLO k Branch if Lower if (C = 1) then PC ← PC + k + 1None 1/2BRMI k Branch if Minus if (N = 1) then PC ← PC + k + 1None 1/2BRPL k Branch if Plusif (N = 0) then PC ← PC + k + 1None 1/2BRGE k Branch if Greater or Equal, Signed if (N ⊕ V = 0) then PC ← PC + k + 1None 1/2BRLT k Branch if Less than Zero, Signed if (N ⊕ V = 1) then PC ← PC + k + 1None 1/2BRHS k Branch if Half-carry Flag Set if (H = 1) then PC ← PC + k + 1None 1/2BRHC k Branch if Half-carry Flag Cleared if (H = 0) then PC ← PC + k + 1None 1/2BRTS k Branch if T-flag Set if (T = 1) then PC ← PC + k + 1None 1/2BRTC k Branch if T-flag Cleared if (T = 0) then PC ← PC + k + 1None 1/2BRVS k Branch if Overflow Flag is Set if (V = 1) then PC ← PC + k + 1None 1/2BRVC k Branch if Overflow Flag is Cleared if (V = 0) then PC ← PC + k + 1None 1/2BRIE k Branch if Interrupt Enabled if (I = 1) then PC ← PC + k + 1None 1/2BRIDkBranch if Interrupt Disabledif (I = 0) then PC ← PC + k + 1None1/26ATtiny28L/V1062FS–AVR–07/06DATA TRANSFER INSTRUCTIONSLD Rd, Z Load Register Indirect Rd ← (Z)None 2ST Z, Rr Store Register Indirect (Z) ← Rr None 2MOV Rd, Rr Move between Registers Rd ← Rr None 1LDI Rd, K Load Immediate Rd ←K None 1IN Rd, P In Port Rd ← P None 1OUT P, RrOut PortP ← Rr None 1LPMLoad Program MemoryR0 ← (Z)None3BIT AND BIT-TEST INSTRUCTIONS SBI P, b Set Bit in I/O Register I/O(P,b) ← 1None 2CBI P, b Clear Bit in I/O Register I/O(P,b) ←None 2LSL Rd Logical Shift LeftRd(n+1) ← Rd(n), Rd(0) ← 0Z,C,N,V 1LSR Rd Logical Shift Right Rd(n) ← Rd(n+1), Rd(7) ← 0Z,C,N,V 1ROL Rd Rotate Left through Carry Rd(0) ← C, Rd(n+1) ← Rd(n), C ← Rd(7)Z,C,N,V 1ROR Rd Rotate Right through Carry Rd(7) ← C, Rd(n) ← Rd(n+1), C ← Rd(0)Z,C,N,V 1ASR Rd Arithmetic Shift Right Rd(n) ← Rd(n+1), n = 0..6Z,C,N,V 1SWAP Rd Swap Nibbles Rd(3..0) ← Rd(7..4), Rd(7..4) ← Rd(3..0)None 1BSET s Flag Set SREG(s) ← 1SREG(s)1BCLR s Flag Clear SREG(s) ← 0SREG(s)1BST Rr, b Bit Store from Register to T T ← Rr(b)T 1BLD Rd, bBit Load from T to Register Rd(b) ← T None 1SEC Set Carry C ← 1C 1CLC Clear Carry C ←0C 1SEN Set Negative Flag N ← 1N 1CLN Clear Negative Flag N ← 0N 1SEZ Set Zero Flag Z ←1Z 1CLZ Clear Zero Flag Z ← 0Z1SEI Global Interrupt Enable I ← 1I 1CLI Global Interrupt Disable I ←I 1SES Set Signed Test FlagS ← 1S 1CLS Clear Signed Test Flag S ←0S 1SEV Set Two’s Complement OverflowV ←1V 1CLV Clear Two’s Complement Overflow V ← 0V 1SET Set T in SREG T ← 1T 1CLT Clear T in SREG T ← 0T 1SEH Set Half-carry Flag in SREG H ← 1H 1CLH Clear Half-carry Flag in SREG H ←H 1NOP No Operation None 1SLEEP Sleep(see specific descr. for Sleep function)None 1WDRWatchdog Reset(see specific descr. for WDR/timer)None1Instruction Set Summary (Continued)MnemonicOperandsDescriptionOperationFlags# Clocks7ATtiny28L/V1062FS–AVR–07/06Notes:1.This device can also be supplied in wafer form. Please contact your local Atmel sales office for detailed ordering informationand minimum quantities.2.Pb-free packaging alternative, complies to the European Directive for Restriction of Hazardous Substances (RoHS direc-tive).Also Halide free and fully Green.Ordering InformationSpeed (MHz)Power Supply (Volts)Ordering Code Package (1)Operation Range 42.7 - 5.5A Ttiny28L-4AC A Ttiny28L-4PC A Ttiny28L-4MC32A 28P332M1-A Commercial (0°C to 70°C)A Ttiny28L-4AI A Ttiny28L-4AU (2)A Ttiny28L-4PI A Ttiny28L-4PU (2)A Ttiny28L-4MI A Ttiny28L-4MU (2)32A 32A 28P328P332M1-A 32M1-A Industrial (-40°C to 85°C)1.21.8 - 5.5A Ttiny28V-1AC A Ttiny28V-1PC A Ttiny28V-1MC32A 28P332M1-A Commercial (0°C to 70°C)A Ttiny28V-1AI A Ttiny28V-1AU (2)A Ttiny28V-1PI A Ttiny28V-1PU (2)A Ttiny28V-1MI A Ttiny28V-1MU (2)32A 32A 28P328P332M1-A 32M1-AIndustrial (-40°C to 85°C)Package Type32A 32-lead, Thin (1.0 mm) Plastic Quad Flat Package (TQFP)28P328-lead, 0.300" Wide, Plastic Dual Inline Package (PDIP)32M1-A32-pad, 5x5x1.0 body, Lead Pitch 0.50mm, Quad Flat No-lead/Micro Lead Frame Package (QFN/MLF)8ATtiny28L/V1062FS–AVR–07/06Packaging Information32A9ATtiny28L/V1062FS–AVR–07/0628P310ATtiny28L/V1062FS–AVR–07/0632M1-A11ATtiny28L/V1062FS–AVR–07/06ErrataAll revisionsNo known errata.12ATtiny28L/V1062FS–AVR–07/06Datasheet Revision HistoryPlease note that the referring page numbers in this section are referred to this docu-ment. The referring revision in this section are referring to the document revision.Rev – 01/06G 1.Updated chapter layout.2.Updated “Ordering Information” on page 7.Rev – 01/06G1.Updated description for “Port A” on page 25.2.Added note 6 in “DC Characteristics” on page 54.3.Updated “Ordering Information” on page 7.4.Added “Errata” on page 11.Rev – 03/05F1.Updated “Electrical Characteristics” on page 54.2.MLF-package alternative changed to “Quad Flat No-Lead/Micro Lead Frame PackageQFN/MLF”.3.Updated “Ordering Information” on page 7.1062FS–AVR–07/06© 2006 Atmel Corporation . All rights reserved. ATMEL ®, logo and combinations thereof, Everywhere You Are ®, AVR ®, AVR Studio ®, and oth-ers, are registered trademarks or trademarks of Atmel Corporation or its subsidiaries. Other terms and product names may be trademarks of oth-ers.Disclaimer: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise,to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN ATMEL’S TERMS AND CONDI-TIONS OF SALE LOCATED ON ATMEL’S WEB SITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDEN-TAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS OF PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABIL ITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBIL ITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and product descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically provided otherwise, Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel’s products are not intended, authorized, or warranted for use as components in applications intended to support or sustain life.Atmel CorporationAtmel Operations2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311Fax: 1(408) 487-2600Regional HeadquartersEuropeAtmel SarlRoute des Arsenaux 41Case Postale 80CH-1705 Fribourg SwitzerlandTel: (41) 26-426-5555Fax: (41) 26-426-5500AsiaRoom 1219Chinachem Golden Plaza 77 Mody Road Tsimshatsui East Kowloon Hong KongTel: (852) 2721-9778Fax: (852) 2722-1369Japan9F, Tonetsu Shinkawa Bldg.1-24-8 ShinkawaChuo-ku, Tokyo 104-0033JapanTel: (81) 3-3523-3551Fax: (81) 3-3523-7581Memory2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311Fax: 1(408) 436-4314Microcontrollers2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311Fax: 1(408) 436-4314La Chantrerie BP 7060244306 Nantes Cedex 3, France Tel: (33) 2-40-18-18-18Fax: (33) 2-40-18-19-60ASIC/ASSP/Smart CardsZone Industrielle13106 Rousset Cedex, France Tel: (33) 4-42-53-60-00Fax: (33) 4-42-53-60-011150 East Cheyenne Mtn. Blvd.Colorado Springs, CO 80906, USA Tel: 1(719) 576-3300Fax: 1(719) 540-1759Scottish Enterprise Technology Park Maxwell BuildingEast Kilbride G75 0QR, Scotland Tel: (44) 1355-803-000Fax: (44) 1355-242-743RF/AutomotiveTheresienstrasse 2Postfach 353574025 Heilbronn, Germany Tel: (49) 71-31-67-0Fax: (49) 71-31-67-23401150 East Cheyenne Mtn. Blvd.Colorado Springs, CO 80906, USA Tel: 1(719) 576-3300Fax: 1(719) 540-1759Biometrics/Imaging/Hi-Rel MPU/High Speed Converters/RF DatacomAvenue de Rochepleine BP 12338521 Saint-Egreve Cedex, France Tel: (33) 4-76-58-30-00Fax: (33) 4-76-58-34-80Literature Requests/literature。

T73227中文资料

T73227

27 MHz VCXO Clock Generator IC

October 2002

1.0 Features

• One-chip tunable voltage controlled crystal oscillator (VCXO) allows precise system frequency tuning

150 100

Deviation From 27 MHz ppm

where CL1 and CL2 are the two extremes of the applied load capacitance.

50

EXAMPLE: A crystal with the following parameters is

Vin

5.0 Electrical Specifications

Table 2: Absolute Maximum Ratings

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. These conditions represent a stress rating only, and functional operation of the device at these or any other conditions above the operational limits noted in this specification is not implied. Exposure to maximum rating conditions for extended conditions may affect device performance, functionality, and reliability.

proteusisis7库元件中英对照表

AD芯片-----TECHWELL TW6805A仿真软件里的AD0809有问题,用0808代替定时/计数器的使用方法:CLK:计数和测频状态时,数字波的输入端。

(counter enable)CE:计数使能端;通过属性设置高还是低有效。

无效暂停计数RST:复位端(RESET),可设上升沿(Low-High)或者下降沿(High-Low)有效。

4种工作方式:通过属性Operating Mode 来选择。

Default : 缺省方式,计数器方式。

Time(secs):100S定时方式,由CE和RST控制暂停和重新开始。

Time(hms):10小时定时方式,同上。

Frequency: 测频方式,CE和RST有效时,显示CLK端数字波频率Count:计数方式。

+++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++常用元件列表:POT-HG 可调电位器7SEG-MPX8-CC-BLUE 8位数码管COMPIM 串口SW- 开关7SEG-BCD 含译码驱动的数显Speaker 扬声器2N5771和2N5772,15V对管300MARES , CAP,BUTTON 按钮开关KEYPAD-PHONE 3*4电话键盘KEYPAD-SMALLCALC 4*4计算器键盘KEYPAD-CALCULATOR 4*6计算器键盘PG160128A 128*128液晶++++++++元件库详细分类ics 模拟集成器件8个子类:amplifier 放大器comparators 比较器display drivers 显示驱动器filters 滤波器miscellaneous 混杂器件regulators 三端稳压器timers 555定时器voltage references 参考电压2,capacitors CAP电容,23个分类别animated 可显示充放电电荷电容audio grade axial 音响专用电容axial lead polypropene 径向轴引线聚丙烯电容axial lead polystyrene 径向轴引线聚苯乙烯电容ceramic disc 陶瓷圆片电容decoupling disc 解耦圆片电容high temp radial 高温径向电容high temp axial electrolytic高温径向电解电容metallised polyester film 金属聚酯膜电容metallised polypropene 金属聚丙烯电容metallised polypropene film 金属聚丙烯膜电容miniture electrolytic 微型电解电容multilayer metallised polyester film 多层金属聚酯膜电容mylar film 聚酯薄膜电容nickel barrier 镍栅电容non polarised 无极性电容polyester layer 聚酯层电容radial electrolytic 径向电解电容resin dipped 树脂蚀刻电容tantalum bead 钽珠电容variable 可变电容vx a xial electrolytic VX 轴电解电容3,CMOS 4000 series 4000系列数字电路adders 加法器buffers & drivers 缓冲和驱动器comparators 比较器counters 计数器decoders 译码器encoders 编码器flip-flops & latches 触发器和锁存器frequency dividers & tiner 分频和定时器gates & inverters 门电路和反相器memory 存储器混杂逻辑电路mutiplexers 数据选择器multivibrators 多谐振荡器phase-locked loops(PLL) 锁相环registers 寄存器signal switcher 信号开关4,connectors 接头;8个分类:audio 音频接头D-type D型接头DIL 双排插座header blocks 插头miscellaneous 各种接头PCB transfer PCB 传输接头SIL 单盘插座ribbon cable 蛇皮电缆terminal blocks 接线端子台5,data converters 数据转换器:4个分类:A/D converters 模数转换器D/A converters 数模转换器sample & hold 采样保持器temperature sensors 温度传感器6,debugging tools 调试工具数据:3个类别:breakpoint triggers 断点触发器logic probes 逻辑输出探针logic timuli 逻辑状态输入7,diodes 二极管;8个分类:bridge rectifiers 整流桥generic 普通二极管rectifiers 整流二极管schottky 肖特基二极管switching 开关二极管tunnel 隧道二极管varicap 稳压二极管8,inductors 电感:3个类别:generic 普通电感SMT inductors 表面安装技术电感transformers 变压器9,laplace primitives 拉普拉斯模型:7个类别:1st order 一阶模型2nd order 二阶模型controllers 控制器non-linear 非线性模型operators 算子poles/zeros 极点/零点symbols 符号10,memory ICs 存储器芯片:7个分类:dynamic RAM 动态数据存储器EEPROM 电可擦出程序存储器EPROM 可擦出程序存储器I2C memories I2C总线存储器memory cards 存储卡SPI Memories SPI总线存储器static RAM 静态数据存储器11,microprocessor ICs 微处理器:13个分类:12,modelling primitivvves 建模源:9个分类:13,operational amplifiers 运算放大器:7个分类:dual 双运放ideal 理想运放macromodel 大量使用的运放octal 8运放quad 4运放single 单运放triple 三运放14,optoelectronics 光电器件:11个分类:7-segment displays 7段显示alphanumeric LCDs 液晶数码显示bargraph displays 条形显示dot matrix displays 点阵显示graphical LCDs 液晶图形显示lamps 灯LCD controllers 液晶控制器LCD controllers 液晶面板显示LEDs 发光二极管optocouplers 光电耦合serial LCDs 串行液晶显示15,resistors 电阻:11个分类:metal film 金属膜电阻10 watt wirewound 10w绕线电阻2w metal film 2w 金属膜电阻3 watt wirewound 3w 绕线电阻7 watt wirewound 7w 绕线电阻generix 普通电阻high voltage 高压电阻NTC 负温度系数热敏电阻resistor packs 排阻variable 滑动变阻器varisitors可变电阻参考试验中采用的可变电阻是:POT-HG16,simulator primitives 仿真源:3个类别:flip-flops 触发器gates 门电路sources 电源17,switches and relays 开关和继电器:4个类别:key pads 键盘relays 普通继电器relays(specific) 专用继电器switches 开关18,switching devices 开关器件:4个分类:DIACs 两端交流开关generic 普通开关元件SCRs 可控硅TRIACs 三端双向可控硅19,真空管:20,传感器:2个分类:pressure 压力传感器temperature 温度传感器21,晶体管:8个分类:bipolar 双极型晶体管generic 普通晶体管(错误)IGBT 绝缘栅双极晶体管JFET 结型场效应管MOSFET 金属氧化物场效应管RF power LDMOS 射频功率LDMOS管RF power VDMOS 射频功率VDMOS管unijunction 单结晶体管Electromechanical 电机MOTOR AC 交流电机MOTOR SERVO 伺服电机双相步进电机motor-bistepper(Bipolar Stepper Motor),四相步进电机motor-stepper(unipolar stepper motor)驱动电路,用ULN2003可以,proteus中推荐的L298和L6201(电子元件-步进电机中有L298资料)+++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++++步进电机,可以用MTD2003,UN2916等专用芯片Proteus中图形液晶模块驱动芯片一览表LM3228 LM3229 LM3267 LM3283LM3287 LM4228 LM4265 LM4267LM4283 LM4287 PG12864F PG24064FPG128128A PG160128AAGM1232G EW12A03GLY HDM32GS12-B HDM32GS12Y-BHDG12864F-1 HDS12864F-3 HDG12864L-4 HDG12864L-6NOKIA7110 TG126410GFSB TG13650FEYAMPIRE128x64 LGM12641BS1RPROTEUS原理图元器件库详细说明单双向可控硅、包括电阻、电容、二极管、三极管和PCB的连接器符号、包括虚拟仪器和有源器件、拨动开关、键盘、可调电位器和开关、包括二极管和整流桥、稳压管、变容二极管、大功率二极管、高速二极管、可控硅、包括LCD、LED、LED阵列包括三极管包括场效应管包括模拟元器件AS 稳压二极管、全桥、74系列、及其他。

平板(LCD)主板的识别及替换课件1

平板主板的识别课件快益点武汉分公司2011年8月13日第一部分液晶类LS08机芯一、LS08机芯:分为F8和18两个系列。

F8系列印制板号为:JUJ7.820.088(特殊情况下可能会遇到印制板号为JUJ7.820.188)两个是通用的,适用机型有:W260F8、TD260F8、W270F8、TD270F8、W320F8、TD320F8、W370F8、TD370F8。

18系列印制板号为;JUJ7.820.211使用机型有:LT2618、LT3218、LT3718、LT4018、LT3718P、LT4018P、LT4219B、LT5520。

图一为F8系列主板,图二为18系列主板。

JUJ7.820.088主板适用产品系列识别CN306CN702UP2JP1JP4JP6适用机器系列/Y Y Y Y Y CHD-TD##F8系列//////CHD-W##F8系列Y/Y Y//CHD-W##F8P系列图一U501U502JP4JP6CN306CN702程序号FlASHR729、R730、R731、R732F8系列主板实物图R505图二:18系列主板实物图LT4018P主板没有此插座就是LT4018机器用;有此插座就是LT4018P没有此插座就是LT4018机器用;有此插座就是LT4018PJT3 JT6我们先介绍F8系列主板的识别方法1、F8系列26“使用LG屏,27”使用奇美屏,32”使用LG和三星屏,37”使用LG屏。

2、判断主板是W*F8还是TD*F8,W*F8和TD*F8两者区别是W*F8机器不带DVD功能;TD*F8机器是带DVD功能。

在进行主板识别时,观察主板左上角两个插座JP4、JP6和CN702插座,如果有则为TD*F8机器用,没有就是W*F8机器用。

3、对主板适用那个屏的判断: LG屏、三星屏、美屏的不同点为:●LG屏主板上右上角无U501;三星、奇美屏主板右上角有U501;●三星和奇美屏主板不同点是:三星屏主板上有R729、R730、R732,奇美屏主板上没有。

嵌入式系统概述(2)

ARM1ቤተ መጻሕፍቲ ባይዱE系列微处理器

ARM10E系列微处理器具有高性能、低功耗的特点,由于采用了新的体系结构,与同 等的ARM9器件相比较,在同样的时钟频率下,性能提高了近50%,同时,ARM10E系 列微处理器采用了两种先进的节能方式,使其功耗极低。 ARM10E系列微处理器的主要特点如下: 支持DSP指令集,适合于需要高速数字信号处理的场合。 6级整数流水线,指令执行效率更高。 支持32位ARM指令集和16位Thumb指令集。 支持64位的高速AMBA总线接口。 支持VFP10浮点处理协处理器。 全性能的MMU,支持Windows CE、Linux、Palm OS等多种主流嵌入式操作系统。 支持数据Cache和指令Cache,具有更高的指令和数据处理能力 主频最高可达400MIPS。 内嵌并行读/写操作部件。 ARM10E系列微处理器主要应用于下一代无线设备、数字消费品、成像设备、工业控 制、通信和信息系统等领域。 ARM10E系列微处理器包含ARM1020E、ARM1022E和ARM1026EJ-S三种类型,以适 用于不同的应用场合。

目前的ARM7和ARM9内核的芯片最大速度只能到 400MHz。目前最快的嵌入式处理器为Intel的 Xscale,最高主频为500MHz。

SecurCore系列微处理器

SecurCore系列微处理器专为安全需要而设计,提供了完善的32位 RISC技术的安全解决方案,因此,SecurCore系列微处理器除了具 有ARM体系结构的低功耗、高性能的特点外,还具有其独特的优势, 即提供了对安全解决方案的支持。 SecurCore系列微处理器除了具有ARM体系结构各种主要特点外, 还在系统安全方面具有如下的特点: 带有灵活的保护单元,以确保操作系统和应用数据的安全。 采用软内核技术,防止外部对其进行扫描探测。 可集成用户自己的安全特性和其他协处理器。

ISIS-7-Professional元件库列表及中英文对照整理版之欧阳术创编

模拟芯片(Analog ICs)放大器(Amplifiers)比较器(Comparators)显示驱动器(Display Drivers)过滤器(Filters)数据选择器(Multiplexers)稳压器(Regulators)定时器(Timers)基准电压(Voltage Reference)杂类(Miscellananeous)电容(Capacitors)可动态显示充放电电容(Animated)音响专用轴线电容(Audio Grade Axial)轴线聚苯烯电容(Axial Lead Polypropene)轴线聚苯烯电容(Axial Lead Polystyrene)陶瓷圆片电容(Ceramic Disc)去耦片状电容(Decoupling Disc)普通电容(Generic)高温径线电容(High Temp Radial)高温径线电解电容(High Temperature Axial Electrolytic)金属化聚酯膜电容(Metallised Polyester Film)金属化聚烯电容(Metallised Polypropene)金属化聚烯膜电容(Metallised Polypropene Film)小型电解电容(Miniture Electrolytic)多层金属化聚酯膜电容(Multilayer Metallised Polyestern Film)聚脂膜电容(Mylar Film)镍栅电容(Nickel Barrier)无极性电容(Non Polarised)聚脂层电容(Polyester Layer)径线电解电容(Radial Electrolytic)树脂蚀刻电容(Resin Dipped)钽珠电容(Tantalum Bead)可变电容(Variable)VX轴线电解电容(VX Axial Electolytic) 连接器(Connectors)音频接口(Audio)D 型接口(D-Type)双排插座(DIL)插头(Header Blocks)PCB转接器(PCB Transfer)带线(Ribbon Cable)单排插座(SIL)连线端子(Terminal Blocks)杂类(Miscellananeous)数据转换器(Data Converter)模/数转换器(A/D converters)数/模转换器(D/A converters)采样保持器(Sample & Hold)温度传感器(Temperature Sensore)调试工具(Debugging Tools)断点触发器(Breakpoint Triggers)逻辑探针(Logic Probes)逻辑激励源(Logic Stimuli)二极管(Diode)整流桥(Bridge Rectifiers)普通二极管(Generic)整流管(Rectifiers)肖特基二极管(Schottky)开关管(Switching)隧道二极管(Tunnel)变容二极管(Varicap)齐纳击穿二极管(Zener)ECL 10000系列(ECL 10000 Series)各种常用集成电路机电(Electromechanical)各种直流和步进电机电感(Inductors)普通电感(Generic)贴片式电感(SMT Inductors)变压器(Transformers)拉普拉斯变换(Laplace Primitives) 一阶模型(1st Order)二阶模型(2st Order)控制器(Controllers)非线性模式(Non-Linear)算子(Operators)极点/零点(Poles/Zones)符号(Symbols)存储芯片(Memory Ics)动态数据存储器(Dynamic RAM) 电可擦除可编程存储器(EEPROM) 可擦除可编程存储器(EPROM)I2C总线存储器(I2C Memories) SPI总线存储器(SPI Memories)存储卡(Memory Cards)静态数据存储器(Static Memories) 微处理器芯片(Microprocess ICs) 6800 系列(6800 Family)8051 系列(8051 Family)ARM 系列(ARM Family)AVR 系列(AVR Family)Parallax 公司微处理器(BASIC Stamp Modules)HCF11 系列(HCF11 Family)PIC10 系列(PIC10 Family)PIC12 系列(PIC12 Family)PIC16 系列(PIC16 Family)PIC18 系列(PIC18 Family)Z80系列(Z80 Family)CPU 外设(Peripherals)杂项(Miscellaneous)含天线、ATA/IDE硬盘驱动模型、单节与多节电池、串行物理接口模型、晶振动态与通用保险、模拟电压与电流符号、交通信号灯建模源(Modelling Primitives)模拟(仿真分析)(Analogy-SPICE)数字(缓冲器与门电路)(Digital--Buffers&Gates)数字(杂类)(Digital--Miscellaneous)数字(组合电路)(Digital--Combinational)数字(时序电路)(Digital--Sequential)混合模式(Mixed Mode)可编程逻辑器件单元(PLD Elements)实时激励源(Realtime Actuators)实时指示器(Realtime Indictors)运算放大器(Operational Amplifiers)单路运放(Single)二路运放(Dual)三路运放(Triple)四路运放(Quad)八路运放(Octal)理想运放(Ideal)大量使用的运放(Macromodel)光电子类器件(Optoelectronics)七段数码管(7-Segment Displays)英文字符与数字符号液晶显示器(Alphanumeric LCDs) 条形显示器(Bargraph Displays)点阵显示屏(Dot Matrix Display)图形液晶(Grphical LCDs)灯泡(Lamp)液晶控制器(LCD Controllers)液晶面板显示(LCD Panels Displays)发光二极管(LEDs)光耦元件(Optocouplers)串行液晶(Serial LCDs)可编程逻辑电路与现场可编程门阵列(PLD&FPGA) 无子类电阻(Resistors)0.6W金属膜电阻(0.6W Metal Film)10W 绕线电阻(10W Wirewound)2W 金属膜电阻(2W Metal Film)3W 金属膜电阻(3W Metal Film)7W 金属膜电阻(7W Metal Film)通用电阻符号(Generic)高压电阻(High Voltage)负温度系数热敏电阻(NTC)排阻(Resisters Packs)滑动变阻器(Variable)可变电阻(Varistors)仿真源(Simulator Primitives)触发器(Flip-Flop)门电路(Gates)电源(Sources)扬声器与音响设备(Speaker&Sounders)无子分类开关与继电器(Switch&Relays)键盘(Keypads)普通继电器(Generic Relays)专用继电器(Specific Relays)按键与拨码(Switchs)开关器件(Switching Devices)双端交流开关元件(DIACs)普通开关元件(Generic)可控硅(SCRs)三端可控硅(TRIACs)热阴极电子管(Thermionic Valves)二极真空管(Diodes)三极真空管(Triodes)四极真空管(Tetrodes)五极真空管(Pentodes)转换器(Transducers)压力传感器(Pressures)温度传感器(Temperature)晶体管(Transistors)双极性晶体管(Bipolar)普通晶体管(Generic)绝缘栅场效应管(IGBY/Insulated Gate Bipolar Transistors结型场效应晶体管(JFET)金属-氧化物半导体场效应晶体管(MOSFET)射频功率LDMOS晶体管(RF Power LDMOS)射频功率VDMOS晶体管(RF Power VDMOS)单结晶体管(Unijunction)CMOS 4000系列(CMOS 4000 seriesTTL 74系列(TTL 74 series)TTL 74增强型低功耗肖特基系列(TTL 74ALS Series) TTL 74增强型肖特基系列(TTL 74AS Series)TTL 74高速系列(TTL 74F Series)TTL 74HC系列/CMOS工作电平(TTL 74HC Series) TTL 74HCT系列/TTL工作电平(TTL 74HCT Series)TTL 74低功耗肖特基系列(TTL 74LS Series)TTL 74肖特基系列(TTL 74S Series)加法器(Adders)缓冲器/驱动器(Buffers&Drivers)比较器(Comparators)计数器(Counters)解码器(Decoders)编码器(Encoders)存储器(Memory)触发器/锁存器(Flip-Flop&Latches)分频器/定时器(Frequency Dividers & Timers)门电路/反相器(Gates&Inverters)数据选择器(Multiplexers)多谐振荡器(Multivibrators)振荡器(Oscillators)锁相环(Phrase-Locked-Loop,PLL)寄存器(Registers)信号开关(Signal Switches)收发器(Tranxceivers)杂类逻辑芯片(Misc.Logic)Proteus isis 的元件库中英对照Proteus 元件名称对照1元件名称中文名说明7407 驱动门1N914 二极管74Ls00 与非门74LS04 非门74LS08 与门74LS390 TTL 双十进制计数器7SEG 4针BCD-LED 输出从0-9 对应于4根线的BCD码7SEG 3-8译码器电路BCD-7SEG[size=+0]转换电路ALTERNATOR 交流发电机AMMETER-MILLI mA安培计AND 与门BATTERY 电池/电池组BUS 总线CAP 电容CAPACITOR 电容器CLOCK 时钟信号源CRYSTAL 晶振D-FLIPFLOP D触发器FUSE 保险丝GROUND 地LAMP 灯LED-RED 红色发光二极管LM016L 2行16列液晶可显示2行16列英文字符,有8位数据总线D0-D7,RS,R/W,EN三个控制端口(共14线),工作电压为5V。

iw1710规格书中文版

iw1710规格书中文版IW1710机翻中文版IW1710数字PWM电流模式控制器,应用准谐工作模式产品特点原边反馈简化了设计,并去除了光耦准谐振模式,提高的整体效率EZ-EMI 设计,轻松满足全球EMI标准高达130 kHz的开关频率,适用于小尺寸变压器极为严格的输出电压调节无需外部补偿元件符合CEC/ EPA空载功耗和平均效率规定内置输出恒流控制与初级侧反馈低启动电流(典型值10μA)内置软启动内置短路保护和输出过压保护可选的AC线路欠压/过电压保护轻负载时工作在PFM模式电流检测电阻短路保护过温保护说明iW1710是一款高性能的AC/DC电源控制器,它采用数字控制技术,打造峰值电流PWM模式反激式电源。

iW1700工作在准谐振模式,在重负载提供高效率,以及一些关键的内置保护功能,同时最大限度地减少了外部元件数量,简化了EMI设计,降低材料成本的总费用。

iW1710不再需要次级反馈电路,同时实现出色的线性和负载调节。

它在去除了环路补偿元件的同时保证稳定的工作。

脉冲波形分析使环路响应是比传统的解决方案快得多,从而提高了动态负载响应。

内置电流限制功能可优化变压器设计,通用的离线应用程序在很宽的输入电压范围。

在轻负载时超低的工作电流和和待机功率,保证iW1710是新管理标准和平均效率应用的理想选择。

应用典型应用电路引脚说明引脚名称类型说明1NC-悬空脚2V模拟输入辅助电压检测(用于初级端调节)3V模拟输入输入端电压平均值检测4SD模拟输入外部关断控制。

通过一个电阻连接到地,如不使用见5GND地地6I模拟输入初级电流检测(用于逐周期峰值电流控制和限制)7OUTPUT输出外部MOSFET管栅极驱动。

8V电源输入控制逻辑的电源和电压检测的上电复位电路。

额定最大值参数符号数值单位VCC直流电压范围(PIN8 V)V~18V 直流电源电流(PIN8 V)I20mA MOSFET栅极驱动(PIN7 OUTPUT)~18V 电压反馈(PIN2 V)~4V 输入端电压检测(PIN3 V)~18V SD输入(PIN4 SD)~18V 功耗T≤25℃P526mW最高结温T125℃工作温度T-65~150℃结到环境的热阻θ160℃/W 防静电等级2000V 闩锁测试±100mA电气特性VCC=12V -40℃至85℃典型性能特性功能框图工作原理iW1710采用了专有的初级侧控制技术,去除了光耦反馈和传统设计所需的二次调节电路的数字控制器。

66572资料

April 1996NEC Electronics Inc.A10616EU1V0DS00CMOS-8LHD3.3-Volt, 0.5-Micron CMOS Gate ArraysPreliminary DescriptionNEC's CMOS-8LHD gate-array family combines cell-based-level densities with the fast time-to-market and low development costs of gate arrays. With a unique heterogeneous cell architecture, CMOS-8LHD provides the very dense logic and RAM capabilities required to build devices for fast computer and communications systems.NEC delivers high-speed, 0.5-micron, drawn gate length (Leff=0.35-micron), three-level metal, CMOS technology with an extensive family of macros. I/O macros include GTL, HSTL, and pECL. TTL CMOS I/Os are provided with 5-V tolerance for applications requiring interface to 5-V logic. PCI signaling standards are also supported,including 3.3-V, 66 MHz PCI. The technology is enhanced by a set of advanced features, including phase-locked loops, clock tree synthesis, and high-speed memory. The CMOS-8LHD gate-array family of 3.3-V devices consists of 12 masters, offered in densities of 75K raw gates to 1.123 million raw gates. Usable gates range from 45K to 674K used gates.The gate-array family is supported by NEC's OpenCAD ®design system, a mixture of popular third-party EDA tools,and proprietary NEC tools. NEC proprietary tools include the GALET floorplanner, which helps to reduce design time and improve design speed, and a clock tree synthesis tool that automatically builds a balanced-buffer clock tree to minimize on-chip clock skew.Figure 1. CMOS-8LHD Package Options: BGA & QFPTable 1. CMOS-8LHD Family Features and BenefitsCMOS-8LHD ApplicationsThe CMOS-8LHD family is ideal for use in personal computer systems, engineering workstations, and telecommunications switching and transmission systems, where extensive integration and high speeds are primary design goals. With power dissipation of 0.21 µW/MHz/gate, CMOS-8LHD is also suited for lower-power applications where high performance is required.OpenCAD is a registered trademark of NEC Electronics Inc.CMOS-8LHD2Cell-Based Array ArchitectureThe CMOS-8LHD gate-array family is built with the Cell-Based Array (CBA) architecture licensed from the Silicon Architects Group of Synopsys. CBA architecture uses two types of cells: compute cells and drive cells.This heterogeneous cell architecture enables very high-density design. Compute cells are used to optimize intramacro logic. Drive cells are optimized for intermacro interconnect. The two cell types are also used to build macros with up to three different power/performance/area points.CBA has a rich macrocell library that is optimized for synthesis. RAM blocks are efficiently created from the CBA architecture, using compute cells as memory cores, and sense amplifiers and drive cells as word and address predecoder drivers.As shown in Figure 2, CBA is divided into I/O and array regions. The I/O region contains input and output buffers. The array region contains the gates used to build logic, RAM blocks, and other design features.Power Rail ArchitectureCMOS-8LHD provides additional flexibility for mixedvoltage system designs. As shown in Figure 2, the arrays contain two power rails: a 3.3-V rail, and V DD2.The V DD2 rail is used for interfaces such as 5-V PCI buffers where a clamping diode allows protection for up to an 11-V voltage spike, per the PCI revision 2.1specification.Figure 2. CBA Layout and Cell ConfigurationThe V DD2 rail is separated into sections to give flexibility for including two or more buses requiring special I/O voltage on one device. Each section can operate as an independent voltage zone, and sections can be linked together to form common voltage zones.Packaging and TestNEC utilizes BIST test structures for RAM testing. NEC also offers advanced packaging solutions including Plastic Ball Grid Arrays (PBGA), Plastic Quad Flat Packs (PQFP), and Pin Grid Arrays (PGA). Please call your local NEC ASIC design center representative for a listing of available master/package combinations.PublicationsThis data sheet contains preliminary specifications for the CMOS-8LHD gate-array family. Additional infor-mation will be available in NEC's CMOS-8LHD Block Library and CMOS-8LHD Design Manual . Call your local NEC ASIC design center representative or the NEC literature line for additional ASIC design information; see the back of this data sheet for locations and phone numbers.Table 2. CMOS-8LHD Base Array Line-upDevice Raw Gates Used Gates (1)Total Pads66562750404502416466563997925987518866565125216751292126656617963210777925266568202400121440268665692681281608763086657029792017875232466571359744215845356665725008643005184206657362054437232646866575802240481344532(1) Actual gate utilization varies depending on circuit implementation.Utilization is 60% for 3LM.3CMOS-8LHDInput/Output CapacitanceV DD =V I =0-V; f =1 MHzTerminal Symbol Typ Max Unit Input C IN 1020pF Output C OUT 1020pF I/OC I/O1020pF(1)Values include package pin capacitancePower ConsumptionDescription Limits Unit Internal gate (1)0.21µW/MHz Input buffer 2.546µW/MHz Output buffer10.60µW/MHzAbsolute Maximum RatingsPower supply voltage, V DD –0.5 to +4.6-VInput voltage, V I3.3-V input buffer (at V I < V DD + 0.5-V)–0.5 to +4.6-V 3.3-V fail-safe input buffer (at V I < V DD + 0.5-V)–0.5 to +4.6-V 5 V-tolerant (at V I < V DD + 3.0-V)–0.5 to +4.6-V Output Voltage, V O3.3-V output buffer (at V O < V DD + 0.5-V)–0.5 to +4.6-V 5-V-tolerant output buffer (at V O < V DD + 3.0-V)–0.5 to +4.6-V 5-V open-drain output buffer (at V O < V DD + 3.0-V)–0.5 to +4.6-VLatch-up current, I LATCH >1 A (typ)Operating temperature, T OPT –40 to +85°C Storage temperature, T STG–65 to +150°C (1) Assumes 30% internal gate switching at one timeCaution: Exposure to absolute maximum ratings for extended periods may affect device reliability; exceeding the ratings could cause permanent damage. The device should not be operated outside the recommended operating conditions.Recommended Operating ConditionsV DD = 3.3-V ±0.165-V; T j = 0 to +100°C3.3-V Interface 5-V Interface5-V PCI 3.3-V PCIBlock BlockLevel LevelParameterSymbol Min Max Min Max Min Max Min Max Unit I/O power supply voltage V DD 3.0 3.6 3.0 3.6 3.0 5.5 3.0 3.6V Junction temperature T J 0+1000+1000+1000+100°C High-level input voltage V IH 2.0V DD 2.0 5.5 2.0V CC 0.5 V CCV CC V Low-level input voltage V IL 00.800.800.800.3 V CCV Positive trigger voltage V P 1.50 2.70 1.50 2.70————V Negative trigger voltage V N 0.60 1.60.60 1.6————V Hysteresis voltage V H 1.10 1.3 1.10 1.3————V Input rise/fall time t R , t F 0200020002000200ns Input rise/fall time, Schmittt R , t F1010————nsAC CharacteristicsV DD = 3.3-V ±0.3-V; T j = –40 to +125°C ParameterSymbol MinTypMax Unit Conditions Toggle frequency (F611)f TOG356MHzD-F/F; F/O = 2 mmDelay time2-input NAND (F322)t PD181ps F/O = 1; L = 0 mmt PD 186ps F/O = 2; L = typ (0.42 mm)Flip-flop (F611)t PD 573ps F/O = 1; L = 0 mm t PD 688ps F/O = 2; L = typ t SETUP 410ps —t HOLD 540ps —Input buffer (FI01)t PD 268ps F/O = 1; L = 0 mm t PD 312ps F/O = 2; L = typ Output buffer (9 mA) 3.3-V (FO01)t PD 1.316ns C L = 15 pF Output buffer (9 mA) 5-V-tolerant (FV01)t PD 1.228ns C L = 15 pF Output buffer (9 mA) 5-V-swing (FY01)t PD 1.517ns C L = 15 pF Output rise time (9 mA) (FO01)t R 1.347ns C L = 15 pF Output fall time (9 mA) (FO01)t F1.284nsC L = 15 pFCMOS-8LHD4(3)Rating is for only one output operating in this mode for less than 1 second.(4)Normal type buffer: I OH < I OL .(5)Balanced buffer: I OH = I OL .(6)Resistor is called 50ký to maintain consistency with previous families.Notes:(1)Static current consumption increases if an I/O block with on-chip pull-up/pull-down resistor or an oscillator is used. Call an NEC ASIC design center repre-sentative for assistance in calculation.(2)Leakage current is limited by tester capabilities. Specification listed representsthis measurement limitation. Actual values will be significantly lower.DC CharacteristicsV DD = 3.3-V ±0.165-V; T j = 0 to +100°C ParameterSymbol Min Typ Max Unit Conditions Quiescent current (1)µPD66578I DDS 2.0300µA V I = V DD or GND µPD66575, 66573, 66572I DDS 1.0300µA V I = V DD or GND Remaining mastersI DDS 0.5200µA V I = V DD or GND Off-state output leakage current3.3-V buffers, 3.3-V PCII OZ ±10µA V O = V DD or GND 5-V-tolerant buffers, 5-V PCI I OZ ±14µA V O = V DD or GND 5-V open-drainI OZ ±14µA V O = V DD or GND Output short circuit current (3)I OS –250mA V O = GND Input leakage current (2)5-V PCI I IH +70, –70µA V IN = 2.7-V, 0.5-V 3.3-V PCI I I ±10µA V IN = V DD or GND RegularI I ±10–5±10µA V I = V DD or GND 50 k Ω pull-up I I –180–40µA V I = GND 5 k Ω pull-up I I –1400–350mA V I = GND 50 k Ω pull-down I I 30160µA V I = V DDResistor values50 k Ω pull-up (6)R pu 2075k Ω5 k Ω pull-upR pu 2.68.6k Ω50 k Ω pull-down (6)R pu 22.5100k ΩInput clamp voltageV IC –1.2V I I = 18 mA Low-level output current (ALL buffer types)3 mA I OL 3mA V OL = 0.4-V 6 mA I OL 6mA V OL = 0.4-V 9 mA I OL 9mA V OL = 0.4-V 12 mA I OL 12mA V OL = 0.4-V 18 mA I OL 18mA V OL = 0.4-V 24 mAI OL 24mA V OL = 0.4-V High-level output current (5-V-tolerant block)3 mA I OH –3mA V OH = V DD –0.4-V 6 mA I OH –3mA V OH = V DD –0.4-V 9 mA I OH –3mA V OH = V DD –0.4-V 12 mA I OH –3mA V OH = V DD –0.4-V 18 mA I OH –4mA V OH = V DD –0.4-V 24 mAI OH –4mA V OH = V DD –0.4-V High-level output current (3.3-V interface block)3 mA I OH –3mA V OH = V DD –0.4-V 6 mA I OH –6mA V OH = V DD –0.4-V 9 mA I OH –9mA V OH = V DD –0.4-V 12 mA I OH –12mA V OH = V DD –0.4-V 18 mA I OH -18mA V OH = V DD –0.4-V 24 mAI OH -24mA V OH = V DD –0.4-V Output voltage (5-V PCI)High-level output voltage V OH 2.4mA I OH = 2 mALow-level output voltage V OL 0.55mA I OL = 3 mA, 6 mA Output voltage (3.3-V PCI)High-level output voltage V OH 0.9 V DDmA I OH = 500 µA Low-level output voltage V OL 0.1 V DDmA I OL = 1500 µA Low-level output voltageV OL 0.1V I OL = 0 mA High-level output voltage, 5-V TTL V OH V DD –0.2V I OL = 0 mA High-level output voltage, 3.3-VV OHV DD –0.1VI OH = 0 mACMOS-8LHD5CMOS-8LHD6Document No. A10616EU1V0DS00For literature, call toll-free 7 a.m. to 6 p.m. Pacific time: 1-800-366-9782or FAX your request to: 1-800-729-9288©1996 NEC Electronics Inc./Printed in U.S.A.NEC ASIC DESIGN CENTERSWEST•3033 Scott Boulevard Santa Clara, CA 95054TEL 408-588-5008FAX 408-588-5017•One Embassy Centre9020 S.W. Washington Square Road,Suite 400Tigard, OR 97223TEL 503-671-0177FAX 503-643-5911THIRD-PARTY DESIGN CENTERSSOUTH CENTRAL/SOUTHEAST•Koos Technical Services, Inc.385 Commerce Way, Suite 101Longwood, FL 32750TEL 407-260-8727FAX 407-260-6227•Integrated Silicon Systems Inc.2222 Chapel Hill Nelson Highway Durham, NC 27713TEL 919-361-5814FAX 919-361-2019•Applied Systems, Inc.1761 W. Hillsboro Blvd., Suite 328Deerfield Beach, FL 33442TEL 305-428-0534FAX 305-428-5906NEC Electronics Inc.CORPORATE HEADQUARTERS2880 Scott Boulevard P.O. Box 58062Santa Clara, CA 95052TEL 408-588-6000No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Electronics Inc. (NECEL). The information in this document is subject to change without notice. ALL DEVICES SOLD BY NECEL ARE COVERED BY THE PROVISIONS APPEARING IN NECEL TERMS AND CONDITIONS OF SALES ONLY. INCLUDING THE LIMITATION OF LIABILITY,WARRANTY, AND PATENT PROVISIONS. NECEL makes no warranty, express, statutory, implied or by description, regarding informa-tion set forth herein or regarding the freedom of the described devices from patent infringement. NECEL assumes no responsibility for any errors that may appear in this document. NECEL makes no commitments to update or to keep current information contained in this document. The devices listed in this document are not suitable for use in applications such as, but not limited to, aircraft control systems,aerospace equipment, submarine cables, nuclear reactor control systems and life support systems. “Standard” quality grade devices are recommended for computers, office equipment, communication equipment, test and measurement equipment, machine tools,industrial robots, audio and visual equipment, and other consumer products. For automotive and transportation equipment, traffic control systems, anti-disaster and anti-crime systems, it is recommended that the customer contact the responsible NECEL salesperson to determine the reliabilty requirements for any such application and any cost adder. NECEL does not recommend or approve use of any of its products in life support devices or systems or in any application where failure could result in injury or death.If customers wish to use NECEL devices in applications not intended by NECEL, customer must contact the responsible NECEL sales people to determine NECEL’s willingness to support a given application.SOUTH CENTRAL/SOUTHEAST•16475 Dallas Parkway, Suite 380Dallas, TX 75248TEL 972-735-7444FAX 972-931-8680•Research Triangle Park2000 Regency Parkway, Suite 455Cary, NC 27511TEL 919-460-1890FAX 919-469-5926•Two Chasewood Park 20405 SH 249, Suite 580Houston, TX 77070TEL 713-320-0524FAX 713-320-0574NORTH CENTRAL/NORTHEAST•The Meadows, 2nd Floor 161 Worcester Road Framingham, MA 01701TEL 508-935-2200FAX 508-935-2234•Greenspoint Tower2800 W. Higgins Road, Suite 765Hoffman Estates, IL 60195TEL708-519-3945FAX 708-882-7564。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

FUNCTIONAL BLOCK DIAGRAM

D0 -Dn (x18 or x9)

WEN WCLK/WR WCS LD SEN SCLK

INPUT REGISTER

OFFSET REGISTER

FF/IR PAF EF/OR PAE HF FWFT/SI PFM FSEL0 FSEL1

ASYW

WRITE CONTROL LOGIC

PIN CONFIGURATIONS (CONTINUED)

A1 BALL PAD CORNER

A

V CC V CC V CC V CC V CC V CC WCLK PRS GND FF EREN RCLK OE VDDQ VDDQ VDDQ VDDQ VDDQ

B

V CC V CC V CC V CC V CC V CC WEN MRS GND PAF EF REN RCS VDDQ VDDQ VDDQ VDDQ VDDQ

FEATURES:

•

• • • • • • • • • • • •

Choose among the following memory organizations: IDT72T1845 2,048 x 18/4,096 x 9 IDT72T1855 4,096 x 18/8,192 x 9 IDT72T1865 8,192 x 18/16,384 x 9 IDT72T1875 16,384 x 18/32,768 x 9 IDT72T1885 32,768 x 18/65,536 x 9 IDT72T1895 65,536 x 18/131,072 x 9 IDT72T18105 131,072 x 18/262,144 x 9 IDT72T18115 262,144 x 18/524,288 x 9 IDT72T18125 524,288 x 18/1,048,576 x 9 Up to 225 MHz Operation of Clocks User selectable HSTL/LVTTL Input and/or Output Read Enable & Read Clock Echo outputs aid high speed operation User selectable Asynchronous read and/or write port timing 2.5V LVTTL or 1.8V, 1.5V HSTL Port Selectable Input/Ouput voltage 3.3V Input tolerant Mark & Retransmit, resets read pointer to user marked position Write Chip Select (WCS) input enables/disables Write operations Read Chip Select (RCS) synchronous to RCLK Programmable Almost-Empty and Almost-Full flags, each flag can default to one of eight preselected offsets Program programmable flags by either serial or parallel means Selectable synchronous/asynchronous timing modes for Almost-

RAM ARRAY 2,048 x 18 or 4,096 x 9 4,096 x 18 or 8,192 x 9 8,192 x 18 or 16,384 x 9 16,384 x 18 or 32,768 x 9 32,768 x 18 or 65,536 x 9 65,536 x 18 or 131,072 x 9 131,072 x 18 or 262,144 x 9 262,144 x 18 or 524,288 x 9 524,288 x 18 or 1,048,576 x 9

2

3

4

5

6

7

8

9

10

11

12

5909 drw02

IDT72T1845/72T1855/72T1865/72T1875/72T1885/72T1895 Only

PBGA: 1mm pitch, 13mm x 13mm (BB144-1, order code: BB) TOP VIEW

2

元器件交易网

C

WEN VDDQ VDDQ VDDQ VCC VCC VDDQ VDDQ VDDQ

D

ASYW

SEN IW

VDDQ

VCC VCC

VCC

GND

GND

VCC

VCC GND

VDDQ VCC

E

SCLK VDDQ GND GND GND GND Q17

F

VREF

D17

VCC VCC

GND

GND

GND

GND

GND

SEPTEMBER 2003

DSC-5909/16

元器件交易网

IDT72T1845/55/65/75/85/95/105/115/125 2.5V TeraSync™ 18-BIT/9-BIT FIFO 2Kx18/4Kx9, 4Kx18/ 8Kx9, 8Kx18/16Kx9, 16Kx18/32Kx9, 32Kx18/64Kx9, 64Kx18/128Kx9, 128Kx18/256Kx9, 256Kx18/512Kx9, 512Kx18/1Mx9 COMMERCIAL AND INDUSTRIAL TEMPERATURE RANGES

READ CONTROL LOGIC

RT MARK ASYR

JTAG CONTROL (BOUNDARY SCAN)

RCLK/RD REN RCS

HSTL I/0 CONTROL

OE

EREN

5909 drw01

Q0 -Qn (x18 or x9)

ERCLK

IDT and the IDT logo are registered trademarks of Integrated Device Technology, Inc. TeraSync FIFO is a trademark of Integrated Device Technology, Inc.

GND

VCC VCC

VDDQ VDDQ

Q16 Q15

G

D15 D16 GND GND GND GND GND GND GND GND GND GND

H J

D13

D14

VDDQ

VCC VCC

VCC

VDDQ

Q14

Q13 Q11

D11

D12

VDDQ

VCC VDDQ

GND VCC

GND VCC

VCC VDDQ

PIN CONFIGURATIONS

A1 BALL PAD CORNER

A

WCS PRS MRS WHSTL LD FF/IR PAF OW HF BE IP ASYR PFM PAE EREN EF/OR REN RCS VDDQ MARK

B

WCLK FWFT/SI FSEL0 SHSTL FSEL1 DNC RHSTL RCLK RT OE

VCC VDDQ

VDDQ

Q12

K

D9 D10 VDDQ D3 D4 VDDQ VDDQ Q10 Q9

L

D7 D5 D6 D1 D2 TRST D0 TCK TMS TDI TD0 ERCLK Q0 Q1 Q2 Q3 Q4 Q5 Q6 Q8 Q7

M

D8

1

NOTE: 1. DNC - Do Not Connect.

IDT72T1845/55/65/75/85/95/105/115/125 2.5V TeraSync™ 18-BIT/9-BIT FIFO 2Kx18/4Kx9, 4Kx18/ 8Kx9, 8Kx18/16Kx9, 16Kx18/32Kx9, 32Kx18/64Kx9, 64Kx18/128Kx9, 128Kx18/256Kx9, 256Kx18/512Kx9, 512Kx18/1MURE RANGES

• •

• • • • • • • • • • • • •

Empty and Almost-Full flags Separate SCLK input for Serial programming of flag offsets User selectable input and output port bus-sizing - x9 in to x9 out - x9 in to x18 out - x18 in to x9 out - x18 in to x18 out Big-Endian/Little-Endian user selectable byte representation Auto power down minimizes standby power consumption Master Reset clears entire FIFO Partial Reset clears data, but retains programmable settings Empty, Full and Half-Full flags signal FIFO status Select IDT Standard timing (using EF and FF flags) or First Word Fall Through timing (using OR and IR flags) Output enable puts data outputs into high impedance state JTAG port, provided for Boundary Scan function Available in 144-pin (13mm x 13mm) or 240-pin (19mm x 19mm) PlasticBall Grid Array (PBGA) Easily expandable in depth and width Independent Read and Write Clocks (permit reading and writing simultaneously) High-performance submicron CMOS technology Industrial temperature range (–40°C to +85°C) is available