一种高速LVDS驱动电路的设计

LVDS原理及设计指南

LVDS原理及设计指南LVDS全称为低压差分信号(Low Voltage Differential Signaling),是一种高速串行接口技术,广泛应用于电子设备中进行高速数据传输。

LVDS主要通过两对差分信号进行数据传输,其中一对信号传输高电平信号,另一对信号传输低电平信号,通过差分运算来提高抗干扰能力和抗噪声能力,以实现高质量的数据传输。

LVDS的工作原理如下:1.发送端:将输入信号通过电流驱动压缩成低压差分信号,并通过双绞线传输给接收端。

2.传输线路:使用双绞线进行数据传输,利用差分运算来抵消传输线上的共模噪声和反射噪声。

3.接收端:对接收到的低压差分信号进行解码,还原成原始的输入信号。

设计LVDS接口时需要注意以下几点:1.信号线路的设计:为了保证信号的完整性和稳定性,需要控制信号线的阻抗匹配,减小信号线的长度和延迟,并避免信号线与高频噪声信号线的交叉和平行布线。

2.布线和PCB设计:保持信号线的长度均匀,并尽量使用同一层或相邻层进行差分信号线布线,以减小信号线之间的不平衡和串扰。

3.电源和接地:为了提供噪声的抑制和信号的稳定性,需要使用低噪声电源和低阻抗接地。

4.EMI抑制:由于LVDS接口传输速率高,会引起较大的电磁辐射干扰,因此需要在设计中加入适当的EMI抑制措施,如电磁屏蔽、地线设计和滤波器等。

5.信号匹配:为了保证所发送信号的完整性和稳定性,需要将发送端与接收端之间的差分阻抗匹配,以最大限度地减小信号反射和串扰。

总之,LVDS是一种高速串行接口技术,通过差分运算进行数据传输,具有抗噪声和抗干扰能力强的特点。

在设计LVDS接口时需注意信号线路的设计、布线和PCB设计、电源和接地、EMI抑制以及信号匹配等方面,以保证高质量的数据传输。

高速转换器的lvds,cml,coms数字输出的分析和对比

高速转换器的lvds,cml,coms数字输出的分析和对比

设计人员有各种模数转换器(ADC)可以选择,数字数据输出类型是选择过程中需要考虑的一项重要参数。

目前,高速转换器三种最常用的数字输出是互补金属氧化物半导体(CMOS)、低压差分信号(LVDS)和电流模式逻辑(CML)。

ADC中每种数字输出类型都各有优劣,设计人员应根据特定应用仔细考虑。

这些因素取决于ADC的采样速率和分辨率、输出数据速率、系统设计的电源要求,以及其他因素。

本文将讨论每种输出类型的电气规格,及其适合特定应用的具体特点。

我们将从物理实现、效率以及最适合每种类型的应用这些方面来对比这些不同类型的输出。

CMOS数字输出驱动器

在采样速率小于200 MSPS的ADC中,CMOS是很常见的数字输出。

典型的CMOS驱动器由两个晶体管(一个NMOS和一个PMOS)组成,连接在电源(VDD)和地之间,如图1a所示。

这种结构会导致输出反转,因此,可以采用图1b所示的背对背结构作为替代方法,避免输出反转。

输出为低阻抗时,CMOS输出驱动器的输入为高阻抗。

在驱动器的输入端,由于栅极与导电材料之间经栅极氧化层隔离,两个CMOS晶体管的栅极阻抗极高。

输入端阻抗范围可达k至M级。

在驱动器输出端,阻抗由漏电流ID控制,该电流通常较小。

此时,阻抗通常小于几百。

CMOS的电平摆幅大约在VDD和地之间,因此可能会很大,具体取决于VDD幅度。

基于CRC校验的高速长线LVDS传输设计

基于CRC校验的高速长线LVDS传输设计李辉景;王淑琴;任勇峰;甄国涌;焦新泉【摘要】In view of the low reliability in the high-speed and long distance data transmission,put forward a new de⁃sign is put forward for reliablehigh-speed and long-term LVDS data transmission system with CRC checksum. This design uses LVDS as high speed data transmission interface,joins the equalization circuit compensating losing of data remote transmission in hardware circuit design and adds the CRC error detection code and the feedback error correction mechanism(ARQ)improving the reliability of data transmission in logic design. In order to reduce loss ofthe data bandwidth in the transmission system,optimize the old ARQ working,ensure the high speed data transmis⁃sion. After testing,the system work stable,and serial data of the rate of 400 Mbit/s can realize zero transmission er⁃ror rate in the 40 m transmission line consisting of four 10 m shielded twisted pairs.%针对数据在高速远距离传输中存在可靠性低的问题,提出了一种带CRC校验的高速长线LVDS数据传输系统设计。

(Xilinx)FPGA中LVDS差分高速传输的实现

(Xilinx)FPGA中LVDS差分高速传输的实现低压差分传送技术是基于低压差分信号(Low Volt-agc Differential signalin g)的传送技术,从一个电路板系统内的高速信号传送到不同电路系统之间的快速数据传送都可以应用低压差分传送技术来实现,其应用正变得越来越重要。

低压差分信号相对于单端的传送具有较高的噪声抑制功能,其较低的电压摆幅允许差分对线具有较高的数据传输速率,消耗较小的功率以及产生更低的电磁辐射。

LVDS:Low Voltage Differential Signaling,低电压差分信号。

LVDS传输支持速率一般在155Mbps(大约为77MHZ)以上。

LVDS是一种低摆幅的差分信号技术,它使得信号能在差分PCB线对或平衡电缆上以几百Mbps的速率传输,其低压幅和低电流驱动输出实现了低噪声和低功耗。

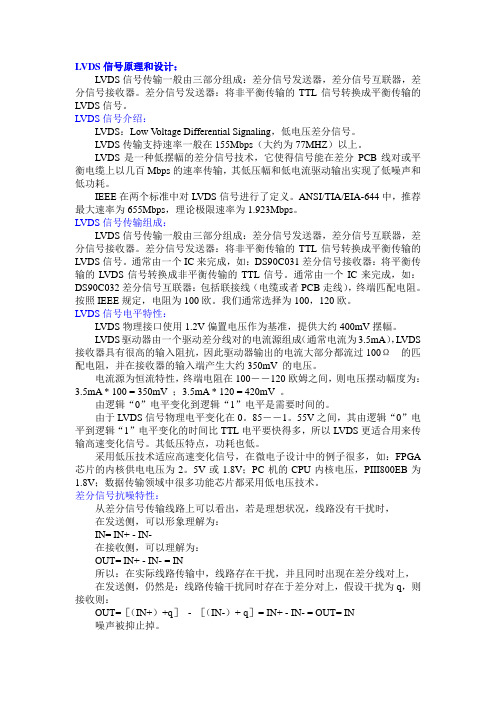

差分信号抗噪特性从差分信号传输线路上可以看出,若是理想状况,线路没有干扰时,在发送侧,可以形象理解为:IN= IN+ —IN-在接收侧,可以理解为:IN+ —IN- =OUT所以:OUT = IN在实际线路传输中,线路存在干扰,并且同时出现在差分线对上,在发送侧,仍然是:IN = IN+ —IN-线路传输干扰同时存在于差分对上,假设干扰为q,则接收则:(IN+ + q) —(IN- + q) = IN+ —IN- = OUT 所以:OUT = IN噪声被抑止掉。

上述可以形象理解差分方式抑止噪声的能力。

From: 美国国家半导体的《LVDS用户手册》P9FPGA中的差分管脚为了适用于高速通讯的场合,现在的FPGA都提供了数目众多的LVDS接口。

如Spartan-3E系列FPGA提供了下列差分标准:LVDSBus LVDSmini-LVDSRSDSDifferential HSTL (1.8V, Types I and III)Differential SSTL (2.5V and 1.8V, Type I)2.5V LVPECL inputs所拥有的差分I/O管脚数目如下From:Spartan-3E FPGA Family:Complete Data Sheet p5I/O管脚的命名方式:From:Spartan-3E FPGA Family:Complete Data Sheet p164From:Spartan-3E FPGA Family:Complete Data Sheet p18 Spartan-3E系列FPGA器件差分I/O接口输入工作的特性参数:From:Spartan-3E FPGA Family:Complete Data Sheet p126 Spartan-3E系列FPGA器件差分I/O接口输出工作的特性参数:From:Spartan-3E FPGA Family:Complete Data Sheet p127Xilinx公司差分原语的使用(原语,其英文名字为Primitive,是Xilinx针对其器件特征开发的一系列常用模块的名字,用户可以将其看成Xilinx公司为用户提供的库函数,类似于C+ +中的“cout”等关键字,是芯片中的基本元件,代表FPGA中实际拥有的硬件逻辑单元,如LUT,D触发器,RAM等,相当于软件中的机器语言。

LVDS信号原理和设计 信号介绍传输组成 技术在数字视频传输系统中的应用

LVDS信号原理和设计:LVDS信号传输一般由三部分组成:差分信号发送器,差分信号互联器,差分信号接收器。

差分信号发送器:将非平衡传输的TTL信号转换成平衡传输的LVDS信号。

LVDS信号介绍:LVDS:Low V oltage Differential Signaling,低电压差分信号。

LVDS传输支持速率一般在155Mbps(大约为77MHZ)以上。

LVDS是一种低摆幅的差分信号技术,它使得信号能在差分PCB线对或平衡电缆上以几百Mbps的速率传输,其低压幅和低电流驱动输出实现了低噪声和低功耗。

IEEE在两个标准中对LVDS信号进行了定义。

ANSI/TIA/EIA-644中,推荐最大速率为655Mbps,理论极限速率为1.923Mbps。

LVDS信号传输组成:LVDS信号传输一般由三部分组成:差分信号发送器,差分信号互联器,差分信号接收器。

差分信号发送器:将非平衡传输的TTL信号转换成平衡传输的LVDS信号。

通常由一个IC来完成,如:DS90C031差分信号接收器:将平衡传输的LVDS信号转换成非平衡传输的TTL信号。

通常由一个IC来完成,如:DS90C032差分信号互联器:包括联接线(电缆或者PCB走线),终端匹配电阻。

按照IEEE规定,电阻为100欧。

我们通常选择为100,120欧。

LVDS信号电平特性:LVDS物理接口使用1.2V偏置电压作为基准,提供大约400mV摆幅。

LVDS驱动器由一个驱动差分线对的电流源组成(通常电流为3.5mA),LVDS 接收器具有很高的输入阻抗,因此驱动器输出的电流大部分都流过100Ω的匹配电阻,并在接收器的输入端产生大约350mV 的电压。

电流源为恒流特性,终端电阻在100――120欧姆之间,则电压摆动幅度为:3.5mA * 100 = 350mV ;3.5mA * 120 = 420mV 。

由逻辑“0”电平变化到逻辑“1”电平是需要时间的。

由于LVDS信号物理电平变化在0。

基于CPLD的LVDS数据传输系统的设计与研究

传输过程 中可能会出现短 时间 ( 小于 5 ) )的失锁 ,所 ( S X 以本 方案 中特 地 引入了 FF IO芯 片 IT 2 2 1 D 7V 4 ,从 存储器 读取的数据先写入 F O,在确认 系统同步的情况下 ,再将 I F FF IO中数据读 出赋给 串化器。从而确保数据 的有效性 ,且 保证 了数 据高速 传输 的不 间断 性。可 见,在 发送模 块 中, 通过 C L P D控制 FF IO芯片 的读 写操作 是实现 L S高速 VD 传输且不丢失有效数据的关键。

4 仿 真结果

d v s dhg — p e d piee u i rfr eb sdta s so se teit d cino i I O (IO)a ad t i a r e ih se daa t q a z ae nmi ins tm,h nr u t f hpFF F F n v l e ot h r s y o o c s aa

NUC.Ta u n0 0 5 ,C ia i a 3 0 1 hn ) y

Ab t a t I r e o s l e t e h g -s e d s n l r c si g a d t n m s o o t n c si aata s rs e d ds n e sr c : n o d rt ov h ih — e i a o es n a s s n b t e e k n d t r f p e i a c p g p n r i i l n e t p o lms a CP D — ae i h s e d L rbe , L b s d h g — p e VDS b sd t rn frs se i d s n d o sr ce i d o VDS c i s u a a t se y tm s ei e ,c n tu t d ak n fL a g hp

LVDS电路的仿真与设计

引言:随着电子设计技术的不断进步,要求更高速率信号的互连。

在传统并行同步数字信号的数位和速率将要达到极限的情况下,设计师转向从高速串行信号寻找出路。

HyperTanspo rt(by AMD), Infiniband(by Intel),PCI-Express(by Intel)等第三代I/O总线标准(3GI/O)不约而同地将低压差分信号(LVDS)作为下一代高速信号电平标准。

本文将从LV DS信号仿真、设计,测试等多方面探讨合适的LVDS信号的实现。

关键词:LVDS,阻抗控制,端接匹配LVDS(Low Voltage Differential Signal)低压差分信号,最早由美国国家半导体公司(National Semiconductor)提出的一种高速串行信号传输电平,由于它传输速度快,功耗低,抗干扰能力强,传输距离远,易于匹配等优点,迅速得到诸多芯片制造厂商和应用商的青睐,并通过TIA/EIA(Telecommunication Industry Association/Electronic Industrie s Association)的确认,成为该组织的标准(ANSI/TIA/EIA-644 standard)。

LVDS信号被广泛应用于计算机、通信以及消费电子领域,并被以PCI-Express为代表的第三代I/O标准中采用。

传输线阻抗设计LVDS信号的电压摆幅只有350MV,为电流驱动的差分信号方式工作,最长的传输距离可以达到10米以上。

为了确保信号在传输线当中传播时,不受反射信号的影响,LVDS信号要求传输线阻抗受控,其中单线阻抗为50ohms,差分阻抗100ohms。

在实际应用当中,利用一些高速电路仿真分析工具,通过合理的设置层叠厚度和介质参数,调整走线的线宽和线间距,计算出单线和差分阻抗结果,来达到阻抗控制的目的。

如下图,使用Mentor公司的eP lanner工具设计差分信号的布线规则,计算出单线和差分阻抗例如通过如下的层叠和布线参数设计,得到单线阻抗为58.8Ω,差分阻抗为:102ΩPCB层叠参数设置和阻抗计算结果但是在很多时候,同时满足单线阻抗和差分阻抗是比较困难的。

LVDS接口电路基本原理

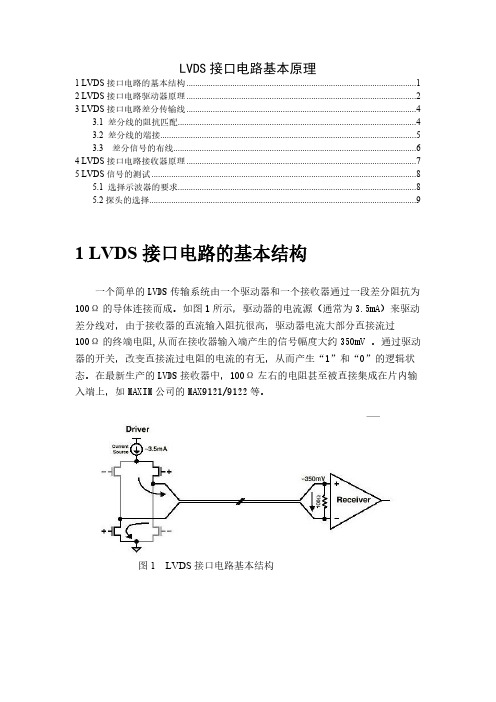

LVDS接口电路基本原理1 LVDS接口电路的基本结构 (1)2 LVDS接口电路驱动器原理 (2)3 LVDS接口电路差分传输线 (4)3.1 差分线的阻抗匹配 (4)3.2 差分线的端接 (5)3.3 差分信号的布线 (6)4 LVDS接口电路接收器原理 (7)5 LVDS信号的测试 (8)5.1 选择示波器的要求 (8)5.2探头的选择 (9)1 LVDS接口电路的基本结构一个简单的LVDS传输系统由一个驱动器和一个接收器通过一段差分阻抗为100Ω的导体连接而成。

如图1所示,驱动器的电流源(通常为3.5mA)来驱动差分线对,由于接收器的直流输入阻抗很高,驱动器电流大部分直接流过100Ω的终端电阻,从而在接收器输入端产生的信号幅度大约350mV 。

通过驱动器的开关,改变直接流过电阻的电流的有无,从而产生“1”和“0”的逻辑状态。

在最新生产的LVDS接收器中,100Ω左右的电阻甚至被直接集成在片内输入端上,如MAXIM公司的MAX9121/9122等。

图1 LVDS接口电路基本结构2 LVDS接口电路驱动器原理The Telecommunications Industry Association(TIA)颁布了一个标准,规定了用于转换二进制信号的LVDS接口电路的电气规格。

LVDS技术利用低电压差分信号来产生高速、低功率的数据传输。

差分信号的使用消除了共模噪声,因此确保了数据的传输速度以及抗噪性能。

如果想了解LVDS标准的详细信息,请查阅“Electrical Characteristics of Low Voltage Differential Signaling(LVDS)Interface Circuits”,TIA/EIA-644(March 1996)。

图2-1举例说明了一个通过一对差分连线115连接到一个LVDS接收器110的LVDS发生器100。

LVDS发生机100将一个数字的输入信号D_IN转换成为一对在差分输出终端TX_A和TX_B上的相反的LVDS输出信号。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

“主从”

高速转换器芯片。

样品电路测试表明,输出速率在时,驱动电路的指标满足标准。

关键词:驱动电路;高速接口电路;共模反馈;模拟集成电路

中图分类号:文献标识码:文章编号:()

:(投稿编号)

’, , , , , ,

(. , Chongqing , . . ; ., ., , . . ; . University Defense , Changsha , . . )

. . , .

.

:; ; ;

言

随着半导体工艺的发展,晶体管的特征尺寸不

断下降,数字或混合信号集成电路芯片内部的工作

速度已经达到几百到几的数量级。

由于芯片的集成

度高,内部元件及单元电路之间的距离近、连线短、

寄生参数小,芯片内部数据的传输、处理可以采用

电平信号。

但是,在高速数据接口方面,由于内部

信号要经过封装键合线、板上的连线以及通孔,才

能与其他芯片连接,如果采用电平作为输出接口,

则各种寄生参数会导致数据的上升下降时间以及多

( )

最常用的接口方式[]。

本原理,分析开关时序和共模反馈对电路的影响;

第节介绍驱动电路中开关控制信号整形电路和基于

“主从”结构的共模设置电路;第节介绍电路仿真和

测试结果;第节给出结论。

输出驱动电路的设计背景和基本原理

输出驱动电路的设计背景

本文介绍的驱动电路应用于

电路功能框图如图所示。

外部输入转换器的时钟信号通过一个÷除法器,产生一个 的电平信号,为数字部分提供需要的时钟。

驱动电路的作用是将分频后

电平的时钟转换为电平的时钟输出。

系统用户可以使用该时钟作为 的时钟,或者作为数据同步信号,实现位 转换器数字部分与外部的时钟同步。

输出驱动电路的基本原理

在图所示的驱动电路中,、信号与、信号相位相反。

这样的电平信号作用于四个开关,使和导通时和截止,反之亦然。

当和之间通过传输连线接一个负载电阻(在接收端,阻值 Ω)时,电流源中的电流会随着开关状态的不同从端通过负载电阻流向端,反之亦然。

这样就产生了电平的输出。

图中,在驱动电路的到端串联连接两个阻值相等的电阻( Ω)。

这种结构一般在高速结构中使用,目的是为了和接收端的负载电阻( Ω)实现阻抗匹配,减少回波干扰。

设计中,需要考虑的是和不能同时导通,否则会让电流源和电流沉瞬间短路,在输出波形上产生一个很大的过冲。

因此,在实际设计中,如图所示,要先为低电平,将关闭,然后,才为低电平,让导通,反之亦然。

由于开关时序非常重要,本文在电路设计时采用了一种开关控制信号整形电路来实现时序的要求。

o u t p

图 驱动电路基本结构

3.3V

vcm

图 差分输出电压摆幅计算原理

如图所示,根据电流源和电流沉节点的电流情况,可以得出:

cm L H L

n C L

V V V V I R R --+= () ()式对应电流沉节点。

H cm H L

p C L

V V V V I R R --+= () ()式对应电流源节点。

()()式,整理后可得:

H L H L p n C L

2V V V V

I I R R --+=+ () 当C L R R =时,可以得到差分输出电压摆幅:

p n

H L L 3

I I V V R +-=

()

对于本设计,C L 100R R ==Ω,p n 3mA I I ≈=,可得:

-()

o u t p

图共模检测电路和共模反馈原理

驱动电路通常采用共模反馈电路来稳定电平的输出共模电压。

一般的做法是通过共模检测电路提取出驱动电路的共模电压和参考共模电压的差值,然后通过反馈结构调整电流源或者电流沉的值来稳定输出共模电压。

目前常用的两种共模电压检测结构如图所示:一种是通过在两个输出端串接两个Ω左右的大电阻[],从中间抽头提取共模电压;另一种是通过两个差分对直接提取共模电压和参考共模电压的差值[]。

这两种常用结构有三个缺点:)两种结构在提取共模电压时都要连接到的两个输出端,所以会加大输出端节点的寄生电容,降低驱动电路的工作频率。

)两种结构都是直接在输出端提取共模电压,而输出端的共模电压在开关切换的过程中会产生一个跳动电压,这一跳动电压会增加共模反馈回路的稳定时间和影响共模电压稳定效果,甚至影响差模信号的摆幅。

如果将这一跳动电压用大电容滤掉,则会增加反馈环路频率补偿的复杂度,并且大大增加整个电路的芯片面积。

)两种结构的整个共模反馈环路中有周期开闭的开关,只有在开关闭合形成稳定环路后,共模反馈环路才能起作用,这就更进一步增加了反馈环路频率补偿的难度。

在电路设计时,针对这三个缺点,提出了一种基于“主从”()结构的共模设置电路,成功地解决了这三个问题。

高速驱动电路关键单元电路设计

开关控制信号整形电路设计

开关控制信号整形电路具有电平信号过零点调节和开关控制信号整形两种功能。

如图所示,和为相互反相的一对电平输入信号,如果两路信号存在延时,则少许的不一致也会导致过零点不在高、低电平的中点。

过零点位置离中点较远会影响后级整形电路的效果,所以,在开关信号进入整形电路前需要对过零点进行微量调节。

如图虚框所示,在两路输入的第级和第级非门之间加入两组反向相接的非门(正反馈),可以改善两路输入信号的过零点。

电路实现时,正反馈中非门的远小于信号通路中非门(如图中标示的值),所以该调节电路只对过零点进行微小的调节。

调节效果如图所示。

in_n

in_p

ph1

ph11

ph2

ph22

I1

I2

N:3/0.18

P:9/0.18

P:24/0.18

P:12/0.18

N:8/0.18

N:4/0.18

P:3/0.18

N:1.2/0.18

P:3/0.18

N:1.2/0.18

N:0.22/0.18

P:0.6/0.18

N:0.22/0.18

P:0.6/0.18

CMOS电平信号过两点调节电路

开关驱动信号

整形电路

图开关控制信号整形电路原理

in_n

in_p

未使用正反馈

使用正反馈

out_p

out_n

out_p

out_n

图过零点调节电路效果

图中的,完成开关输入信号的整形功能。

,的电路结构和整形效果如图所示。

具体工作原理为:在输入信号()从低电平向高电平变化时,由于先导通,所以(的漏极)先向低电平变化,由于后截止,所以(的漏极)后向低电平变化;在输入信号()从高电平向低电平变化时,由于先导通,(的漏极)先向高电平变化,由于后截止,(的漏极)后向高电平变化。

这样就满足了第节介绍的对开关时序的要求。

in

ph11

ph1

24/0.18

12/0.18

8/0.18

4/0.18

ph1

mp21

ph11

mp33

mn36

mn25

in

图开关控制信号整形电路结构及效果。