用译码器设计组合逻辑电路例题分析word精品

74LS153译码器组合逻辑电路设计案例分析

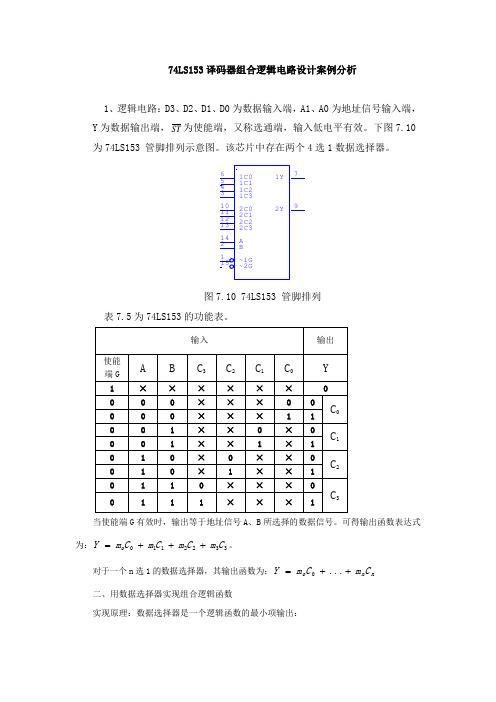

74LS153译码器组合逻辑电路设计案例分析1、逻辑电路:D3、D2、D1、D0为数据输入端,A1、A0为地址信号输入端,Y 为数据输出端,ST 为使能端,又称选通端,输入低电平有效。

下图7.10为74LS153 管脚排列示意图。

该芯片中存在两个4选1数据选择器。

2Y92C0102C1112C2122C313A 14B 2~1G 11Y71C061C151C241C33~2G15图7.10 74LS153 管脚排列表7.5为74LS153的功能表。

当使能端G 有效时,输出等于地址信号A 、B 所选择的数据信号。

可得输出函数表达式为:3322110C m C m C m C m Y o +++=。

对于一个n 选1的数据选择器,其输出函数为:n n o C m C m Y ++=...0 二、用数据选择器实现组合逻辑函数实现原理:数据选择器是一个逻辑函数的最小项输出:∑-===++=1200...n i ii n n o c m C m C m Y 而任何一个n 位变量的逻辑函数都可变换为最小项之和的标准式。

对照函数表达式和相应的数据选择器输出函数表达式,可以实现用数据选择器来表示逻辑函数。

实现步骤:(1)根据函数变量选择合适的数据选择器,一般变量个数n 个,选择2n 选1的数据选择器。

(2)将被表示的函数转换成标准与或表达式。

(3)写出选择的数据选择器的输出函数。

(4)对比两函数,使数据选择器的地址端和函数变量一一对应(高位对高位),表达式中出现的最小项相应的输入数据C 为1,否则为0。

(5)画逻辑电路图。

例:用数据选择器和门电路实现AC AB Y +=的组合逻辑电路。

(1) 选择数据选择器:选8选1数据选择器74LS151。

(2) 标准与或表达式756m m m ABC C B A C AB AC AB Y '+'+'=++=+=' (3)写出数据选择器输出函数776655443322110C m C m C m C m C m C m C m C m Y o +++++++=(4)对照上述两表达式,令A=A2,B=A1,C=A0,则n n m m '=,所以,C 0=C 1=C 2=C 3=C 4=0;C 5=C 6=C 7=1。

译码器设计组合逻辑电路案例分析

译码器设计组合逻辑电路案例分析【信息单】一、编码器在数字系统中,把二进制码按一定的规律编排,使每组代码具有特定的含义,称为编码。

具有编码功能的逻辑电路称为编码器。

编码器是一个多输入多输出的组合逻辑电路。

按照编码方式不同,编码器可分为普通编码器和优先编码器;按照输出代码种类的不同,可分为二进制编码器和非二进制编码器。

1.普通编码器普通编码器分二进制编码器和非二进制编码器。

若输入信号的个数N 与输出变量的位数n 满足N =2n ,此电路称为二进制编码器;若输入信号的个数N 与输出变量的位数n 不满足N =2n ,此电路称为非二进制编码器。

普通编码器任何时刻只能对其中一个输入信息进行编码,即输入的N 个信号是互相排斥的。

若编码器输入为4个信号,输出为两位代码,则称为4线-2线编码器(或4/2线编码器)。

2.优先编码器优先编码器是当多个输入端同时有信号时,电路只对其中优先级别最高的信号进行编码的编码器。

3.集成编码器10线-4线集成优先编码器常见型号为54/74147、54/74LS147,8线-3线常见型号为54/74148、54/74LS148。

4.编码器举例(1)键控8421BCD 码编码器10个按键S 0~S 9代表输入的10个十进制数0~9,输入为低电平有效,即某一按键按下,对应的输入信号为0,输出对应的8421码,输出为4位码,所以有4个输出端A 、B 、C 、D 。

真值表见表7.1,由真值表写出各输出的逻辑表达式为 9898S S S S =+=A76547654S S S S S S S S =+++=B 76327632S S S S S S S S =+++=C 9753197531S S S S S S S S S S =++++=D表7.1键控8421BCD 码编码器真值表(2)二进制编码器用n 位二进制代码对2n 个信号进行编码的电路称为二进制编码器。

3位二进制编码器有 8个输入端3个输出端,所以常称为8线—3线编码器,其功能真值表见表7.2,输入为高电平有效。

译码器、数据选择实现组合逻辑电路的设计(完整电子教案)

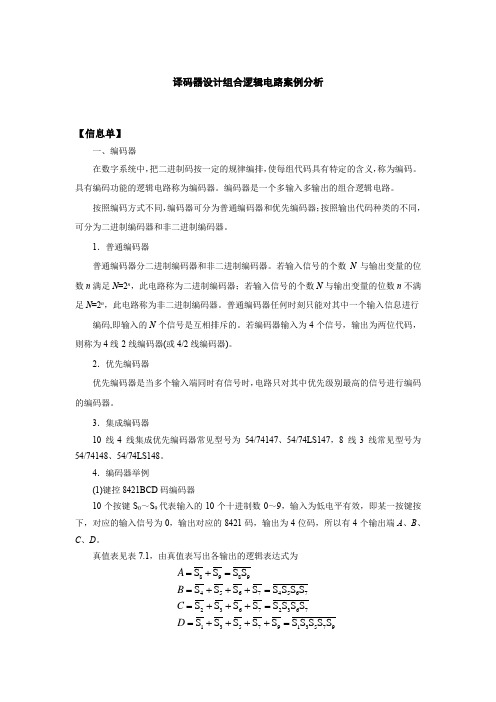

译码器、数据选择实现组合逻辑电路的设计(完整电子教案)7.1 利用译码器实现输出控制【项目任务】市电互补控制器中共有4种工作模式,编号0为停机、1为太阳工作、2为市电互补、3为市电模式。

当停机模式时,市电和光伏电不导入;当太阳工作模式,市电不导入,光伏电导入;当市电互补模式,市电和光伏电都导入;当市电模式,市电导入,光伏发电部导入。

利用译码器实现上述组合逻辑电路功能。

图7.1译码器实现输出控制【信息单】一、编码器在数字系统中,把二进制码按一定的规律编排,使每组代码具有特定的含义,称为编码。

具有编码功能的逻辑电路称为编码器。

编码器是一个多输入多输出的组合逻辑电路。

按照编码方式不同,编码器可分为普通编码器和优先编码器;按照输出代码种类的不同,可分为二进制编码器和非二进制编码器。

1.普通编码器普通编码器分二进制编码器和非二进制编码器。

若输入信号的个数N与输出变量的位数n满足N=2n,此电路称为二进制编码器;若输入信号的个数N与输出变量的位数n不满足N=2n,此电路称为非二进制编码器。

普通编码器任何时刻只能对其中一个输入信息进行编码,即输入的N个信号是互相排斥的。

若编码器输入为4个信号,输出为两位代码,则称为4线-2线编码器(或4/2线编码器)。

2.优先编码器优先编码器是当多个输入端同时有信号时,电路只对其中优先级别最高的信号进行编码的编码器。

3.集成编码器10线-4线集成优先编码器常见型号为54/74147、54/74LS147,8线-3线常见型号为54/74148、54/74LS148。

4.编码器举例(1)键控8421BCD 码编码器10个按键S 0~S 9代表输入的10个十进制数0~9,输入为低电平有效,即某一按键按下,对应的输入信号为0,输出对应的8421码,输出为4位码,所以有4个输出端A 、B 、C 、D 。

真值表见表7.1,由真值表写出各输出的逻辑表达式为 9898S S S S =+=A76547654S S S S S S S S =+++=B 76327632S S S S S S S S =+++=C 9753197531S S S S S S S S S S =++++=D表7.1键控8421BCD 码编码器真值表(2)二进制编码器用n 位二进制代码对2n 个信号进行编码的电路称为二进制编码器。

译码器应用—实现组合电路

Ci m3 m5 m6 m7 Y3 Y5 Y6 Y7

(5)画连线图

Si

Ci

&

&

Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7 STA 1

CT74LS138

STB

A0 A1 A2

STC

Ci-1 Bi AiFra bibliotekEXIT

【例6-22】 试用3线-8线译码器74LS138和门电路实现下列多 输出逻辑函数:

Y

&

Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7 STA 1

74LS138 A0 A1 A2

STB STC

C BA

EXIT

[例] 试用译码器实现全加器。

解:(1)分析设计要求,列出真值表

设被加数为 Ai ,加数为 Bi ,低位进位数为 Ci-1 。 输出本位和为 Si ,向高位的进位数为 Ci 。

(3)根据译码器的输出有效电平确定需用的门电路

EXIT

74LS138 输出低电平有效, Yi mi ,i = 0 ~ 7 因此,将 Y 函数式变换为 Y m1 m3 m5 m6 m7

Y1 Y3 Y5 Y6 Y7

采用 5 输入与非门,其输入取自 Y1、Y3、Y5、Y6 和 Y7 。

(4)画连线图

列出全加器的真值表如下: (2)根据真值表写函数式 输 入 输出

Ai Bi Ci-1 Si Ci 00000 00110 01010

Si m1 m2 m4 m7 Ci m3 m5 m6 m7 (3)选择译码器

0 1 1 0 1 选用 3 线 – 8 线译码器

1 1 1

0 0 1

0 1 0

1 0 0

0 1 1

CT74LS138。并令 A2 = Ai,A1 = Bi,A0 = Ci-1。

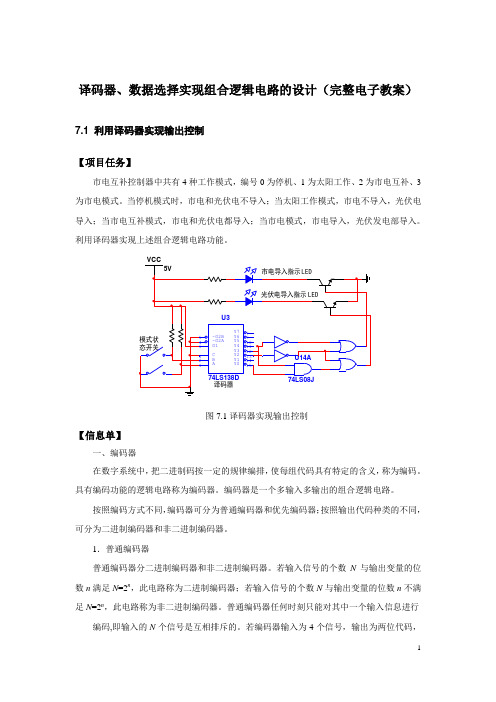

用译码器设计组合逻辑电路例题

用译码器设计组合逻辑电路例题一、用3线—8线译码器74HC138W门电路实现逻辑函数Y A/B/C/ A/ BC/ ABC。

(要求写出过程,画出连接图)(本题10分)解:(1) 74HC138勺输出表达式为:(2分) Y i/ m:(i 0~7)(2) 将要求的逻辑函数写成最小项表达式:(2分)Y A/B/C/ A/BC/ ABC m0 m2 m7 (m0m1/m7)/(3) 将逻辑函数与74HC138的输出表达式进行比较:设A= A2、B= A1、C= A0,得:Y (m0m1/m7)/ (丫0/丫2/丫7/)/(2分)(4) 可用一片74HC138H加一个与非门就可实现函数。

其逻辑图如下图所示。

(4分)t丫。

Y1 Y2 Y3 Y4 Y5 Y a Y7 74HC138A〉A〔A。

Sg S3r ~0ABC +5V d.三、公司A 、8 C 三个股东,分别占有50% 30咧日20%勺股份,试用一片3线-8 线译码器74HC138^若干门电路设计一个三输入三输出的多数表决器, 用丁开会 时按股份大小记分输出通过、平■局和否决三种表决结果。

通过、平■局和否决,分 别用X 、Y 、Z 表示(股东赞成和输出结果均用1表示)。

(12分)(3)画连线图(4分)令 74HC138的地址码 A 2 A,A 1 B,A 0 CX AB /C ABC / ABC 74HC138 A- A* S 〔 Sg S3 == | 二 午 ABC +5Vm 5 m 6 m 7 (m 5m ;m 7),Y A /BC AB /C / ABC m 3 mu/ / / \ / (m 3m 4) Z A /B /C / A /B /C A /BC / m 0 m 1 m 2 (m 0m ;m ;)/解:(2)歹0写表达式(4四、某学校学生参加三门课程A、B、C的考试,根据课程学时不同,三门课程考试及格分别可得2、4、5分,不及格均为0分,若总得分大丁等丁7分,便可结业。

38译码器实现组合逻辑电路

院系电子信息工程学院班级姓名学号实验名称38译码器实现组合逻辑电路实验日期一、实验目的1.掌握常用集成组合电路的应用;2.掌握译码器的工作原理和特点;3.熟悉集成门电路、译码器的逻辑功能和管脚排列。

二、实验器件1.数字电路实验箱2.集成电路:74LS00、74LS138三、实验原理译码器所谓译码,就是把代码的特定含义“翻译”出来的过程,而实现译码操作的电路称为译码器。

译码器可分为三类:变量译码器、码制变换译码器和显示译码器。

变量译码器又称二进制译码器,用以表示输入变量的状态。

对应于输入的每一组二进制代码,译码器都有确定的一条输出线有信号输出。

若有n个输入变量,则有2n个不同的组合状态,就有2n个输出端。

而每一个输出所代表的函数对应于n 个输入变量的最小项。

74LS138为3/8译码器,管脚图如图所示:其中:A2、A1、A0为地址输入端Y0-Y7 为输出端,低电平有效STA、STB、STC 为选通端74LS138功能表如表3-2所示,当STA=1,STB+STC=0时,执行正常的译码操作,地址码所指定的输出端有信号输出(低电平0),其它所有输出端均无信号输出(全为1)。

当STA=0,STB+STC=1,或STA=,STB+STC=1时,译码器被禁止,所以输出同时为1。

指导教师签名院系电子信息工程学院班级姓名学号实验名称38译码器实现组合逻辑电路实验日期三、设计电路,实现四、(1)逻辑电路图(2)原理图指导教师签名院系电子信息工程学院班级姓名学号实验名称38译码器实现组合逻辑电路实验日期(3)实物连接图五、电路功能验证ABC为0,Y为1 A为1,BC为0,Y为0 AB为0,B为1,Y为0指导教师签名院系电子信息工程学院班级姓名学号实验名称38译码器实现组合逻辑电路实验日期AB为0,C为1,Y为0 A为0,BC为1,Y为0 ABC为1,B为1AB为1,C为0,Y为1 AC为1,B为0,Y为0指导教师签名。

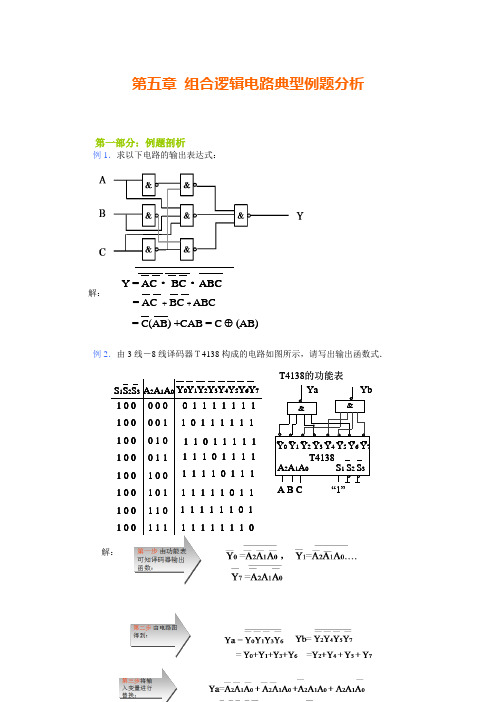

(完整版)第五章组合逻辑电路典型例题分析

第五章 组合逻辑电路典型例题分析第一部分:例题剖析例1.求以下电路的输出表达式:解:例2.由3线-8线译码器T4138构成的电路如图所示,请写出输出函数式.解:Y = AC BC ABC= AC +BC + ABC = C(AB) +CAB = C (AB) T4138的功能表&&Y 0 Y 1 Y 2 Y 3 Y 4 Y 5 Y 6 Y 7“1”T4138A B CA 2A 1A 0YaYbS 1 S 2 S 30 0 00 0 10 1 00 1 11 0 01 0 11 1 01 1 1S 1S 2S 31 0 01 0 01 0 01 0 01 0 01 0 01 0 01 0 0A 2A 1A 0Y 0Y 1Y 2Y 3Y 4Y 5Y 6Y 70 1 1 1 1 1 1 11 0 1 1 1 1 1 11 1 0 1 1 1 1 11 1 1 0 1 1 1 11 1 1 1 0 1 1 11 1 1 1 1 0 1 11 1 1 1 1 1 0 11 1 1 1 1 1 1 0例3.分析如图电路,写出输出函数Z的表达式。

CC4512为八选一数据选择器。

解:例4.某组合逻辑电路的真值表如下,试用最少数目的反相器和与非门实现电路。

(表中未出现的输入变量状态组合可作为约束项)CC4512的功能表A ⨯DIS INH 2A 1A 0Y1 ⨯0 10 00 00 00 00 00 00 00 0⨯⨯⨯⨯⨯0 0 00 0 10 1 00 1 11 0 0 1 0 11 1 01 1 1高阻态 0D 0D 1D 2D 3D 4D 5D 6D 7ZCC4512A 0A 1A 2D 0 D 1 D 2 D 3 D 4 D 5 D 6 D 7DIS INHD1DA B C D Y 0 0 0 0 10 0 0 1 00 0 1 0 10 0 1 1 00 1 0 0 0CD AB 00 01 11 1000 1 0 0 101 0 1 0 1 11 ××××10 0 1 ××AB第一步画卡诺图第三步画逻辑电路图例5.写出下面组合电路的输出表达式,分析逻辑功能。

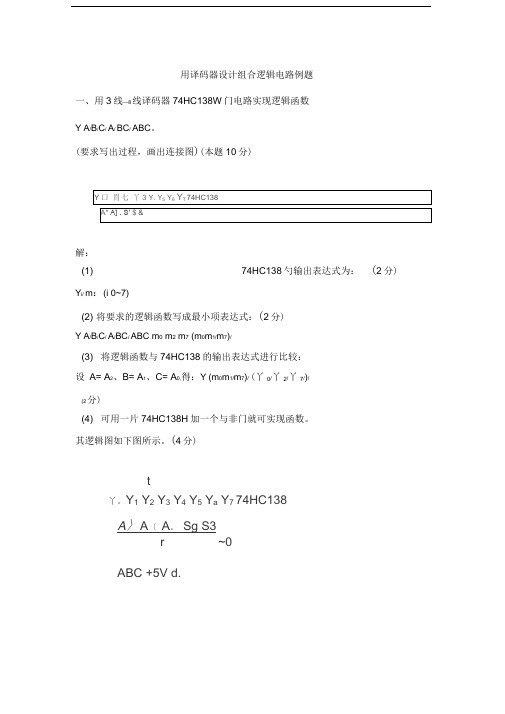

(完整word版)用译码器设计组合逻辑电路例题分析(word文档良心出品)

用译码器设计组合逻辑电路例题一、用3线-8线译码器74HC138和门电路实现逻辑函数ABC BC A C B A Y ++=/////。

(要求写出过程,画出连接图) (本题10分)解:(1)74HC138的输出表达式为: (2分))7~0(//==i m Y i i(2)将要求的逻辑函数写成最小项表达式:(2分)//7/1/0720/////)(m m m m m m ABC BC A C B A Y =++=++=(3)将逻辑函数与74HC138的输出表达式进行比较:设A= A 2、B= A 1、C= A 0,得://7/2/0//7/1/0)()(Y Y Y m m m Y == (2分)(4)可用一片74HC138再加一个与非门就可实现函数。

其逻辑图如下图所示。

(4分)三、公司A 、B 、C 三个股东,分别占有50%、30%和20%的股份,试用一片3线-8线译码器74HC138和若干门电路设计一个三输入三输出的多数表决器,用于开会时按股份大小记分输出通过、平局和否决三种表决结果。

通过、平局和否决,分别用X 、Y 、Z 表示(股东赞成和输出结果均用1表示)。

(12分)解:ABC XYZ 000 001 001 001 010 001 011 010 100 010 101 100 110 100 111100//7/6/5765//)(m m m m m m ABC ABC C AB X =++=++= //4/343///)(m m m m ABC C AB BC A Y =+=++=//2/1/0210///////)(m m m m m m BC A C B A C B A Z =++=++=(3)画连线图(4分)令74HC138的地址码210,,A A A B A C ===四、某学校学生参加三门课程A 、B 、C 的考试,根据课程学时不同,三门课程考试及格分别可得2、4、5分,不及格均为0分,若总得分大于等于7分,便可结业。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

用译码器设计组合逻辑电路例题、用3线—8线译码器74HC138和门电路实现逻辑函数

^A/B/C/A/BC/ABC。

(要求写出过程,画出连接图)(本题10分)

Y° Y t Y2 Y3 Y4 Y5Y B Y7

74HC138

A] A A Q字昼

\ r ~Q Q ~

解:

(1)74HC138的输出表达式为:(2分)

Y i/ =m((i =0 〜7)

(2)将要求的逻辑函数写成最小项表达式:(2分)

Y = A/B/C/ A/ BC/ ABC 二m0 m2 m7 = (m0m1/m7)/

(3)将逻辑函数与74HC138的输出表达式进行比较:设A= A2、B= A1、C= A o,得:Y =(m0m;m7)/ = (Y/Y^Y^)'(2分)

(4)可用一片74HC138再加一个与非门就可实现函数。

其逻辑图如下图所示。

(4分)

Y o Y1 Y; Y3 Y4 Y5 Y6 Y;

74HC138

A? A[ A o S1 S2 S3 r ~7"

ABC +5V

三、公司A B C 三个股东,分别占有50% 30唏口 20%勺股份,试用一片3线-8 线译码器74HC138和若干门电路设计一个三输入三输出的多数表决器, 用于开会 时按股份大小记分输出通过、平局和否决三种表决结果。

通过、平局和否决,分 别用X 、丫、Z 表示(股东赞成和输出结果均用1表示)。

(12分) Y c Y 1 Y 2 Y 3 Y 4 Y 5 Y S Y 7

74HC138

A :, A. Ai S? S*

X = AB /C ABC / ABC = m 5 m 6 m 7 = (m 5m 6m 7)/ 丫二 A ’BC AB /C / ABC 二 m 3 m 4 =

Z = A /B /C / ' A / B /C A /BC / = m 0

m t 二(m 0m 1 m 2)/ (3)画连线图(4分)

令 74HC138的地址码 A^AA^B'A^C

ABC

XYZ 000

001 001

001 010

001 011

010 100

010 101

100 110

100 111 100

解:

(1)列写真值表(4

分) (2)列写表达式(4

分)

四、某学校学生参加三门课程A、B、C的考试,根据课程学时不同,三门课程考试及格分别可得2、4、5分,不及格均为0分,若总得分大于等于7分,便可结业。

试用3线一8线译码器74HC138和门电路实现该逻辑功能。

(15分)

解:

(1)、列写真值表:(6分)

课程及格用1表示,不及格用0表示;可以结业用1表示,不能结业用0表示。

ABC Y

0 0 00

0 0 10

0 1 00

0 1 11

1 0 00

1 0 11

1 1 00

1 1 11

(2)、列写表达式(4分)

丫二A,BC AB,C …ABC 二m3 m5 m7二(m3m5m7)/

(3)、画连线图(5分)

令74HC138的地址码煦= 41\=3,&=0

3、试用两片双四选一数据选择器74HC153 —片3线-8线译码器74HC138与个四输入或门接成16选1的数据选择器(不能另加器件)。

74HC138与74HC153 的逻辑图如图(a)、(b)所示。

设计要求:(1)写出设计思路及每个器件在设计中的作用;

(2)画出连线图。

(13分)

A-;Aq S-j S Q S-i

解:设计思路:

(1)选用74HC138来控制四个四选一数据选择器的选通控制端,所以16选一数据选择器的高两位地址作为138的输入信息;(7分)

(2)16选一数据选择器的低两位地址作为两片74HC153勺地址码输入,两片

74HC153俞入16个待选数据。

(4分)

(3)两片74HC153勺四个输出端作为四输入或门的输入,该或门的输出即为

16选一数据选择器的输出。

(2分)。