简易数字钟设计(已仿真)

简易数字钟的设计

中文摘要数字钟已经成为人们日常生活中不可缺少的必需品,广发应用于家庭及办公室等公共场所,给人们的生活、学习、工作及娱乐带来了极大的方便。

由于数字集成电路技术的发展和采用了先进的石英技术,使得数字钟具有走时准确、性能稳定、携带方便等优点,它还用于计时、自动报时及自动控制等各个领域。

尽管目前市场上已有现成的数字钟集成电路芯片出售,价格便宜、使用方便,但鉴于单片机的定时器功能也可以完成数字钟的设计,因此进行数字的设计是必要的。

在这里我们将已学过的比较零散的数字电路的知识有机的、系统的联系起来用于实际,来培养我们的综合分析和设计电路,写程序、调试电路的能力。

单片机具有体积小、功能强、可靠性高、价格低廉等一系列优点,不仅已成为工业测控领域普遍采用的智能化控制工具,而且已渗入到人们工作和生活的各个角落,有力地推动了各行各业的技术改造和产品的更新换代,应用前景广阔。

本次做的数字钟是以单片机(AT89C51)为核心,结合相关的元器件(共阴极LED 数码显示器等),再配以相应的软件,达到制作简易数字钟的目的。

硬件部分采用了单片机原理实验室的实验箱进行合理接线调试;软件部分通过keil进行了C程序的修改编译,protues软件仿真等。

最终在实验箱上实现了与仿真结果相同的实际效果。

关键词单片机定时功能、AT89C51、共阴LED、Keil、Protues软件。

AbstractMicroelectronics and computer technology along with the rapid development and progress, making the design of electronic systems and applications have entered a new era. The traditional manual design process is being advanced electronic design automation technology to replace. And is currently supporting modern technology has become the universal platform for electronic design, and step by step to support the development of system-level design. Only to hardware description language and logic synthesis-based top-down design methodology to meet the increasingly complex needs of digital system design. The progressive development of the taxi industry, the taxi meter is getting higher and higher requirements, the user requires not only the performance of the stability of billing, billing and accurate anti-cheat functions; and as a result of the instability in oil prices, billing system the need for regular adjustment of the meter so that users can request not to change the hardware to facilitate the billing system modifications.The system is the use of language, it can make use of digital circuits and system description, simulation and automatic design, and software as a development platform designed billing system procedures taxi and carried out a simulation program. To the achievement of pre-billing and simulation, as well as car to start, stop, pause and other functions, and dynamic scan shows the number of fares.Key Words Microcontroller\、AT89C51、7SEG-MPX6-CC-RED 、Keil、Proteus目录中文摘要 (I)Abstract (II)目录......................................................................................................................................... I II 1设计任务描述.. (1)1.1设计题目:简易数字钟的设计 (1)1.2 设计要求: (1)1.2.1 设计目的 (1)1.2.2 基本要求 (1)2设计思路 (2)3设计方框图 (3)3.1数字钟硬件部分示意图 (3)3.2数字钟软件部分组成框图 (4)3.2.1时间调整的程序流程 (4)3.2.2时钟显示程序流程 (5)4各部分模块介绍 (6)4.1单片机AT89C51芯片分析 (6)4.2晶振电路模块 (7)4.3复位电路模块 (7)4.4显示模块 (8)4.5时间校对按键模块 (9)5简易数字钟源程序 (10)5.1源程序 (10)6数字钟源程序的仿真 (15)6.1编译、连接 (15)6.2仿真 (16)6.2.1生成HEX文件 (16)6.2.2仿真结果 (16)7数字钟硬件原理图 (17)7.1总原理图 (17)8主要原器件清单 (18)小结 (19)致谢 (20)参考文献 (21)1 设计任务描述1.1 设计题目:简易数字钟的设计1.2 设计要求:1.2.1 设计目的熟练使用Keil开发环境,具备编写单片机程序(汇编语言或C语言)的初步能力,通过完成本课题的软硬件设计,使同学们了解单片机实例的整个开发流程。

简易数字钟的设计

第三单元简易数字钟的设计数字钟是一种用数字显示秒、分、时的计时装置,与传统的机械钟相比,它具有走时准确、显示直观、无需机械传动等优点。

因而得到了广泛的应用。

小到人们日常生活中的电子手表,大到车站、码头、机场等公共场所的大型数字电子钟,数字钟到处可见。

在数字电路的学习中,已经学习过用计数器芯片搭建数字钟。

51单片机内部集成了定时器/计数器,这为构建数字钟带来了方便。

在本单元中,学习如何用51单片机来构建一个功能数字钟。

【任务要求】➢在6个数码管上显示时、分、秒,共6位数字。

➢通过单片机内部定时器控制走时,走时准确。

➢系统有四个按键,功能分别是调整时间,加,减,确定。

在按下调整键时候,显示“时”的两位数码管以1 Hz 频率闪烁。

如果再次按下调整键,则“分”开始闪烁,“时”恢复正常显示,依次循环,直到按下确定键,恢复正常的显示。

在数码管闪烁的时候,按下加或者减键可以调整相应的显示内容。

按键支持短按和长按,即短按时,所修改的数字每次增加1或者减小1,长按时候以一定速率连续增加或者减少10。

【学习知识点】➢数码管的原理,驱动程序的实现。

➢51单片机内部定时器的原理及应用➢独立按键的原理及程序的实现。

【内容安排】第一节:数码管显示原理及应用实现第二节:独立按键检测原理及应用实现第三节:计时的原理及实现第四节:基于定时器的程序改进第五节:数字钟的构建第一节数码管显示原理及应用实现1.1 数码管显示原理数字钟要把时间显示到数字显示装置上,常用的数字显示装置有数码管、液晶、LED、CRT显示器等。

在单片机系统设计中,LED数码管是最基本的显示装置。

在数字钟的设计中我们用数码管对中的小时、分和表来进行显示。

LED数码管能显示各种数字或符号,由于它具有显示清晰、亮度高、寿命长、价格低廉等特点,因此使用非常广泛。

图1.1是几个数码管的图片:a图为单位数码管, b图为双位数码管,c图为四位数码管。

a 单位数码管b 双位数码管c 四位数码管图1.1 数码管图片那么数码管是如何的工作呢?还记得我们小时候玩过的“火柴棒游戏”吗,几根火柴组合起来,可以拼成各种各样的图形,数码管实际上就是利用这个原理做成的。

数字钟设计(带仿真和连接图)

数字电子技术课程设计报告题目:数字钟的设计与制作专业:电气本一班学号:姓名:指导教师:时间:一、设计内容数字钟设计技术指标:(1)时间以24小时为周期;(2能够显示时,分,秒;(3)有校时功能,可以分别对时及分进行单独校时,使其校正到标准时间;(4)计时过程具有报时功能,当时间到达整点前5秒进行蜂鸣报时;(5)为了保证计时的稳定及准确须由晶体振荡器提供表针时间基准信号.二、设计时间:第十五、十六周三、设计要求:(1)画出设计的电路原理图;(2) 选择好元器件及给出参数,在原理图中反应出来;(3)并用仿真软件进行模拟电路工作情况;(4)编写课程报告。

摘要数字钟实际上是一个对标准频率(1Hz)进行计数的计数电路。

振荡器产生的时钟信号经过分频器形成秒脉冲信号,秒脉冲信号输入计数器进行计数,并把累计结果以“时”、“分”、“秒”的数字显示出来。

秒计数器电路计满60后触发分计数器电路,分计数器电路计满60后触发时计数器电路,当计满24小时后又开始下一轮的循环计数。

一般由振荡器、分频器、计数器、译码器、数码显示器等几部分组成。

振荡电路:主要用来产生时间标准信号,因为时钟的精度主要取决于时间标准信号的频率及稳定度,所以采用石英晶体振荡器。

分频器:因为振荡器产生的标准信号频率很高,要是要得到“秒”信号,需一定级数的分频器进行分频。

计数器:有了“秒”信号,则可以根据60秒为1分,24小时为1天的进制,分别设定“时”、“分”、“秒”的计数器,分别为60进制,60进制,24进制计数器,并输出一分,一小时,一天的进位信号。

译码显示:将“时”“分”“秒”显示出来。

将计数器输入状态,输入到译码器,产生驱动数码显示器信号,呈现出对应的进位数字字型。

由于计数的起始时间不可能与标准时间(如北京时间)一致,故需要在电路上加一个校时电路可以对分和时进行校时。

另外,计时过程要具有报时功能,当时间到达整点前10秒开始,蜂鸣器1秒响1秒停地响5次。

设计制作电子时钟

设计制作简易数字钟一、设计要求1、设计一振荡源,用于产生1Hz的脉冲信号;2、能完成从00时00分00秒到23时59分59秒走时,并实时显示时、分、秒;3、具有手动校时、校分、校秒功能。

发挥部分:具有正点报时功能。

要求在59分58秒开始报时,持续5秒钟。

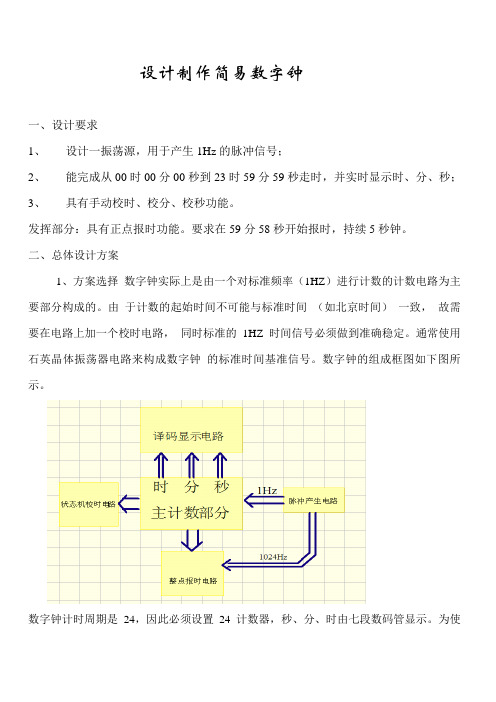

二、总体设计方案1、方案选择数字钟实际上是由一个对标准频率(1HZ)进行计数的计数电路为主要部分构成的。

由于计数的起始时间不可能与标准时间(如北京时间)一致,故需要在电路上加一个校时电路,同时标准的1HZ 时间信号必须做到准确稳定。

通常使用石英晶体振荡器电路来构成数字钟的标准时间基准信号。

数字钟的组成框图如下图所示。

数字钟计时周期是24,因此必须设置24 计数器,秒、分、时由七段数码管显示。

为使数字钟走时与标准时间一致,校时电路是必不可少的。

设计中采用状态机控制校时,通过切换开关用秒脉冲或手动按键产生脉冲先后对“时” “分” “秒”计数器进行校时操作。

2、数字钟的构成(1)数字钟的构成:振荡器、分频器、计数器、译码器、LED数码管显示器等几部分。

附加功能的实现还需采用T’触发器及与门和或门及蜂鸣器组成报时电路。

(2)数字钟的时、分、秒实际上就是由一个24 进制计数器(00-23),两个60 进制计数器(00-59)级联构成。

设计数字钟实际上就是计数器的级联。

(3)芯片选型:由于24进制、60进制计数器均由集成计数器级联构成,且都包含有基本的十进制计数器,从设计简便考虑,芯片选择十进制计数器74LS390。

3、元器件列表:型号74LS00、74LS04、74LS08、74LS21、74LS32、74LS47、74LS74、74LS86、74LS390、CD4068、CD4060、CD4511。

晶体管8050、510欧姆电阻、LED、轻触开关、自锁开关、蜂鸣器、10p电容、晶振32768、10M电阻。

三、系统工作原理1、主计数部分原理图图1主计数部分原理图如图所示,用两个十进制计数器74LS390组成60进制计数器和24进制计数器,分别用于对分、秒和时的计数。

数字时钟仿真设计

基于multisim 10.0的数字时钟仿真设计一、设计目的1、综合运用数字电路的知识,掌握数字时钟的设计方法。

2、掌握计数器、译码器、分频器的设计原理和设计方法。

3、掌握运用仿真软件multisim 10.0设计综合数字电路的方法。

二、设计意义数字时钟是用数字集成电路构成的、用数码显示的一种现代计时器,与传统机械表相比,它具有走时准确、校时方便、显示直观、无机械传动装置等特点,因而广泛应用于车站、码头、机场、商店等公共场所。

在控制系统中,数字时钟也常用来做定时控制的时钟源。

三、设计要求1、设计一个具有时、分、秒的十进制数字显示的计时器。

2、具有手动校时、校分的功能。

3、通过开关能实现小时的十二进制和二十四进制转换。

4、具有整点报时的功能。

5、用74系列集成电路设计实现6、电路实现的各功能部分用子电路表示。

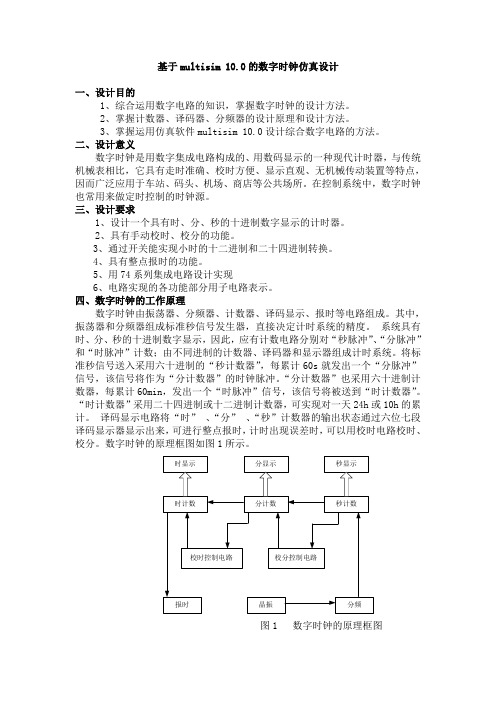

四、数字时钟的工作原理数字时钟由振荡器、分频器、计数器、译码显示、报时等电路组成。

其中,振荡器和分频器组成标准秒信号发生器,直接决定计时系统的精度。

系统具有时、分、秒的十进制数字显示,因此,应有计数电路分别对“秒脉冲”、“分脉冲”和“时脉冲”计数;由不同进制的计数器、译码器和显示器组成计时系统。

将标准秒信号送入采用六十进制的“秒计数器”,每累计60s就发出一个“分脉冲”信号,该信号将作为“分计数器”的时钟脉冲。

“分计数器”也采用六十进制计数器,每累计60min,发出一个“时脉冲”信号,该信号将被送到“时计数器”。

“时计数器”采用二十四进制或十二进制计数器,可实现对一天24h或10h的累计。

译码显示电路将“时”、“分”、“秒”计数器的输出状态通过六位七段译码显示器显示出来,可进行整点报时,计时出现误差时,可以用校时电路校时、校分。

数字时钟的原理框图如图1所示。

图1 数字时钟的原理框图五、单元电路设计单元电路分为小时计时模块、分钟和秒计时模块、整点译码电路、时钟产生电路、校时电路等。

待单元电路设计完成后,将各单元电路进行封装连接得到总体电路,进行总体电路的仿真、调试,最终完成数字时钟的设计。

简易数字时钟实验报告

简易数字时钟实验报告简易数字时钟实验报告引言:在现代社会中,时钟是人们生活中不可或缺的一部分。

无论是在家庭、学校还是工作场所,时钟都扮演着重要的角色。

然而,我们是否曾想过时钟是如何工作的呢?为了更好地理解时钟的原理和机制,我们进行了一项简易数字时钟实验。

实验目的:本实验的目的是通过制作一个简易的数字时钟来了解时钟的工作原理和数字显示技术。

实验材料:1. Arduino Nano开发板2. 数字时钟模块3. 面包板4. 连接线5. 电源适配器实验步骤:1. 将Arduino Nano开发板插入面包板上,并连接好电源适配器。

2. 将数字时钟模块与Arduino Nano开发板通过连接线连接起来。

3. 编写Arduino代码,实现数字时钟的显示功能。

4. 将编写好的代码上传到Arduino Nano开发板上。

5. 打开电源适配器,观察数字时钟是否能够正常显示时间。

实验结果:经过一番努力,我们成功地制作出了一个简易的数字时钟。

当我们打开电源适配器时,时钟模块上的数字显示屏幕亮起,并显示出当前的时间。

我们可以清晰地看到小时数、分钟数和秒数的变化。

这让我们深刻地认识到时钟背后的复杂工作原理和数字显示技术的重要性。

实验分析:通过这个实验,我们了解到数字时钟的工作原理是基于微控制器的。

Arduino Nano开发板作为一个微控制器,通过接收来自时钟模块的信号,然后将这些信号转化为可读的数字显示。

数字时钟模块内部包含了一系列的LED灯,通过控制这些LED灯的亮灭来显示时间。

同时,Arduino代码也起到了关键的作用,它将接收到的信号进行处理,并将处理后的结果发送给数字时钟模块进行显示。

实验心得:通过这个实验,我们不仅仅了解了数字时钟的工作原理和数字显示技术,还学习到了如何使用Arduino开发板和编写Arduino代码。

这个实验不仅提高了我们的动手能力,还培养了我们的逻辑思维和问题解决能力。

同时,我们也深刻认识到了科学实验的重要性,它能够帮助我们更好地理解和掌握知识。

数字钟的设计与仿真

综合实践(论文)题目数字钟学院通信与电子工程学院专业班级学生姓名学生学号指导教师摘要:本次设计主要是利用数字电路实验箱上的74LS160、555定时器、74LS00与七段显示译码器设计简易数字钟,实现准确计时,以数字形式显示时、分、秒的时间和校时功能。

由于采用纯数字硬件设计制作,与传统机械表相比,它具有走时准、显示直观、无机械传动装置等特点。

它的小时周期为12,分和秒的周期为60。

关键字:数字时钟时计数器分计数器秒计数器校时器目录摘要: (I)第1章绪论 (1)1.1 设计要求 (1)1.2 设计任务 (1)第2章总体框图 (2)2.1 总体框图 (2)2.2 设计思路及模块功能 (2)第3章选择器件 (3)3.1 74LS160(本实验需要6片) (4)3.2 74LS04(本实验需要1片) (6)3.3 74LS00(本实验需要2片) (7)3.4 74LS20(本实验需要1个) (8)3.5 LED(本实验需要6个) (9)3.6 三极管8099(本实验需要1个) (11)3.7 小灯泡(本实验需要1个) (11)第4章功能模块 (13)4.1 秒脉冲发生器 (13)4.2 计数译码显示 (13)4.3 整点报时电路 (17)第 5章总体设计电路图 (19)结论 (21)参考文献 (22)附录 (23)第1章绪论1.1 设计要求能进行正常的时,分,秒计时功能,分别由6个数码管显示24h,60min,60s.Sb键进行校时:按下Sh键时,时计数器一秒速度递增,并按24循环,记满23后再回00.Sm键进行校分:按下Sm键时,分计时器以秒速度递增,并按60计数循环,记满59后再回00,但不能向“时”进位。

Sc键进行秒清零:按下Sc键时,可对秒清零。

扬声器整点报时:当计时器达59'51、59'53、59'55及59'57时,鸣叫声频率为500Hz;到达59'59是为最后一声整点报时,频率为1k Hz。

设计一个能显示时、分、秒的简易数字钟

数字电子技术课程设计报告要求:设计一个能显示时、分、秒的简易数字钟。

步骤:用verilog语言在记事本编写程序,再用QuartusⅡ仿真,定义针脚,在面板上模拟。

数字钟是一种用数字电路技术实现时、分、秒计时的装置,与机械式时钟相比具有更高的准确性和直观性,且无机械装置,具有更长的寿命,因此得到广泛的应用。

设计原理及框图数字钟实际上是一个对标准频率(1HZ)进行计数的计数电路,具有时、分、秒计数显示功能,以24小时为计数循环。

这次实验主要是要实现时钟的计时功能,时间计数由秒个位和秒十位计数器,分个位和分十位计数器及时个位和时十位计数器,,其中秒个位和秒十位计数器,分个位和分十位计数器为60进制计数器,而根据设计要求,时个位和时十位计数器为24进制计数器.,然后需要把8位二进制数转变为译码管需要的8421码。

设计方案:这个实验总体分:秒、分、时三个模块,计时和较准两个模式标准秒信号送入“秒计数器”,“秒计数器”采用60进制计数器,每累计60秒发出一个“分脉冲”信号,该信号将作为“分计数器”的时钟脉冲之一。

“分计数器”也采用60进制计数器,每累计60分钟,发出一个时脉冲信号,该信号作为时计数器的时钟脉冲之一,时计数器采用24进制计时器,可实现对一天24小时的计时。

译码显示电路将“时”、“分”、“秒”计数器的输出状态通过译码管显示。

这们时钟的计时功能就实现了,秒模块是一个以1HZ的clock信号控制的60进制计数器,并同时产生分进位信号tun。

always @(posedge clock)beginif(sec==59) \\当秒等于59时,如果处于计时模式时产生begin \\一个进位脉冲tun, 否则tun信号暂停sec<=0;tun<=1;elsetun<=tun;endelse \\若秒不等于59,同样如果处于计时模式begin \\就使tun信号清0,否则tun信号暂停sec<=sec+1;if(at==0)tun<=0;elsetun<=tun;endend分模块也是一个60进制计数器,并产生小时的进位信号mod,但要受到两个控制信号的控制一个是进位信号tun,另一个是t_min的按建信号。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

简易数字钟设计

摘 要 本文针对简易数字钟的设计要求,提出了两种整体设计方案,在比较两个方案的优缺点后,选择了其中较优的一个方案,进行由上而下层次化的设计,先定义和规定各个模块的结构,再对模块内部进行详细设计。

详细设计的时候又根据可采用的芯片,分析各芯片是否适合本次设计,选择较合适的芯片进行设计,

最后将设计好的模块组合调试,并最终在EWB 下仿真通过。

关键词 数字钟,EWB ,74LS160,总线,三态门,子电路

一、引言:所谓数字钟,是指利用电子电路构成的计时器。

相对机械钟而言,数字钟能达到准确计时,并显示小时、分、秒,同时能对该钟进行调整。

在此基础上,还能够实现整点报时,定时报闹等功能。

设计过程采用系统设计的方法,先分析任务,得到系统要求,然后进行总体设计,划分子系统,然后进行详细设计,决定各个功能子系统中的内部电路,最后进行测试。

二、任务分析:能按时钟功能进行小时、分钟、秒计时,并显示时间及调整时间,能整点报时,定点报时,使用4个数码管,能切换显示。

总体设计

本阶段的任务是根据任务要求进行模块划分,提出方案,并进行比较分析,最终找到较优的方案。

方案一、采用异步电路,数据选择器

将时钟信号输给秒模块,秒模块的进位输给分模块,分模块进位输入给时模块,切换的时候使用2选1数据选择器进行切换,电路框图如下:

该方案的优点是模块内部简单,基本不需要额外的电路,但缺点也很明显,该方案结构不清晰,模块间关系混乱,模块外还需使用较多门电路,不利于功能扩充,且使用了异步电路,计数在59的时候,高一级马上进位,故本次设计不采用此方案。

方案二、采用同步电路,总线结构

时钟信号分别加到各个模块,各个模块功能相对独立,框图如下: 显示 切换

秒钟

分钟 小时 控制

1Hz 脉冲信号

闹钟

该方案用总线结构,主要功能集中在模块内部,模块功能较为独立,模块间连线简单,易于扩展,本次设计采用此方案。

综上所述,本次设计采用方案二。

秒计数和分计数为60进制,时计数为24进制,为了简化设计,秒和分计数采用同一单元。

控制模块有两部分,一为实现调整切换,二为实现显示切换。

现对本方案中的各个主要功能模块的接口定义如下:

1. 60进制模块(电路图中模块名称为60count ,下同。

)

实现同步60进制计数,可调整 电源 5v

时钟信号输入

接1Hz 的信号源 进位输入

接秒的进位信号,实现秒功能时,接低电平。

进位输出

秒模块接分模块,分模块接时模块 显示输出

接到显示总线,能闪烁 闹钟比较信号输出

接到闹钟,秒模块悬空 整点报时信号输出

接到响铃,实现3短1长响铃 调整使能端

入0有效,有效时,显示信号输出,同时屏蔽进位输入和进位输出,允许调整信号输入。

显示使能端

入0有效 调整信号输入

2. 24进制模块(24count )

实现同步24进制计数,可调整

电源,时钟信号

同上 进位输入

接分的进位信号 进位输出

秒模块接分模块,分模块接时模块 显示输出

同上 闹钟比较信号输出 接到闹钟

闹钟 小时 分钟 秒钟

显示

控制

显示总线

控制总线

1Hz 信号

调整使能端,显示使

同上

能端,调整信号输入

3.闹钟模块(60clock,24clock)

实现可与时钟比较,并输出闹铃信号,可调整

电源,时钟信号同上

闹钟比较信号输入秒模块接分模块,分模块接时模块

显示输出同上

闹铃输出接到蜂鸣器

同上

调整使能端,显示使

能端,调整信号输入

4.控制模块(fun,func)

管理总线资源,对各个模块输出控制信号

电源5v VCC

调整切换信号接各个需要调整的模块

调整信号接到各个需要调整的模块

显示切换信号接到各个需要共享显示总线的模块

控制信号输出接到各个模块,有且只能有1个为0

至此,本阶段就结束了。

在上面的接口定义中,也可以发现,各个模块的独立性是很强的,这样的结构使得以后的扩展很容易。

二、详细设计

在上一阶段进行总体设计完成后,现在就可以分开独立的完成各个功能模块了。

本阶段主要问题在于计数器的设计,计数部分需要24进制和60进制计数器,控制部分需要循环计数器。

由于标准集成计数器没有所需进制,需要编程实现。

首先,需要选择使用集成芯片,总体思路是在满足所需功能前提下,能是电路尽可能简单。

有以下方案:

1.采用74160

该芯片管脚及功能表如图所示:74160为异步复位,同步置数,ENP,ENT同

时为一时才可以计时,其中之一为高电平时,则保持。

RCO产生进位信号。

74160相对于其他芯片来说,功能较少,使用简单,但是也因功能简单导致在实现数字钟的某些特定功能时需要加入比较多的附加电路。

如74160没有减计数的功能,须寻求其他方法来解决,设计较复杂。

,由于不准备设计减计数,在功能能满足要求的前提下,该芯片使用简单,适合此次设计。

2.采用74190

芯片管脚图及真值表如图所示:可知,74190上升

沿触发,由U/D’控制加减计数,有异步置数段LO

AD,没有复位端,RCO输出低电平的进位或借位

信号,MAX/MIN在为9或0时输出高电平,C

TEN高电平时保持。

74190的功能相当强,但也因此

使用复杂,不利于电路的简化,且该芯片没有复位端,

不利于某些功能的实现。

由于本次设计不使用加减计

数,该芯片有较多多余功能,不采用。

3.采用74192

管脚图和真值表如图所示:可知,74192上

升沿触发,由UP,DOWN两管脚控制加减计

数,有异步置数端LOAR和异步复位端CL

R,BO’和CO’分别输出高电平表示加进位

和减进位。

74192功能可以完成本次设计目标,

但如果不设计减计数的话则有许多多余管脚,使

用复杂,基于简单原则,本设计不采用。

综上所述,本次设计采用74160作为主要芯片。

本次设计还要使用循环计数器,采用74160与74138

构成。

74138的管脚图和真值表如图:输出信号中只有一

条为低电平,其余为高电平,与74160组合使用后,可

产生满足要求的控制信号。

至此,可以根据总体设计中对子模块的定义,对各个模块进行单独设计了。

设计过程中可对单个模块进行调试,调试通过后,打包成模块(子电路),方便以后使用。

(详细电路图附在文后)

三、组装电路并调试

在经过前面几个阶段的设计后,数字钟的各个模块已经设计完毕,根据总体设计时的方案框图,将各个子电路组合起来,加入1Hz的时钟信号,对电路进行总体测试。

经测试,电路可以正常计时,并显示,调整无误。

将时间调整到23:59,闹钟调到00:01分,进行测试,时钟进位正常,有整点报时,报时为3短1长,闹铃正常,响铃持续1分钟,中间可按调整键关闭闹铃。

四、缺陷及改进

1.只能进行加调整,要进行减调整几乎不可能在现有电路基础上改进,只能重新设计,

这是一开始就没考虑到的。

2.分钟和秒使用同一功能模块,简化了设计,但对秒计时来说,该模块有较多不需要

的功能,在实际生产的时候,应该分开设计。

3.为了方便使用,可以将控制模块输出的控制信号接到LED指示灯上,指明当前所

在的状态。

五、心得体会

经过长达两个星期的设计与思考,最终在EWB上完成了数字钟的模拟。

其间遇到了许多问题,但最后都一一得到解决。

现将心得体会总结如下:

1.设计初期要考虑周到,否则后期改进很困难。

应该在初期就多思考几个方案,进行

比较论证,选择最合适的方案动手设计。

总体设计在整个设计过程中非常重要,应

该花较多的时间在上面。

2.方案确定后,才开始设计。

设计时,多使用已学的方法,如列真值表,化简逻辑表

达式,要整体考虑,不可看一步,做一步。

在整体设计都正确后,再寻求简化的方

法。

3.在设计某些模块的时候无法把握住整体,这时可以先进行小部分功能的实现,在此

基础上进行改进,虽然可能会多花一些时间,但这比空想要有效的多。

4.尽可能是电路连线有序,模块之间关系清楚,既利于自己修改,也利于与别人交流。

如果电路乱的连自己都看不懂,那还如何改进和扩展。

5.很多难点的突破都来自于与同学的交流,交流使自己获得更多信息,开拓了思路,

因此要重视与别人的交流。

6.应该有较好的理论基础,整个实验都是在理论的指导下完成了,设计过程中使用了

许多理论课上学的内容,如真值表、卡拉图等。

本次设计把理论应用到了实践中,

同时通过设计,也加深了自己对理论知识的理解和掌握。

参考资料

[1] EWB5.0 自带帮助文档

[2] 清华大学教研组编,阎石主编:《数字电子技术基础》(第四版),北京,高等教育

出版社,2004年

作者简介陈晓炜,厦门大学信息科学与技术学院,通信工程系本科三年级,学号03142007。

附录一使用说明

1.调整时间

按L键切换到调整小时,或调整分钟,按J键调整。

2.调整闹钟

按L键切换到调整闹钟小时,调整闹钟分钟,按J键调整。

闹铃时候,按J键可以关闭闹铃。

3.切换显示

按T键切换显示秒,闹钟。