verilog 分频器,30s计数器及交通灯控制器设计

Verilog实现任意分频

Verilog实现任意分频在Verilog中实现任意分频可以通过使用计数器和分频比例来实现。

下面是一个基于计数器的Verilog代码示例,用于实现任意分频。

```verilogmodule frequency_dividerinput clk,input rst,input [7:0] div_ratio,output reg outreg [7:0] count;beginif (rst)count <= 0;else if (count == div_ratio - 1)count <= 0;elsecount <= count + 1;endbeginif (rst)out <= 0;else if (count == div_ratio - 1)out <= ~out;endendmodule```在以上代码中,我们定义了一个名为"`frequency_divider`"的模块,该模块具有以下输入和输出:- `clk`:时钟信号- `rst`:复位信号- `div_ratio`:分频比例,使用8位二进制表示,范围为0到255- `out`:输出信号我们使用一个8位计数器(`count`)来进行分频。

每当计数器达到分频比例减1时,输出信号取反。

例如,如果分频比例为1,则输出信号将与时钟信号同步;如果分频比例为2,则输出信号将是时钟信号的一半频率;如果分频比例为4,则输出信号将是时钟信号的四分之一频率,以此类推。

需要注意的是,以上示例代码仅展示了分频的基本原理,并未考虑输入和输出信号的时序问题,如使 `div_ratio` 在运行时可更改、输出信号的不稳定性等。

针对具体应用需求,可以根据实际情况做出适当的修改和调整。

希望以上内容对您有所帮助!。

verilog课程设计交通灯

verilog课程设计交通灯一、教学目标本节课的教学目标是使学生掌握Verilog HDL的基本知识,能够使用Verilog编写简单的交通灯控制系统。

具体来说,知识目标包括理解Verilog的基本语法、模块化设计方法以及状态机的设计原理;技能目标包括能够使用Verilog编写交通灯控制器的代码,并能够进行仿真测试;情感态度价值观目标包括培养学生的团队合作意识,提高他们对电子工程的兴趣。

二、教学内容本节课的教学内容主要包括Verilog基础知识、模块化设计方法、状态机设计原理以及交通灯控制系统的实现。

具体来说,首先介绍Verilog的基本语法,包括数据类型、运算符、语句等;然后讲解模块化设计方法,如何将复杂的系统分解为简单的模块,并介绍模块的调用和连接;接着介绍状态机的设计原理,如何根据状态转移图编写状态机的Verilog代码;最后,通过实例讲解如何使用Verilog编写交通灯控制系统的代码,并进行仿真测试。

三、教学方法为了达到本节课的教学目标,将采用多种教学方法相结合的方式进行教学。

首先,通过讲授法,为学生讲解Verilog的基本语法、模块化设计方法和状态机设计原理;然后,通过案例分析法,分析交通灯控制系统的实现过程,让学生加深对知识的理解;接着,通过实验法,让学生动手编写交通灯控制器的Verilog代码,并进行仿真测试,提高他们的实践能力;最后,通过讨论法,让学生分享自己的学习心得,培养他们的团队合作意识。

四、教学资源为了支持本节课的教学内容和教学方法的实施,将准备以下教学资源:教材《Verilog HDL Primer》和相关参考书,用于讲解Verilog的基本语法和设计方法;多媒体教学课件,用于展示交通灯控制系统的原理和实现过程;实验设备,包括计算机和仿真器,用于让学生动手编写代码并进行仿真测试。

此外,还将提供在线编程平台,让学生可以随时随地编写代码并进行调试。

五、教学评估本节课的教学评估将采用多元化的评估方式,以全面、客观、公正地评价学生的学习成果。

实验六 Verilog设计分频器计数器电路答案

实验六Verilog设计分频器/计数器电路一、实验目的1、进一步掌握最基本时序电路的实现方法;2、学习分频器/计数器时序电路程序的编写方法;3、进一步学习同步和异步时序电路程序的编写方法。

二、实验内容1、用Verilog设计一个10分频的分频器,要求输入为clock(上升沿有效),reset(低电平复位),输出clockout为4个clock周期的低电平,4个clock周期的高电平),文件命名为fenpinqi10。

v.2、用Verilog设计一异步清零的十进制加法计数器,要求输入为时钟端CLK(上升沿)和异步清除端CLR(高电平复位),输出为进位端C和4位计数输出端Q,文件命名为coute r10.v。

3、用Verilog设计8位同步二进制加减法计数器,输入为时钟端CLK(上升沿有效)和异步清除端CLR(低电平有效),加减控制端UPDOWN,当UPDOWN为1时执行加法计数,为0时执行减法计数;输出为进位端C和8位计数输出端Q,文件命名为couter8.v。

4、用VERILOG设计一可变模数计数器,设计要求:令输入信号M1和M0控制计数模,当M1M0=00时为模18加法计数器;M1M0=01时为模4加法计数器;当M1M0=10时为模12加法计数器;M1M0=11时为模6加法计数器,输入clk上升沿有效,文件命名为mcout5。

v。

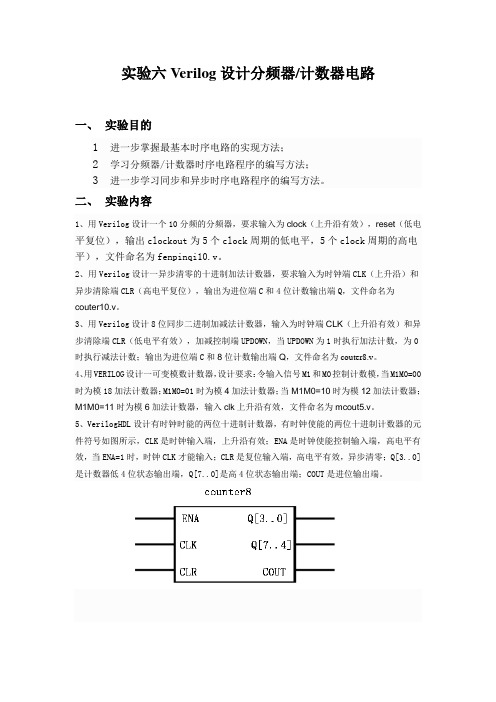

5、VerilogHDL设计有时钟时能的两位十进制计数器,有时钟使能的两位十进制计数器的元件符号如图所示,CLK是时钟输入端,上升沿有效;ENA是时钟使能控制输入端,高电平有效,当ENA=1时,时钟CLK才能输入;CLR是复位输入端,高电平有效,异步清零;Q[3.。

0]是计数器低4位状态输出端,Q[7..0]是高4位状态输出端;COUT是进位输出端.三、实验步骤实验一:分频器1、建立工程2、创建Verilog HDL文件3、输入10分频器程序代码并保存4、进行综合编译5、新建波形文件6、导入引脚7、设置信号源并保存8、生成网表9、功能仿真10、仿真结果分析由仿真结果可以看出clockout输出5个clock周期的低电平和5个clock的高电平达到10分频的效果,设计正确。

实验六Verilog设计分频器计数器电路

实验六Verilog设计分频器/计数器电路一、实验目的1进一步掌握最基本时序电路的实现方法;2学习分频器/计数器时序电路程序的编写方法;3进一步学习同步和异步时序电路程序的编写方法。

二、实验内容1、用Verilog设计一个10分频的分频器,要求输入为clock(上升沿有效),reset(低电平复位),输出clockout为5个clock周期的低电平,5个clock周期的高电平),文件命名为fenpinqi10.v。

2、用Verilog设计一异步清零的十进制加法计数器,要求输入为时钟端CLK(上升沿)和异步清除端CLR(高电平复位),输出为进位端C和4位计数输出端Q,文件命名为couter10.v。

3、用Verilog设计8位同步二进制加减法计数器,输入为时钟端CLK(上升沿有效)和异步清除端CLR(低电平有效),加减控制端UPDOWN,当UPDOWN为1时执行加法计数,为0时执行减法计数;输出为进位端C和8位计数输出端Q,文件命名为couter8.v。

4、用VERILOG设计一可变模数计数器,设计要求:令输入信号M1和M0控制计数模,当M1M0=00时为模18加法计数器;M1M0=01时为模4加法计数器;当M1M0=10时为模12加法计数器;M1M0=11时为模6加法计数器,输入clk上升沿有效,文件命名为mcout5.v。

5、VerilogHDL设计有时钟时能的两位十进制计数器,有时钟使能的两位十进制计数器的元件符号如图所示,CLK是时钟输入端,上升沿有效;ENA是时钟使能控制输入端,高电平有效,当ENA=1时,时钟CLK才能输入;CLR是复位输入端,高电平有效,异步清零;Q[3..0]是计数器低4位状态输出端,Q[7..0]是高4位状态输出端;COUT是进位输出端。

三、实验步骤:第一个实验:1、打开QuartusII,新建一个工程f_fenpinq10yjq2、新建一个Verilog HDL文件3、输入程序:module fenpinqi10(clk,reset,clkout);input clk,reset;output clkout;reg clkout;reg[2:0] cnt;always @(posedge clk , negedge reset)beginif(!reset)begin clkout<=0;cnt<=0;endelse if(cnt==4)begin cnt<=0;clkout<=~clkout;endelse cnt<=cnt+1;endendmodule4、设置顶层实体名(点settings>general >下拉选fenpinqi10)5、编译6、执行file>Create/Update>Create Symbol Files for Current Flie为VHDI设计文件生成原件符号7、建立波形文件8、导入引脚9、仿真结果如下:总结:仿真结果与实验一的题意相符,所以仿真正确。

verilog实验报告流水灯数码管秒表交通灯

流水灯实验目的:在basys2开发板上实现LED灯的花样流水的显示,如隔位显示,依次向左移位显示,依次向右移位显示,两边同时靠中间显示。

实验仪器:FPGA开发板一块,计算机一台。

实验原理:当一个正向的电流通过LED时,LED就会发光。

当阳极的电压高于阴极的电压时,LED就会有电流通过。

当在LED上增添一个典型值为1.5V—2.0V之间的电压时,LED就会有电流通过并发光。

实验内容:顶层模块:输入信号:clk_50MHz(主时钟信号),rst(重置信号),输出信号:[7:0] led(LED灯控制信号)。

module led_top(clkin,rst,led_out);input clkin, rst;output [7:0] led_out;wire clk_1hz;divider_1hz d0(clkin, rst, clk_1hz);led l0(clk_1hz, rst, led_out);endmodule分频模块:module divider_1hz(clkin,rst,clkout);input clkin,rst;output reg clkout;reg [24:0] cnt;always@(posedge clkin, posedge rst)beginif(rst) begincnt<=0;clkout<=0; endelse if(cnt==24999999) begincnt<=0;clkout=!clkout; endelse cnt<=cnt+1;endendmodule亮灯信号模块:module led(clkin,rst,led_out);input clkin,rst;output [7:0] led_out;reg [2:0] state;always@(posedge clkin, posedge rst)if(rst) state<=0;else state<=state+1;always@(state)case(state)3'b000:ledout<=8'b0000_0001;3'b001:ledout<=8'b0000_0010;3'b010:ledout<=8'b0000_0100;3'b011:ledout<=8'b0000_1000;3'b100:ledout<=8'b0001_0000;3'b101:ledout<=8'b0010_0000;3'b110:ledout<=8'b0100_0000;3'b111:ledout<=8'b1000_0000;endcaseendmodule实验中存在的问题:1 芯片选择问题automotive spartan3EXA3S100E XA3S250E CPG132spartan3EXC3S100E XC3S250E CP1322 时序逻辑部分,阻塞赋值和非阻塞赋值混用always@(posedge clk)begina=b+c;d<=e+f;end3 UCF文件格式错误NET “CLK” LOC = “B8”;NET “a” LOC = “N11”;NET “b” LOC = “G13”;NET “c[0]”LOC =“K11;数码管实验目的:设计一个数码管动态扫描程序,实现在四位数码管上动态循环显示“1”、“2”“3”“4”;实验仪器:FPGA开发板一块,计算机一台。

基于VHDL的交通灯控制器的设计

基于VHDL的交通灯控制器的设计一、设计目的1、掌握计数器、分频器、译码器的工作原理和设计方法;2、掌握数码管的动态扫描译码显示的工作原理和设计方法;3、掌握交通灯控制器的设计方法;4、掌握在EDA开发软件QuartusII环境下基于FPGA/CPLD的数字系统设计方法,掌握该环境下系统的功能仿真、时序仿真、管脚锁定和芯片下载的方法。

二、概述在城市的的十字路口处都设置有交通信号灯控制系统,这个系统由绿、黄、红信号灯指挥十字路口车辆和行人的正常通行。

其示意图如下所示:要支道主要干道S主要干道次要支道三、设计任务与要求设计一个主要干道和次要支道交叉路口处的交通信号灯控制器,其技术要求如下:1、要求主要干道和次要支道上各具有绿、黄、红三色信号灯,用来指示车辆的允许通行或禁止通行,同时设有计时、译码及显示电路,显示定时器的定时状态。

2、如果只有一个方向有车时,则保持该方向畅通;当两个方向都有车时,主要干道和次要支道交替通行,但主要干道通行的时间要比次要支道长一些。

设主要干道每次通行的时间为60秒,即主要干道每次绿灯亮的时间为60秒;次要支道上每次通行时间为30秒,即次要支道上绿灯亮的时间为30秒。

3、要求主要干道或是次要支道上绿灯亮足规定的时间后,要求黄灯先亮5秒钟后红灯才能亮,然后才能交换通行车道。

四、系统框图及组成系统主要由控制器和处理器两部分组成,控制器接受外部系统时钟信号。

处理器由定时器和译码显示器组成。

定时器能向控制器发出5秒、30秒和60秒的定时信号,译码器在控制器的控制下,改变交通灯的信号。

根据上述要求画出系统框图如下:图中:R:主要干道传感器来的信号,高电平表示有车,低电平表示设车。

S:次要支道传感器来的信号,高电平表示有车,低电平表示设车。

T L:主要干道绿灯亮的时间间隔为60秒,即主要干道车辆通行的时间为60秒,定时时间到时,T L=1,否则,T L=0。

T S:次要支道绿灯亮的时间间隔为30秒,即次要支道车辆通行的时间为30秒,定时时间到时,Ts=1,否则,T S=0。

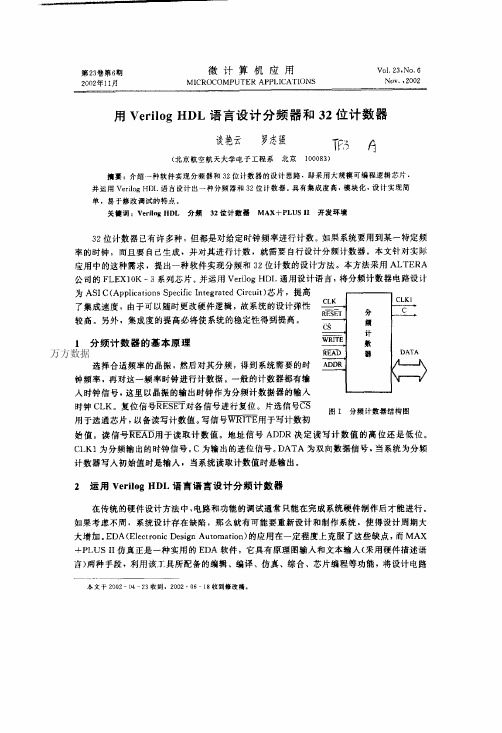

用Verilog+HDL语言设计分频器和32位计数器

i<i+1l

end

cs)∥有片选信号

end endrnodule

begin if(addr)

aceuh<2data}

该模块已通过软件仿真,符合设计要求。并已将程序下载到FPGA芯片,在电路板上与 系统进行联调,已证明设计达到预期功能,正式投入使用。

参 考 文 献

1夏宇闻.复杂数字电路与系统的VerilogHDL设计技术.北京t北京航空航天大学出版杜,1999.1—86 2阎石鼓字电子技术基础.北京:高等教育出版社.1 997.224--295 3束万焘·罗 车,吴顺军.CPI,D技术及其盥用西安:西安电子科技大学出版社,1999.30】oo

end end

output

elkl.c}//输出时钟和计数进位信号

j

wirte[15

reg

பைடு நூலகம்

O]data—reg·dataI

c,clkl{

if(i>=119) 计数值的高16位数和低

begin

∥对输人时钟进行J20分频

reg[1 5:O]aceub.aecul;

1

6位数

j<=0; clkl<=~clkl;

第23卷第6期 2002年1 1月

微计算机应用

MICROCOMPUTER APPLICATIONS

Vol

23.N。.6

Nov-,2002

用Ver|log

HDL语言设计分频器和32位计数器

谈艳云 罗志强

100083)

仍局

(北京航空航天大学电子工程东北京

擅要t介绍一种软件实现分频器和32位计数器的设计思路.即采用大规模可编程逻辑芯片.

+PLUS

II仿真正是一种实用的EDA软件,它具有原理图输入和文本输入(采用硬件描述语

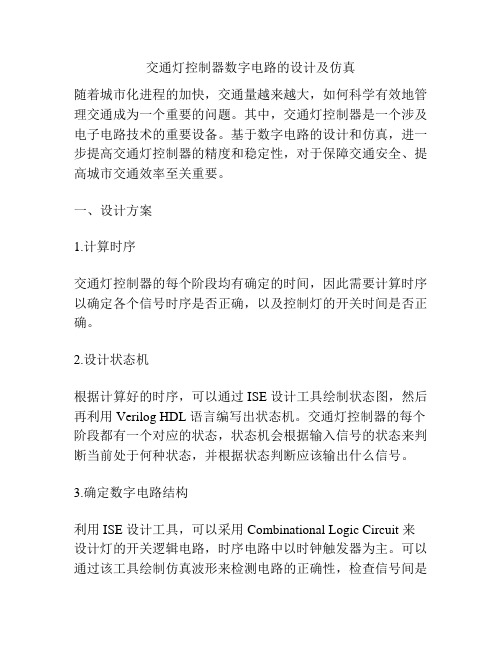

交通灯控制器数字电路的设计及仿真

交通灯控制器数字电路的设计及仿真随着城市化进程的加快,交通量越来越大,如何科学有效地管理交通成为一个重要的问题。

其中,交通灯控制器是一个涉及电子电路技术的重要设备。

基于数字电路的设计和仿真,进一步提高交通灯控制器的精度和稳定性,对于保障交通安全、提高城市交通效率至关重要。

一、设计方案1.计算时序交通灯控制器的每个阶段均有确定的时间,因此需要计算时序以确定各个信号时序是否正确,以及控制灯的开关时间是否正确。

2.设计状态机根据计算好的时序,可以通过 ISE 设计工具绘制状态图,然后再利用 Verilog HDL 语言编写出状态机。

交通灯控制器的每个阶段都有一个对应的状态,状态机会根据输入信号的状态来判断当前处于何种状态,并根据状态判断应该输出什么信号。

3.确定数字电路结构利用 ISE 设计工具,可以采用 Combinational Logic Circuit 来设计灯的开关逻辑电路,时序电路中以时钟触发器为主。

可以通过该工具绘制仿真波形来检测电路的正确性,检查信号间是否存在错误。

二、仿真过程1.绘制输入信号波形首先,需要绘制出输入信号的波形,并且在仿真时要按照相应的频率和占空比输出。

2.对仿真波形进行仿真分析仿真过程中,可以通过 Xilinx 仿真工具,对仿真波形进行分析,检测电路的正确性和稳定性。

同时,可以通过仿真过程中的输出信号波形,判断各阶段信号的状态。

3.检验仿真结果与设计方案借助仿真工具,可以非常直观地验证数字电路的设计方案是否合理、可靠。

此外,还可以通过不同的应用场景,不断优化和调整设计方案,以实现更高的效率与精度。

三、总结数字电路的设计和仿真,可以有效地提高交通灯控制器的精度和稳定性,在城市交通管理中起到关键的作用。

当前数字电路技术的不断推进,为实现更加高效安全的交通管理提供了强有力的支持。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

分频器module div(clk, div1,div2,div3);input clk;output div1;output div2;output div3;reg [31:0] counter1;reg [31:0] counter2;reg [31:0] counter3;reg div1;reg div2;reg div3;initial begindiv1=0;div2=0;div3=0;counter1=0;counter2=0;counter3=0;endalways @(posedge clk)begin/*if(counter1==2) counter1 <= 0;else counter1 <= counter1+1;if(counter2==3) counter2 <= 0;else counter2 <= counter2+1;if(counter3==4) counter3 <= 0;else counter3 <= counter3+1;*/ if(counter1==24999999) counter1 <= 0;else counter1 <= counter1+1;if(counter2==24999) counter2 <= 0;else counter2 <= counter2+1;if(counter3==12499999) counter3 <=0;else counter3 <= counter3+1;endalways @(posedge clk)begin/*if(counter1==2) div1 <= ~div1;if(counter2==3) div2 <= ~div2;if(counter3==4) div3 <= ~div3;*/if(counter1==24999999) div1 <= ~div1;if(counter2==24999) div2 <= ~div2;if(counter3==12499999) div3 <= ~div3;endendmodule30s计数器module count30(div1,number,direction );input div1;output [4:0] number;reg [4:0] number;reg direction;initialbegindirection=0;number=30;endalways@(posedge div1)beginif(number==0)begindirection<=~direction;number<=30;endelse number<=number-1;endendmodule控制器module moniter( div3,number,direction,eastred,eastyellow,eastgreen,northred,northyellow,northgreen );input div3;input direction;input [4:0]number;output eastred;output eastyellow;output eastgreen;output northred;output northyellow;output northgreen ;//wire [4:0] number;reg eastred;reg eastyellow;reg eastgreen;reg northred;reg northyellow;reg northgreen ;initial begineastred<=1;eastgreen<=0;northred<=1;northgreen<=0;northyellow<=eastyellow<=0;endalways @(posedge div3)beginif(number<=3)beginif (direction==0) eastyellow<=~eastyellow;else northyellow<=~northyellow;endelse begin eastyellow<=0;northyellow<=0;end endalways @(number )/*beginif(number==30&&direction==0)begin eastred<=1;eastgreen<=0;northred<=1;northgreen<=0;end*/if (number>2'b00010&&direction==0)begineastred<=0;eastgreen<=1;northred<=1;northgreen<=0;endelse if(number<3&&direction==0)begineastred<=0;eastgreen<=0;northred<=1;northgreen<=0;endelse if(number>2&&direction==1)begineastred<=1;eastgreen<=0;northred<=0;northgreen<=1;endelse if(number<3&&direction==1)begineastred<=1;eastgreen<=0;northred<=0;northgreen<=0;endendmodule译码器module yimaqi( clk,number,led1,led2);input clk;input [4:0] number;output [6:0] led1;output [6:0] led2;reg [6:0] led1;reg [6:0] led2;always @( number )begincase (number)5'b00000: begin led1 <= 7'b0000001; led2 <= 7'b0000001;end5'b00001: begin led1 <= 7'b0000001; led2 <= 7'b1001111;end5'b00010: begin led1 <= 7'b0000001; led2 <= 7'b0010010;end7'b0000110;end5'b00100: begin led1 <= 7'b0000001; led2 <= 7'b1001100;end5'b00101: begin led1 <= 7'b0000001; led2 <= 7'b0100100;end5'b00110: begin led1 <= 7'b0000001; led2 <= 7'b1100000;end5'b00111: begin led1 <= 7'b0000001; led2 <= 7'b0001111;end5'b01000: begin led1 <= 7'b0000001; led2 <= 7'b0000000;end5'b01001: begin led1 <= 7'b0000001; led2 <= 7'b0001100; end5'b01010: begin led1 <= 7'b1001111; led2 <= 7'b0000001;end5'b01011: begin led1 <= 7'b1001111; led2 <= 7'b1001111; end5'b01100: begin led1 <= 7'b1001111; led2 <= 7'b0010010;end5'b01101: begin led1 <= 7'b1001111; led2 <= 7'b0000110; end5'b01110: begin led1 <= 7'b1001111; led2 <= 7'b1001100;end5'b01111: begin led1 <= 7'b1001111; led2 <= 7'b0100100;end5'b10000: begin led1 <= 7'b1001111; led2 <= 7'b1100000;end5'b10001: begin led1 <= 7'b1001111; led2 <= 7'b0001111;end5'b10010: begin led1 <= 7'b1001111; led2 <= 7'b0000000;end5'b10011: begin led1 <= 7'b1001111; led2 <= 7'b0001100;end5'b10100: begin led1 <= 7'b0010010; led2 <= 7'b0000001;end5'b10101: begin led1 <= 7'b0010010; led2 <= 7'b1001111;end5'b10110: begin led1 <= 7'b0010010; led2 <= 7'b0010010;end5'b10111: begin led1 <= 7'b0010010; led2 <= 7'b0000110;end5'b11000: begin led1 <= 7'b0010010; led2 <= 7'b1001100;end7'b0100100;end5'b11010: begin led1 <= 7'b0010010; led2 <= 7'b1100000;end5'b11011: begin led1 <= 7'b0010010; led2 <= 7'b0001111;end5'b11100: begin led1 <= 7'b0010010; led2 <= 7'b0000000;end5'b11101: begin led1 <= 7'b0010010; led2 <= 7'b0001100;end5'b11110: begin led1 <= 7'b0000110; led2 <= 7'b0000001;enddefault: begin led1 <= 7'b0000000; led2 <= 7'b0000000;endendcaseendendmodulemodule dianzhen(direction,clk,div2,row,con);input div2;input clk;input direction;output[15:0] row;output[15:0] con;reg[15:0] row;reg[15:0] con;integer cnt,b;reg[15:0] r[48:0];initialbeginif (direction==0)begin// 丁r[0] <=16'b1111111111111111;r[1] <=16'b1011111111111111;r[2] <=16'b1011111111111111;r[3] <=16'b1011111111111111;r[4] <=16'b1011111111111111;r[5] <=16'b1011111111111011;r[6] <=16'b1011111111111101;r[7] <=16'b1000000000000011;r[8] <=16'b1011111111111111;r[9] <=16'b1011111111111111;r[10]<=16'b1011111111111111;r[11] <=16'b1011111111111111;r[12]<=16'b1011111111111111;r[13]<=16'b1011111111111111;r[14]<=16'b1011111111111111;r[15]<=16'b1111111111111111;// 乾r[16]<=16'b1101111111101111 ;r[17]<=16'b1101000000101111 ;r[18]<=16'b1101010101101111 ;r[19]<=16'b0000010101101111 ;r[20]<=16'b1101010100000000 ;r[21]<=16'b1101010101101111 ;r[22]<=16'b1101000000101111 ;r[23]<=16'b1101110111101111 ;r[24]<=16'b1111001111110011 ;r[25]<=16'b0000110111001101 ;r[26]<=16'b1010110110111101 ;r[27]<=16'b1110110101111101 ;r[28]<=16'b1110110011111101 ;r[29]<=16'b1110110111100001 ;r[30]<=16'b1110111111111011 ;r[31]<=16'b1111111111111111 ;// 全灭r[32]<=16'b1111111111111111;r[33]<=16'b1111111111111111;r[34]<=16'b1111111111111111;r[35]<=16'b1111111111111111;r[36]<=16'b1111111111111111;r[37]<=16'b1111111111111111;r[38]<=16'b1111111111111111;r[39]<=16'b1111111111111111;r[40]<=16'b1111111111111111;r[41]<=16'b1111111111111111;r[42]<=16'b1111111111111111;r[43]<=16'b1111111111111111;r[44]<=16'b1111111111111111;r[45]<=16'b1111111111111111;r[46]<=16'b1111111111111111;r[47]<=16'b1111111111111111;endelse if(direction==1)begin//1r[0] <=16'b 1111111111111111;r[1] <=16'b 1111111111111111;r[2] <=16'b 1111111111111111;r[3] <=16'b 1111111111111111;r[4] <=16'b 1111111111111111;r[5] <=16'b 1111011111111011;r[6] <=16'b 1111011111111011;r[7] <=16'b 1110000000000011;r[8] <=16'b 1111111111111011;r[9] <=16'b 1111111111111011;r[10]<=16'b 1111111111111111;r[11] <=16'b 1111111111111111;r[12]<=16'b 1111111111111111;r[13]<=16'b 1111111111111111;r[14]<=16'b 1111111111111111;r[15]<=16'b 1111111111111111;// 0r[16]<=16'b 1111111111111111;r[17]<=16'b 1111111111111111;r[18]<=16'b 1111111111111111;r[19]<=16'b 1111111111111111;r[20]<=16'b 1111111111111111;r[21]<=16'b 1111100000001111;r[22]<=16'b 1111011111110111;r[23]<=16'b 1110111111111011;r[24]<=16'b 1110111111111011;r[25]<=16'b 1111011111110111;r[26]<=16'b 1111100000001111;r[27]<=16'b 1111111111111111;r[28]<=16'b 1111111111111111;r[29]<=16'b 1111111111111111;r[30]<=16'b 1111111111111111;r[31]<=16'b 1111111111111111;// 9r[32]<=16'b 1111111111111111;r[33]<=16'b 1111111111111111;r[34]<=16'b 1111111111111111;r[35]<=16'b 1111111111111111;r[36]<=16'b 1111111111111111;r[37]<=16'b 1111100011111111;r[38]<=16'b 1111011101110011;r[39]<=16'b 1110111110111011;r[40]<=16'b 1110111110111011;r[41]<=16'b 1111011101110111;r[42]<=16'b 1111100000001111;r[43]<=16'b 1111111111111111;r[44]<=16'b 1111111111111111;r[45]<=16'b 1111111111111111;r[46]<=16'b 1111111111111111;r[47]<=16'b 1111111111111111;endendalways@(posedge clk )beginif (b==47)b<=0;else b<=b+1;endalways@(posedge div2)beginif(cnt==15)begincnt<=0;endelsecnt<=cnt+1;case(cnt)15: con<=16'b0000_0000_0000_0001; 14: con<=16'b0000_0000_0000_0010; 13: con<=16'b0000_0000_0000_0100; 12: con<=16'b0000_0000_0000_1000; 11: con<=16'b0000_0000_0001_0000; 10: con<=16'b0000_0000_0010_0000; 9: con<=16'b0000_0000_0100_0000; 8: con<=16'b0000_0000_1000_0000; 7: con<=16'b0000_0001_0000_0000; 6: con<=16'b0000_0010_0000_0000; 5: con<=16'b0000_0100_0000_0000; 4: con<=16'b0000_1000_0000_0000; 3: con<=16'b0001_0000_0000_0000; 2: con<=16'b0010_0000_0000_0000; 1: con<=16'b0100_0000_0000_0000; 0: con<=16'b1000_0000_0000_0000;endcasecase(cnt)0: row<=r[b+0];1: row<=r[b+1];2: row<=r[b+2];3: row<=r[b+3];4: row<=r[b+4];5: row<=r[b+5];6: row<=r[b+6];7: row<=r[b+7];8: row<=r[b+8];9: row<=r[b+9];10: row<=r[b+10];11: row<=r[b+11];12: row<=r[b+12];13: row<=r[b+13];14: row<=r[b+14];15: row<=r[b+15];endcaseendendmodule。