EDA设计流程及其工具

第03章EDA设计流程与开发

EDA技术与 技术与VHDL 技术与 IP的功能块。 IP的功能块。 的功能块 原理图编辑绘制完成后, 原理图编辑绘制完成后,原理图编辑器将对输入的图形文件进行排 之后再将其编译成适用于逻辑综合的网表文件。 错,之后再将其编译成适用于逻辑综合的网表文件。用原理图表达的 输入方法的优点是显而易见的: 输入方法的优点是显而易见的: 设计者进行电子线路设计不需要增加新的相关知识(诸如HDL (1)设计者进行电子线路设计不需要增加新的相关知识(诸如HDL 等)。 方法与用PROTEL作图相似,设计过程形象直观, PROTEL作图相似 (2)方法与用PROTEL作图相似,设计过程形象直观,适用于初学 或教学演示。 或教学演示。 对于较小的电路模型,其结构与实际电路十分接近, (3)对于较小的电路模型,其结构与实际电路十分接近,设计者 易于把握电路全局。 易于把握电路全局。 由于设计方式接近于底层电路布局, (4)由于设计方式接近于底层电路布局,因此易于控制逻辑资源 的耗用,节省面积。 的耗用,节省面积。 然而,使用原理图输入方式的设计方法的缺点同样是十分明显的: 然而,使用原理图输入方式的设计方法的缺点同样是十分明显的: 由于图形设计方式并没有标准化,不同的EDA EDA软件中的图形处 (1)由于图形设计方式并没有标准化,不同的EDA软件中的图形处 理工具对图形的设计规则、存档格式和图形编译方式都不同, 理工具对图形的设计规则、存档格式和图形编译方式都不同,因此图 形文件兼容性差,难以交换和管理。 形文件兼容性差,难以交换和管理。 随着电路设计规模的扩大、 (2)随着电路设计规模的扩大、原理图输入描述方式必然引起一 系列难以克服的困难,如电路功能原理的易读性下降, 系列难以克服的困难,如电路功能原理的易读性下降,错误排查困

基于EDA软件的FPGA/CPLD EDA软件的FPGA/CPLD开发流程框图 图3-1基于EDA软件的FPGA/CPLD开发流程框图

EDA简介PPT课件

.

12

6. EDA的发展趋势

• IC设计的发展方向:单片系统或称系统集成芯片, 即在一个芯片上完成系统级的集成。

• 更趋于电路行为级的硬件描述语言,如SystemC、 Superlog及系统级混合仿真工具,可以在同一个开发 平台上完成高级语言,如C/C++等,与标准HDL语言 (Verilog HDL、VHDL) 或其他更低层次描述模块 的混合仿真。

• FPGA与ASIC正在互相融合,取长补短。

• 目前,许多PLD公司开始为ASIC提供FPGA 内核。

• 现在,传统ASIC和FPGA之间的界限正变得模糊。 系统级芯片不仅集成RAM和微处理器,也集成FPGA。

.

13

二、 EDA设计流程及其工具 FPGA/CPLD设计流程

应用于FPGA/CPL.D的EDA开发流程

.

2

1. EDA技术实现目标

利用EDA技术进行电子系统设计,最后的目标 是完成专用集成电路ASIC的设计和实现。

三条实现途径: 1)超大规模可编程逻辑器件***

主流器件:

FPGA(Field Programmable Gate Array) CPLD (Complex Programmable Logic Device)

生产工艺直接相关,因此可移植性差;

(5)只有在设计出样机或生产出芯片后才能进行实测。

.

11

采用EDA技术的优点:

(1)采用硬件描述语言作为设计输入; (2)库(Library)的引入;(支持自动设计) (3)设计文挡的管理; (4)强大的系统建模、电路仿真功能; (5)具有自主知识产权; (6)开发技术的标准化、规范化以及IP核的可利用性; (7)适用于高效率大规模系统设计的自顶向下设计方案; (8)全方位地利用计算机自动设计、仿真和测试技术; (9)对设计者的硬件知识和硬件经验要求低; (10)与以CPU为主的电路系统相比,高速性能好; (11)纯硬件系统的高可靠性。

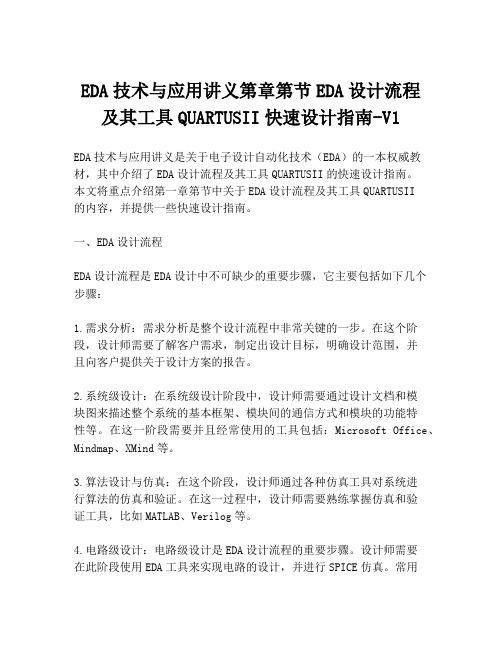

EDA技术与应用讲义第章第节EDA设计流程及其工具QUARTUSII快速设计指南-V1

EDA技术与应用讲义第章第节EDA设计流程及其工具QUARTUSII快速设计指南-V1EDA技术与应用讲义是关于电子设计自动化技术(EDA)的一本权威教材,其中介绍了EDA设计流程及其工具QUARTUSII的快速设计指南。

本文将重点介绍第一章第节中关于EDA设计流程及其工具QUARTUSII的内容,并提供一些快速设计指南。

一、EDA设计流程EDA设计流程是EDA设计中不可缺少的重要步骤,它主要包括如下几个步骤:1.需求分析:需求分析是整个设计流程中非常关键的一步。

在这个阶段,设计师需要了解客户需求,制定出设计目标,明确设计范围,并且向客户提供关于设计方案的报告。

2.系统级设计:在系统级设计阶段中,设计师需要通过设计文档和模块图来描述整个系统的基本框架、模块间的通信方式和模块的功能特性等。

在这一阶段需要并且经常使用的工具包括:Microsoft Office、Mindmap、XMind等。

3.算法设计与仿真:在这个阶段,设计师通过各种仿真工具对系统进行算法的仿真和验证。

在这一过程中,设计师需要熟练掌握仿真和验证工具,比如MATLAB、Verilog等。

4.电路级设计:电路级设计是EDA设计流程的重要步骤。

设计师需要在此阶段使用EDA工具来实现电路的设计,并进行SPICE仿真。

常用的工具包括SPICE仿真器、电路设计与验证工具等。

5.物理设计:在物理设计阶段中,设计师需要对电路进行物理实现和布局。

可以使用EDA工具中的Autoplacer和Autorouter等工具。

二、QUARTUSII快速设计指南QUARTUSII是EDA设计中广泛使用的FPGA开发工具,它可以从高层次的RTL代码到底层的逻辑等级进行仿真和综合,最终生成bitstream文件上传到FPGA中实现电路的设计。

QUARTUSII的快速设计指南包括:1.了解quartus ii软件:在使用QUARTUSII之前,首先需要熟悉软件的基本操作和使用流程。

eda设计流程详解

eda设计流程详解英文回答:EDA (Exploratory Data Analysis) is a crucial step in the data analysis process. It involves examining and visualizing the data to gain insights and identify patterns or relationships. EDA helps in understanding the data and making informed decisions before applying any statistical models or machine learning algorithms.The EDA process typically involves the following steps:1. Data collection: This step involves gathering the required data from various sources. It could be in the form of structured data from databases or unstructured data from text documents or web scraping.2. Data cleaning: In this step, the collected data is cleaned and preprocessed. This includes handling missing values, removing outliers, and transforming variables ifnecessary. Data cleaning ensures that the data is in a suitable format for analysis.3. Data visualization: Visualization is a powerful tool for understanding the data. It helps in identifying patterns, trends, and outliers. Various charts, graphs, and plots can be used to visualize the data, such as histograms, scatter plots, and box plots.For example, let's say I have collected data on the sales of a retail store. I can create a histogram to visualize the distribution of sales across different products. This can help me identify the most popular products and any potential outliers.4. Data exploration: This step involves exploring the data further by calculating summary statistics, such as mean, median, and standard deviation. It also includes identifying correlations between variables using techniques like correlation matrices or scatter plots.Continuing with the previous example, I can calculatethe average sales for each product category and compare them. This can help me identify any significant differences in sales between different categories.5. Hypothesis testing: In this step, statistical tests are performed to test hypotheses or assumptions about the data. This helps in making data-driven decisions and validating any patterns or relationships observed during the exploration phase.For instance, I can perform a t-test to determine if there is a significant difference in sales between two different time periods. This can help me understand if there has been any change in sales over time.6. Conclusion and insights: Finally, the EDA process concludes with summarizing the findings and drawing meaningful insights from the data. These insights can be used to guide further analysis or to make informed business decisions.中文回答:EDA(探索性数据分析)是数据分析过程中至关重要的一步。

EDA使用的12个流程

EDA使用的12个流程

1. 数据收集

•确定数据来源和收集方式

•对数据进行初步的探索性分析

2. 数据清洗

•处理缺失值、异常值等数据质量问题

•进行数据变换和规范化

3. 数据可视化

•使用图表和可视化工具将数据表现出来

•探索数据的分布和关联性

4. 描述统计分析

•统计数据的基本概述,包括均值、中位数、标准差等•分析变量的分布和特征

5. 探索性数据分析(EDA)

•通过可视化和统计分析来寻找数据中的规律和结构

•发现数据之间的关系和相互影响

6. 双变量分析

•分析两个变量之间的相关性和相互作用

•使用散点图、线性回归等方法进行分析

7. 多变量分析

•分析多个变量之间的关系

•使用热力图、多元回归等方法进行分析

8. 因果分析

•研究变量之间的因果关系

•使用因果图、实验设计等方法进行分析

9. 预测建模

•基于数据特征和模型算法,进行预测和建模

•使用回归、分类、聚类等方法进行分析

10. 模型评估

•对预测模型进行评估,包括准确率、召回率等指标

•使用交叉验证、ROC曲线等方法进行评估

11. 结果解释

•解释模型的结果和预测的意义

•提出结论和建议

12. 报告撰写

•将整个分析过程整理成报告

•包括数据分析的方法、结果和结论

以上是EDA使用的12个流程,通过这些流程可以帮助我们更好地理解和分析数据,发现其中的规律和关联性,并提供数据驱动的决策依据。

采用Markdown 格式进行编写可以使得文档结构清晰,便于阅读和理解。

立创eda电子设计流程介绍

立创eda电子设计流程介绍Electronic design automation (EDA) stands for a category of software tools for designing electronic systems such as printed circuit boards and integrated circuits.电子设计自动化(EDA)是指一类用于设计印刷电路板和集成电路等电子系统的软件工具。

它们可以帮助工程师快速、高效地完成设计工作,并在整个设计流程中提供支持。

The EDA process involves various stages, starting from design specification and requirements, through circuit design and simulation, to physical layout and fabrication.EDA过程涉及各个阶段,从设计规范和要求开始,通过电路设计和模拟,到物理布局和制造。

In the design specification and requirements phase, the engineer outlines the functionality and features of the electronic system. This phase sets the foundation for the entire design process and requires clear communication between the design team and the client.在设计规范和需求阶段,工程师概述了电子系统的功能和特性。

这个阶段为整个设计流程奠定了基础,并需要设计团队与客户之间的清晰沟通。

Following the design specification, the circuit design and simulation phase involves the creation and testing of the schematic diagram of the electronic system using specialized EDA software. This is a critical stage where the engineer simulates the behavior of the circuit to ensure it meets the desired functionality and performance.在设计规范之后,电路设计和模拟阶段涉及使用专门的EDA软件创建和测试电子系统的原理图。

简述用eda技术设计电路的设计流程

EDA技术设计电路的设计流程EDA(Electronic Design Automation)技术是指通过计算机软件工具辅助进行电子电路设计、分析和验证的技术。

它可以提高设计师的效率和设计质量,并减少设计周期。

本文将详细描述使用EDA技术设计电路的设计流程,包括以下步骤:1. 需求分析在进行电路设计之前,首先需要明确电路的需求和要求。

这包括功能需求、性能指标、电源和环境条件等。

设计人员需要与客户或系统工程师进行充分的沟通和交流,确保对电路设计目标的共识。

2. 架构设计在需求分析的基础上,设计人员需要进行电路的架构设计。

在这一阶段,设计人员需要选择合适的电路拓扑结构、制定电路通信方式、确定信号处理算法等。

架构设计的目标是在满足需求的前提下,最大程度地降低功耗、电路面积和成本。

3. 电路原理图设计电路原理图是电路设计的基础,它描述了各个元件和电子器件之间的连接关系。

在EDA工具中,设计人员可以通过拖拽符号、连接引脚等方式来完成电路原理图的设计。

在这一阶段,设计人员需要根据架构设计的要求选择合适的元件,并进行连接。

此外,还需要进行信号的调节和滤波等处理。

4. 电路仿真电路仿真是验证电路设计的关键步骤之一。

通过仿真,设计人员可以预测电路的性能、稳定性和可靠性。

在EDA工具中,设计人员可以通过输入电路的参数和信号来进行仿真,并通过仿真结果进行分析。

常用的电路仿真工具有SPICE、Verilog等。

4.1 直流分析直流分析可以得到电路的稳态工作状态,包括电流、电压和功率等。

设计人员需要根据设计要求设置电路的直流电源和参数,并进行仿真分析。

4.2 交流分析交流分析可以得到电路在不同频率下的频率响应和滤波效果。

设计人员需要设置交流源和参数,并进行交流仿真分析。

4.3 时序分析时序分析可以得到电路在不同时钟频率下的时序性能,包括时钟延迟、数据到达时间和时序安全裕度等。

设计人员需要设置时钟源和时钟参数,并进行时序仿真分析。

EDA设计流程

EDA设计流程:设计输入,综合,适配,时序仿真和功能仿真,编辑下载,硬件测试VHDL综合:将用行为和功能层次表达的电子系统转换为低层次的便于具体实现的模块组合装配过程,综合仅对hdl而言的,综合过程将把软件的hdl描述与硬件结果挂钩是将软件转化为硬件电路的关键步骤,是文字描述与硬件实现的一座桥梁FPGA/CPLD基于什么结构:查找表结构器件;乘积项结构器件。

IP:知识产权核或知识产权模块,软IP:用vhdl等硬件描述语言描述的功能块。

固IP:完成综合的功能块。

硬Ip:提供设计的最终阶段产品即掩模资源共享:主要针对数据通路中耗费逻辑资源较多的模块,通过选择复用方式共享使用该模块,以减少使用该模块的使用个数,以减少资源浪费。

时钟边缘检测描述语句:“CLK'EVENT AND CLK='1'” 检测时钟信号CLK的上升沿的,<信号名>'EVENT 侧下降沿:CLK=’0’AND CLK’LAST_V ALUE=’1’、falling_edge()、CLK’EVENT AND (CLK=’0’)等各种状态机编码的优缺点:一般有限状态机(\状态机克服了纯硬件数字系统顺序方式控制不灵活的缺点\状态机可以定义符号化枚举类型的状态\状态机容易构成性能良好的同步时序逻辑模块\状态机的VHDL表述丰富多样、程序层次分明,易读易懂\在高速运算和控制方面,状态机更有其巨大的优势\高可靠性 .)Moore型有限状态机.Mealy型有限状态机速度优化和面积优化:面积优化:指FPGA/CPLD的资源利用优化(资源共享,逻辑优化,串行化)a使用规模更小的可编程逻辑芯片,降低成本。

b可编程器件由于布线资源有限耗用资源过多会严重影响电路性能。

c为技术升级留下可编程资源。

d资源耗用过多会使功耗上升。

速度优化:流水线设计,寄存器配平,关键路径法。

标准逻辑矢量数据类型的赋值:B:OUT STD_logic_vector(7downto0);signalA:STD_logic_vector(1to4)进程中的信号与变量赋值:信号SIGNAL 变量V ARIABLE基本用法用于作为电路中的信号连线用于作为进程中局部数据存储单元适用范围在整个结构体内的任何地方都能适用只能在所定义的进程中使用行为特性在进程的最后才对信号赋值立即赋值变量Variable a: std_logic;信号Y<=a+b;结构体的定义:是实体所定义的设计实体中的一个组成部分标识符的格式:以英文字母开头,必须是单一“_”,且左右必须有英文或数字,不区分大小写,允许图形符号(回车符,换行符等),也允许有空格符。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

15

6、硬件测试

将含有载入了设计的FPGA或CPLD的硬件系统进行统一

测试,以便最终验证设计项目在目标系统上的实际工作情况。

16

实验开发系统

17

2.2 ASIC及其设计流程

一、集成电路工艺的发展特点和规律

九十年代以来,集成电路工艺发展非常迅速,已从亚微米 (0.5到1微米)进入到深亚微米(小于0.5微米),进而进入到超深亚 微米(小于0.25微米)。其主要特点: – 特征尺寸越来越小 – 芯片尺寸越来越大 – 单片上的晶体管数越来越多 – 时钟速度越来越快 – 电源电压越来越低 – 布线层数越来越多 – I/O引线越集成电路按导电类型可分为双极型集成电路和单极型集成电路,他们都 是数字集成电路. 双极型集成电路的制作工艺复杂,功耗较大,代表集成电路有TTL、 ECL、HTL、LST-TL、STTL等类型。单极型集成电路的制作工艺简单, 功耗也较低,易于制成大规模集成电路,代表集成电路有CMOS、NMOS、 PMOS等类型。

延时特性。

12

3)时序仿真:

接近真实器件运行特性的仿真,仿真文件中已包含了

器件硬件特性参数,仿真精度高。

13

5、编程下载

将适配后的下载文件,通过通信电缆或专用编程器写至 相应目标器件的过程。

FPGA与CPLD的辨别和分类主要是根据其结构特点和工作原理。通常的分类方法 为:

将以乘积项结构方式构成逻辑行为的器件称为CPLD,它所产生的是熔丝图文件 即JEDEC文件(简称JED文件)。如Lattice的ispLSI系列、Xilinx的XC9500系列、 Altera的MAX7000S系列和Lattice(原Vantis)的Mach系列等。 将以查表法结构方式构成逻辑行为的器件称为FPGA,它所产生的是位流数据文 件。如Xilinx的SPARTAN系列、Altera的FLEX10K或ACEX1K系列等。

9

④.

门级映射网表:

过程:取出优化后的布尔描述,并利用工艺库中得 到的逻辑和定时上的信息去做网表,网表是对用户所 描述的面积和速度指标的一种体现形式。工艺库中存 有大量的网表,它们的功能相同,但可以在速度和面 积之间权衡。

10

3、 适配

适配器也称结构综合器,它的功能是将由综合器产生的 网表文件配臵于指定的目标器件中,使之产生最终的下载文 件,如JEDEC、Jam格式的文件。适配所选定的目标器件 (FPGA/CPLD芯片)必须属于原综合器指定的目标器件系列。 逻辑综合通过后必须利用适配器将综合后网表文件针对某 一具体的目标器件进行逻辑映射操作,其中包括底层器件配 臵、逻辑分割、逻辑优化、逻辑布局布线操作。适配完成后 可以利用适配所产生的仿真文件作精确的时序仿真,同时产 生可用于编程的文件。

功能 仿真

时序与功能 门级仿真 1.功能仿真 2.时序仿真

2.JTAG方式下载

3.针对SRAM结构的配置 4.OTP器件编辑

(One Time Programming)

2

2.1.1 设计输入(原理图/HDL文本编辑)

1. 图形输入

原理图输入 图 形 输 入

状态图输入

波形图输入

3

1、设计输入(原理图/HDL文本编辑)

– 1)在发展微细加工技术的基础上,开发超高速、超高 集成度的电路。 – 2)迅速、全面地利用已达到的或已成熟的工艺技术、 设计技术、封装技术、和测试技术等发展各种专用集成 电路(ASIC)。 从另一个角度来说,进入90年代以来,电子信息类产品的 开发明显地出现了两个特点:

1、开发产品的复杂程度加深,出现SOC;

18

发展规划代次的指标

年份 最小线宽 (μ m ) DRAM容量 每片晶体管数 (M) 芯片尺寸 (平方毫米) 频率 (兆赫) 1997 0.25 256M 11 300 750 1999 0.18 1G 21 440 1200 2001 0.15 1G~4G 40 385 1400 2003 0.13 4G 76 430 1600 2006 0.10 16G 200 520 2000 2009 0.07 64G 520 620 2500 2012 0.01 256G 1400 750 3000

第2 章

EDA设计流程及其工具

1:FPGA/CPLD设计流程

2:ASIC及其设计流程 3:常用EDA工具

4:IP核

1

2.1 FPGA/CPLD 设计流程

FPGA:现场可编程门阵列 CPLD:复杂可编程逻辑器件 一、这2种器件的一般开发流程为:

原理图/HDL文本编辑

综合 逻辑综合器 FPGA/CPLD 器件和电路系统 1.isp方式下载 FPGA/CPLD 适配 结构综合器 FPGA/CPLD 编程下载

(五)按用途分类

集成电路按用途可分为电视机用集成电路、音响用集成电路、影碟 机用集成电路、录像机用集成电路等。

25

(六)按应用领域分

集成电路按应用领域可分为标准通用集成电路和专用集成电路。

(七)按外形分

集成电路按外形可分为圆形(金属外壳晶体管封装型,一般适合用 于大功率)、扁平型(稳定性好,体积小)和双列直插型 。

将需设计的电子系统的功能和结构以图形或文本方式表 达。 1) 图形输入:原理图输入、状态图输入、波形图输入 原理图方式应用最为广泛,原理图输入对原理图进行功能 验证后再进行编译即可转换为网表文件。 但此方法一般仅实用于小电路。对于稍大的电路,其可读 性、可移植性差。

波形图主要应用于仿真功能测试时产生某种测试信号;

金属化层层数

最低供电电压 (v ) 最大晶圆直径 (mm)

6

1.8-2.5 200

6-7

1.5-1.8 300

7

1.2-1.5 300

7

1.2-1.5 300

7-8

0.9-1.2 300

8-9

0.6-0.9 450

9

0.5-0.6 450

19

二、 IC发展方向与我国IC的发展情况

• 1、集成电路发展的方向

②、工艺库:

工艺库将提供综合工具所需要的全部半导体工艺信息。即

工艺库不仅含有ASIC单元的逻辑功能、单元面积、输入到输出 的定时关系、输出的扇出限制和对单元所需的定时检查。

8

③、逻辑综合3步曲: 逻辑综合工具将RTL级描述转换为门级描述一般有3步: 1). 将RTL描述(VHDL程序)转换为未优化的门级布尔描 述(布尔逻辑方程的形式)这一步称为“展平” 。 2). 执行优化算法,化简布尔方程,这一步称为“优化” 。 3). 按半导体工艺要求,采用相应的工艺库,把优化的布 尔描述映射成实际的逻辑电路(逻辑实现)

26

2.2.1 ASIC设计方法

按版图结构及制造方法分,有半定制(Semi-custom)和全 定制(Full-custom)两种实现方法。

全定制方法 是一种

基于晶体管级的,手工 设计版图的制造方法。

全定制法 半定制法 ASIC设计方法

半定制法 是一种

约束性设计方式,约 束的目的是简化设计 ,缩短设计周期,降 低设计成本,提高设 计正确率。 门阵列法 标准单元法

11

4、行为仿真、功能仿真、时序仿真

仿真就是让计算机根据一定的算法和一定的仿真库对

EDA设计进行模拟,以验证设计,排除错误。 1)行为仿真: 此时的仿真只是根据VHDL的语义进行的,与具体电路 没有关系。 2)功能仿真: 直接对VHDL、原理图描述或其他描述形式的逻辑功能 进行测试模拟,以了解其实现的功能是否满足原设计的要 求的过程,仿真过程不涉及任何具体器件的硬件特性,如

23

(二)按制作工艺分类

集成电路按制作工艺可分为半导体集成电路和膜集成电路。 膜集成电路又分类厚膜集成电路和薄膜集成电路。

(三)按集成度高低分类

集成电路按集成度高低的不同可分为 SSI 小规模集成电路(Small Scale Integrated circuits) MSI 中规模集成电路(Medium Scale Integrated circuits) LSI 大规模集成电路(Large Scale Integrated circuits) VLSI 超大规模集成电路(Very Large Scale Integrated circuits) ULSI 特大规模集成电路(Ultra Large Scale Integrated circuits) GSI 巨大规模集成电路也被称作极大规模集成电路或超特大规模 集成电路(Giga Scale Integration)。

–芯片加工厂(Foundry)

• 我国集成电路芯片制造业现己相对集中,主要分布在上海、北京、江 苏、浙江等省市。

–后工序(测试、封装、设备) 其中IC设计以人为主,脑力密集型,属高回报产业。

21

• 3、我国集成电路生产能力方面:

93年生产的集成电路为1.78亿块,占世界总产量的 0.4%,相当于美国1969年的水平,日本1971年的水平。 96年为7.09亿块,而1996年国内集成电路市场总用量为 67.8亿块,国内市场占有率仅为10%。 99年为23亿块,销售额70多亿元,国内市场占有率不足 20%,绝大部分依靠进口。 2000年需求量为180亿块,预计可生产32亿块。 总之,我国集成电路产业的总体发展水平还很低,与国 外相比大约落后15年。但是,目前已具备0.25微米芯片设计 开发和0.18微米芯片规模生产能力,以“方舟”、“龙芯” 为代表的高性能CPU芯片开发成功,标志着我国已掌握产业 发展的部分重大核心技术。

状态图常用于建模中。 2) HDL文本输入:目前主流输入方式,是最有效的方式,

其可读性、可移植性好、便于存档。

4

2 综合

整个综合过程就是将设计者在 EDA 平台上编辑 输入的 HDL 文本、原理图或状态图形描述,依据 给定的硬件结构组件和约束控制条件进行编译、 优化、转换和综合,最终获得门级电路甚至更底 层的电路描述网表文件。由此可见,综合器工作 前,必须给定最后实现的硬件结构参数,它的功 能就是将软件描述与给定的硬件结构用某种网表 文件的方式对应起来,成为相应互的映射关系。