全差分高增益运放的设计

全差分运算放大器设计概要

全差分运算放大器设计概要全差分运算放大器是一种常见的电子电路,它可以将输入信号的差分放大,并在输出端提供差分信号。

全差分运算放大器广泛应用于模拟与数字信号处理中,如低噪声放大器、滤波器和交叉耦合放大器等领域。

本文将介绍全差分运算放大器的设计概要,包括电路结构、设计要点和性能指标等。

[图片]该电路由两个共模反馈放大器组成,其中一个作为正放大器,另一个作为负放大器。

输入信号通过差分输入端口加到两个反馈放大器上,经过放大后,在输出端口提供差分信号。

为了保证优良的性能,必须对电路的参数进行适当的设计和调整。

首先,需要确定全差分运算放大器的增益要求。

增益是指输出信号与输入信号之间的比例关系。

在不同的应用中,增益要求可能不同。

根据增益要求,可以选择合适的放大器型号和电路拓扑结构。

其次,需要选择适当的放大器元件。

放大器元件包括晶体管、电阻、电容等。

选择合适的元件是设计成功的关键。

晶体管的选择要考虑其增益、噪声系数、带宽等指标。

电阻和电容的选择要考虑其阻值、容值、精度等因素。

然后,需要确定电路的偏置方案。

全差分运算放大器需要提供适当的偏置电压,以确保电路能够正常工作。

偏置电压的选择要考虑元件的工作状态和参数的稳定性。

常见的偏置方案包括电流镜偏置、电流源偏置等。

设计完成后,需要对电路进行性能测试和优化。

性能测试包括增益、带宽、噪声系数、非线性失真等指标的测试。

根据测试结果,可以进行相应的电路优化,以满足设计要求。

最后,需要对电路进行可靠性分析。

可靠性分析是为了确保电路在长时间工作过程中不会出现故障。

可靠性分析包括温度分析、电路重要参数的敏感度分析等。

全差分运算放大器设计的关键在于电路的结构和元件的选择。

合理的电路结构和适当的元件选择可以使电路具有较高的增益、宽带和低噪声等性能。

此外,还需要注意电路的偏置方案和可靠性分析,以确保电路的正常工作和长时间可靠性。

总之,全差分运算放大器是一种重要的电子电路,具有广泛的应用前景。

一种高增益CMOS全差分运算放大器的设计

邮局订阅号:82-946360元/年技术创新电子设计《PLC 技术应用200例》您的论文得到两院院士关注一种高增益CMOS 全差分运算放大器的设计Design of a High-gain CMOS Fully Differential Operational Amplifier(江南大学)李杨先顾晓峰浦寿杰LI Yang-xian GU Xiao-feng PU Shou-jie摘要:设计了一种用在高精度音频Σ-ΔA/D 转换器中的高增益CMOS 全差分运算放大器。

该运算放大器采用了套筒式共源共栅结构和开关电容共模反馈电路。

通过分析和优化电路性能参数,实现了高增益和低功耗。

采用SMIC 0.35μm CMOS 工艺,经Spectre 仿真验证,电路在3.3V 电源电压和2.6pF 负载电容条件下,单位增益带宽为110MHz,开环直流电压增益达76dB,功耗为1.4mW 。

关键词:运算放大器;套筒式共源共栅;高增益;A/D 转换器中图分类号:TN402文献标识码:AAbstract:A high -gain CMOS fully differential operational amplifier has been designed for the application to high -resolution audio Σ-ΔA/D converters.The telescopic cascade structure and the switched capacitor common -mode feedback circuit were adopted in this operational amplifier.High gain and low power dissipation were achieved by analyzing and optimizing the circuit parameters.The Spectre simulation using SMIC 0.35μm CMOS process shows that,with 3.3V power voltage and 2.6pF capacitor load,the circuit has a unity-gain bandwidth of 110MHz,an open-loop gain of 76dB and a power dissipation of 1.4mW.Key words:Operational amplifier;Telescopic cascade;High-gain;A/D converter文章编号:1008-0570(2009)10-2-0207-031引言运算放大器作为模拟系统和混合信号系统中的一个重要电路单元,广泛应用于数/模与模/数转换器、有源滤波器、波形发生器和视频放大器等各种电路中。

一款高增益、低功耗、宽带宽全差分运放设计

一款高增益、低功耗、宽带宽全差分运放设计周吉;龚敏;高博【摘要】基于SMIC 0.18 μm工艺模型设计了一种低电压1.8 V下的高增益、低功耗、宽输出摆幅、宽带宽的运算放大器电路.采用增益自举技术的折叠共源共栅结构极大地提高了增益,并采用辅助运放电流缩减技术有效地降低了功耗,且具有开关电容共模反馈(SC-CMFB)电路.在Cadence spectre平台上仿真得到运放具有极高的开环直流增益(111.2 dB)和1.8V的宽输出摆幅,单位增益带宽576 MHz,相位裕度为58.4°,功耗仅为0.792 mW,在1 pF的负载时仿真得到0.1%精度的建立时间为4.597 ns,0.01%精度的建立时间为4.911 ns.【期刊名称】《电子与封装》【年(卷),期】2016(016)005【总页数】5页(P26-30)【关键词】低功耗;运算放大器;高增益;宽带宽;折叠共源共栅【作者】周吉;龚敏;高博【作者单位】四川省微电子技术重点实验室,四川大学物理学院,成都610064;四川省微电子技术重点实验室,四川大学物理学院,成都610064;四川省微电子技术重点实验室,四川大学物理学院,成都610064【正文语种】中文【中图分类】TN402运算放大器(简称运放)是许多模拟系统和混合信号系统中一个完整且关键的部分,随着无线通讯技术和CMOS集成电路制造工艺技术的迅猛发展,电源电压越来越低,功耗要求越来越小,但数模混合信号系统对分辨率和速度的要求却越来越高,因此高性能的运放设计成为了必要[1]。

根据模拟电路设计的“八边形法则[1]”,运放的关键性能参数如增益、速度、功耗、输出摆幅等参数相互制约,这对高性能放大器的设计提出了许多难题。

因此,设计同时具有高增益、宽带宽、宽输出摆幅并且低功耗的放大器便成为了本设计的难点[1,2,3]。

高速、高精度的应用需要运放具有很高的增益和带宽,而这必然会增加运放的功耗,Mersi A.等发表的文献中采用两级带补偿结构的运放功耗仅为0.86 mW[4],而这种结构对进一步提高运放带宽等有一定的局限性,本文采用了一种不同的低功耗运放结构,希望解决这个问题。

一种全差分增益增强型运算放大器的设计

一种全差分增益增强型运算放大器的设计史志峰;王卫东【期刊名称】《电子器件》【年(卷),期】2015(000)001【摘要】A fully differential op-amp used in a high speed ADC is designed. This operational amplifier is consisted of a main OTA in folded cascade,four single-ended auxiliary OTA and a modified switched capacitor common mode feedback circuit. Gain-boosted technique has been introduced. Based on SMIC 0.18 μm,1.8 V process,Simulation has been run in Spectre under Cadence platform. The result shows that DC-gain of the amplifier is as high as 115 dB,unity-gain bandwidth is 805 MHz and the power consumption is 10. 5 mW. And it can reach an accuracy of 0.01% within 8 ns. This amplifier is specially used in a high speed pipelined ADC.%设计了一种用于高速ADC中的全差分运算放大器。

该运算放大器由主运放、4个辅助运放和一种改进型开关电容共模反馈电路组成,主运放采用折叠式共源共栅结构,并引入增益增强技术提高增益。

采用SMIC 0.18μm,1.8 V工艺,在Cadence电路设计平台中利用Spectre仿真,结果表明:运放增益达到115 dB,单位增益带宽805 MHz,而功耗仅为10.5 mW,运放在8 ns的时间内可以达到0.01%的建立精度,可用于高速高精度流水线( Pipelined) ADC中。

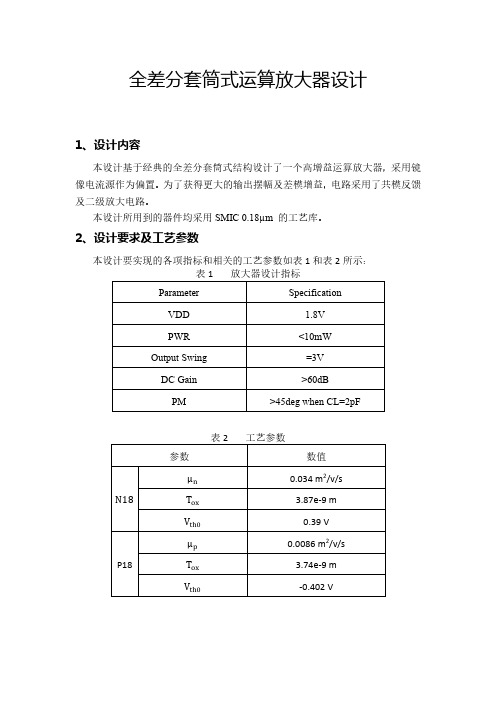

全差分套筒式运算放大器设计

全差分套筒式运算放大器设计1、设计内容本设计基于经典的全差分套筒式结构设计了一个高增益运算放大器,采用镜像电流源作为偏置。

为了获得更大的输出摆幅及差模增益,电路采用了共模反馈及二级放大电路。

本设计所用到的器件均采用SMIC 0.18µm的工艺库。

2、设计要求及工艺参数本设计要实现的各项指标和相关的工艺参数如表1和表2所示:3、放大器设计3.1 全差分套筒式放大器拓扑结构与实际电路图1 全差分套筒式放大器拓扑结构图2 最终电路图3.2 设计过程在图1中,Mb1和M9组成的恒流源为差放提供恒流源偏置,且M1,M2完全一样,即两管子所有参数均相同。

Mb2、M7和M8构成了镜像电流源,M5、M6和M7、M8构成了共源共栅电流源,M1、M2、M3、M4构成了共源共栅结构,可以显著提高输出阻抗,提高放大倍数(把M3的输出阻抗提高至原来的(gm3 + gmb3)ro2倍。

但同时降低了输出电压摆幅。

为了提高摆幅,控制增益,在套筒式差分放大器输出端增加二级放大。

本设计中功率上限为10mW,可以给一级放大电路分配3mA的电流。

设计要求摆幅为3V,所以图1中M1、M3、M5、M9的过驱动电压之和不大于1.8-3/2=0.3V。

我们可以平均分配每个管子的过驱动电压。

根据漏电计算流公式(1)(考虑沟道长度调制效应),可以计算出每个管子的宽长比。

I D=12μn C ox WL(V GS−V TH)2(1+λV DS)(1)其中,C ox等于ε/t ox,μn和t ox可以从工艺库中查找。

4、仿真结果经过调试优化之后的仿真结果如以下各图所示:图3 增益及相位裕度从图中可以看出,本设计的低频增益达到了74.25dB,达到了预期要求。

3dB 带宽为35kHz左右,比较小,可见设计还有改进的余地。

当CL为2pF时,相位裕度:PM=180°+∠βH(ω)=180°−125.5°=54.5°电源电压为1.8V时,输出摆幅如下图所示,达到了3V。

采样保持电路中全差分增益提高放大器设计

采样保持电路中全差分增益提高放大器设计钱黎明;魏敬和【摘要】介绍了一种全差分增益增强CMOS运算放大器的设计和实现.该放大器用于12位20 MHz采样频率的流水线模/数转换器(A/D)的采样保持电路.为了实现大的输入共模范围,采用折叠式共源共栅放大器.主放大器采用开关电容共模反馈电路,辅助放大器则采用简单的连续时间共模反馈电路.该放大器采用CMOS 0.5 μm工艺,电源电压为3.3 V.Cadence Spectre仿真结果显示,在负载为6 pF的情况下,其增益为99 dB,单位增益带宽为318 MHz,相位裕度为53°.【期刊名称】《电子与封装》【年(卷),期】2017(017)009【总页数】4页(P19-22)【关键词】增益提高;共模反馈;采样保持电路【作者】钱黎明;魏敬和【作者单位】中国电子科技集团公司第五十八研究所,江苏无锡214072;中国电子科技集团公司第五十八研究所,江苏无锡214072【正文语种】中文【中图分类】TN752高清图像、视频处理芯片的快速发展对A/D的速度和精度要求越来越高,这直接转化为对运算放大器的要求。

A/D的采样速度取决于运算放大器的建立时间(Settling Time),建立时间取决于摆率(Slew Rate,SR)和运放的增益带宽积(GainBandwidth,GBW)。

A/D的采样精度要求运算放大器具有高直流增益。

而随着工艺尺寸和电源电压的不断降低,普通运算放大器大概能实现50~60 dB的直流增益。

而一些高精度A/D要求放大器的直流增益为90 dB以上,两级放大器虽然能实现较高的增益,但其功耗太大,并且速度也很难满足要求。

增益提高运算放大器是将共源共栅电流源中通过增加反馈放大器而提高输出阻抗的思想应用到运放中。

这使得即使亚微米工艺制备的运放其增益也可以达到90 dB以上。

增益提高运算放大器如图1所示,该结构的运放提高增益的思想是在共源共栅电流源中增加反馈放大器而提高输出阻抗,从而大大增加了增益,在深亚微米工艺制程中其增益可以达到90 dB以上。

全差分运算放大器设计

全差分运算放大器设计全差分运放(Fully-Differential Amplifier,简称FDA)是一种特殊的运放,它具有两个差动输入和两个差动输出。

全差分运放具有许多优点,包括良好的共模抑制和电源抑制比,适用于高精度传感器信号放大、功率放大和模拟信号处理等领域。

在这篇文章中,我将介绍全差分运放的设计原理和步骤。

首先,我们需要确定设计的要求和规范。

这包括增益要求、带宽要求、电源电压和输入输出电阻等参数。

根据这些要求,我们可以选择合适的运放器件和电路拓扑。

全差分运放的常见电路拓扑有两级差分放大器、共射共源放大器和增益交换放大器等。

在这里,我们以两级差分放大器为例进行设计。

第一步是选择运放器件。

我们需要根据设计要求选择适合的运放器件,可以根据其增益带宽积、供电电压范围和失调电流等参数进行选择。

一般来说,我们可以选择低失调电流、高增益带宽积和低电压噪声的器件。

第二步是确定电路拓扑。

在两级差分放大器中,第一级是差分放大器,第二级是共射共源放大器。

差分放大器的作用是提供高输入阻抗和共模抑制比,共射共源放大器的作用是提供电流放大和驱动能力。

由于这两级放大器要分别满足不同的要求,我们可以选择不同的放大倍数和器件参数来优化电路性能。

第三步是确定偏置电路。

偏置电路的作用是提供恒定的工作电流,这可以通过电流源和电阻网络来实现。

偏置电流的选择要根据运放器件的要求和特点,可以使用恒流源或电流反馈等方法来实现。

第四步是确定反馈电路。

反馈电路的作用是控制放大倍数和增益稳定性,可以使用电阻、电容或者电流源等元件来实现。

选择适当的反馈方式可以减小失调电压和非线性,提高性能。

第五步是进行电路仿真和优化。

通过电路仿真,我们可以验证设计的性能和满足要求。

优化可以通过调整电路参数和进行迭代仿真来实现,以达到设计要求。

第六步是进行电路布局和线路板设计。

在设计布局时,要注意分离放大器电路和干扰源,减少电源和信号线的串扰。

线路板设计要保证差分信号走线的对称性和阻抗匹配,以提高传输性能。

一种全差分增益提升运放的设计与建立特性优化

D

adst ̄ exo ln 0 l n e e ff 1l [l  ̄ I I _

0 F l ieetl f eyDf r i  ̄ a l na

Bot pA osdo mp e

S ULiQI , U l i n

(ntu o col t n s f h hnsA a e yo cec , t i 02, hn) Istt f i e Mi e c oi e i e cdm r e r co T C e fSi e Bi n 1 0 9 C i ns jg0 a

维普资讯

第 2 卷 第1 9 期 20 06年 3月

电 子 器 件

Of ee J emlo l t n D v  ̄ i e or f Ee r ei n co c

V_ . 9 No 1 o 2 1 . Ma .0 6 r2 0

fr n il o d d c s o eOp Amp t o tn o st  ̄ BSa e u e sa xl r p o i ce s e e ta le -a c d f swih c n iu u -i Cl me m r s d a u ia y op A i m st n r a e t eo e -o pg i ft eman o p n a dto h p n l an o h i p a .I d i n,a smu ain b s d o t z to t o o h ih m i i lto - a e p i ain meh d f rt e hg - mi s e d d sg fg i- o se p e e i o an b o td Op Amp wa lo p e e t d n sa s r s n e .Th i lto e ut h w h tt ed sg e esmu ain r s lss o t a h e i d n Op A m p a h e e cg i f1 2d wih au iy g i r q e c f8 2M Hz c iv s d ano 0 B t nt - an fe u n yo 2 a .W iht eh g -p e p i - t h ih s e do t i m

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

增益增强技术的原理如图 1所示. 其工作原 理 [ 1] 是: 辅助放大器 A 和共栅管形成负反馈, 因 而输入管的漏端电压总是稳定在 Vref, 这就大大减 小了输出节点电压对该节点电压的影响. 因此, 辅

助放大器 A 就大大增加了该电路的输出电阻.

2 运放的设计

两级运算放大器也能实现较高的直流增益, 但是它的功耗通常是单级放大器的 2倍, 速度也 不能满足高速度的要求. 套筒式共源共栅运算放 大器在速度和功耗方面都有很好的优势, 但是采 样保持电路要求运算放大器有较大的输入共模电 压范围, 并且在误差消除技术中要求输入和输出 短接, 因此在该设计中主放大器采用折叠式共源 共栅放大器. 除了输入电压共模范围大的优点之 外, 它还能实现较大的输出电压摆幅. 为了能够实 现高直流增益, 采用增益增强技术, 整个运算放大 器结构如图 2所示. 为了能够获得较高的相位裕 度, 主放大器采用 PMOS管作为输入管, 这样可以 使电路更加稳定. 而且 P 管输入对减小运放的噪 声有一定的好处. 为了获得良好的匹配关系, 从而 大大减小由工艺带来的偏差, 辅助放大器采用全 差分折叠式共源共栅放大器. 辅助运放输入管子 类型的 选取, 主要 是 由 输 入 共 模范 围 决 定 的, PMOS共栅管的辅助放大器采用 NMOS 输入对,

摘 要: 在 3. 3 V 电源电压下采用中芯国际 ( SM IC ) 0. 18 Lm 混合信号 CM O S工艺设计了一个单级全差分 运算放大器. 所设计的运放采用了增益提升技术, 其主运放为一个带有开关电容共模反馈的全差 分折叠 共源共栅运放 , 两个简单的连续时间共模反馈电路的运放作为辅运 放用来提升主运放的开环增益. 仿真结 果表明, 所设计的运放直流增益可达 110 dB, 单位增益带宽为 5 MH z.

单级放大器的结构主要有套筒式放大器和折 叠式放大器, 与前者相比, 后者具有功耗大、折叠 处寄生电容高等缺点, 但它却具有较高输出电压 摆幅, 套筒式运算放大器多消耗一个过驱动电压, 这在低压工艺中体现得越发重要. 除此之外, 后者 输入电压的共模范围比前者大得多, 这在 A /D 的 采样保持电路中具有明显优势, 特别是在采用误 差消除技术中, 在一定时间段内要求输入和输出 短接, 这使后者成为唯一选择.

4 偏置电路

为了使偏置电路与主电路有一致性, 而且主 运放与辅助运放尽量用一个偏置电路, 本放大器 所设计的偏置电路如图 5.

26

辽宁大学学报 自然科学版

2009 年

5 仿真结果

使用 SM IC 0. 18 Lm 工 艺对 该电 路进行 仿 真, 在其负载为 3 pF 时, 得到其直 流增益为 110 dB, 单位增益带宽为 5 MH z. 结果如图 6, 仿真放 大器性能如表 1.

参 考文献:

[ 1] 毕 查 德 # 拉 扎 维. 模 拟 CM O S 集 成 电 路 的 设 计 [M ]. 西安: 西安交通大学出版社, 2000.

[ 2] PAUL R. GRAY. 模拟集成电路的分析与设计 [ M ]. (第 4版 ). 北京: 高等教育出版社.

[ 3] R. Jacob Bake. CM OS电路设计布局 与仿真 [M ]. 北 京: 机械工业出版社, 2006.

* 作者简介: 李 佳 ( 1982-) , 女, 辽宁铁岭人, 讲师, 从事微电子技术研究. 基金项目: 沈阳市攻关项目 ( 1071115) 1) 00)

收稿日期: 2008-10-17

第 1期

李 佳, 等: 全差分高增益运放的设计

25

NM 0S共栅管则采用 PMOS 输入对. 由于辅助放 大器的引入, 它与共栅管形成一个闭环. 所以辅助 放大器的速度不能太高, 否则会出现稳定问题. 但 是辅助放大器的单位增益频率必须大于主放大器 的 - 3 dB 频率. 最后由经验得到, BXu < X < X2. BXu是闭环系统的主极点, X 是辅助运放的单位 增益带宽, X2 是主运放的第二极点.

Key w o rds: fu lly differentia;l ga in boosted op am p. operat iona l am plifier.

(责任编辑 郑绥乾 )

该共模反馈电路的好处是对运放的输出摆幅 没有任何限制, 不会增加电路的阻抗, 也没有静态 功耗. 其基本工作原理是: 当 < 2 为高时, C 1 和 C2 并联, C2 两端的直流电压由 C 1 决定, 并且在每个 < 2 周期内进行刷新. 当 < 1 为高时, C1 两 端的充 电到 Vocm - V cm fb, 其中 V ocm 为期望 的输出共 模电 压, V cm fb为输出共模电压为理想值时电流源管的 栅电压. 电容 C 2 产生电流源管的偏置电压 Vcm = ( Vout1 + Vou t2 ) /2- ( V ocm - V cmfb ).

关键词: 全差分; 增益提 升; 运放.

中图分类号: TN432 文献标识码: A 文章编号: 1000-5846( 2009) 01-0024-03

随着工艺尺寸和电源电压的不断降低, 普通 运算放大器大概能实现 50- 60 dB 的直流增益. 而一些高精度 A /D要求放大器的直流增益为 100 dB, 两级放大器虽然能 实现较高的增益, 但其功 耗太大, 并且速度也很难满足要求. 这样增益增强 技术应运而生.

图 1 增益增强技术原理图 图 2 运放整体图

3 共模反馈电路

虽然全差分电路有很多优点, 诸如大的输出 电压摆幅, 避免了镜像极点, 消除了偶次项失真和 抑制了衬底噪音等, 但差分电路唯一的一个缺点 就是要求有共模反馈电路 ( CM FB ) 来稳定输出共 模电压. 本论文中的主放大器采用开关电容形式 的共模反馈电路 [ 2] , 如图 3.

表 1 仿真结果

性能指标

直流增益 / dB 相位裕度 / ( b) 建立时间 ( 0. 001% ) / ns 差分输出摆幅 /V

功耗 /mW

仿真结果

110 89 350 3 0. 5

6 结论

分析和设计了一个采用增益增强技术的折叠

式共源共栅全差分放大器. 具有高直流增益, 大输 出摆幅. 主放大器和辅助放大器采用不同的共模 反馈电路来优化设计和降低功耗. 本放大器如果 应用于高速电路中, 还需调节放大器的单位增益 带宽, 使之满足速度的要求.

辽宁大学学报 自然科学版

第 36卷 第 1 期 2009年

JOURNAL OF LIAONING UNIVERSIT Y

N atural Sciences Ed ition V o.l 36 N o. 1ቤተ መጻሕፍቲ ባይዱ2009

全差分高增益运放的设计

李 佳 * , 万祥义, 石广源

(辽宁大学 物理 学院, 辽宁 沈阳 110036)

CMFB电路中的电容增加了运放的负载, 因 此应尽量减小, 但必须与共模电压的精度和共模 环路的稳定性进行折中. 共模电压的精度与共模 环路的增益、电容的取值有关, 而选择 C1 大于 C2 可以减小稳态误差、电荷注入误差和漏电流误差, 并且还可以使共模电压获得较快的建立时间.

辅助运放采用连续时间的共模反馈电路 [ 3] , 连续时间共模反馈电路如图 4.

Abstrac:t A single stage fully differential operationa l am plifierw as designed in SM IC 0. 18 Lm m ixed sig-

nal CMOS techno logy w ith 3. 3 V pow er supp ly. The designed Op Am p utilizes ga in boosting techn ique. T he m a in Op Am p is a fully d ifferent ial folded cascode Op Amp w ith sw itched capacitor CMFB. Two sim ple continuous tim e CMFB Op Am ps are used as aux iliary Op Am p to increase the open loop gain o f the m ain Op Am p. The sim ulat ion resu lts show that the designed Op Am p ach ieves a DC ga in of 110 dB w ith a un ity gain frequency of 5 MH z.

Designed for Fully D ifferentialH igh G ain Operational Amplifier

L I Jia, WAN X iang-y,i SH I Guang-yuan (The C ollege of P hysics, L iaoning University, Shenyang 110036, China )