高频接收机和发射机中的锁相环-第2部分

移动通信终端构成与工作原理

Page 28

通信终端技术

外围电路模块-关机部分

电源管理芯片 CPU 关机触发

1、当长按关机键时触发关机操作,CPU输出信号给睡眠时钟和电源管理芯片。

2、睡眠时钟工作,电源管理芯片停止输出供电,手机振铃电路、显示电路、射 频电路 停止工作完成关机操作。

睡眠时钟

Page 29

通信终端技术

关于移动终端开关机问题的几点说明:

•

睡眠时钟为手机提供计时的基准频率,不论是否开机,只要电池有电就可起振。它 供向电源管理芯片和CPU,以维持手机的时间准确,并提供关机后的计时功能,从 而支持关机闹钟。

32.768KHz实时时钟的作用一般有两个,一是保持手机中时间的准确性,二是在待机状态下,作为逻辑电路 的主时钟(目的是为了节电,待机时13M间隔工作的周期延长,基本处于休眠,逻辑电路主要由32.768KHz 作为主时钟)。

由于电池电压的不稳定和器件对电压、电流要求的精确性与多样性, 最重要的是出于降低功耗的考虑,手机需要专门的电源管理单元。 对各种电压的要求: 内核电压:电压较低,要求精确度高,稳定性好。 音频电压:模拟电压,要求电源比较干净,纹波小。 I/O 电压:要求在不需要时可以关闭或降低电压,以减少功耗。 功放电压:由于电流要求较大,直接由电池供电。

1、无论是上电还是复位后,软件首先进行各个任务的初始化,最后判断当前电源开关是处于 开状态还是关状态,如果是处于开状态,立即执行正常的开机过程(如执行小区搜索及开机注

册等),如果是处于关状态,则判断当前是否有外接电源,如果有,则一直等待直到开机;否

则就立即发起关机。如果在等待开机过程中外接电源被拔掉,手机同样也会发起关机。 2、手机开机后,如果没有外接电源,并且电池采样电压低于电池关机门限时,手机发起关机。 如果只有外接电源,并且外接电源的采样电压低于了外接电源存在门限,手机同样发起关机。

(完整版)锁相环工作原理

基本组成和锁相环电路1、频率合成器电路频率合成器组成:频率合成器电路为本机收发电路的频率源,产生接收第一本机信号源和发射电路的发射信号源,发射信号源主要由锁相环和VCO电路直接产生。

如图3-4所示。

在现在的移动通信终端中,用于射频前端上下变频的本振源(LO),在射频电路中起着非常重要的作用。

本振源通常是由锁相环电路(Phase-Locked Loop)来实现。

2.锁相环:它广泛应用于广播通信、频率合成、自动控制及时钟同步等技术领域3.锁相环基本原理:锁相环包含三个主要的部分:⑴鉴相器(或相位比较器,记为PD或PC):是完成相位比较的单元,用来比较输入信号和基准信号的之间的相位.它的输出电压正比于两个输入信号之相位差.⑵低通滤波器(LPF):是个线性电路,其作用是滤除鉴相器输出电压中的高频分量,起平滑滤波的作用.通常由电阻、电容或电感等组成,有时也包含运算放大器。

⑶压控振荡器(VCO):振荡频率受控制电压控制的振荡器,而振荡频率与控制电压之间成线性关系。

在PLL中,压控振荡器实际上是把控制电压转换为相位。

1、压控振荡器的输出经过采集并分频;2、和基准信号同时输入鉴相器;3、鉴相器通过比较上述两个信号的频率差,然后输出一个直流脉冲电压;4、控制VCO,使它的频率改变;5、这样经过一个很短的时间,VCO 的输出就会稳定于某一期望值。

锁相环电路是一种相位负反馈系统。

一个完整的锁相环电路是由晶振、鉴相器、R分频器、N分频器、压控振荡器(VCO)、低通滤波器(LFP)构成,并留有数据控制接口。

锁相环电路的工作原理是:在控制接口对R分频器和N分频器完成参数配置后。

晶振产生的参考频率(Fref)经R分频后输入到鉴相器,同时VCO的输出频率(Fout)也经N分频后输入到鉴相器,鉴相器对这两个信号进行相位比较,将比较的相位差以电压或电流的方式输出,并通过LFP滤波,加到VCO的调制端,从而控制VCO的输出频率,使鉴相器两输入端的输入频率相等。

第2章发射机和接收机

第2章 发射机和接收机本章讨论用于无线传输的发射机和接收机的设计。

使用的术语将有如下界定的含义:从调制器直至发射天线的各部件构成发射机,而从接收天线直至解调器的各部件则构成接收机。

对发射机和接收机的要求显然是不同的,这是因为发射机只须处理所要求的信号,而接收机则须从天线接收的各种频率混合的信号中将所要求的信号提取出来。

此外,发射机处理的信号强度是恒定的,或者仅有很微小的变化,而接收机所应对的信号强度差异极大,其大小取决于与发射机的远近程度。

发射机主要欲达到的目标有:将有用信号转换为干扰尽可能小的高频传输信号、以尽可能最高的效率放大信号、并使转换或放大所产生的不良干扰信号的传输降至最低。

接收机主要欲达到的目标有:在邻近频率范围接收到很强信号的同时,还要从强度很弱的信号中将所要求的信号过滤出来,并产生一个清晰的、具有高信噪比和最低互调失真的信号。

因此,就发射机而言,主要难点在效率;而接收机所面临的是选择性、动态范围和噪声等问题。

2.1 发射机我们首先考虑模拟方式调制的发射机结构,其后再讨论数字方式调制的发射机。

其中,借助一些简化的方框图来加以说明,这些方框图将只显示出基本的组成部分。

2.1.1 模拟方式调制的发射机直接调制型发射机当模拟调制器的载波频率f C 与发射频率f RF 相同时,就实现了最简单的发射机。

在这种情况下,只需将调制器的输出信号放大并馈送到天线。

在实际应用中,发射放大器必须后接一个输出滤波器,以使源于放大器的信号失真降低到可接受的水平。

图2.1(a )所示为直接调制型发射机结构,其信号频谱如图2.2所示。

单中频发射机随着频率的增高和需求的增长,使得要实现所需精度的调制器越发困难。

因此,要用较低的中频f IF 作为载波频率f CC IF RF f f f =使用中频可以更容易地构建调制器。

图2.1(b )所示为单中频发射机的结构,它用混频器M1将中频f IF 转换为发射频率f RF ,由本机振荡器(Local Oscillator ,LO )向混频器提供频率LO RF IF f f f =−混频处理所产生的和频与差频为LO IF RF f f f +=,LO IF RF IF 2f f f f −=−其中,发射频率部分用RF 滤波器滤出,然后馈入发射机放大器。

PLL02

当输入信号频率固定时,锁定后 控制频差=固有频差。 稳态频差=0 ∆ 稳态相差 θ e (∞) = are sin KF ωj00 ) (

第四节 一阶环的捕获、锁定 与失锁

当F(p)=1时,环路的动 态方程是一个一阶非 线性方程。 pθ e (t ) = pθ1 (t ) − K sin θ e (t ) 1: 可以解析求解。 2:采用图解法求解。

是一个电压频率变换装置在环路中作为被控振荡器其振荡频率随输入控制电压线性地变化环路的相位模型鉴相特性鉴相器是一个相位比较装置用来检测输入信号相位?之间的相位差t

锁相技术 第二讲

• PLL的环路组成 • PLL环路的动态方程 • 一阶锁相环的捕获、锁定与失锁

锁相技术教案PLL--02

第二节 锁相环路的基本组成

u d (t ) = u d sin θ e (t )

环路滤波器LF

环路滤波器是一个线性电路,在时域中可以用 一传输算子F(p)表示,在频域中可以用传递函 数F(s)表示。 • RC积分滤波器。 • 无源比例滤波器 • 有源比例滤波器。

RC积分滤波器

RC积分滤波器是结构最简单的滤波器

传输算子是:

1 + pτ 2 F= pτ 1

环路的相位模型

上面是一个基本的锁相环路的相位模型。 下面是用锁相环组成的单环频率合成器的相位模型

压控振荡器VCO

VCO的振荡频率应随输入控制电压线性

ω 变化。 ν

式中 ν 为VCO的瞬时角频率;K0控制 灵敏度,单位是rad/s.v。

VCO具有一个各积分因子1/p,这是相位 与角频率之间的积分关系形成的。

MC145162锁相环(中文)

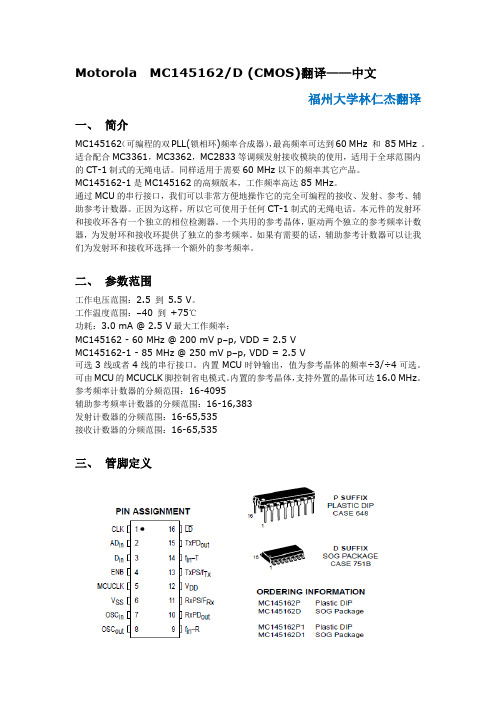

Motorola MC145162/D (CMOS)翻译——中文福州大学林仁杰翻译一、简介MC145162(可编程的双PLL(锁相环)频率合成器),最高频率可达到60 MHz 和85 MHz 。

适合配合MC3361,MC3362,MC2833等调频发射接收模块的使用,适用于全球范围内的CT-1制式的无绳电话。

同样适用于需要60 MHz以下的频率其它产品。

MC145162-1是MC145162的高频版本,工作频率高达85 MHz。

通过MCU的串行接口,我们可以非常方便地操作它的完全可编程的接收、发射、参考、辅助参考计数器。

正因为这样,所以它可使用于任何CT-1制式的无绳电话。

本元件的发射环和接收环各有一个独立的相位检测器。

一个共用的参考晶体,驱动两个独立的参考频率计数器,为发射环和接收环提供了独立的参考频率。

如果有需要的话,辅助参考计数器可以让我们为发射环和接收环选择一个额外的参考频率。

二、参数范围工作电压范围:2.5 到5.5 V。

工作温度范围:–40 到+75℃功耗:3.0 mA @ 2.5 V最大工作频率:MC145162 - 60 MHz @ 200 mV p–p, VDD = 2.5 VMC145162-1 - 85 MHz @ 250 mV p–p, VDD = 2.5 V可选3线或者4线的串行接口。

内置MCU时钟输出,值为参考晶体的频率÷3/÷4可选。

可由MCU的MCUCLK脚控制省电模式。

内置的参考晶体,支持外置的晶体可达16.0 MHz。

参考频率计数器的分频范围:16-4095辅助参考频率计数器的分频范围:16-16,383发射计数器的分频范围:16-65,535接收计数器的分频范围:16-65,535三、管脚定义输入端:OSCin/OSCout——参考晶体输入/输出引脚(第7、8脚)当连接到一个外接的并联谐振晶体的时候,这些引脚组成了一个参考振荡器。

应用在各国的无绳电话时,图6显示了不同的晶体频率和参考频率的关系。

高频课程设计报告_调频发射机

高频课程设计报告_调频发射机目录1. 内容概述 (2)1.1 课程背景 (3)1.2 报告目的 (3)1.3 报告结构 (4)2. 调频发射机概述 (5)2.1 调频通信原理 (6)2.2 调频发射机组成 (7)3. 调频发射机设计要求 (8)3.1 系统指标 (10)3.2 性能要求 (11)4. 设计方案与实现 (11)4.1 发射机结构设计 (13)4.2 高频电路设计 (14)4.3 调制和解调电路设计 (15)4.4 电源模块设计 (17)5. 调试与优化 (19)5.1 测试方法 (21)5.2 调试过程 (22)5.3 性能优化 (23)6. 测试结果与分析 (25)6.1 发射功率 (26)6.2 频谱纯度 (27)6.3 调制质量 (28)6.4 系统稳定性 (30)7. 结论与展望 (31)7.1 设计总结 (32)7.2 存在问题 (34)7.3 未来改进方向 (35)1. 内容概述本报告详细介绍了调频发射机的高频课程设计,围绕其工作原理、设计要点、实现路径以及未来改进方向展开深入探讨。

从调频发射机的基本原理出发,我们讨论了信号调制、载波频率的调整以及功率放大等关键技术点。

报告紧密结合实际工程需求,详尽阐述了调频发射机的工作著魔步骤和各个模块的功能设计,包括射频前端、调制器、功率放大器等核心部件。

在分析过程中,我们考虑了复杂信号环境下的抗干扰性设计,确保信号传输的稳定性和清晰度。

通过对调频发射机的仿真和数据分析,本报告优化了不同负载条件下的性能表现,为实际生产提供了有效的理论支持。

本课程设计报告还包括了项目实施过程中的遇到的挑战和解决方案,同时讨论了调频发射机在现代无线通信技术中的应用及其市场潜力。

报告最后展望了的未来科技发展趋势,提出了进一步提升调频发射机性能的潜在技术和创新方向。

通过本报告的学习与应用,读者能够获得关于高频调频发射机设计过程的全面了解,并为后续相关研究提供有益的参考和指导。

三相锁相环算法

三相锁相环算法三相锁相环算法是一种常用的控制算法,用于同步两个或多个信号的相位和频率。

它在许多领域中都有广泛的应用,如通信系统、电力系统和自动控制系统等。

本文将详细介绍三相锁相环算法的原理、应用和优缺点。

一、原理三相锁相环算法的原理基于负反馈控制的思想。

它通过比较输入信号和参考信号的相位差,然后根据相位差的大小调整输出信号的频率和相位,从而使输出信号与参考信号保持同步。

具体来说,三相锁相环算法包括三个主要组件:相位检测器、环路滤波器和压控振荡器。

相位检测器用于测量输入信号与参考信号的相位差,环路滤波器用于平滑相位差的变化,压控振荡器用于调整输出信号的频率和相位。

二、应用三相锁相环算法在通信系统中有着广泛的应用。

例如,在无线通信系统中,接收机需要与发射机保持同步,以确保信号的正确接收。

通过使用三相锁相环算法,接收机可以根据接收到的信号与发射信号之间的相位差,自动调整自身的频率和相位,实现同步接收。

三相锁相环算法还可以应用于电力系统中。

在电力系统中,各个发电机需要同步工作,以确保电网的稳定运行。

通过使用三相锁相环算法,发电机可以根据电网的频率和相位差,自动调整自身的频率和相位,实现与电网的同步。

三相锁相环算法还可以应用于自动控制系统中。

例如,在自动驾驶系统中,多个传感器需要同步工作,以提供准确的环境感知数据。

通过使用三相锁相环算法,各个传感器可以根据参考信号,自动调整自身的频率和相位,实现同步工作。

三、优缺点三相锁相环算法具有以下优点:1. 可以实现快速同步:三相锁相环算法可以快速地将输出信号与参考信号同步,确保信号的准确接收或传输。

2. 高精度的同步:三相锁相环算法可以达到很高的同步精度,通常可以达到纳秒级别的精度。

3. 稳定性好:三相锁相环算法通过负反馈控制,可以实现对相位差的稳定控制,使系统具有良好的稳定性。

然而,三相锁相环算法也存在一些缺点:1. 系统复杂:三相锁相环算法由多个组件组成,需要进行参数调整和系统优化,增加了系统的复杂性。

二阶数字锁相环

二阶数字锁相环二阶数字锁相环(Second-Order Digital Phase-Locked Loop,简称SODPLL)是数字信号处理领域中常用的一种技术,其主要功能是实现信号同步和频率稳定。

在很多通信系统中,由于接收到的信号可能会受到各种干扰和非理想因素的影响,因此需要通过锁相环技术将信号同步到参考信号上,以保证数据的准确传输。

本文将围绕着二阶数字锁相环展开,介绍其原理、结构以及应用。

一、SODPLL原理二阶数字锁相环的原理是通过比较参考信号和输出信号的相位差,然后对其进行差分和积分,使得输出信号的相位始终保持在参考信号的相位之内。

相位差可以通过一些算法,比如arctan函数、反正切函数等等来计算。

SODPLL比一阶数字锁相环(First-Order Digital Phase-Locked Loop)具有更高的追踪精度和更快的锁定速度,因此在很多领域中被广泛应用。

二、SODPLL结构SODPLL主要由三个主要部分组成:相位检测器、滤波器和控制器。

相位检测器负责计算输入信号与参考信号之间的相位差,滤波器通过对相位差进行差分和积分运算,生成控制信号,控制器则通过控制VCO(VoltageControlled Oscillator)的输出,将输出信号锁定在参考信号上。

1. 相位检测器相位检测器是SODPLL中的核心部分,也是决定SODPLL性能的关键因素。

常用的相位检测器有三种:平均相位检测器(Average Phase Detector)、正弦相位检测器(Sine Phase Detector)和二分频相位检测器(Binary Phase Detector)。

其原理分别如下:平均相位检测器:将输入信号和参考信号分别进行取平均值操作,然后取它们的差值,得到相位差。

平均相位检测器的优点是简单易实现,缺点是追踪速度慢,追踪误差大。

正弦相位检测器:将输入信号和参考信号均输入到正弦函数中,然后将它们的乘积相加,得到相位差。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

⎜⎟ ⎝ fm ⎠

⎥ ⎦⎥

(1)

where: LPM is single-sideband phase noise density (dBc/Hz) F is the device noise factor at operating power level A (linear) k is Boltzmann’s constant, 1.38 × 10–23 J/K T is temperature (K)

4. Choose an active device that has minimal noise figure as well as low flicker frequency. The flicker noise can be reduced by the use of feedback elements.

Noise in Oscillator Systems In any oscillator design, frequency stability is of critical importance. We are interested in both long-term and short-term stability. Longterm frequency stability is concerned with how the output signal varies over a long period of time (hours, days or months). It is usually specified as the ratio, ∆f/f for a given period of time, expressed as a percentage or in dB.

1

For Leeson’s equation to be valid, the following must be true: • fm, the offset frequency from the carrier, is greater than the 1/f

flicker corner frequency; • the noise factor at the operating power level is known; • the device operation is linear; • Q includes the effects of component losses, device loading and

Random Noise Fluctuation

Discrete Spurious Signal

Amplitude

f0

Frequency

Figure 1. Short-term stability in oscillators.

The discrete spurious components could be caused by known clock frequencies in the signal source, power line interference, and mixer products. The broadening caused by random noise fluctuation is due to phase noise. It can be the result of thermal noise, shot noise and/or flicker noise in active and passive devices.

A is oscillator output power (W) QL is loaded Q (dimensionless) fO is the oscillator carrier frequency fm is the frequency offset from the carrier

Analog Dialogue 33-5 (© 1999 Analog Devices)

Phase-Locked Loops for High-Frequency Receivers and Transmitters–Part 2

by Mike Curtin and Paul O’Brien The first part of this series of articles introduced the basic concepts of phase-locked loops (PLLs). The PLL architecture and principle of operation was described and accompanied by an example of where a PLL might be used in a communication system.

In this second part, we will focus on a detailed examination of two critical specifications associated with PLLs: phase noise and reference spurs. What causes them and how can they be minimized? The discussion will include measurement techniques and the effect of these errors on system performance. We will also consider output leakage current, with an example showing its significance in openloop modulation schemes.

In many radio systems, an overall integrated phase error specification must be met. This overall phase error is made up of the PLL phase error, the modulator phase error and the phase error due to base band components. In GSM, for example, the total allowed is 5 degrees rms.

noise transition

Offset Frequency, fm (Hz)

Figure 3. Phase noise in a VCO vs. frequency offset.

Leeson’s equation only applies in the knee region between the break (f1) to the transition from the “1/f ” (more generally 1/fγ) flicker noise frequency to a frequency beyond which amplified white noise dominates (f2). This is shown in Figure 3 [γ = 3]. f1 should be as low as possible; typically, it is less than 1 kHz, while f2 is in the region of a few MHz. High-performance oscillators require devices specially selected for low 1/f transition frequency. Some guidelines to minimizing the phase noise in VCOs are:

Phase Noise in Voltage-Controlled Oscillators Before we look at phase noise in a PLL system, it is worth considering the phase noise in a voltage-controlled oscillator (VCO). An ideal VCO would have no phase noise. Its output as seen on a spectrum analyzer would be a single spectral line. In practice, of course, this is not the case. There will be jitter on the output, and a spectrum analyzer would show phase noise.To help understand phase noise, consider a phasor representation, such as that shown in Figure 2.

buffer loading; • a single resonator is used in the oscillator.

Phase Noise (dBc/Hz)

9dB/Octave

6dB/Octave Leeson's Equation Applies

f0 / 2QL

Flat

f1

f2

1/f flicker

Short-term stability, on the other hand, is concerned with variations that occur over a period of seconds or less.These variations can be random or periodic. A spectrum analyzer can be used to examine the short-term stability of a signal. Figure 1 shows a typical spectrum, with random and discrete frequency components causing a broad skirt and spurious peaks.