FPGA设计的秒表设计实验报告

基于FPGA的秒表实验

基于FPGA的秒表实验目的4个七段数码管分别表示十分分十秒秒当SW0为1的时候,暂停计时,进入设置。

按BTN0时秒加1,按BTN1时增加10秒按BTN2时增加1分,按BTN3时增加10分module miaobiao(clk,out,out1,control,btn);//模块名及端口input clk,control,btn;//输入端口声明output out,out1;//输出端口声明wire control;//输入控制信号是wire类型wire [3:0] btn;//四位按键reg [6:0] out1;//定义段选7位寄存器reg [3:0] out;//定义位选4位寄存器reg [31:0] count;//定义一个计数器reg [3:0] sec_l,sec_h,min_l,min_h,out2;//定义存储秒、十秒、分、十分的寄存器,还有显示寄存器供译码用;initial out1 <= 7'b0000001;//给段选赋初值,刚开始时位0000always @(posedge clk)//计数行为语句begincount = count + 1;if ((count==50000000)&&(control==0))//进行分频与控制信号的检测,控制信号为假,继续计数beginsec_l = sec_l +1;count = 0;if(sec_l==10)beginsec_l=0;sec_h = sec_h + 1;if(sec_h == 6)beginsec_h = 0;min_l = min_l + 1;if (min_l==10)beginmin_l = 0;min_h = min_h + 1;if(min_h==6)min_h = 0;endendendendelse if((count==50000000)&&(control==1))//控制信号为真,进入操作模式begincount = 0;if (btn[0]==1)beginsec_l = sec_l + 1;if (sec_l==10)sec_l = 0;endif (btn[1]==1)beginsec_h = sec_h + 1;if (sec_l==6)sec_h = 0;endif (btn[2]==1)beginmin_l = min_l + 1;if (min_l==10)min_l = 0;endif (btn[3]==1)beginmin_h = min_h + 1;if (min_h==6)min_h = 0;endendendalways @(posedge clk)//时钟扫描(动态扫描)行为语句begincase(count[15:14])2'b00:begin out <= 4'b1110; out2 <= sec_l;end//打通第一个管子的时候,把秒寄存器的值给显示寄存器,显示寄存器通过译码转换为段码2'b01:begin out <= 4'b1101; out2 <= sec_h;end2'b10:begin out <= 4'b1011; out2 <= min_l;end2'b11:begin out <= 4'b0111; out2 <= min_h;endendcaseendalways @(posedge clk)//译码行为语句,根据显示寄存器的值,译为2进制代码来赋予电平信号,打通led管begincase(out2)0:out1 <= 7'b0000001;1:out1 <= 7'b1001111;2:out1 <= 7'b0010010; 3:out1 <= 7'b0000110; 4:out1 <= 7'b1001100; 5:out1 <= 7'b0100100; 6:out1 <= 7'b0100000; 7:out1 <= 7'b0001111; 8:out1 <= 7'b0000000; 9:out1 <= 7'b0000100; endcaseendendmodule。

基于FPGA的电子秒表设计

基于FPGA的电⼦秒表设计基于FPGA的电⼦秒表设计摘要简⽽⾔之,电⼦秒表的⼯作原理就是不断输出连续脉冲给加法计数器,⽽加法计数器通过译码器来显⽰它所记忆的脉冲周期个数。

电⼦秒表是⽇常⽣活中⽐较常见的电⼦产品。

本设计秒表的逻辑结构主要由74LS00, 555定时器,RS 触发器,74LS90等器件组成。

使⽤了基本RS触发器作为电⼦秒表的开关,基本RS触发器属低电平直接触发的触发器,有直接置位,复位的功能。

整个秒表需有⼀个清零/ 启动信号和⼀个停⽌/保持信号装置,以便秒表能随意停⽌及启动,计数器的输出全都为BCD码输出,⽅便显⽰译码器连接。

本设计基于简单易⾏的原则,秒表显⽰以0.01s为最⼩单位,设计时,按照设计任务的次序,将各单元电路逐个进⾏接线和调试,即分别测试基本RS触发器、时钟发⽣器及计数器的逻辑功能,待各单元电路⼯作正常后,再将有关电路逐级连接起来进⾏测试……,直到测试电⼦秒表整个电路的功能。

最后进⾏总结.做到经典⽽没有缺憾的设计结果。

关键字:74LS00 555定时器 RS触发器 BCD码⽬录摘要 (1)⼀、引⾔ (3)(⼀)设计的背景 (3)(⼆)设计实现的基本功能 (4)(三)设计的结构安排 (4)⼆、系统硬件设计 (5)(⼀)总体设计 (5)(⼆)555定时器简简介 (9)(三)基本RS触发器 (10)(四)功能测试 (12)三、系统软件设计 (14)(⼀) 设计⽅案 (14)(⼆)分频模块 (14)(三)计数模块 (16)(四)启停控制模块 (17)(五)显⽰控制模块 (18)(六)编译仿真 (19)参考⽂献 (22)致谢 (23)⼀、引⾔(⼀)设计的背景秒表计时器是电器制造,⼯业⾃动化控制、国防、实验室及科研单位理想的计时仪器,他⼴泛应⽤于各种继电器、电磁开关、控制器、延时器、定时器等的时间测试。

有关电⼦秒表的发展历史,⼤致可以分为三个演变阶段。

1、从⼤型钟向⼩型钟演变。

2、从⼩型钟向袋表过度。

FPGA 数字秒表的设计

学院FPGA设计实践报告题目:数字秒表的设计院系:计算机与信息工程学院专业:电子科学与技术年级姓名:学号:指导老师:一、课程设计目的:本课程的授课对象是电子科学与技术专业本科生,是电子类专业的一门重要的实践课程,是理论与实践相结合的重要环节。

本课程有助于培养学生的数字电路设计方法、掌握模块划分、工程设计思想与电路调试能力,为以后从事各种电路设计、制作与调试工作打下坚实的基础。

二、课程设计要求:l. 设计用于体育比赛用的数字秒表, 要求:⑴计时精度应大于l/100S, 计时器能显示1/100S的时间, 提供给计时器内部定时的时钟脉冲频率应大于l00Hz, 这里选用1kHz 。

⑵计时器的最长计时时间为l小时, 为此需要一个6位的显示器, 显示的最长时间为59分59.99秒。

2. 设置有复位和起/停开关⑴复位开关用来使计时器清零, 并作好计时准备。

⑵起/停开关的使用方法与传统的机械式计时器相同, 即按一下起/停开关, 启动计时器开始计时, 再按一下起/停开关计时终止。

⑶复位开关可以在任何情况下使用,即使在计时过程中, 只要按一下复位开关, 计时进程立刻终止, 并对计时器清零。

3. 复位和起/停开关应有内部消抖处理。

4. 采用VHDL语言用层次化设计方法设计符合上述功能要求的数字秒表。

5. 对电路进行功能仿真, 通过有关波形确认电路设计是否正确。

6. 完成电路全部设计后, 通过系统实验箱下载验证设计课题的正确性。

三、系统组成与工作原理:数字秒表框图:1、电路原理图 :2、工作原理:l.计时控制器作用是控制计时。

计时控制器的输入信号是启动、暂停和清零。

为符合惯例, 将启动和暂停功能设置在同一个按键上, 按一次是启动, 按第二次是暂停, 按第三次是继续。

所以计时控制器共有2个开关输入信号, 即启动/暂停和清除。

计时控制器输出信号为计数允许/保持信号和清零信号。

2. 计时电路的作用是计时, 其输入信号为lkHz 时钟、计数允许/保持和清零信号, 输出为l0ms、l00ms、s 和min 的计时数据。

基于FPGA数字秒表设计

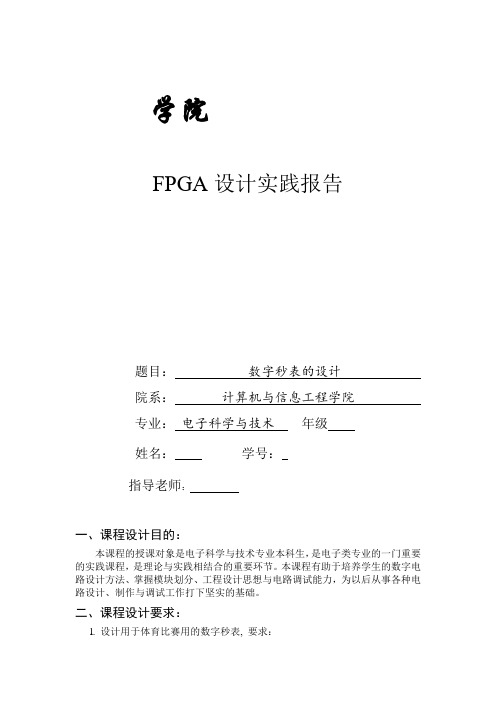

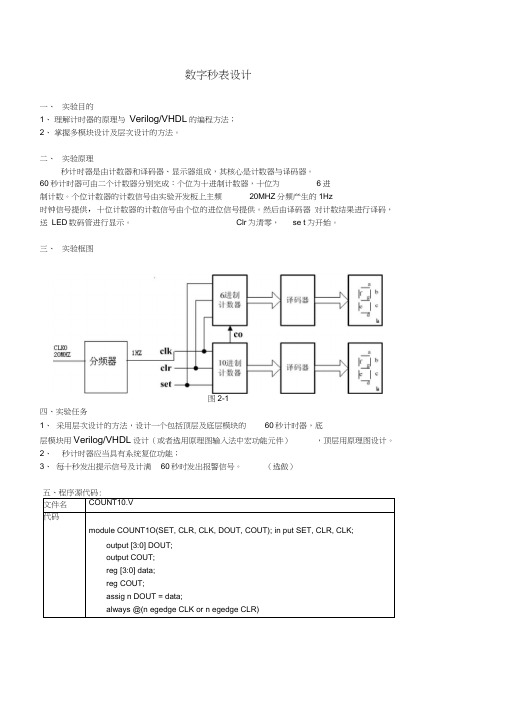

数字秒表设计一、实验目的1、理解计时器的原理与Verilog/VHDL的编程方法;2、掌握多模块设计及层次设计的方法。

二、实验原理秒计时器是由计数器和译码器、显示器组成,其核心是计数器与译码器。

60秒计时器可由二个计数器分别完成:个位为十进制计数器,十位为6进制计数。

个位计数器的计数信号由实验开发板上主频20MHZ分频产生的1Hz时钟信号提供,十位计数器的计数信号由个位的进位信号提供。

然后由译码器对计数结果进行译码,送LED数码管进行显示。

Clr为清零,se t为开始。

三、实验框图图2-1四、实验任务1、采用层次设计的方法,设计一个包括顶层及底层模块的60秒计时器,底层模块用Verilog/VHDL设计(或者选用原理图输入法中宏功能元件),顶层用原理图设计。

2、秒计时器应当具有系统复位功能;3、每十秒发出提示信号及计满60秒时发出报警信号。

(选做)文件名COUNT10.V代码module COUNT1O(SET, CLR, CLK, DOUT, COUT); in put SET, CLR, CLK;output [3:0] DOUT;output COUT;reg [3:0] data;reg COUT;assig n DOUT = data;always @(n egedge CLK or n egedge CLR)4'HF: Q<=7'H71 ;default: Q<=7'B1111111;endcaseenden dmoduleCOUNT60.bdf文件名原理图五、实验步骤1•创建工程2•选择目标器件3. 编写verilog hdl程序4编译5. 生成符号文件6. 创建编辑原理图7. 设置顶层文件8编译六、实验结果1. 编译结果Flow StatusQuartos II VersionRevisicxi NameTop^vel Entity NarneFamlyDeviceTrning ModdsMet timmg requiTiefrientsTata logic ate merit ETold conbinatKMial fundioni Dedfcatcd logic registers Total negiateFBTotal pinsTot日virtual pinsTotaJ rnemory bits&vibedded Multiplier &dements Total PLLs SuccessfLi - Sat Nov 01 11:12:49 30149 1 Build 222 10/21/200& SJ Wet> Editicri COUNTSCOUNTGOl^done I IIEP3C5E144C8Fmi^lN/AG3/5.136( 1 X)33/5.136(<1 X)3J26/96(27*}Q/4?3^36<0%)0/4&(D%)0/2(0%)2. 仿真结果文件名COUNT6.V仿真结果Mann 白Value i17.B F^07ua邑更 g ^?JE^7ub ia-19 JB 71字麼甲 5 33—0宀^^4CLKCLHSETCOUTB D0UTHDH1卜1HD卜0TLrLrLrLnrLrLnnrLrLrLrLrLrLrLrLrLnjTrLrLrLrLrLrumfmrLrLrLrLri L r~1 i 1 i厂-n n文件名COUNT10.V9. 创建编辑波形图文件10. 使用波形图仿真11. 锁定管脚12. 编译13. 下载至芯片仿真结果文件名仿真结果17J?5na■TLTLrLnirLrLrWLn_ruwwjwrLnjmjirLrLrwin_ruijWWUi[n JTT ®(n2XDE®®o^oD203®2xnixD®(n®®©(n2XD®@i®OE®i®<ri i i _______ i i _______COUNT60.V (为了简便将分频器设置2分频的)C_KfHRSET 冋DOITH hiDOirn uOH5 xHUTL_nu jnlimnninmmiMmmmmrimimmMJMominroinnrumiminmTmmmnnrmim!irrno“j 厂JCJZ : 前t 底—I 強—r 耶弋騙工如丫非—仍丈丸朗代熾:璇绽帰它狀减燉麒^峨*]炊輕烫处好號爼仞XCOK切默XX*X*X5XIMM*>X*iXXXAN WtXXXCO Z備出七、实验小结通过本次实验,我掌握了分频器的设计,学习了如何通过原理图设计,知道了如何在一个工程中同时使用verilog hdl程序和原理图。

fpga秒表设计实验报告

fpga秒表设计实验报告本次实验是基于FPGA设计的秒表。

秒表主要是用来计时的一种仪器,具有精准度高、显示清晰等优点。

在实验中,我们使用FPGA来实现秒表的设计。

1. 实验目的通过本次实验,我们的目的是掌握FPGA的使用方法,并设计出一个能够精准计时的秒表。

同时,也能够加深理解数字电路的基本原理和数字信号的处理方式。

2. 实验原理秒表的原理很简单,在起点按下计时键后,秒表开始计时,时间会显示在数码管或LCD屏幕上。

在终点按下停止键后,秒表停止计时。

我们需要用数字电路来实现这个过程,分为三个部分。

2.1. 时钟模块时钟模块是秒表实现的基础。

我们可以使用FPGA内置的时钟控制器IP,也可以自己实现时钟模块。

在这个实验中,我们使用了FPGA内置的时钟控制器IP。

2.2. 计时模块计时模块是实现秒表的关键。

我们可以使用FPGA内置的计数器IP,也可以自己实现计数器模块。

在这个实验中,我们使用了FPGA内置的计数器模块。

2.3. 显示模块显示模块用来显示计时结果。

我们可以使用数码管或LCD屏幕来显示计时结果。

在这个实验中,我们使用了数码管来显示计时结果。

3. 实验步骤3.1. 创建工程首先,我们需要在Vivado IDE中创建一个FPGA工程。

在创建工程时,需要选择适当的设备型号、板卡等参数。

3.2. 添加时钟控制器IP在Vivado IDE中,选择IP Catalog,搜索并添加时钟控制器IP。

3.3. 添加计数器IP在Vivado IDE中,选择IP Catalog,搜索并添加计数器IP。

3.4. 添加数码管IP在Vivado IDE中,选择IP Catalog,搜索并添加数码管IP。

3.5. 连接IP在Vivado IDE中,将时钟控制器IP、计数器IP和数码管IP进行连接。

3.6. 程序设计使用Vivado IDE中的HDL语言对秒表进行程序设计。

3.7. 烧录程序将程序烧录到FPGA中,实现秒表功能。

FPGA秒表实验报告

课程设计报告专业班级课程题目秒表的设计学号姓名同组人成绩2013年5月一、设计目的1.进一步熟悉七段码译码器的硬件接口。

2.掌握用扫描方法驱动多个数码管硬件接口。

3.掌握秒表VHDL的编程方法。

二、系统总体设计(1).设计要求:1.秒表共有6个输出显示,分别为百分之一秒、十分之一秒、秒、十秒、分、十分,所以共有6个计数器与之相对应,6个计数器的输出全都为BCD码输出,这样便于和显示译码器的连接。

当计时达60分钟后,蜂鸣器鸣响10声。

2.整个秒表还需有一个启动信号和一个归零信号,以便秒表能随意停止及启动。

3.秒表的逻辑结构较简单,它主要由显示译码器、分频器、十进制计数器、六进制计数器和报警器组成。

在整个秒表中最关键的是如何获得一个精确的100HZ 计时脉冲。

(2).实验原理:秒表由于其计时精确,分辨率高(0.01秒),在各种竞技场所得到了广泛的应用。

秒表的工作原理与数字时基本相同,唯一不同的是秒表的计时时钟信号,由于其分辨率为0.01秒,所以整个秒表的工作时钟是在100Hz的时钟信号下完成。

当秒表的计时小于1个小时时,显示的格式是mm-ss-xx(mm表示分钟:0~59;ss 表示秒:0~59;xx表示百分之一秒:0~99),当秒表的计时大于或等于一个小时时,显示的和多功能时钟是一样的,就是hh-mm-ss(hh表示小时:0~99),由于秒表的功能和钟表有所不同,所以秒表的hh表示的范围不是0~23,而是0~99,这也是和多功能时钟不一样的地方。

在设计秒表的时候,时钟的选择为100Hz。

变量的选择:因为xx(0.01秒)和hh(小时)表示的范围都是0~99,所以用两个4位二进制码(BCD码)表示;而ss(秒钟)和mm(分钟)表示的范围是0~59,所以用一个3位的二进制码和一个4位的二进制码(BCD)码表示。

显示的时候要注意的问题就是小时的判断,如果小时是00,则显示格式为mm-ss-xx,如果小时不为00,则显示hh-mm-ss。

FPGA秒表实验报告

课程设计报告专业班级课程题目秒表的设计学号姓名同组人成绩2013年5月一、设计目的1.进一步熟悉七段码译码器的硬件接口。

2.掌握用扫描方法驱动多个数码管硬件接口。

3.掌握秒表VHDL的编程方法。

二、系统总体设计(1).设计要求:1.秒表共有6个输出显示,分别为百分之一秒、十分之一秒、秒、十秒、分、十分,所以共有6个计数器与之相对应,6个计数器的输出全都为BCD码输出,这样便于和显示译码器的连接。

当计时达60分钟后,蜂鸣器鸣响10声。

2.整个秒表还需有一个启动信号和一个归零信号,以便秒表能随意停止及启动。

3.秒表的逻辑结构较简单,它主要由显示译码器、分频器、十进制计数器、六进制计数器和报警器组成。

在整个秒表中最关键的是如何获得一个精确的100HZ 计时脉冲。

(2).实验原理:秒表由于其计时精确,分辨率高(0.01秒),在各种竞技场所得到了广泛的应用。

秒表的工作原理与数字时基本相同,唯一不同的是秒表的计时时钟信号,由于其分辨率为0.01秒,所以整个秒表的工作时钟是在100Hz的时钟信号下完成。

当秒表的计时小于1个小时时,显示的格式是mm-ss-xx(mm表示分钟:0~59;ss 表示秒:0~59;xx表示百分之一秒:0~99),当秒表的计时大于或等于一个小时时,显示的和多功能时钟是一样的,就是hh-mm-ss(hh表示小时:0~99),由于秒表的功能和钟表有所不同,所以秒表的hh表示的范围不是0~23,而是0~99,这也是和多功能时钟不一样的地方。

在设计秒表的时候,时钟的选择为100Hz。

变量的选择:因为xx(0.01秒)和hh(小时)表示的范围都是0~99,所以用两个4位二进制码(BCD码)表示;而ss(秒钟)和mm(分钟)表示的范围是0~59,所以用一个3位的二进制码和一个4位的二进制码(BCD)码表示。

显示的时候要注意的问题就是小时的判断,如果小时是00,则显示格式为mm-ss-xx,如果小时不为00,则显示hh-mm-ss。

FPGA实验报告5篇

FPGA实验报告5篇第一篇:FPGA实验报告FPGA实验报告专业:XXX 姓名:XXX 学号:XX一:实验目的1.熟悉Modelsim和Quartus II软件的运行环境和使用2.熟练使用Quartus II仿真软件生成网表。

3.熟悉FPGA前仿真和后仿真的整个流程。

二:实验内容编写counter计数器,在Quartus II仿真软件中生成网表,再在Modelsim中进行后仿真。

三: 实验步骤1.在Modelsim编写源程序(counter计数器及激励),编译源文件,确保程序的正确性,并进行前仿真,生成波形图如下:附:源程序如下:module counter(q,clk,reset);input clk,reset;output [3:0] q;reg [3:0] q;always @(posedge reset or negedge clk)if(reset)q <= 4'b0;elseq <= q + 1;endmodule module top;reg CLK,RESET;wire [3:0] Q;counter c1(Q,CLK,RESET);initialCLK=1'b0;always#1 CLK=~CLK;initial$monitor($time,“Q=%d”,Q);initialbeginRESET=1'b1;#5 RESET=1'b0;#180 RESET=1'b1;end endmodule 2.新建文件夹,将源程序counter.v放进去。

然后启动Quartus II仿真软件,生成网表。

1).在【File】下拉菜单中选中New Project Wizard选项,出现对话框。

并指定工程工作目录、工程名称和顶层模块名,如图(a)所示。

2).添加(Add)counter.v文件。

如图(b)所示。

3).选择器件系列4).指定其它EDA工具,如图(d)所示。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

《FPGA原理及应用》

实验报告书

(7)

题目秒表设计

学院专业

姓名学号

指导教师

2015年10-12月

一、实验目的

掌握小型电路系统的 FPGA 设计法。

二、实验内容

用文本法结合原理图的方法设计一个秒表,并在实验箱上进行验证。

秒表基本功能要求如下:

(1)要求设置复位开关。

当按下复位开关时,秒表清零并做好计时准备。

在任何情况下只要按下复位开关,秒表都要无条件地进行复位操作,即使是在计时过程中也要无条件地进行清零操作。

(2)要求设置启/停开关。

当按下启/停开关后,将启动秒表并开始计时,当再按一下启/停开关时,将终止秒表的计时操作。

(3)要求计时精确度大于秒。

要求设计的计时器能够显示分(2 位)、秒(2 位)、秒(1 位)的时间。

(4)要求秒表的最长计时时间为 1 小时。

要求外部时钟频率尽量高,分频后再给秒表电路使用。

三、实验条件

1、开发软件:QuartusⅡ

2、实验设备:KX_DN8EDS实验开发系统

3、拟用芯片:EP3C55F484C8

四、实验设计

1、六进制计数器

仿真波形

2、十进制计数器

3、分频计

4、七段数码管译码器

5、100进制原理图

6、60进制原理图

7、秒表原理图

8、管脚锁定

新建好工程文件,芯片选择Cyclone Ⅲ下面的EP3C55F484C8系列。

然后锁定引脚:选择Assignments → Assignments Editor命令。

9、编译文件下载

将编译产生的SOF格式配置文件下载进FPGA中。

10、FPGA实验箱接线

在KX-EDA40A++实验箱上进行连线,分配J4,J5的引脚,输入CLK(PIN_接到时钟信号,输入的EN,RST 接到电平开关L1,L2。

五、实验总结

经过本次实验,我对QuartusⅡ的使用认识更加深刻,对FPGA技术有了更深层次的认识,有助于我对以后的电子电路设计有极大帮助。