一种基于CPLD的单片机与PCI接口设计解决方案

毕业设计137基于单片机+CPLD体系结构的信标机设计

基于单片机+CPLD体系结构的信标机设计摘要在机场的无线电通信导航设备中,信标机是一种重要的导航设备,因此对信标机的研究和设计具有十分重要的战略意义。

我撰写的论文题目是基于“单片机+CPLD体系结构的信标机设计”,此论文主要针对现在使用的信标机设计技术及元器件类型相对陈旧,实现功能过于手工化、分离元件过多,体积大、重量大、维修困难等问题,为实现设备的小型化、模块化和标准化,进一步提高设备的集成度和可靠性,提高智能化,为此,我根据目前广泛应用于各类仪器、设备中的单片机、CPLD器件,对基于单片机+CPLD体系结构的信标机设计方法进行了浅显的探讨。

设计的主要内容如下:1.对单片机、CPLD和FPGA性能特点进行分析,提出了基于“单片机+CPLD体系结构”的信标机设计方案;2.在CPLD中实现音频信号分频的计算方法,给出了设计原理图;3.单片机与CPLD接口以总线方式实现译码、数据和控制锁存功能的VHDL设计;4.信标发射机的设计;5.给出了整机监控流程图和单片机监控程序的编制。

本文详细介绍了信标机的实现方法,对实现信标机的小型化、微机化进行了有益的尝试,具有一定意义。

关键词单片机信标机 CPLDBased on “MCU+CPLD Architecture”to design beacon tranmitterAbstractBeacon transmitter is an important device to the wired comunication and navigation in airport,so it's of great strategic value to make applied researches.This paper's name is baseed on "MCU+CPLD Architecture" to design beacon transmitter. this thess points out some disadvantages of device ,such as technology backward in technique and type of components obsolete,manual operations,many absolute components,very large size and weight,operating and maintaining diffculty. In order to small size and modules and standardization ,and improve the device's intergrated and very high enough realiability ,intelligence, I explored the methodof beacon transmitter's designing based on "MCU+CPLD Architecture",according to MCU,CPLD components applied to the many instrument and device.The major work of this dissertation is as follows.1. Analysising the feature of MCU,CPLD, FPGA, I provided the method of beacon transmitter basee on "MCU+CPLD Architecture".2. Audio signal frequency is implemented in CPLD,give the schematic of the designing.3. Decording,latching data controlling signals are implemented in CPLD by interface between MCU and CPLD.4. Beacon transmitter's designing.S. Drawing the flow chart and making the MCU controlling and monitered programe.This paper introduced the method of the beacon transmitter, and gived the advantage tastes bymaking beacon transmitter very small size and controlled by computer.Key words MCU beacon transmitter CPLD目录第一章绪论 (1)1.3研究背境 (2)第二章解决方案、设计内容和技术难点 (3)2. 1解决方案 (3)2.1.1 CPLD/FPGA器件及EDA设计技术 (3)2.1.2“单片机+CPLD体系结构”的特点 (5)2.2设计内容 (7)2.2.1信标机的系统结构框图 (7)2.3技术难点 (8)2. 3. 1 CPLD与单片机的接口方式 (8)2. 3. 2 CPLD片内功能的实现 (8)2.3.3可编程逻辑器件的选型 (8)第三章CPLD片内逻辑功能设计 (9)3. 1 CPLD选型 (9)3. 1. 1 CPL。

毕业设计171基于CPLD的DSP系统接口设计

基于CPLD的DSP系统接口设计中文摘要本论文详细介绍了基于CPLD的DSP系统接口设计的方案与实现方法。

在本次设计过程中,主要是以模块思想来设计整个DSP系统。

在整个硬件系统设计中,以DSP芯片为核心,用CPLD来实现控制数据中转、与外围设备的通信。

本论文介绍了如何利用CPLD设计并实现TMS320C5416芯片与SRAM、FLASH、串并转换器等外围设备之间的接口,即利用了CPLD 实现TMS320C5416系统接口的扩展。

关键词:DSP;系统接口; CPLDDesign DSP system connection with CPLDAbstractThe present paper in detail introduced the DSP system connection of based on the CPLD designs plan and the realization method. In this design process, mainly designs the entire DSP system by the module of thought.In the entire hardware system design process, takes the DSP chip as the core, realizes the control data relay by the CPLD decoding, and the auxiliary equipment correspondence. This introduced how switching using CPLD connection designs the between TMS320C5416 chip and SRAM, FLASH, string and auxiliary equipment and so on, namely used CPLD to design the TMS320C5416 system connection the expansion.Key words: DSP ; The interface of system ;CPLD第一章:绪论§1.1 课题的提出及意义随着信息化技术的飞速发展,各种便携式电子产品和个人助理不断涌现,但是,许多消费电子的采集处理系统有着自身的不足,采集装置的复杂化,图像实时处理对处理器的依赖,图像处理系统的造价、速度及体积都成为限制图像技术应用的瓶颈。

基于VHDL_CPLD的I2C串行总线控制器设计及实现.

集谴电路瞳舶基于VHDL/CPLD的12C串行总线控制器设计及实现钱敏,黄秋萍,李富华,刘蓓(苏州大学电子信息学院微电子系,江苏苏州215021)摘要:分析了12C串行总线的数据传输机制,用VHDL设计了串行总线控制电路,其中包括微处理器接口电路和12C总线接口电路。

采用ModelSimPlus6.0SE软件进行了前仿真和调试,并在XilinxISE7.1i开发环境下进行了综合、后仿真和CPLD器件下载测试。

结果表明实现了12C串行总线协议的要求。

关键词:12C串行总线控制器接口电路VHDLCPLD串行总线和并行总线相比具有结构简单、占用引脚其传输过程为:首先主机产生起始位,然后传送第一个少、成本低的优点。

常见的串行总线有USB、1EEEl394、字节。

8位数据中首先传送的是数据的最高位MSB,最12C等,其中12C总线具有使用简单的特点,在单片机、串低位LSB为读写指示位,1表示主机读,0表示主机写,行E2PROM、LCD等器件中具有广泛的应用。

高7位地址可使主机寻址128个从器件。

12C(InterICBUS)是Philips公司开发的用于芯片之从机收到第一字节数据后发响应位,主机收到响应间连接的总线。

12C总线用两根信号线进行数据传输,位后接着发送第二个字节的数据。

数据发送完毕后产生一根为串行数据线(SDA),另一根为串行时钟线(SCL)。

结束位,数据传送结束。

数据传送时,只有时钟SCL为低12C总线允许若干兼容器件(如存储器、A/D转换器、D/A电平时SDA才允许切换,SCL为高电平时SDA必须稳转换器、LCD驱动器等)共享总线。

12C总线理论上可以定,此时SDA的电平就是总线转送的数值。

允许的最大设备数,是以总线上所有器件的总电容(其在SCL为高电平时,SDA线由高到低切换表示起始中包括连线本身的电容和连接端的引出电容)不超过位,SDA线由低到高切换表示停止位。

起始位和停止位400pF为限,总线上所有器件依靠SDA线发送的地址信由主机产生,在起始位产生后总线处于忙状态,停止位号寻址,不需要片选线。

探究低功耗CPLD设计-设计应用

探究低功耗CPLD设计-设计应用随着科技的发展,很多技术对于现在的工程师在设计上是必要的。

每个便携设备或者手持设备工程师都知道使功耗化是当前设计需要的。

但是,一个经验丰富的工程师就会明白微妙的细节可以使电池寿命延长到。

这篇文章主要关注老练的怎样使用极低功耗的CPLD 从嵌入式设计的I/O子系统里去挤出一点功耗。

我们先回顾一下CPLD在嵌入式设计中一般被用来减少功耗和版大小,以及BOM成本。

接下来,我们看怎样在待机模式下减少CPLD功耗,不只是小心选择设备,而且是选择一个合适的总线结构。

我们在工作状态下的节能探索将包括选择逻辑门技术,智能I/O设计技术及电压供电管理技术。

便携式或手持产品涉及任何工程师都知道,降低功耗消费是对今后的设计是必要的。

其中重要的细节便是怎么延伸一个系统的电池寿命的值。

在这篇文章中我们将重点放在如何将这些经验丰富的采用超低功耗复杂可编程逻辑器件(CPLD)来了解智能I / O子系统的嵌入式设计。

我们将首先检讨如何CPLD是常用来缩小嵌入式设计功率,电路板空间和BOM成本。

下一步,我们将看到一个CPLD如何尽量减少在其待机模式功耗,不仅通过仔细选择器件本身,而且还通过选择适当的巴士泊车计划。

我们的节能探索在积极运作,包括技术,如选择性的逻辑门,智能I / O设计和精密的电源电压管理。

备用电源基础在掌握功耗CPLD的步是要了解设备在他们的经营行为和待机状态(也称为静态)。

由于许多器件在待机状态下度过了大部分时间,我们将仔细看看这个经常被误解模式。

CPLD是一个据说是在待机状态时,该设备已申请其输入功率但其内部的逻辑是不计时。

在这种状态下,仍然吸引CPLD的一些权力由于其漏电流和偏置(虽然大大低于当它的实际运作)。

泄漏电流会随着温度的变化,工作电压和制造工艺。

一个CPLD内偏置电流是由负载,如内部振荡器,上拉/下来我电路/ O线和其他固定开销,目前无论是无论设备的逻辑功能正在使用。

用CPLD实现单片机与ISA总线接口的并行通信

用CPLD 实现单片机与ISA 总线接口的并行通信摘要:介绍了用ALTERA 公司MAX7000系列CPLD 芯片实现单片机与 PC104ISA 总线接口之 间的关行通信。

给出了系统设计方法及程序源代码。

关键词:CPLD ISA 总线并行通信CP LD( Comp lex P rogrammable Logic Device )是一种复杂的用户可编程逻辑器件, 由于采用连续连接结构,易于预测延时,从而使电路仿真更加准确。

集成电路产品,可用于各种数字逻辑系统的设计。

近年来,由于采用先进的集成工艺和大 指量生产,CPLD 器件成本不断下降,集成密度、速度和性能大幅度提高,一个芯片就可以 实现一个复杂的数字电路系统;再加上使用方便的开发工具,使用CPLD 器件可以极大地缩 短产品开发周期,给设计修改带来很大方便[1]。

本文以ALTERA 公司的MAX7000系列为例, 实现MCS51单片机与PC104ISA 总线接口的并行通信。

采用这种通信方式,数据传输准确高 速,在12MHz 晶振的MCS51单片机控制的数据采集系统中,可以满足与 PC104 ISA 总线接1系统总体设计方案用CPLD 实现单片机与PC104ISA 总线接口的并行通信, 由于PC104主要完成其它方面 的数据采集工作,只是在空闲时才能接收单片机送来的数据,所以要求双方通信的实时性 很强,但数据量不是很大。

因此在系统设计中,单片机用中断方式接收数据, 查询方式接收数据。

系统设计方案如图1所示。

在单片机部分,D [0..7]是数据总线,A [0..15]是地址总线,RD 和WR 分别是读写信号CPLD 是标准的大规模 口实时通信的要求,通信速率达200Kbps 。

P C104采用PC1O4ISA 总线接口之间的数据传输、状态查询及延时等待。

在PC104ISA 部分,只用到 PC104的8位数据总线 D[0..7] ,A[0..9]是PC104的地址 总线;/IOW 和/IOR 是对指定设备的读写信号;AEN 是允许DMA 控制地址总线、数据总线和读写命令线进行 DMA 专输以及对存储器和I/O 设备的读写;IOCHRDY 是I/O 就绪信号,I/O信号为低电平使 CPU 插入等待周期,从而延长 I/O 周期;SYSCLK 是系统时钟信号,使系统与外部设备保持同步; RESETD 是上电复位或系统初始化逻辑信号,是系统总清信号。

基于CPLD_单片机和网络的固态调制器触发控制

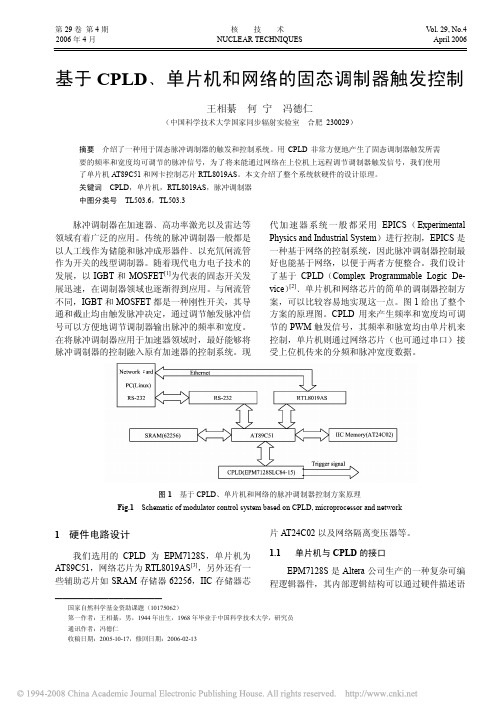

第29卷 第4期 核 技 术 V ol. 29, No.4 2006年4月 NUCLEAR TECHNIQUES April 2006——————————————国家自然科学基金资助课题(10175062)第一作者:王相綦,男,1944年出生,1968年毕业于中国科学技术大学,研究员 通讯作者:冯德仁收稿日期:2005-10-17,修回日期:2006-02-13基于CPLD ﹑单片机和网络的固态调制器触发控制王相綦 何 宁 冯德仁(中国科学技术大学国家同步辐射实验室 合肥 230029)摘要 介绍了一种用于固态脉冲调制器的触发和控制系统。

用CPLD 非常方便地产生了固态调制器触发所需要的频率和宽度均可调节的脉冲信号,为了将来能通过网络在上位机上远程调节调制器触发信号,我们使用了单片机A T89C51和网卡控制芯片RTL8019AS 。

本文介绍了整个系统软硬件的设计原理。

关键词 CPLD ,单片机,RTL8019AS ,脉冲调制器 中图分类号 TL503.6,TL503.3脉冲调制器在加速器﹑高功率激光以及雷达等领域有着广泛的应用。

传统的脉冲调制器一般都是以人工线作为储能和脉冲成形器件﹑以充氘闸流管作为开关的线型调制器。

随着现代电力电子技术的发展,以IGBT 和MOSFET [1]为代表的固态开关发展迅速,在调制器领域也逐渐得到应用。

与闸流管不同,IGBT 和MOSFET 都是一种刚性开关,其导通和截止均由触发脉冲决定,通过调节触发脉冲信号可以方便地调节调制器输出脉冲的频率和宽度。

在将脉冲调制器应用于加速器领域时,最好能够将脉冲调制器的控制融入原有加速器的控制系统。

现代加速器系统一般都采用EPICS (Experimental Physics and Industrial System )进行控制,EPICS 是一种基于网络的控制系统,因此脉冲调制器控制最好也能基于网络,以便于两者方便整合。

我们设计了基于CPLD (Complex Programmable Logic De-vice )[2]﹑单片机和网络芯片的简单的调制器控制方案,可以比较容易地实现这一点。

基于单片机的PCI总线通信功能设计

基于单片机的PCI总线通信功能设计————————————————————————————————作者:————————————————————————————————日期:郑州大学毕业设计(论文)题目:基于ARM的PCI总线通信功能设计指导教师:职称:学生姓名:学号:专业:院(系):完成时间:2011年5月25日年月日摘要本文详细介绍了基于AT91RM9200单片机的PCI总线通信功能的设计,包括硬件设计和软件设计两部分.通信功能的设计着重于单片机与上位机之间通过PCI总线进行的数据传送.本次设计在于用比较容易掌握的单片机来实现PCI控制器的功能,在PCI总线的简单运用场合,大大简化了设计的复杂程度。

设计的实现是利用单片机的I/O口与PCI 总线的控制信号线以及地址/数据信号线等直接相连,用对单片机的编程来控制数据的传输.文中介绍了PCI总线的基本概念,一些重要信号的定义,以及PCI总线事务的时序。

单片机部分介绍了型号的选择,选择了AT91RM9200单片机的理由和AT91RM9200单片机的基本知识.本次设计选择AM29LV160和57V561620作为AT91RM9200外接存储器。

设计的结果是成功的完成了原理图绘制和PCB版图的设计,和实验仿真。

关键词:PCI总线单片机AbstractThis paper introduces in detail the communication function design of the PCI bus based on AT91RM9200 MCU, including hardware design and software design。

Communication function design focuses on the data transfer between SCM and PC by PCI bus。

The design is to use MCU to realize the function of PCI controller,which is easier to master。

基于DWC_PCIE_Core的数据传输系统设计

基于DWC PCIE Core的数据传输系统设计刘肖婷1,2(1.北京全路通信信号研究设计院集团有限公司,北京 100070;2.北京市高速铁路运行控制系统工程技术研究中心,北京 100070)摘要:在铁路信号系统中,为有效减少铁路信号系统设备C P U 资源占用率,设计一种基于D W C PCIE Core 的数据发送与接收系统。

该系统采用内嵌ARM Cortex-A9双核的FPGA 开发板套件,利用FPGA 的灵活性和可扩展性,采用可配置的PCIE 硬核IP 模块以及以太网硬核IP 模块。

该系统主要介绍Host PC 与FPGA 之间基于PCIE 2.0的DMA 数据传输以及FPGA 之间基于GMAC 的以太网数据传输,通过PCIe 总线、以太网基于DMA 模块实现数据高速可靠传输。

关键词:DWC PCIE Core ;FPGA ;数据传输;DMA 中图分类号:U284.7 文献标志码:A 文章编号:1673-4440(2024)01-0026-04Design of Data Transmission System Based on DWC PCIE CoreLiu Xiaoting 1, 2(1. CRSC Research & Design Institute Group Co., Ltd, Beijing 100070, China )(2. Beijing Engineering Technology Research Center of Operation Control Systems for High Speed Railways, Beijing 100070, China )Abstract: In the railway signaling system, a data sending and receiving system based on DWC PCIECore is designed to reduce the CPU resource occupancy of railway signaling system. The system adopts FPGA development board suite embedded with ARM Cortex-A9 dual core, which takes the advantage of the fl exibility and scalability of FPGA, and uses confi gurable PCIE hard core IP module and confi gurable Ethernet hard core IP module. This paper mainly introduces the realization of high-speed and reliable data transmission through PCIE bus and Ethernet based on DMA modules between Host PC and FPGA and between FPGA boards.Keywords: DWC PCIE Core; FPGA; data transmission; DMADOI: 10.3969/j.issn.1673-4440.2024.01.005收稿日期:2020-12-29;修回日期:2023-12-19基金项目:国家重点研究计划项目(2022YFB4300600)作者简介:刘肖婷(1989—),女,工程师,硕士,主要研究方向:嵌入式软件开发,邮箱:*********************.cn 。

基于单片机和CPLD的等精度频率计设计

在 升沿触发的, 在Tpr 时间内 对Fx 的计数Nx 无误差;在此时间内Fs 的计 数Ns 最多相差一个脉冲, 即!p et I< 1, 1 09下

式成立:

Fx/ Nx=Fs/ Ns Fxe/ Nx =Fs/ (Ns+ p et ) 所以有:

S C IENCE & TECHNOLOGY INF OR MA T ION

T‘ 技

术

基于单片机和 CP LD 的等精度频率计设计

魏景田

( 古林省古林市环境卫生科学研究所)

摘 要: 本文主要论述了利用CPLD 进行测频计数, 单片机实施控制实现多功能频率计的设计过程。该频率计利用CP LD 来实现频率、 周期、 脉宽和占空比的测量计数, 利用单片机完成整个测量电路的测试控制、数据处理和显示输出。 关键词:频率计 测频 等精度 单片机 CPLD 中图分类号:T M935 文献标识码: A 文章编号: 1672- 3791(2007)12(a卜0072- 02

Fx = (Fs/ Ns)*Nx

图2 系统原理框图

图 3 R9试原理框

科技资讯 SCIENCE & 丁 ECHNOLOGY INFORMATION

丁 技

术

马上跳转到测频子程序, 测频子程序先置测频 控制位 CLR(PI A , TF(P l . 1), CHOISE(P1. 2) , CPLD 内的计数器清零, 将 然后通过键盘 将预置门的时间值读入单片机, 扣开预置门进 行测频计数, 等预置门时间到后, 关断预置门, CPLD 关断预置门后将给单片初一个结束信 号, 单片机读到结束信号后, 通过置 IADRA, ADR B】的四个状态, 分四次将测频结果的 32 位数据读人单片机, 计算后将结果转换为 BCD 码送LED 显示输出。 测频主程序: / / R3 为最高位 h }fOV R4, 74H

基于DSP的PCI接口设计与实现

D S P芯 片不支 持 P C I 总线 接 口 , 无 法 与其他 P C I 总线 设备 通信 。 因此 文 中以 D S P芯 片外 部存 储 器 总线 为接 口设 计 实现 了

一

数据管理的 D P R A M, 使D S P 芯片可直接通过 P C I 总线访问外部设备并响应其他 P C I 设备发来的操作 , 实现通过 P C I 总线

d o i : 1 0 . 3 9 6 9 / j . i s s n . 1 6 7 3 — 6 2 9 X. 2 0 1 3 . 0 8 . 0 2 9

De s i g n a nd Re a l i z a t i o n o f PCI I n t e r f a c e Ba s e d o n DS P

第2 3卷

第 8期

计 算 机 技 术 与 发 展 源自C0MP UT ER T ECHNOL 0GY AND DEVEL OP MENT

2 0 1 3年 8月

Vo l _ 2 3 No . 8 Aug . 2 01 3

基 于 DS P的 P C I 接 口设 计 与 实 现

Abs t r a c t : P CI h a d b e e n c o n s i d e r e d a s o n e o f t h e mo s t wi d e l y u s d e p a r a l l e l b u s e s . DS P c h i p s a l s o h a d e x t e n s i v e a p pl i c a t i o n i n d i g i t a l s i g — n l a p r o c e s s i n g ie f l d. Ho we v e r . p r e s e n t l y mo s t DS P c ip h s d i ( h l ’ t s u p p o r t t h e P CI i n t e fa r c e n o t t O c o mmu n i c a t e wi t h o he t r PCI . i n t r o d u c d e

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

PLDCPLDFPGA应用中文核心期刊《微计算机信息》(嵌入式与SOC)2006年第22卷第6-2期文章编号:1008-0570(2006)06—2—田22垂-03一种基于CPLD的单片机与PCI接口设计解决方案AkindofaccordingtoCPLDofamachineandPCIconnectapeopleSdesignsolution(南京工业大学)高建华Gao。

Jianhua摘要:本文描述丁用赛灵恩公司的XC95216系列CPLD芯片实现扩展单片机与计算机PCI04的接口并行通信的穷法。

解决了在嵌入式攮谚系统申攀蔗撩岛主规总线设务蠢交遣资源不足的固有缺陷,把娃太网卡抟功巍集成在一冀XC95216蟋CPLD中,简化了硬件,邋信实时性强;并给出用VHDL编写的主鼹源程序。

该方案在实践中检验通过。

关键词:单片机;CPLD;PCI枣蚕分类号:翻眩7文献糠浚玛:嚣Abstract:ThearticleintroducemethodofparalldcommunicationbetweenexpandMCUandinterfaceofPCI04byCPLDchips(XC95216)ofxilinxcompany.ThemethodsalutedsomeproblemsofflushbondingOS&busdevicesinmainboardthatintegrat-ingthefunctionsofEthernetcardinCPLD(XC95216).ThearticlegavethemainprogramofVHDL.Themethodwaspassedbytestofpractice。

Keyword:MCU,;CPLD,PCI引言8位单片枫在嵌入式系统中应用广泛,然藤让它直接与PCI总线设备打交道却有其阐有缺陷。

8位单片机只有16位地址线,8位数据端姻,而PCI总线2.0规范中.除了有32位地址数据复用AD[3一Ol岁t-,还有FRAME、IRDY、TRDY等重要的信号线。

让单片机有限的I/O端鼙来直接控创如此众多的信号线是不可髓的。

一种可行的方案就是利用CPLD作为沟通单片机与PCI设备闻静桥梁,充分盥}』耀CPLD中I/O资源丰富、用户可自定制逻辑的优势,来帮助单片机完成与PCI设备问的通信任务。

1PCI接口设计原理1.1PCI总线协议篱介这星只讨论PCI总线2.0协议。

其它协议仅仅是在2。

0熬基础上作了一些扩屣,仅就单片桃与PCI设备间的通信来说,意义不大。

PCI总线是高性能局部总线,工作频率0—33MHz,可同时支持多组外围设备。

在这里.我{fj只关心单片机与一个PCI设备闻透信的情况.而且是以单片机与CPLD一方作为主控方,另一方作麦PCI铁设备。

这样傲的弱酶是为了简化阁题,降低系统造价。

PCI总线上信号线虽然多,但并不是每个信号都毒建华:助理王程舞硕士磷究生要用劐。

实际上PCI设备也并不会支持所有的信号线,比如错误报告信号PERR与SERR在网卡中就不支持。

我锏可戳针对具体憋应熏选择支持其中郝分信号线,还有一些信号线可以直接连电源或接地。

下面简单分绍一下常用信号线的功能。

AD[31—01:地址数据多路复用信号。

在FRAME有效的第一个周期为地址,在IRDY与TRDY同时有效的时候为数据。

C/BE[3—0】:总线命令与字节使能控制信号。

在地址中佟输的是总线命令:在数据嬲内是字节傻能控铡信号,表示AD[31—01中哪些字节是有效数据。

以下是总线命令编码鲍说明:C/BE[30]命令类型说明C/BE[30]#命令类型说明0000中断应答1000保留0001特殊周期1001保留0010I/O读1010配置读0011I/O写1011配置写0100保留1100存储器多行读010l保留1l01双地址周期0110存储器读1110存储器一行读0I11存储器写l1l1存储器墨并无效PCI总线上所有的数据传输基本上都由以下三条傣号线控制。

FRAME:桉周矮信号。

由主设备驱动,表示一次访问的开始和持续时间,FRAME有效时(0为有效,下阕>,表示数据传输进行中,失效后,为数据传输最霰一224—360元,警邮局订阕号:82-946 PLDCPLDFPGA应用一个周期。

IRD:主设备准备好信号。

由主设备驱动,表示主设备已经准备好进行数据传输。

TRDY:从设备准备好信号。

由从设备驱动.表示从设备已经准备好进行数据传输。

当IRDY与TRDY同时有效时,数据传输才会真正发生。

另外,还有IDSEL信号用来在配置空间读写期间作为片选信号。

对于只有一个PCI从设备的情况.它总可以接高电平。

IDSEL信号由从设备驱动,表示该设备已成为当前访问的从设备,可以不理会。

在PCI总线上进行读写操作时.PCI总线上的各种信号除了RST、IRQ、IRQC、IRQ之外,只有时钟的下降沿信号会发生变化。

而在时钟上升沿信号必须保持稳定。

1.2CPLD设计规划出于对单片机和CPLD处理能力和系统成本的考虑,下面的规划不支持PCI总线的线性突传输等需要连续几个数据周期的读写方式.而仅支持一个址周期加一个数据周期的读写方式。

对于大部分应用而言,这种方式已经足够了。

图1是经过简化后的PCI总线读写操作时序。

在CPLD内设有13个8位寄存器用来保存进行一次PCI总线读写时所需要的数据.其中pci_ad—dress0一pci—address3是读写时的地址数据:面]厂———一百万——]厂豫叫—————]厂AD涎玖茎塑×CBE二XDC至匝E×二图1简化的PCI写操作时序pcidatas0一pci—datas3是要往PCI设备写的数据;pci_cbe[3—0】保存地址周期时的总线命令;pci_cbe[7—4】保存数据周期时的字节使能命令:pci_data0一pci_data3保存从PCI设备返回的数据;pci—request是PCI总线读写操作状态寄存器,用于向单片机返回一些信息。

当单片机往pci_cbe寄存器写入一个字节的时候,会复位CPLD中的状态机。

触发CPLD进行PCI总线的读写操作:单片机则通过查询pci_request寄存器得知读写操作完成。

再从pci_data寄存器读出PCI设备返回的数据。

CPLD中状态机的状态转移图如图2所示。

每一个状态对应FRAME与IRD信号的一种输出,而其它输入输出信号线可由这两个信号线和pci_cbe的值及TRDY的状态决定。

当FRAME为有效时,AD[31—0]由pci—address驱动,而C/BE[3—0]由pci—cbe低4位驱动;当IRDY有效时,C/BE[3—01视总线命令,要么由pci—cbe高4位驱动,要么设为高阻态,而AD[31—01在pci_cbe[0]为“0”(PCI读命令)时,设为高阻态,而在pci—cbe[01为“1”(PCI写命令)时由pci_datas驱动。

另外一方面,一旦TRDY信号线变为低电平,AD[31—01线上的数据被送入pci—data寄存器,而C/BE[3一O】线上的数据被送入pci_request寄存器的低4位。

图2状态转移图考虑到在不正常情况下,PCI设备不会对PCI总线作出响应,即TRDY不会有效。

为了不使状态机陷入状态S2的僵持局面,另外增设了一个移位计数器myeounter。

当IRD信号有效时,计数器开始计数。

计数溢出之后.不论PCI总线操作是否完成.状态机都会从状态s2转移到状态S3,即结束PCI总线操作。

当TRDY有效时.会立即置位mycounter.cout。

PCI总线操作是否正确完成.可查询pci_request的最高位是否为“1”.而IRDY与FRAME的值可分别查询pci—request的第4位和第5位。

这两位反映了PCI总线操作所处的状态.两位都为“1”时可以认为PCI总线操作已经完成。

在实践中,如果单片机的速度不是足够快的话,可以认为PCI总线操作总是即时完成的。

2PCI设计接口实现2.1CPLDVHDL程序设计我们针对8位单片机控制PCI以太网卡进行了程序设计,CPLD器件选用Xilinx的XC95216系列。

针对以太网卡的特点在逻辑上进行了再次简化,最终程序将适配进XC95261芯片中.并在实践中检验通过。

以太网卡仅支持对配置空间和I/O空间的读写操作.而且这两个空问的地址都可以设置在0xFF以内,所以可以只用一个pci—address0寄存器,其它地址都直接设为“O”;如果再限制,每次只往网卡写入一个字节数据,则可以只用一个pci—datas0寄存器,其它数值在具体操作时设成与pci_datas0寄存器的一样即可。

2.2单片机PCI读写C语言程序设计在CPLD在帮助下,单片机读写PCI设备就变得相当简单。

首先,将pci_cbe等寄存器都声明为外部存@喇搠邮局订眠82删360.7L/-q--225—PLDCPLDFPGA应用中文核心期刊《微计算机信息》(嵌入式与SOC)2006年第22卷第6-2期储器变量,并根据CPLD的设计指定地址。

然后,传递(接150页)适当的参数给以下嚣个读写予函数,即可完成对PCI设备配置空间、I/O空间、存储器空间的读写操作。

从PCI设备的返回数据存放在全局变量savedata中。

实际土在写PCI设备时.也可以从pci到返回数据。

这个数据必须等于往PCI设备写的数据。

剩臻这一点可以进行差错检验帮故障判断,褫具体应用而定。

bdateunignedcharrequest;sbitIRDY0=request^4;sbitFRAME0=request^5;bitVALID=request^7;voidreadpci(unsignedcharaddr,unsignedcharcbe){pci_address0=addr;pcicbe=cbe;request=pci_request;while(!IRDY0&FRAMEO))request=pci_request;savedata0=pci—dataO;savedatal--pcidatal;savedata2=pci_data2;savedata3=pci_data3;遮!VALID)prinff(”Datareadisinvalid!”);lvoidwritepci(ucharaddr,ucharvalueO,ucharcbo){datauchartemp;pci—address0=addr;pci_datasO=xalueO;pci_cbe=cbe;request=pci_request;while(!(IRDY0&FRAME0))request=pci_request;谢!VALID)prlnff(”Datawriteisinvalid!”);}3结论震CPLD实现单片枫与PCI总线接鹭豹并行逶信,电路结构简单、体积小,1片CPLD芯片足够,并且控制方便,实时性强,遴信效率高。