半导体专业词汇

半导体mfg生产制造中常用的英文单词

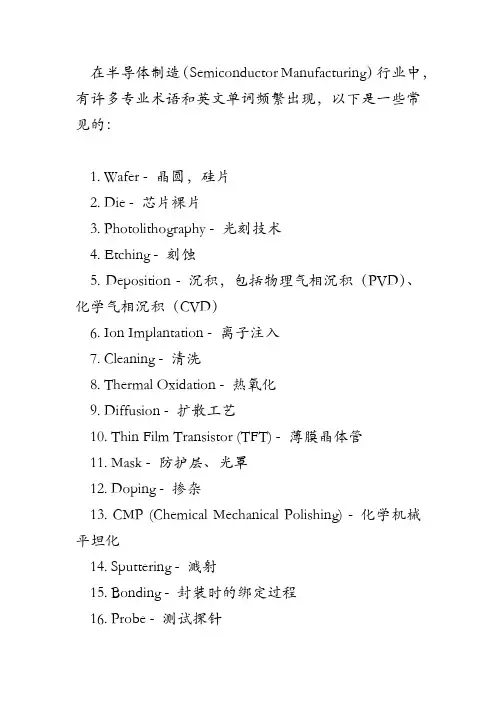

在半导体制造(Semiconductor Manufacturing)行业中,有许多专业术语和英文单词频繁出现,以下是一些常见的:1. Wafer - 晶圆,硅片2. Die - 芯片裸片3. Photolithography - 光刻技术4. Etching - 刻蚀5. Deposition - 沉积,包括物理气相沉积(PVD)、化学气相沉积(CVD)6. Ion Implantation - 离子注入7. Cleaning - 清洗8. Thermal Oxidation - 热氧化9. Diffusion - 扩散工艺10. Thin Film Transistor (TFT) - 薄膜晶体管11. Mask - 防护层、光罩12. Doping - 掺杂13. CMP (Chemical Mechanical Polishing) - 化学机械平坦化14. Sputtering - 溅射15. Bonding - 封装时的绑定过程16. Probe - 测试探针17. Final Test - 最终测试18. Packaging - 封装19. Silicon Wafer Fab - 晶圆厂20. Yield - 产出率,良率此外,还有许多与质量管理、设备维护、生产控制相关的词汇,例如:- Process Control - 工艺控制- Defect Inspection - 缺陷检测- Metrology - 测量科学- End-of-Line (EOL) Testing - 生产线末尾测试- Quality Assurance (QA) - 质量保证- Failure Analysis (FA) - 失效分析这些词汇共同构成了半导体制造行业的语言基础。

半导体专业词汇--汇总

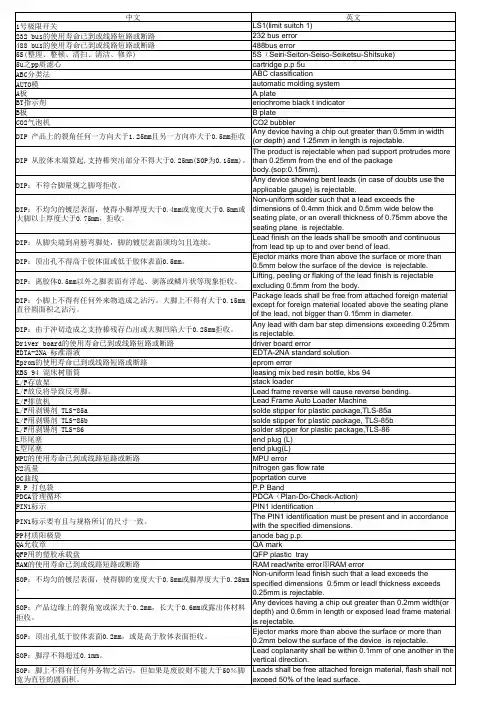

Lifting, peeling or flaking of the lead finish is rejectable excluding 0.2mm of the lead length from body. Any lead with dam bar step dimensions exceeding 0.1mm is rejectable. end plug (S) manager of XX department XX Electronics CO.Ltd X-ray yield X-ray X-ray inspection safety curtain safety stock safety glasses ammoniam water Press the emergency button. lot for lot lifted bond lifted wedge cavity plate,cavity block PPM (parts per million) Pareto chart plate mold semiconductor insufficient ball size off loader wrong orentation molding wrong orientation molding molding molding mold chase mold chase molding mismatch packing packing packing box packing defect criteria shipping box carrying cost carrying cost rate safety time holdup time shelf life scrap remark backside metal (Au/Ag) back side back marking chip package chips specific gravity specific gravity hydrometer closed loop MRP closing time bending side rail edge die reject die around slice edge side rail edge die Tape & Reel tape/real peel back force test braid flat cable,ribbon cable flat ball variation discoloration discolor(yellowish,blcken,water mark) discoloration/oxidation/lifting deformed

半导体专业词汇

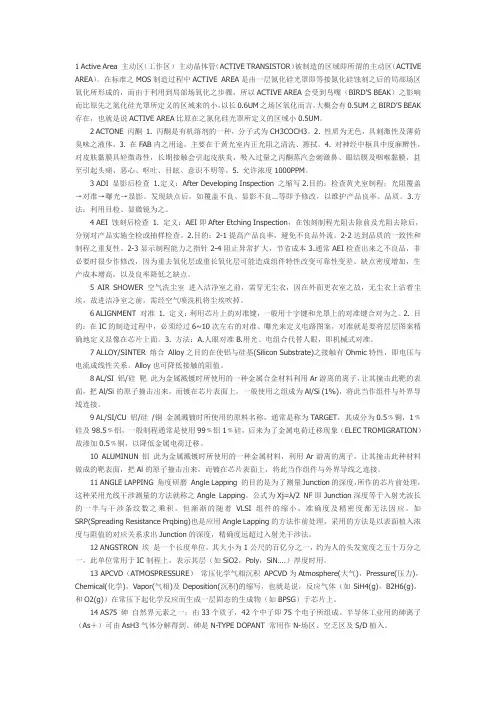

1 Active Area 主动区(工作区)主动晶体管(ACTIVE TRANSISTOR)被制造的区域即所谓的主动区(ACTIVE AREA)。

在标准之MOS制造过程中ACTIVE AREA是由一层氮化硅光罩即等接氮化硅蚀刻之后的局部场区氧化所形成的,而由于利用到局部场氧化之步骤,所以ACTIVE AREA会受到鸟嘴(BIRD’S BEAK)之影响而比原先之氮化硅光罩所定义的区域来的小,以长0.6UM之场区氧化而言,大概会有0.5UM之BIRD’S BEAK 存在,也就是说ACTIVE AREA比原在之氮化硅光罩所定义的区域小0.5UM。

2 ACTONE 丙酮1. 丙酮是有机溶剂的一种,分子式为CH3COCH3。

2. 性质为无色,具刺激性及薄荷臭味之液体。

3. 在FAB内之用途,主要在于黄光室内正光阻之清洗、擦拭。

4. 对神经中枢具中度麻醉性,对皮肤黏膜具轻微毒性,长期接触会引起皮肤炎,吸入过量之丙酮蒸汽会刺激鼻、眼结膜及咽喉黏膜,甚至引起头痛、恶心、呕吐、目眩、意识不明等。

5. 允许浓度1000PPM。

3 ADI 显影后检查1.定义:After Developing Inspection 之缩写2.目的:检查黄光室制程;光阻覆盖→对准→曝光→显影。

发现缺点后,如覆盖不良、显影不良…等即予修改,以维护产品良率、品质。

3.方法:利用目检、显微镜为之。

4 AEI 蚀刻后检查1. 定义:AEI即After Etching Inspection,在蚀刻制程光阻去除前及光阻去除后,分别对产品实施全检或抽样检查。

2.目的:2-1提高产品良率,避免不良品外流。

2-2达到品质的一致性和制程之重复性。

2-3显示制程能力之指针2-4阻止异常扩大,节省成本3.通常AEI检查出来之不良品,非必要时很少作修改,因为重去氧化层或重长氧化层可能造成组件特性改变可靠性变差、缺点密度增加,生产成本增高,以及良率降低之缺点。

5 AIR SHOWER 空气洗尘室进入洁净室之前,需穿无尘衣,因在外面更衣室之故,无尘衣上沾着尘埃,故进洁净室之前,需经空气喷洗机将尘埃吹掉。

半导体专业词汇汇总

半导体专业词汇汇总

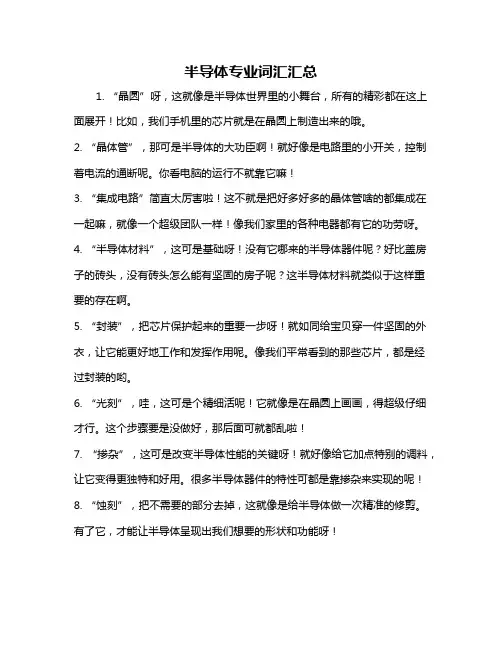

1. “晶圆”呀,这就像是半导体世界里的小舞台,所有的精彩都在这上面展开!比如,我们手机里的芯片就是在晶圆上制造出来的哦。

2. “晶体管”,那可是半导体的大功臣啊!就好像是电路里的小开关,控制着电流的通断呢。

你看电脑的运行不就靠它嘛!

3. “集成电路”简直太厉害啦!这不就是把好多好多的晶体管啥的都集成在一起嘛,就像一个超级团队一样!像我们家里的各种电器都有它的功劳呀。

4. “半导体材料”,这可是基础呀!没有它哪来的半导体器件呢?好比盖房子的砖头,没有砖头怎么能有坚固的房子呢?这半导体材料就类似于这样重要的存在啊。

5. “封装”,把芯片保护起来的重要一步呀!就如同给宝贝穿一件坚固的外衣,让它能更好地工作和发挥作用呢。

像我们平常看到的那些芯片,都是经过封装的哟。

6. “光刻”,哇,这可是个精细活呢!它就像是在晶圆上画画,得超级仔细才行。

这个步骤要是没做好,那后面可就都乱啦!

7. “掺杂”,这可是改变半导体性能的关键呀!就好像给它加点特别的调料,让它变得更独特和好用。

很多半导体器件的特性可都是靠掺杂来实现的呢!

8. “蚀刻”,把不需要的部分去掉,这就像是给半导体做一次精准的修剪。

有了它,才能让半导体呈现出我们想要的形状和功能呀!

总之,这些半导体专业词汇可都太重要啦,它们共同构建了半导体这个神奇的领域!。

半导体行业术语

半导体行业术语半导体行业术语是专门用于描述和解释半导体技术和相关概念的专业词汇。

在描述半导体行业的相关术语时,需要确保清晰度和准确性。

以下是一些常见的半导体行业术语及其解释:1.半导体:半导体是一种电子材料,具有介于导体和绝缘体之间的电导特性。

半导体材料通常可以控制电流的流动,是构成电子器件和集成电路的基本元件。

2.集成电路(IC):集成电路是一种由多个电子元件(如晶体管、电容、电阻等)以及连接器件(如导线、金属线等)组成的电路系统。

集成电路可用于执行各种计算、存储和处理任务。

3.晶体管:晶体管是一种半导体器件,可以放大和控制电流。

晶体管由三层材料组成,其中包括一个控制区域、一个输入区域和一个输出区域。

晶体管被广泛用于电子设备和电路中。

4.功耗:功耗是指半导体器件在正常运行时消耗的电能。

功耗通常以瓦特(W)为单位进行衡量,是半导体行业中一个重要的考虑因素。

5.时钟频率:时钟频率是计量半导体器件工作速度的指标,通常以赫兹(Hz)为单位。

时钟频率越高,半导体器件的数据处理和运行速度越快。

6.互连:互连是指将不同的半导体器件或电子组件连接在一起的过程。

互连通常使用导线、金属线、连接器等来完成。

7.工艺技术:工艺技术是指用于制造半导体器件和集成电路的特定技术过程。

包括一系列的步骤,如沉积、蚀刻、掩膜制备等,用于制造和构建电子器件。

8.掩膜:掩膜是一种用于制造半导体器件的模板。

掩膜通常是由光刻工艺制备的,可以在半导体材料上形成特定的图案和结构,用于制造电子器件的特定组件。

9.封装:封装是将半导体芯片和连接线封装在外壳中的过程。

封装有助于保护芯片和电路,并提供适当的物理连接和支持。

10.微纳加工技术:微纳加工技术是一种用于制造微小尺度结构和器件的技术。

在半导体行业中,微纳加工技术被广泛应用于制造芯片和集成电路,以及其他微小尺度的器件。

以上是一些常见的半导体行业术语及其解释。

了解和熟悉这些术语对于了解半导体技术和行业发展趋势非常重要。

半导体常用词汇汇总

1. accepta nce testing (WAT: wafer accepta nce testing)2. accepto r: 受主,如B,掺入Si中需要接受电子3. ACCESS:一个EDA(Enginee ring Data Analysi s)系统4. Acid:酸5. Activedevice:有源器件,如MOS FET(非线性,可以对信号放大)6. Align mark(key):对位标记7. Alloy:合金8. Aluminu m:铝9. Ammonia:氨水10. Ammoniu m fluorid e:NH4F11. Ammoniu m hydroxi de:NH4OH12. Amorpho us silicon:α-Si,非晶硅(不是多晶硅)13. Analog:模拟的14. Angstro m:A(1E-10m)埃15. Anisotr opic:各向异性(如POLY ETCH)16. AQL(Accepta nce Quality Level):接受质量标准,在一定采样下,可以95%置信度通过质量标准(不同于可靠性,可靠性要求一定时间后的失效率)17. ARC(Antiref lectiv e coating):抗反射层(用于METAL等层的光刻)18. Antimon y(Sb)锑19. Argon(Ar)氩20. Arsenic(As)砷21. Arsenic trioxid e(As2O3)三氧化二砷22. Arsine(AsH3)23. Asher:去胶机24. Aspectration:形貌比(ETCH中的深度、宽度比)25. Autodop ing:自搀杂(外延时SUB的浓度高,导致有杂质蒸发到环境中后,又回掺到外延层)26. Back end:后段(CONTACT以后、PCM测试前)27. Baselin e:标准流程28. Benchma rk:基准29. Bipolar:双极30. Boat:扩散用(石英)舟31. CD:(Critica l Dimensi on)临界(关键)尺寸。

半导体常用词汇汇总

半导体常用词汇汇总1. 半导体 (semiconductor): 一种材料,具有介于导体和绝缘体之间的导电特性。

2. 硅 (silicon): 最常用的半导体材料之一,其化学符号为Si。

3. pn结 (pn junction): 由n型半导体和p型半导体结合而成的结构。

4. 栅极 (gate): 用于控制场效应晶体管(FET)的电流流动的电极。

5. 晶体管 (transistor): 一种用于放大和开关电信号的电子器件。

6. 集成电路 (integrated circuit): 由一系列电子器件(如晶体管、电容器等)组成的微小芯片。

7. 缺陷 (defect): 半导体中存在的材料缺陷,可以影响其性能。

8. 掺杂 (doping): 向半导体中引入杂质,以改变其电导率。

9. 导带 (conduction band): 半导体中的能带,其中电子可以自由移动。

10. 价带 (valence band): 半导体中的能带,其中电子处于较稳定的状态。

11. 能隙 (band gap): 价带和导带之间的能量差,决定了半导体的导电性质。

12. 内禀载流子 (intrinsic carrier): 在纯净半导体中由热激发产生的自由电子和空穴。

13. 唐氏理论 (Drift-Diffusion theory): 描述半导体中载流子扩散和漂移的物理模型。

14. 热噪声 (thermal noise): 由于温度引起的随机电信号。

15. 热扩散 (thermal diffusion): 载流子由高浓度区向低浓度区扩散的过程。

16. 绝缘体 (insulator): 电阻极高的材料,电流很难通过。

17. 金属 (metal): 电阻很低的材料,电流可以自由通过。

18. 肖克利效应 (Seebeck effect): 温差引起的电压差效应。

19. 过渡边沿 (rising edge): 信号从低电平向高电平变化的边缘。

半导体制造行业专业术语

半导体词汇1. ac cepta nce t estin g (WA T: wa fer a ccept ancetesti ng) 2. ac cepto r: 受主,如B,掺入Si中需要接受电子3.ACCES S:一个E DA(En ginee ringDataAnaly sis)系统4. Acid:酸5. Act ive d evice:有源器件,如MOS FET(非线性,可以对信号放大)6. Ali gn ma rk(ke y):对位标记7. All oy:合金8.Alumi num:铝9.Ammon ia:氨水10. Ammo niumfluor ide:N H4F 11. A mmoni um hy droxi de:NH4OH 12. A morph ous s ilico n:α-S i,非晶硅(不是多晶硅)13. An alog:模拟的14. A ngstr om:A(1E-10m)埃15. A nisot ropic:各向异性(如POL Y ETC H)16. AQ L(Acc eptan ce Qu ality Leve l):接受质量标准,在一定采样下,可以95%置信度通过质量标准(不同于可靠性,可靠性要求一定时间后的失效率)17.ARC(A ntire flect ive c oatin g):抗反射层(用于METAL等层的光刻)18. Ant imony(Sb)锑19. Argo n(Ar)氩20. Ars enic(As)砷21.Arsen ic tr ioxid e(As2O3)三氧化二砷22. A rsine(AsH3)23. Ash er:去胶机24. Asp ect r ation:形貌比(ETCH中的深度、宽度比)25. A utodo ping:自搀杂(外延时SUB的浓度高,导致有杂质蒸发到环境中后,又回掺到外延层)26. Bac k end:后段(C ONTAC T以后、P CM测试前)27. Bas eline:标准流程28. Benc hmark:基准29. B ipola r:双极30.Boat:扩散用(石英)舟31. C D:(C ritic al Di mensi on)临界(关键)尺寸。

半导体专业词汇

1.acceptance testing (WAT: wafer acceptance testing)2.acceptor: 受主,如:8,掺入Si中需要接受电子3.ACCESS :一个EDA ( Engineering Data Analysis )系统4.Acid :酸5.Active device :有源器件,如MOS FET (非线性,能够对信号放大)6.Align mark(key):对位标志7.Alloy :合金8.Aluminum :铝9.Ammonia :氨水10.Ammonium fluoride : NH4F11.Ammonium hydroxide : NH4OH12.Amorphous silicon : a-Si,非晶硅(不是多晶硅)13.Analog :模拟的14.Angstrom : A ( 1E-10m )埃15.Anisotropic :各向异性(如POLY ETCH )16.AQL(Acceptance Quality Level):接受质量标准,在必定采样下,能够95%置信度经过质量标准(不一样于靠谱性,靠谱性要求一准时间后的无效率)17.ARC(Antireflective coating):抗反射层(用于METAL 等层的光刻)18.Antimony(Sb) 锑19.Argon(Ar) 氩20.Arsenic(As)砷21.Arsenic trioxide(As2O3) 三氧化二砷22.Arsine(AsH3)23.Asher :去胶机24.Aspect ration :容貌比(ETCH中的深度、宽度比)25.Autodoping :自夹杂(外延时SUB的浓度高,致使有杂质蒸发到环境中后,又回掺到外延层)26.Back end :后段(CONTACT 此后、PCM 测试前)27.Baseline :标准流程28.Benchmark :基准29.Bipolar :双极30.Boat :扩散用(石英)舟31.CD : (Critical Dimension )临界(重点)尺寸。

半导体专业英语词汇

半导体专业词汇1.a cceptance testing (WAT: wafer acceptance testing)2.a cceptor: 受主,如 B ,掺入 Si 中需要接受电子3.A CCESS :一个 EDA (Engineering Data Analysis )系统4.A cid :酸5.A ctive device :有源器件,如 MOS FET (非线性,可以对信号放大)6.A lign mark(key) :对位标记7.A lloy :合金8.A luminum :铝9.A mmonia :氨水10.A mmonium fluoride : NH4F11.A mmonium hydroxide : NH4OH12.A morphous silicon :α -Si ,非晶硅(不是多晶硅)13.A nalog :模拟的14.A ngstrom : A (1E-10m)埃15. Anisotropic :各向异性(如 POLY ETCH )16 . AQL(Acceptance Quality Level) :接受质量标准,在一定采样下,可以95%置信度通过质量标准(不同于可靠性,可靠性要求一定时间后的失效率)17 . ARC(Antireflective coating) :抗反射层(用于 METAL 等层的光刻)18.A ntimony(Sb) 锑19.A rgon(Ar) 氩20.A rsenic(As) 砷21.A rsenic trioxide(As2O3) 三氧化二砷22.A rsine(AsH3)23.A sher:去胶机24.A spect ration :形貌比( ETCH 中的深度、宽度比)25.A utodoping :自搀杂(外延时 SUB 的浓度高,导致有杂质蒸发到环境中后,又回掺到外延层)26.B ack end:后段( CONTACT 以后、 PCM 测试前)27.B aseline:标准流程28.B enchmark :基准29.B ipolar :双极30.B oat:扩散用(石英)舟31. CD :( Critical Dimension )临界(关键)尺寸。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1. acceptance testing (WAT: wafer acceptance testing)2. acceptor: 受主,如B,掺入Si中需要接受电子3. ACCESS:一个EDA(Engineering Data Analysis)系统4. Acid:酸5. Active device:有源器件,如MOS FET(非线性,可以对信号放大)6. Align mark(key):对位标记7. Alloy:合金8. Aluminum:铝9. Ammonia:氨水10. Ammonium fluoride:NH4F11. Ammonium hydroxide:NH4OH12. Amorphous silicon:α-Si,非晶硅(不是多晶硅)13. Analog:模拟的14. Angstrom:A(1E-10m)埃15. Anisotropic:各向异性(如POLY ETCH)16. AQL(Acceptance Quality Level):接受质量标准,在一定采样下,可以95%置信度通过质量标准(不同于可靠性,可靠性要求一定时间后的失效率)17. ARC(Antireflective coating):抗反射层(用于METAL等层的光刻)18. Antimony(Sb)锑19. Argon(Ar)氩20. Arsenic(As)砷21. Arsenic trioxide(As2O3)三氧化二砷22. Arsine(AsH3)23. Asher:去胶机24. Aspect ration:形貌比(ETCH中的深度、宽度比)25. Autodoping:自搀杂(外延时SUB的浓度高,导致有杂质蒸发到环境中后,又回掺到外延层)26. Back end:后段(CONTACT以后、PCM测试前)27. Baseline:标准流程28. Benchmark:基准29. Bipolar:双极30. Boat:扩散用(石英)舟31. CD:(Critical Dimension)临界(关键)尺寸。

在工艺上通常指条宽,例如POLY CD 为多晶条宽。

32. Character window:特征窗口。

用文字或数字描述的包含工艺所有特性的一个方形区域。

33. Chemical-mechanical polish(CMP):化学机械抛光法。

一种去掉圆片表面某种物质的方法。

34. Chemical vapor deposition(CVD):化学汽相淀积。

一种通过化学反应生成一层薄膜的工艺。

35. Chip:碎片或芯片。

36. CIM:computer-integrated manufacturing的缩写。

用计算机控制和监控制造工艺的一种综合方式。

37. Circuit design :电路设计。

一种将各种元器件连接起来实现一定功能的技术。

38. Cleanroom:一种在温度,湿度和洁净度方面都需要满足某些特殊要求的特定区域。

39. Compensation doping:补偿掺杂。

向P型半导体掺入施主杂质或向N型掺入受主杂质。

40. CMOS:complementary metal oxide semiconductor的缩写。

一种将PMOS和NMOS在同一个硅衬底上混合制造的工艺。

41. Computer-aided design(CAD):计算机辅助设计。

42. Conductivity type:传导类型,由多数载流子决定。

在N型材料中多数载流子是电子,在P型材料中多数载流子是空穴。

43. Contact:孔。

在工艺中通常指孔1,即连接铝和硅的孔。

44. Control chart:控制图。

一种用统计数据描述的可以代表工艺某种性质的曲线图表。

45. Correlation:相关性。

46. Cp:工艺能力,详见process capability。

47. Cpk:工艺能力指数,详见process capability index。

48. Cycle time:圆片做完某段工艺或设定工艺段所需要的时间。

通常用来衡量流通速度的快慢。

49. Damage:损伤。

对于单晶体来说,有时晶格缺陷在表面处理后形成无法修复的变形也可以叫做损伤。

50. Defect density:缺陷密度。

单位面积内的缺陷数。

51. Depletion implant:耗尽注入。

一种在沟道中注入离子形成耗尽晶体管的注入工艺。

(耗尽晶体管指在栅压为零的情况下有电流流过的晶体管。

)52. Depletion layer:耗尽层。

可动载流子密度远低于施主和受主的固定电荷密度的区域。

53. Depletion width:耗尽宽度。

53中提到的耗尽层这个区域的宽度。

54. Deposition:淀积。

一种在圆片上淀积一定厚度的且不和下面层次发生化学反应的薄膜的一种方法。

55. Depth of focus(DOF):焦深。

56. design of experiments (DOE):为了达到费用最小化、降低试验错误、以及保证数据结果的统计合理性等目的,所设计的初始工程批试验计划。

57. develop:显影(通过化学处理除去曝光区域的光刻胶,形成所需图形的过程)58. developer:Ⅰ)显影设备;Ⅱ)显影液59. diborane (B2H6):乙硼烷,一种无色、易挥发、有毒的可燃气体,常用来作为半导体生产中的硼源60. dichloromethane (CH2CL2):二氯甲,一种无色,不可燃,不可爆的液体。

61. dichlorosilane (DSC):二氯甲硅烷,一种可燃,有腐蚀性,无色,在潮湿环境下易水解的物质,常用于硅外延或多晶硅的成长,以及用在沉积二氧化硅、氮化硅时的化学气氛中。

62. die:硅片中一个很小的单位,包括了设计完整的单个芯片以及芯片邻近水平和垂直方向上的部分划片槽区域。

63. dielectric:Ⅰ)介质,一种绝缘材料;Ⅱ)用于陶瓷或塑料封装的表面材料,可以提供电绝缘功能。

64. diffused layer:扩散层,即杂质离子通过固态扩散进入单晶硅中,在临近硅表面的区域形成与衬底材料反型的杂质离子层。

65. disilane (Si2H6):乙硅烷,一种无色、无腐蚀性、极易燃的气体,燃烧时能产生高火焰,暴露在空气中会自燃。

在生产光电单元时,乙硅烷常用于沉积多晶硅薄膜。

66. drive-in:推阱,指运用高温过程使杂质在硅片中分布扩散。

67. dry etch:干刻,指采用反应气体或电离气体除去硅片某一层次中未受保护区域的混合了物理腐蚀及化学腐蚀的工艺过程。

68. effective layer thickness:有效层厚,指在外延片制造中,载流子密度在规定范围内的硅锭前端的深度。

69. EM:electromigration,电子迁移,指由通过铝条的电流导致电子沿铝条连线进行的自扩散过程。

70. epitaxial layer:外延层。

半导体技术中,在决定晶向的基质衬底上生长一层单晶半导体材料,这一单晶半导体层即为外延层。

71. equipment downtime:设备状态异常以及不能完成预定功能的时间。

72. etch:腐蚀,运用物理或化学方法有选择的去除不需的区域。

73. exposure:曝光,使感光材料感光或受其他辐射材料照射的过程。

74. fab:常指半导体生产的制造工厂。

75. feature size:特征尺寸,指单个图形的最小物理尺寸。

76. field-effect transistor(FET):场效应管。

包含源、漏、栅、衬四端,由源经栅到漏的多子流驱动而工作,多子流由栅下的横向电场控制。

77. film:薄膜,圆片上的一层或多层迭加的物质。

78. flat:平边79. flatband capacitanse:平带电容80. flatband voltage:平带电压81. flow coefficicent:流动系数82. flow velocity:流速计83. flow volume:流量计84. flux:单位时间内流过给定面积的颗粒数85. forbidden energy gap:禁带86. four-point probe:四点探针台87. functional area:功能区88. gate oxide:栅氧89. glass transition temperature:玻璃态转换温度90. gowning:净化服91. gray area:灰区92. grazing incidence interferometer:切线入射干涉仪93. hard bake:后烘94. heteroepitaxy:单晶长在不同材料的衬底上的外延方法95. high-current implanter:束电流大于3ma的注入方式,用于批量生产96. hign-efficiency particulate air(HEPA) filter:高效率空气颗粒过滤器,去掉99.97%的大于0.3um的颗粒97. host:主机98. hot carriers:热载流子99. hydrophilic:亲水性100. hydrophobic:疏水性101. impurity:杂质102. inductive coupled plasma(ICP):感应等离子体103. inert gas:惰性气体104. initial oxide:一氧105. insulator:绝缘106. isolated line:隔离线107. implant : 注入108. impurity n : 掺杂109. junction : 结110. junction spiking n :铝穿刺111. kerf :划片槽112. landing pad n :PAD113. lithography n 制版114. maintainability, equipment : 设备产能115. maintenance n :保养116. majority carrier n :多数载流子117. masks, device series of n : 一成套光刻版118. material n :原料119. matrix n 1 :矩阵120. mean n : 平均值121. measured leak rate n :测得漏率122. median n :中间值123. memory n : 记忆体124. metal n :金属125. nanometer (nm) n :纳米126. nanosecond (ns) n :纳秒127. nitride etch n :氮化物刻蚀128. nitrogen (N2 ) n:氮气,一种双原子气体129. n-type adj :n型130. ohms per square n:欧姆每平方: 方块电阻131. orientation n:晶向,一组晶列所指的方向132. overlap n :交迭区133. oxidation n :氧化,高温下氧气或水蒸气与硅进行的化学反应134. phosphorus (P) n :磷,一种有毒的非金属元素135. photomask n :光刻版,用于光刻的版136. photomask, negative n:反刻137. images:去掉图形区域的版138. photomask, positive n:正刻139. pilot n :先行批,用以验证该工艺是否符合规格的片子140. plasma n :等离子体,用于去胶、刻蚀或淀积的电离气体141. plasma-enhanced chemical vapor deposition (PECVD) n:等离子体化学气相淀积,低温条件下的等离子淀积工艺142. plasma-enhanced TEOS oxide deposition n:TEOS淀积,淀积TEOS的一种工艺143. pn junction n:pn结144. pocked bead n:麻点,在20X下观察到的吸附在低压表面的水珠145. polarization n:偏振,描述电磁波下电场矢量方向的术语146. polycide n:多晶硅/金属硅化物,解决高阻的复合栅结构147. polycrystalline silicon (poly) n:多晶硅,高浓度掺杂(>5E19)的硅,能导电。