XST Synthesis

如何防止ISE综合时信号被优化掉

如何防止ISE综合时信号被优化掉如何防止ISE综合时你想抓取的信号不被优化掉:1.右键synthesis,在综合选项里将keep hierarchy选择YES ,或者选择soft(在综合时保持层次,在实现时有利用ISE软件自动进行优化),这样有利于你从模块中找到你想抓取的信号和信号名不被更改。

2.在Constraints Guide中,有防止信号被优化掉的说明。

具体在X:\Xilinx\13.4\ISE_DS\ISE\doc\usenglish\isehelp文件夹下。

里面介绍了如何解决信号被优化的问题。

其实ISE的工程设置有“keep_hierarchy”。

在程序里面,也可以通过添加一些语句。

如果是Verilog :Place the Verilog constraint immediately before the module or instantiation .Specify the Verilog constraint as follows:(* KEEP = “{TRUE|FALSE|SOFT}” *)假如我们要观察的一个信号cnt:reg [10:0] cnt;,那么就按照文档中的介绍,要保持此信号不被综合,则:(* KEEP = “TRUE”*) reg [10:0] cnt,或者(* keep= “true”*) reg [10:0] cnt这样就可以实现ChipScope的观察而不被优化掉了。

类似的VHDL:Declare the VHDL constraint as follows:attribute keep : string;Specify the VHDL constraint as follows:attribute keep of signal_name: signal is “{TRUE|FALSE|SOFT}”;当然,这些都是针对ISE的综合器XST的,如soft只有在XST里才可以使用,其它的综合工具,可以参看相关的文档,这些问题都有专业而又明确的说明。

基于FPGA的4位全加器实验

试验一 4位全加器实验1.实验原理.实验原理全加器能进行加数、被加数和低位来的进位信号相加,并根据求和结果给出该位的进位信号。

该位的进位信号。

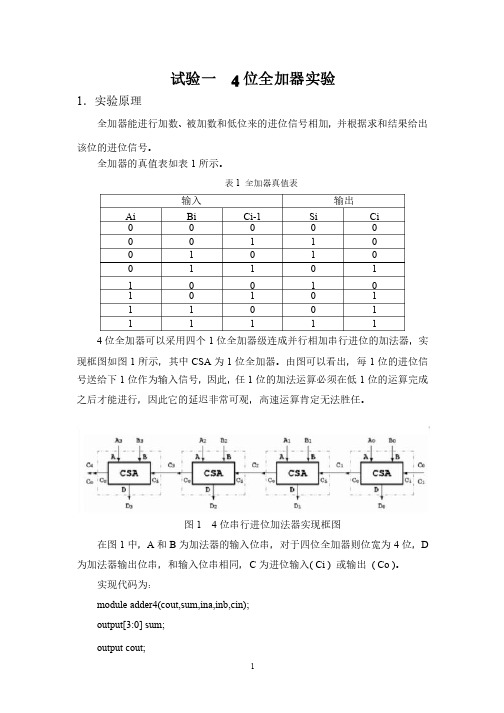

全加器的真值表如表1所示。

所示。

表1 全加器真值表全加器真值表输入输入输出输出AiBi Ci-1 Si Ci0 0 0 0 0 0 0 1 1 0 0 1 0 1 0 0 1 1 0 1 1 0 0 1 0 1 0 1 0 1 1 1 0 0 1 111114位全加器可以采用四个1位全加器级连成并行相加串行进位的加法器,位全加器级连成并行相加串行进位的加法器,实实现框图如图1所示,其中CSA 为1位全加器。

由图可以看出,每1位的进位信号送给下1位作为输入信号,因此,任1位的加法运算必须在低1位的运算完成之后才能进行,因此它的延迟非常可观,高速运算肯定无法胜任。

之后才能进行,因此它的延迟非常可观,高速运算肯定无法胜任。

图1 4位串行进位加法器实现框图位串行进位加法器实现框图在图1中,A 和B 为加法器的输入位串,对于四位全加器则位宽为4位,D 为加法器输出位串,和输入位串相同,C 为进位输入( Ci ) 或输出或输出( Co )。

实现代码为:实现代码为:module adder4(cout,sum,ina,inb,cin); output[3:0] sum; output cout;input[3:0] ina,inb; input cin;assign {cout,sum}=ina+inb+cin; endmodule2.实验目的.实验目的⒈熟悉⒈熟悉 ISE9.1 开发环境,掌握工程的生成方法;开发环境,掌握工程的生成方法; ⒉了解⒉了解 V erilog HDL 语言在语言在 FPGA 中的使用;中的使用; ⒊了解4位全加器的V erilog HDL 语言实现。

语言实现。

3.实验内容.实验内容⒈用V erilog HDL 语言设计4位全加器,进行功能仿真验证。

Xilinx的综合技术_高级篇

reg

O

d1 d2 clk

O

reg

P2

d2

reg

P1

Maximum Frequency: 855.139MHz

LUT3

d1 clk

reg

reg

O

d2

reg

d3

XST Synthesis Strategies - 10

Incremental Synthesis

B1.NGC

B2.NGC

B3.NGC

B1.NGC

B2.NGC B3.NGC

NEW

During re-synthesis, XST has visibility of the entire design, and the modified block is re-optimized taking into account its specific context

clk d1 d2 d3 clk d1 d2 O clk d1 d2 O O

XCF: MODEL p1 incremental_synthesis = "yes"; MODEL p2 incremental_synthesis = "yes";

Maximum Frequency: 516.849MHz

• The main difference between this mode and incremental synthesis is that here XST will not have visibility of other portions of the design when a module is synthesized

XST Synthesis Strategies - 13

ISE使用指导

-3-

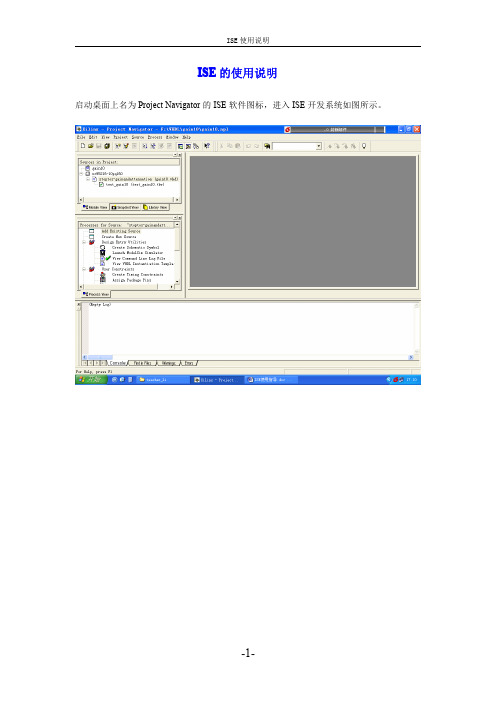

ISE 使用说明

下一步,进行可编程器件型号的选择以及设计流程的设置。在器件型号栏有 Device family , Device (型号) ,封装,speed grade,可以根据实验平台所用的可编程逻辑器件分别设置相 应选项。对话框下半部分是对设计语言和综合仿真工具的选择。

然后下一步,采用默认设置,完成了 New Project Information 的设置。如图所示:

-9-

ISE 使用说明

count<="000000"; end if; elsif flag='1' and flag1='1' then if count<59 then count<=count+1; elsif count>=59 then count<="000000"; end if; end if; end if; end process; end Behavioral; -- flag='1' , 则进行 60 进制计数

然后单击工程 counter 下的子目录 count-Behavioral(count.vhd) , 接着在界面的 Processes for Source 一栏选择 Implement Design,进行布局布线的综合:

-15-

ISE 使用说明

然后工程名 counter 上单击右键,弹出对话框,选择新建 Test Bench Waveform,在 file 命名 为 test_counter。

在界面的 Processes for Source 一栏,是一系列综合工具。 Synthesize XST 工具一般可以分析 代码的语法错误,查看错误报告和 RTL 级的电路设计图。 单击 View Synthesis,出现如图所示对话框:

ISE设计工具简介和快速入门

第四章 ISE 6.x 设计工具简介和使用§4.1概述本章将详细介绍Xilinx 公司新的高性能设计开发工具ISE(Integrated Software Environment),并以第六版本进行讲解和演示。

Xilinx 根据不同的用户,分别提供四种不同功能的设计开发工具:ISE WebPACK,ISE Foundation,ISE BaseX和ISE Alliance。

(1) ISE WebPACK版:该软件为全免费版,可通过Xilinx网站直接下载。

支持包括XC95*/XC95*XL/XC95*XV、CoolRunner XPLA3、CoolRunner-II全系列 CPLD;以及Spartan-II/Spartan-IIE全系列FPGA;Spartan-3系列器件中的XC3S50、XC3S200、XC3S400;Virtex-E部分FPGA(V50E-V300E)器件;Virtex-II部分FPGA(2V40-2V250)器件;Virtex-II Pro部分FPGA(2VP2)器件。

集成了XST(Xilinx Synthesis Technology)综合工具。

但不支持Core Generator(核生成)工具和PACE(引脚和区域约束编辑器)。

(2) ISE Foundation版:该软件为完全版。

提供了设计开发工具的所有功能.支持Xilinx的全系列逻辑器件产品。

并集成了XST(Xilinx Synthesis Technology)综合工具。

支持Core Generator(核生成)工具和PACE(引脚和区域约束编辑器)。

(3) ISE BaseX版:该软件为部分受限版。

即支持XC95*/XC95*XL/XC95*XV全系列CPLD; CoolRunner XPLA3全系列CPLD;CoolRunner-II全系列 CPLD;以及Spartan-II/Spartan-IIE全系列FPGA;Spartan-3系列器件中的XC3S50、XC3S200、XC3S400;Virtex/Virtex-E部分FPGA(V50/V50E—V600/V600E)器件;Virtex-II部分FPGA(2V40--2V250)器件;Virtex-II Pro部分FPGA(2VP2、2VP4、2VP7)器件。

片内逻辑分析仪工具——ChipScopePro

第11章片内逻辑分析仪工具——ChipScope Pro11.1 ChipScope Pro工具介绍在FPGA调试阶段,传统的信号分析手段要求在设计时保留一定数量的FPGA管脚作为测试管脚,这种方法灵活性差,对PCB布线也有一定的影响。

当今先进的FPGA器件所具有的规模、速度和板级要求使得利用传统逻辑分析方法来调试采用FPGA器件进行的设计几乎是不可能的。

Xilinx公司推出的片内逻辑分析仪ChipScope Pro能够通过JTAG口,实时地读出FPGA的所有内部信号,而只需要片内的少量BlockRAM和逻辑资源,使得逻辑分析灵活方便。

ChipScope Pro是与ISE配套使用的,其版本经过了ChipScope 4.1i,ChipScope 4.2i,ChipScope Pro 5.1i,ChipScope Pro 5.2i和ChipScope Pro 6.1i的升级过程,ChipScope Pro 6.1i是与ISE 6.1配套使用的最新版本。

ChipScope Pro软件由3个工具组成:(1) ChipScope Pro内核生成器:为综合控制器(ICON)内核、CoreConnect™ OPB的总线分析内核(IBA/OPB)、逻辑分析(ILA)内核及安捷伦跟踪内核(ILA/ATC)提供网表和实例化的模板;(2) ChipScope Pro内核插入器:自动地为用户已经综合完的设计中插入ICON、ILA和ILA/ATC的内核;(3) ChipScope Pro分析仪:提供器件的配置、触发的设定和ILA、IBA/OPB及ILA/ATC核的踪迹显示功能。

各种内核实现了信号的触发和捕获,而ICON内核专门用于与边界扫描(Boundary Scan)管脚的通信。

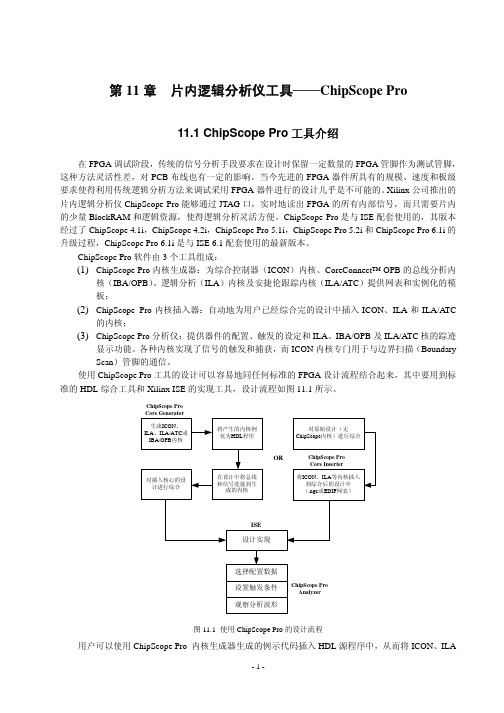

使用ChipScope Pro工具的设计可以容易地同任何标准的FPGA设计流程结合起来,其中要用到标准的HDL综合工具和Xilinx ISE的实现工具,设计流程如图11.1所示。

Verilog实现补码一位乘法课程设计

计算机科学与工程学院课程设计报告题目全称:Verilog实现补码一位乘法课程名称:计算机组成原理指导老师:文泉职称:指导老师评语:指导签字:课程设计成绩:目录第 1 章序言 (1)1.1 课程设计目的 (1)1.2 课程设计作用 (2)1.3 课程设计需求 (2)1.3.1Xilinx设计软件 (2)1.3.2 在xilinx ISE集成开发环境下,使用Verilog HDL (2)第 2 章正文 (4)2.1 实现补码一位乘法的原理 (4)2.2 比较补码一位乘法方法 (6)2.2.1 分步乘法 (6)2.2.2 运算规则 (7)2.2.3 运算实例 (7)2.2.4算法流程图 (8)2.2.5 比较法(Booth算法) (8)2.3课程设计实验代码(概要设计) (10)2.4课程设计详细设计方案 (12)2.4.1顶层方案图的设计与实现 (13)2.4.2 功能模块的设计与实现 (14)2.4.3 仿真调试 (13)第 3 章结论 (16)3.1课程设计总结 (16)摘要本定点补码一位乘法器,具有良好的可移植性。

本文介绍了定点补码一位乘法的概念已及定点补码一位乘法的的原理和方法,分析了定点补码一位乘法器的设计,并详细介绍了使用EDA环境,Xilinx设计软件,在XCV200实验板的XCV200可编程逻辑芯片中上进行定点补码一位乘法器的移植。

通过测试,系统移植成功。

关键词:定点补码;EDA;一位乘法器;设计第1 章序言当今时代是一个信息的时代,我们的生活与信息紧密相连。

伴随着计算机的生活化,我们更近一步接触到信息技术的发展。

如今,计算机技术迅猛发展,它的发展不仅仅表现在软件领域取得辉煌的成就,同时也在硬件方面也取得了长足的发展。

因此,很多功能已经可以通过硬件来实现。

但是通常对嵌入式软件的基本要求是体积小、指令速度快、具有较好的裁减性和可移植性,目前这方面的设计已经很多也很优异,但是基于补码一位乘法器的实现,克服了定点补码乘法器的缺点,实现更加方便有效。

Xilinx ISE 使用入门手册

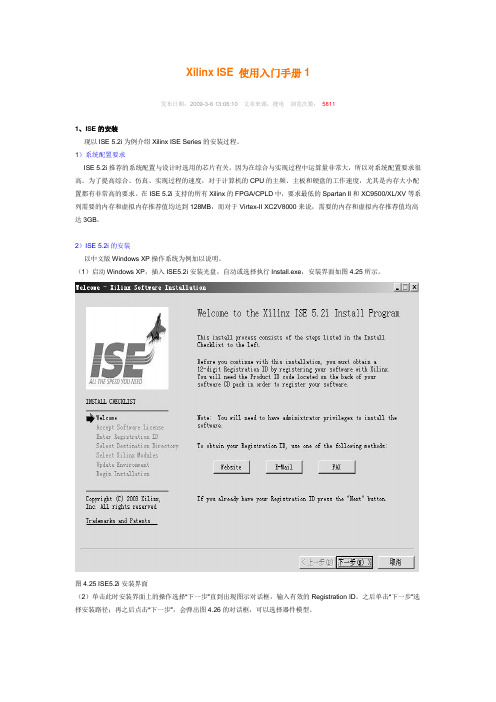

Xilinx ISE 使用入门手册1发布日期:2009-3-6 13:06:10文章来源:搜电浏览次数:58111、ISE的安装现以ISE 5.2i为例介绍Xilinx ISE Series的安装过程。

1)系统配置要求ISE 5.2i推荐的系统配置与设计时选用的芯片有关。

因为在综合与实现过程中运算量非常大,所以对系统配置要求很高。

为了提高综合、仿真、实现过程的速度,对于计算机的CPU的主频、主板和硬盘的工作速度,尤其是内存大小配置都有非常高的要求。

在ISE 5.2i支持的所有Xilinx的FPGA/CPLD中,要求最低的Spartan II和XC9500/XL/XV等系列需要的内存和虚拟内存推荐值均达到128MB,而对于Virtex-II XC2V8000来说,需要的内存和虚拟内存推荐值均高达3GB。

2)ISE 5.2i的安装以中文版Windows XP操作系统为例加以说明。

(1)启动Windows XP,插入ISE5.2i安装光盘,自动或选择执行Install.exe,安装界面如图4.25所示。

图4.25 ISE5.2i安装界面(2)单击此时安装界面上的操作选择“下一步”直到出现图示对话框,输入有效的Registration ID。

之后单击“下一步”选择安装路径;再之后点击“下一步”,会弹出图4.26的对话框,可以选择器件模型。

图4.26 器件模型选择对话框(3)点击“下一步”,如图4.27所示,可以选择器件种类。

图4.27 器件种类选择对话框通过以上步骤后,可根据具体情况来选择,继续“下一步”即可完成安装。

安装完成后,环境变量应作如下描述:若操作系统是Windows NT/2000/XP,选择开始->控制面板->系统->选项->系统->高级->环境变量,在环境变量中加入:变量名:Xilinx变量值:C:Xilinx(即安装路径)具体设置如图4.28所示。

图4.28 环境变量设置操作图3)安装第三方软件在PC上安装完ISE之后,还需要安装第三方仿真软件,如ModelSim等。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

BEGIN MODEL entity_name INST instance_name constraint_name = constraint_value; NET signal_name constraint_name = constraint_value; END;

Presentation Name 16

Language Templates

Two methods to open templates:

– Language Icon – Edit -> Language Templates

Language Templates provide common templates for designs:

-uc -iuc

Presentation Name 23

XCF - MODEL

• To apply a constraint to the entire entity or module, use the following

syntax:

MODEL entity_name constraint_name = constraint_value;

Note: If a constraint is applied to an entity or module, the constraint will be applied to each instance of the entity/module

• To apply constraints to specific instances or signals within an entity or

Presentation Name 18

What are Constraints?

Writing constraints is a method of communicating your design and performance objectives to the synthesis tools and implementation tools

– Translates V, VHD, SCH files into an industry standard format EDIF file

Netlist Implement BIT File

• Step 3: Implement design (netlist)

– Translate, Map, Place & Route

– Optimization Goal (speed/area) – Optimization Effort (normal/high) – Synthesis Constraints File – – – – –

• Any text file Use Synthesis Constraints File Global Optimization Goal Generate RTL Schematic Write Timing Constraints Verilog 2001

To Implementation Tools

Synthesis Report File

Presentation Name 7

Main Synthesis Steps

HDL

HDL Parsing Identification of language syntax errors HDL Synthesis Macro recognition, FSM extraction, resource sharing Low Level Optimization Macro implementation, timing optimization, LUT mapping, register replication

.NGC .LOG

Presentation Name 8

ISE GUI

Synthesis options

– Global synthesis and optimization goal and effort

HDL options

– Family-specific inference and optimization opFPGA

– Download BIT file into FPGA

Presentation Name 3

XST Synthesis in Project Navigator

Module/entity selected in Sources window treated as “top” XST-specific processes

Presentation Name 5

Device Support

XST provides technology specific optimization for:

FPGAs

– – – – – –

CPLDs

– -

Virtex Virtex-E Virtex-II Virtex-II Pro Spartan-II Spartan-IIE

XST Synthesis

FPGA Design Workshop

Objectives

After completing this module, you will be able to…

List the synthesis options for XST Describe how to insert code from the Language Template Specify various methods for entering constraints

Presentation Name 21

XST Constraints

• XST will accept synthesis constraints through the Xilinx Constraints File (XCF)

– Do not confuse this with the User Constraints File (UCF), which contains implementation constraints for the Xilinx tools

• When using an XCF file, specify the file in the Synthesis Options tab

Presentation Name 22

XST Constraints

• To quickly enable or disable the use of a constraint file by XST, you can check or uncheck the Use Synthesis Constraint File menu

Presentation Name 14

XST: HDL Options

• Set family-specific inference and optimization options

– – – – – – – –

FSM Encoding Algorithm RAM/ROM/Multiplexer Extraction RAM/Multiplexer Style Decoder/Priority Encoder Extraction Shift Register/Logical Shifter Extraction XOR Collapsing Resource Sharing Complex Clock Enable Extraction

– Component instantiation – Language templates – Synthesis templates

Presentation Name 17

Language Templates

To use template, be sure that an HDL source file is already opened Place cursor at the location for the code to be entered In the Language Template GUI, rightclick on the template you wish to use Select “Use in…” Be sure the appropriate file name is listed

Xilinx Specific options

– Specific low-level implementation and optimization algorithms

Presentation Name 13

XST: Synthesis Options

• Set global synthesis, optimization goal, and effort

– Synthesize

• View Synthesis Report • Analyze Hierarchy • Check Syntax

AM2910 as top-level

XST-specific properties

– Synthesis Options – HDL Options – Xilinx Specific Options

-

XC9500 XC9500XL XC9500XV CoolRunner CoolRunner-II

Presentation Name 6

XST Flow

VHDL Verilog

Synthesis Technology Specific Optimization