MCS-51单片机外部并行接口扩展技术讲述

3.1MCS-51单片机的并行IO口

一、并行I/O口的功能结构

2、接口功能 (2)通用I/O接口

(四)P0口

此时“控制”信号为“0”,多路开关 MUX向下,输出驱动器处于开漏状态,故需 外接上拉电阻,这种情况下,电路结构与P1 相同,所以也是一个准双向口,当要作为输 入时,必须先向口锁存器写“1”。

一、并行I/O口的功能结构

(四)P0口

这是由接口的特殊结构所决定的。每一个 口都包含一个锁存器,一个输出驱动器和两 个(P3口为3个)输入缓冲器。各口的结构也 P 3 有些差异,下面分别介绍。

一、并行I/O口的功能结构

1、接口结构

(一)P1口

P1口一位的结构如下图所示:

图2.15

一、并行I/O口的功能结构

1、接口结构

(一)P1口

接口结构中锁存器起输出锁存作用, 8位锁存器组成特殊功能寄存器P1,场 效应管和上拉电阻组成输出驱动器,以 增大负载能力,三态门1和三态门2分别 用于控制输入引脚和锁存器的状态。

作为I/O口应用的一个实例,下面介绍 8031单片机的最小应用系统如下图所示

二、产生接口控制信号的指令

(四)P0口

8051指令系统中能与接口打交道的指令 大体可分两类 1.一般的输入/输出指令 2.“读-修改-写”指 令

二、产生接口控制信号的指令

1.一般的输入输出指令

(四)P0口

输入指令执行时,内部产生“读引脚”信号, 直接从口线读入,亦称“读引脚”指令。 下面是属于这种指令的各种实例:

二、产生接口控制信号的指令

(四)P0口 2.“读-修改-写”指令 INC P2 接口锁存器加1 DEC P1 接口锁存器内容减1 DJNZ P3,LOOP 减1后不为零则跳转 还有三条虽不明显,但也属此列: MOV P1.1,C CLR P1.1 SETB P1.1 将进位位送接口的某位 清接口的某一位 接口的某一位置位

单片机系统的扩展技术

INC R0

INC DPTR

; 修改数据指针

DJNZ R7, AG

END

4.2.3 MCS-51对外部存储器的扩展

下 图 所 示 的 8031 扩 展 系 统 中 , 外 扩 了 16KB 程 序 存 储 器 ( 使 用 两 片 2764芯片)和8KB数据存储器(使用一片6264芯片)。采用全地址译码方 式,用于控制2―4译码器的工作,参加译码,且无悬空地址线,无地址重 叠现象。1# 2764, 2# 2764, 3# 6264的地址范围分别为:0000H~1FFFH, 2000H~3FFFH, 4000~5FFFH。

4.2 存储器的扩展

存储器是计算机系统中的记忆装置,用来存放要运行的程序和程序 运行所需要的数据。单片机系统扩展的存储器通常使用半导体存储器, 根据用途可以分为程序存储器(一般用ROM)和数据存储器(一般用 RAM)两种类型。

MCS-51单片机对外部存储器的扩展应考虑的问题:

(1)选择合适类型的存储器芯片

引脚符号的含义和功能如下:

D7~D0:三态数据总线; A0~Ai:地址输入线,i=12~15。2764的地址线为13位,i=12; 27512的地址线为16位,i=15; CE :片选信号输入线; OE :输出允许输入线;

CE

VPP:编程电源输入线; PGM :编程脉冲输入线; VCC:电源; GND:接地; NC:空引脚。

8051扩展2764的电路连接方法:

数据线:P0口接EPROM的D0~D7 ;

地址线: 2764容量为8KB,213=8KB,需要A0~A12共13根地址线。P0口

经地址锁存器后接EPROM的A0~A7 ; 为了与片内存储器的空间地址衔 接,~接EPROM的A8~A11 , 经非门后与A12连接。

第5章 MCS-51单片机外部并行口扩展技术-5.3并行口扩展

377(2)

0

1

74LS377 具有“使能” 具有“使能”控制端的锁存器

扩展8位并行输入 输入口 2. 扩展8位并行输入口

0 0

0

A15 P2.7 0 1

A14 P2.6 0 0

A13 P2.5 0 1

A12 P2.4 0 1

2…P0.7 0….0 1….1

LOOP: MOV

DPTR,#0FEFFH ,

;0FEFFH为扩展 口地址 为扩展I/O口地址 为扩展 ;输入数据,将244中开关状态读入 输入数据, 中开关状态读入 输入数据 ;读入数据输出,送273驱动 读入数据输出, 驱动LED 读入数据输出 驱动 ;循环测试 循环测试

MOVX A,@DPTR , MOVX @DPTR,A , SJMP LOOP

常用 输入 74LS244、74LS245、74LS240等 74LS244、74LS245、74LS240等 输出 74LS373、74LS273、74LS377、74LS573等 74LS373、74LS273、74LS377、74LS573等 LS373

扩展简单输入/ 3. 扩展简单输入/输出电路

MCS-51单片机外部 第5章 MCS-51单片机外部 并行口扩展技术

5.3 并行口扩展

单片机 单片机 单片机

√

三总线

存储器 外设 外设

×

三总线 I/O 接口电路

√

接口电路的功能 协调高速计算机与低速外设的速度匹配问题 协调高速计算机与低速外设的速度匹配问题 高速计算机 外设 如:计算机与打印机的速度 提供输入/输出过程中的状态信号 提供输入 输出过程中的状态信号 输出过程中的 如:计算机必须知道打印机的状态信号 解决计算机信号与外设信号之间的不一致 解决计算机信号与外设信号之间的不一致 如:串行口负逻辑,而单片机正逻辑 串行口负逻辑,

第六章 MCS-51系统扩展技术2(8255、74LS)

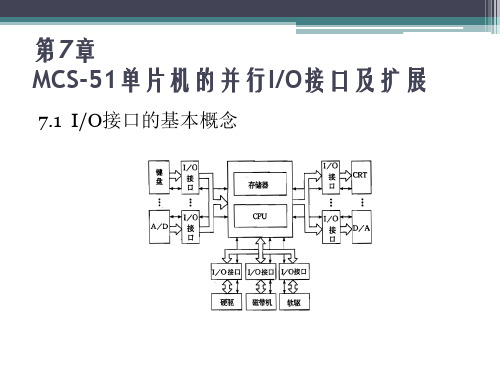

3、MCS-51系统扩展示意图 、 系统扩展示意图

单 片 微 型 机 原 理 与 应 用

为了唯一地选中外部某一存储单元(I/O接口芯片已作为数据存储器的一 接口芯片已作为数据存储器的一 为了唯一地选中外部某一存储单元 部分),必须进行两种选择:一是必须选择出该存储器芯片(或 接口芯片 接口芯片), 部分 ,必须进行两种选择:一是必须选择出该存储器芯片 或I/O接口芯片 , 称为片选;二是必须选择出该芯片中的某一存储单元(或 接口芯片中的寄 称为片选;二是必须选择出该芯片中的某一存储单元 或I/O接口芯片中的寄 存器),称为字选。 存器 ,称为字选。 常用的选址方法有两种:线选法和译码法, 常用的选址方法有两种:线选法和译码法,其中译码法又分为全译码和 部分译码两种。 部分译码两种。

四、部分译码法

单 片 微 型 机 原 理 与 应 用

以上也可采用全译码法, 以上也可采用全译码法,电路更简单

五、扩展存储器时应考虑的几个问题

1. 地址锁存器的选用 2. MCS-51对存储容量的要求 对存储容量的要求 3. 地址线的连接和地址译码方式 4. 工作速度匹配

单 片 微 型 机 原 理 与 应 用

第二节 程序存储器的扩展

一、 常用的程序存储器

单 片 微 型 机 原 理 与 应 用

1. EPROM芯片 芯片 ROM芯片分为 类,即掩膜 芯片分为3类 即掩膜ROM、可编程 芯片分为 、可编程PROM和可擦除 和可擦除 可编程ROM(包括 包括EPROM和E2PROM)。前面两组在实际中使用 可编程 包括 和 。 得很少,因此这里只介绍最常用的可擦除可编程ROM。 得很少,因此这里只介绍最常用的可擦除可编程 。 EPROM芯片:可通过专用的紫外线光源进行照射以擦除其 芯片: 芯片 原有内容,而后用专门的编程器向其写入新的内容。 原有内容,而后用专门的编程器向其写入新的内容。 E2PROM芯片:电可擦除 。 芯片: 芯片

单片机并行I-O口的扩展方法

单片机并行I/O口的扩展方法摘要:由于在MCS-51单片机开发中P0口经常作为地址/数据复用总线使用,P2口作为高8位地址线使用,P3口用作第二功能(定时计数器、中断等)使用,所以对于51单片机的4个I/O口,其可以作为基本并行输入/输出口使用的只有P1口。

因此在单片机的开发中,对于并行I/O口的扩展十分重要,主要分析3种扩展并行I/O口的方法。

关键词: MCS-51单片机; 并行I/O口; 扩展MCS-51单片机有4个并行的I/O口,分别为P0口、P1口、P2口和P3口,4个并行I/O 口在单片机的使用中非常重要,可以说对单片机的使用就是对这4个口的使用。

这4个并行I/O口除了作为基本的并行I/O口使用,还常作为其他功能使用,如P0口经常作为地址/数据复用总线使用[1], P2口作为高8位地址线使用,P3口用作第二功能(定时计数器、中断等等)使用。

这样,单片机只有P1口作为基本的并行I/O口使用,如果在单片机的使用中对并行I/O口需求较多,对于并行I/O口的扩展就非常重要了。

下面通过具体的实例(8位流水灯设计)来给出几种不同的并行I/O口扩展方法。

为了更好地说明以下几种不同的并行I/O口扩展方法,假设利用单片机实现流水灯的设计。

采用单片机的P1口设计流水灯,电路。

由图1可知,8只LED直接连接在单片机的P1口上,通过对单片机进行编程即可以实现8只发光二极管产生流水灯。

1 使用单片机的串行口扩展并行I/O口单片机有一个全双工的串行口[2],这个口既可以用于网络通信,也可以实现串行异步通信,还可以作为移位寄存器使用。

当单片机的串行口工作在模式0时,若外接一个串入/并出的移位寄存器(74LS164),就可以扩展一个8 bit并行输出口;若外接一个并入/串出的移位寄存器(74LS165),就可以扩展一个8 bit并行输入口。

,单片机外接一个串入/并出的移位寄存器(74LS164),这样就可以扩展8 bit并行输出口。

第10章51单片机外部存储器扩展讲解

第10章 51单片机外部存储器扩展

10.1 外部I/O的扩展 10.2 存储器概述 10.3 外部存储器扩展

第410章章 M51单CS片-5机1单外片部机存系储统器功扩能展的扩展

第10章 51单片机外部存储器扩展 10.1 外部I/O的扩展

1

7FFFH

8253 1001 1111 1111 11xx

4

9FFCH~9FFFH

第410章章 M51单CS片-5机1单外片部机存系储统器功扩能展的扩展

二、地址译码法 对于RAM和I/O容量较大的应用系统,当芯片所需的片选信号

多于可利用的地址线时,常采用地址译码法。用译码器对高位地 址进行译码,译出的信号作为片选线。

系统的扩展归结为三总线的连接,连接的方法很简 单,连线时应遵守下列原则:

1.连接的双方数据线连数据线,地址线连地址线, 控制线连控制线。

2.控制线相同的地址线不能相同,地址线相同的控 制线不能相同。

3.片选信号有效的芯片才选中工作,当同类芯片多 片时,片选端可通过线译码、部分译码、全译码接地址线, 在单片机中多采用线选法。

A3

四、常用的SRAM存储器介绍

A9

Intel SRAM 的典型芯片 A11

有2KB 的6116、8KB 的6264

A12

以及32KB的62256。

D0

D7

其中6264 芯片应用最为 广泛。其内部组成如图所示。

…

…

… …

VCC

GND .

行译 .

512X16X8

码.

存储阵列

……

输入

列I/O

数据 电路

第5章 MCS-51单片机的外部并行接口扩展技术_存储器(20130320)

外部扩展的数据存储器都采用静态数据存储器(SRAM)。

SRAM具有存取速度快、使用方便等特点,但系统一旦

掉电,内部所存数据便会丢失。所以,要使内部数据不 丢失,必须不间断地供电。 SRAM不需要刷新电路,使用简单方便。 常用的SRAM型号有6116(2KB×8)、6264(8 KB×8)、 62128(16 KB×8)和62256(32 KB×8)。

5.1.1 系统总线扩展

图5.1

MCS-51系统扩展结构图

5.1.1 系统总线扩展

图5.2

单片机扩展总线结构图

5.1.1 系统总线扩展 存储器的扩展过程中使用的外部总线 ◙地址总线:P0口(A0~A7),P2口(A8~A15); ◙数据总线:P0口(D0~D7); ◙控制总线:控制信号的具体定义如表5-1所示。

5.2.2 数据存储器(RAM)的扩展

图5.9

片外SRAM读/写操作的时序

5.2.2 数据存储器(RAM)的扩展

【例】编程,将外部RAM以1000H为首址的16个单元内容,依次 传送到外部RAM以2000H为首址的区域。 【入口参数】DPTR指向1000H,R0指向00H,P2指向20H, R7为单元计数值。 MOV P2,#20H ;P2R0=2000H MOV R0,#0 0H ;DPTR=1000H MOV DPTR,#1000H MOV R7,#16 LOOP:MOVX A,@DPTR MOVX @R0,A INC DPTR INC R0 DJNZ R7,LOOP RET END

第5章 MCS-51单片机外部并行接口扩展技术

5.1 系统总线扩展及编址技术 5.2 存储器扩展

内容

5.3 并行口扩展 5.4 键盘/显示器扩展接口技术

第7章MCS-51单片机的并行IO接口及扩展

2. P1口一个位的结构

读锁存器 Vcc

*

上拉电阻 P1.x

内部总线 写

D Q CP Q T2

读引脚

P1口的作用特点: 1)内部具备上拉电阻,执行输出功能是,无须连接外部上拉电阻。 2)若要执行输入功能,必须先输出高电平(1)才能读取该口所 连接的外部数据。

• 例7-2-1 试编出模拟图7-2-5中电路的程序。

• 在51系列的C语言中对四个I/O端口进行编程,必 须要利用8051的C语言头文件,其中给出P0~P3 标号的定义。并且可以使用Px^y格式对P0~P3端 口的单个位进行表示,其中x是端口0、1、2或3, y是该端口的位0~7,例如P1^7指示P1.7。

8255A的内部结构如图7-4-2所示,由三部分电路组成: 与CPU的接口电路、内部控制逻辑电路和与外设连接的输 入/输出接口电路。 (1)与CPU的接口电路 (2)内部控制逻辑电路 (3)输入/输出接口电路

图7-4-2 8255A的内部结构

表7-4-1 8255A的端口分配及读/写功能

7.4.2 8255A的工作方式及其初始化编程

地址 控制

Vcc * 上拉电阻 P2.x

D Q CP Q

MUX

T2

4 . P3口 P3口一个位的结构

选择输出功能 读锁存器 Vcc * 上拉电阻 P3.x 内部总线 写 D Q CP Q T2

读引脚

第二输入功能

P3口的第二功能

P3引脚 P3.0 P3.1 P3.2 兼用功能 串行通讯输入(RXD) 串行通讯输出(TXD) 外部中断0(INT0)

7.3 用TTL芯片扩展简单的I/O接口

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

5.2.2数据存储器的扩展

➢ 为什么要扩展?

8031片内只有128个字节,8032只有256个字节。片外扩展一般 小于64K。

➢ 用什么扩展?

RAM,6116(2K),6264 (8K) ,62256(32K) ✓ AN~A0:地址端 ✓ D0~D7:数据端 ✓ VCC、GND:电源端 ✓ /CE:片选信号 ✓ /OE:读信号线 ✓ /WE:写信号线

第5章 MCS-51单片机外部并行接口扩展技术

教学提示:MCS-51单片机并行接口扩展技术是单

片机应用的重要部分。并行接口扩展主要包括系统扩 展、键盘及显示器原理和应用、A/D及D/A转换电路的 设计与实现和开关量输入/输出通道的设计。了解并 行接口扩展技术的工作原理和特点,并在实际中使用 它们,是单片机设计与应用的重要组成部分。

RAM器件

➢怎样扩展?

✓ 首先我们了解读/写外部RAM的时序。 ✓ 怎样扩展?

看图 ✓ 分析

A.74LS373的作用,与扩展ROM一样,锁存低8位地址; B.高位地址线的连接决定地址单元编号,举例; C. 信号线的连接

/RD---/OE;/WR---/WE;P2---AN~A8 P0---D0~D7(A7~A0,经74373锁存)

线选法

译码法

5.2 存储器扩展

➢ 5.2.1 程序存储器的扩展 ➢ 5.2.2 数据存储器的扩展 ➢ 5.2.3 非易失性数据存储器的扩展(有并行

E2PROM和NVRAM等,自己找资料及教材 看不作要求)

5.2.1程序存储器的扩展

➢ 为什么要扩展? 8031片内无ROM,8051、8751、89C51等内ROM容量不够。

/RD)的具体定义见表5-1。

MCS-51系统扩程序存储器

I/O接口

地址总线AB 数据总线DB 控制总线CB

I/O接口

单片机扩展总线结构图

PSEN

RD

单 WR 片 机 P2

ALE

EA

P0

CB

A8~A15

锁存器 D0~D7

A0~A7

扩展时注意的问题: ➢ 地址锁存器的选用:74LS373 ➢ 存储器空间冲突问题:外RAM(/RD、/WR)有效,由

5.1 系统总线扩展技术及编址技术

由于MCS-51单片机内部资源数量和种类的 限制,因此在实际使用时系统常常需要由外部 扩展,其中包括外部程序存储器的扩展、外部 数据存储器的扩展和I/O 端口的扩展以及其他 功能器件的扩展等。本节介绍采用并行总线结 构的单片机扩展方法及编址方法。

5.1.1 系统总线扩展

MCS-51系列单片机系统扩展主要包括存储器扩 展、I/O口的扩展。存储器扩展分为程序存储器的扩 展、数据存储器的扩展。扩展的能力为: ➢ 程序存储器可扩展至64KB; ➢ 数据存储器可扩展至64KB; ➢ I/O口的扩展。

➢ 注意:MCS-51单片机的外部数据存储器和扩展I/O口 是统一编址的,即每一个扩展的I/O口相当于外部 RAM的一个存储单元,所以,对I/O端口的访问与对 外部RAM的读/写操作一样。

取指时序

ROM扩展

注意:

➢ 2716、2732、27128等的扩展方法与2764类似,只是P2口与地 址线连接数量有差异。

➢ ALE与/PSEN信号每MC出现两次,即1MC取指两次。单字节指令 取指1MC,双字节指令取指1MC,3字节指令(DJNZ,CJNE)取 指2个MC。

➢ 执行MOVX时,由于需要用P2口提供外部RAM的高8位地址,因 此当取出MOVX指令时,下一个机器周期/PSEN和ALE无效,此 时,P2提供RAM高8位地址,/RD或/WR有效,P0输入/输出MOVX 中的数据,因此MOVX需要2个MC才被执行。

➢ 用什么扩展? EPROM,2716(2K),2732(4K),2764

(8K),…27512(64K)

✓ AN~A0:地址端 ✓ D0~D7:数据端 ✓ VCC、GND:电源端 ✓ /CE:片选端 ✓ /OE:输出信号允许端 ✓ VPP:编程电压输入端 ✓ /PGM:编程控制输入线

EPROM器件

读RAM时序

写RAM时序

RAM扩展

➢ 读写的执行过程: ✓ 读RAM: /PSEN取指--指令(ROM中)通过P0口入CPU-- P2P0提供RAM地址--/RD有效--RAM中的数据通 过P0口入CPU。

✓ 写RAM: /PSEN取指--指令(ROM中)通过P0口入CPU-- P2P0提供RAM地址--/WR有效--CPU中的数据通 过P0口入外部RAM 。

➢ I/O接口指令:MOVX ➢ 接口信号与时序:与外RAM扩展方法一样 ➢ 输入/输出的数据交换方式(例 A/D转换器):无条

件方式;延时等待方式;查询方式;中断方式

单片机系统扩展使用的外部总线有以下三种: ➢ 地址总线:P0口(A0~A7),P2口(A8~A15); ➢ 数据总线:P0口(D0~D7); ➢ 控制总线:控制信号(ALE、/PSEN、/EA、/WR、

教学要求:

本章介绍了单片机并行接口扩展技术的工作原理、 特点及应用实例。要求掌握系统扩展方法、键盘及显 示器原理、A/D和D/A转换电路的原理及扩展应用;了 解常用典型并行接口器件应用,在实际中使用它们。

第5章 MCS-51单片机外部并行接口扩展技术

➢ 5.1 系统总线扩展及编址技术

➢ 5.2 存储器扩展 ➢ 5.3 并行口扩展 ➢ 5.4 键盘/显示器接口扩展技术 ➢ 5.5 模拟量I/O通道 ➢ 5.6 开关量I/O通道 ➢ 5.7 本章小结

MOVX实现;外ROM(/PSEN)有效,由PC指针自动实 现,由于CPU的内ROM化,使/PSEN作用弱化。 ➢ 编址技术问题:必须会!

5.1.2 编址技术

地址的译码: ➢ 线选法:简单,但浪费地址资源; ➢ 译码法:稍复杂,但地址资源的利用率高。

常用的器件有74LS138。全译码与部 分译码。

EPROM器件

EPROM器件

➢怎样扩展?

✓ 首先我们了解单片机怎样从外存中取指,取指信号操作包 括ALE、/PSEN、P2和P0

✓ 怎样扩展? 看图。

✓ 分析 A.74LS373的作用; G=1,Q0~Q7=D0~D7 G下降沿时,D0~D7被锁存在Q0~Q7上 利用该特点,将ALE与G端相连。 B./PSEN与/OE线的连接。