计算机组成原理习题 第三章存储系统

计算机组成原理—习题解答(第三章)

Copyright ©2012 Computer Organization Group. All rights reserved.

第三章 3.10

题解:

⑴ 64K×32位 / 16K×8位 = 4×4 = 16片; ⑵ 见下页; ⑶ 8ms / 128 = 62.5us,刷新周期为62.5us,128个刷新周期; ⑷ 分散式对存储器刷新一遍用时128×0.5us×2=128us,在8ms

题解: 1ms(1000us)内必须刷新64次,每次刷新时间为1/4us ,则1ms内16us用于刷新,比例为1.6%。 或者, 1ms中包含的存取周期数为:1ms/250ns=4000个

Copyright ©2012 Computer Organization Group. All rights reserved.

第三章 3.10

A6~0行 A13~7列

A6~0 刷新

A14

A15 -RAS

REF

A6~0 地址 -WE 多路 选择 -RAS0 器

-RAS1

片 选 译 -RAS2 码 器 2:4 -RAS3

-CAS

A6~0 -WE

16KX8 DRAM

16KX8 DRAM

第三章 3.6

3.6若用1M×1位的DRAM芯片构成1M×16位的主存储器 ,芯片内部存储元排列成正方形阵列,其刷新最大间隔时 间为4ms。则采用异步刷新时,两次刷新操作应相隔多长 时间?4ms时间内共需多少个刷新周期?

题解: 刷新定时信号的周期时间为: 4ms/1024 = 3.9us; ; 4ms时间内共需1024个刷新周期。

题解:

(1) 寻址范围=64K / (32/8) = 16K字;存储容量为16K×32bit。 (2) 字地址与字节地址的分配:(大端方式)

计算机组成原理习题 第三章存储系统

计算机组成原理习题第三章存储系统第三章习题一、填空题:1. 广泛使用的A.______和B.______都是半导体随机读写存储器。

前者速度比后者C.______,集成度不如后者高。

2. CPU能直接访问A.______和B.______,但不能直接访问磁盘和光盘。

3. 广泛使用的 ______和 ______都是半导体随机读写存储器,前者比后者速度快, ___ ___不如后者高。

它们断电后都不能保存信息。

4. 由于存储器芯片的容量有限,所以往往需要在A.______和B.______两方面进行扩充才能满足实际需求。

5. Cache是一种A______存储器,是为了解决CPU和主存之间B______不匹配而采用的一项重要的硬件技术。

6. 虚拟存贮器通常由主存和A______两级存贮系统组成。

为了在一台特定的机器上执行程序,必须把B______映射到这台机器主存贮器的C______空间上,这个过程称为地址映射。

7. 半导体SRAM靠A______存贮信息,半导体DRAM则是靠B______存贮信息。

8. 主存储器的性能指标主要是存储容量,A.______和B.______。

9. 由于存储器芯片的容量有限,所以往往需要在A.______和B.______两方面进行扩充才能满足实际需求。

10. 存储器和CPU连接时,要完成A.______的连接;B.______的连接和C.______的连接,方能正常工作。

11. 广泛使用的A.______和B.______都是半导体随机读写存储器,它们共同的特点是C.______。

12. 对存储器的要求是A.______,B.______,C.______,为了解决这三个方面的矛盾。

计算机采用多级存储器体系结构。

13. 虚拟存贮器通常由主存和A______两级存贮系统组成。

为了在一台特定的机器上执行程序,必须把B______映射到这台机器主存贮器的C______空间上,这个过程称为地址映射。

计算机组成原理第三章课后习题参考答案

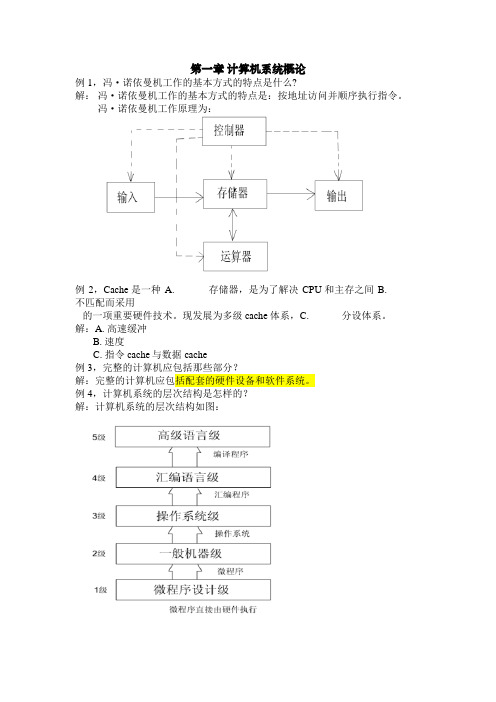

第三章(P101)1.(1)M 4832*220= 字节 (2)片84*28*51232*1024==K K(3)1位地址作芯片选择2. (1)个内存条4264*264*222426==(2)328*264*22242=每个内存条内共有32个DRAM 芯片 (3)4*32 = 128个主存共需要128个DRAM 芯片,CPU 通过由高位地址选择各内存条。

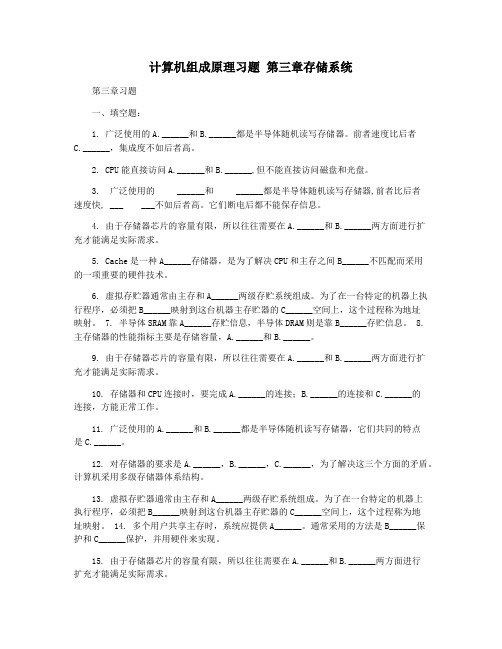

3. (1)首先计算所需芯片数目:168*232*21416=片 芯片容量为16K ,所以芯片内部寻址需14位;四个芯片组成一组形成32个位线,共需4组,需2位地址进行组间寻址; 其中使用一片2:4译码器;所以所以采用位并联与地址串联相结合的方法来组成整个存储器,其组成逻辑图如图所示,(2)根据已知条件,CPU 在1us 内至少访存一次,而整个存储器的平均读/写周期为0.5us ,如果采用集中刷新,有64us 的死时间,肯定不行 如果采用分散刷新,则每1us 只能访存一次,也不行 所以采用异步式刷新方式。

假定16K*8位的DRAM 芯片用128*128矩阵存储元构成,刷新时只对128行进行异步方式刷新,则刷新间隔为2ms/128 = 15.5us ,可取刷新信号周期15us 。

刷新一遍所用时间=15us ×128=1.92ms4. (1)片328*12832*1024 K K ,共分8组,每组4片;地址线共20位,其中组间寻址需3位,组内17位; (2)(3)如果选择一个行地址进行刷新,刷新地址为A 0-A 8,因此这一行上的2048个存储元同时进行刷新,即在8ms 内进行512个周期(即512行)。

采用异步刷新方式,刷新信号周期为:8ms/512 = 15.5us 。

注:存储器由128K*8位的芯片构成,分8组,每组4片,组内芯片并行工作,需17条地址线进行寻址,其中X 行线为9根,Y 位线为8根,29=512行。

5. 用256K*16位的SRAM 芯片设计1024K*32的存储器,需进行字位同时扩展方式继续拧设计,所需芯片数目:片816*25632*1024 K K ,设计的存储器容量为1M ,字长为32,故需20位地址(A0~A19);所用芯片存储容量为256K ,字长为16位,故片内寻址需18位(A0~A17)。

计算机组成原理第三章习题课

3

RAM:1K×4位—>1K×8位

D7-D0

D7-D4 RAM1 1K×4 CS CS

D3-D0 RAM2 1K×4 CS

A9-A0 A9-A0

A9-A0

2、字存储容量扩展

• 增加地址线,使得存储器单元数增加 • 连接方式:三组信号线中

– 地址总线和数据总线公用 – 多余的地址线用来片选

1、20位地址,32位字长

(2)由512K×8位的芯片构成,需要多少片 存储器:1M×32位 512K →1M:说明有容量扩展 8位→32位:说明有字长扩展 8 →32 需要: (1M/512K)×(32位/ 8位) = 2×4 =8

1、20位地址,32位字长

(3)需要多少位地址作为芯片选择 512K×8位→1M×32位 芯片选择只和地址线相关 512K=2 512K 219,即有19根地址线 19 1M =220,即有20根地址线 多余的一根地址线一定是做片选的 ∴需要1根地址线作为片选

3、16K×8位—>64K×32位

RAM1 RAM2 RAM3 RAM4 CS CS CS CS

字长扩展 16K×8位—>16K×32位

16K×32位 16K×32位 16K×32位

容量扩展 16K×32位—>64K×32位

A15 A14 A13-A0

3、16K×8位—>64K×32位

错误: 1、只看到了A13-A0,缺少A15、A14 2、数据总线、地址总线,一定要标明起止符 号,例如A13-A0, D7-D0 3、三组信号线要全部标明

7. 某机器中,已知配有一个地址空间为(0000—1FFF)16 的ROM区域,现在用一个 用一个SRAM芯片(8K×8位)形 芯片( × 位 用一个 芯片 成一个16K×16位的 位的RAM区域 区域,起始地址为(2000) 成一个 × 位的 区域 16 。假设SRAM芯片有CS和WE控制端,CPU地址总 线A15-A0 ,数据总线为D15-D0 ,控制信号为R / W (读 / 写),MREQ(当存储器读或写时,该信号 指示地址总线上的地址是有效的)。 分析:一个RAM区,一个ROM区 RAM ROM 其中RAM需要容量扩展 由8K×8位芯片构成1—>16K×16位(容量扩展) 共需要4片芯片,每两片构成8K×16位单元 字长扩展不改变地址分配,容量扩展才会改变

计算机组成原理.各章例题

第一章计算机系统概论例1,冯·诺依曼机工作的基本方式的特点是什么?解:冯·诺依曼机工作的基本方式的特点是:按地址访问并顺序执行指令。

冯·诺依曼机工作原理为:例2,Cache是一种A. ______存储器,是为了解决CPU和主存之间B. ______不匹配而采用的一项重要硬件技术。

现发展为多级cache体系,C. ______分设体系。

解:A. 高速缓冲B. 速度C. 指令cache与数据cache例3,完整的计算机应包括那些部分?解:完整的计算机应包括配套的硬件设备和软件系统。

例4,计算机系统的层次结构是怎样的?解:计算机系统的层次结构如图:第二章 运算方法和运算器例 1.设机器字长32位,定点表示,尾数31位,数符1位,问:(1)定点原码整数表示时,最大正数是多少?最大负数是多少? (2)定点原码小数表示时,最大正数是多少?最大负数是多少? 解:(1最大正数:数值 = (231 – 1)10最大负数: 数值 = -(231 – 1)10 (2)定点原码小数表示: 最大正数值 = (1 – 231 )10最大负数值 = -(1–231 )10例2.已知 x = - 0.01111 ,y = +0.11001, 求 [ x ]补 ,[ -x ]补 ,[ y ]补 ,[ -y ]补,x + y = ? ,x – y = ?解:[ x ]原 = 1.01111 [ x ]补 = 1.10001 所以 :[ -x ]补 = 0.01111[ y ]原 = 0.11001 [ y ]补 = 0.11001 所以 :[ -y ]补 = 1.00111 [ x ]补 11.10001 [ x ]补 11.10001 + [ y ]补 00.11001 + [ -y ]补 11.00111 [ x + y ]补 00.01010 [ x - y ]补 10.11000所以: x + y = +0.01010 因为符号位相异,结果发生溢出例3.设有两个浮点数 N 1 = 2j1 × S 1 , N 2 = 2j2 × S 2 ,其中阶码2位,阶符1位,尾数四位,数符一位。

(完整版)计算机组成原理第3章习题参考答案

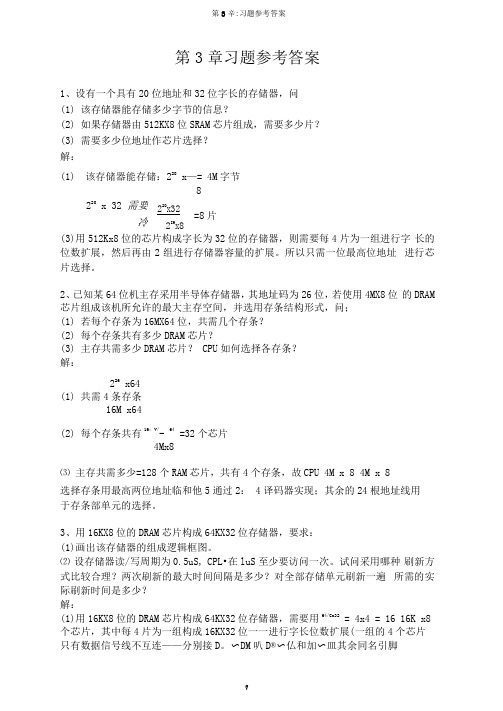

第3章习题参考答案1、设有一个具有20位地址和32位字长的存储器,问(1) 该存储器能存储多少字节的信息?(2) 如果存储器由512K ×8位SRAM 芯片组成,需要多少片?(3) 需要多少位地址作芯片选择?解:(1) 该存储器能存储:字节4M 832220=⨯(2) 需要片8823228512322192020=⨯⨯=⨯⨯K (3) 用512K ⨯8位的芯片构成字长为32位的存储器,则需要每4片为一组进行字长的位数扩展,然后再由2组进行存储器容量的扩展。

所以只需一位最高位地址进行芯片选择。

2、已知某64位机主存采用半导体存储器,其地址码为26位,若使用4M ×8位的DRAM 芯片组成该机所允许的最大主存空间,并选用内存条结构形式,问;(1) 若每个内存条为16M ×64位,共需几个内存条?(2) 每个内存条内共有多少DRAM 芯片?(3) 主存共需多少DRAM 芯片? CPU 如何选择各内存条?解:(1) 共需内存条条4641664226=⨯⨯M (2) 每个内存条内共有个芯片32846416=⨯⨯M M (3) 主存共需多少个RAM 芯片, 共有4个内存条,1288464648464226=⨯⨯=⨯⨯M M M 故CPU 选择内存条用最高两位地址A 24和A 25通过2:4译码器实现;其余的24根地址线用于内存条内部单元的选择。

3、用16K ×8位的DRAM 芯片构成64K ×32位存储器,要求:(1) 画出该存储器的组成逻辑框图。

(2) 设存储器读/写周期为0.5μS ,CPU 在1μS 内至少要访问一次。

试问采用哪种刷新方式比较合理?两次刷新的最大时间间隔是多少?对全部存储单元刷新一遍所需的实际刷新时间是多少?解:(1) 用16K ×8位的DRAM 芯片构成64K ×32位存储器,需要用个芯片,其中每4片为一组构成16K ×32位——进行字长位16448163264=⨯=⨯⨯K K数扩展(一组内的4个芯片只有数据信号线不互连——分别接D0~D 7、D 8~D 15、D 16~D 23和D 24~D 31,其余同名引脚互连),需要低14位地址(A 0~A 13)作为模块内各个芯片的内部单元地址——分成行、列地址两次由A 0~A 6引脚输入;然后再由4组进行存储器容量扩展,用高两位地址A 14、A 15通过2:4译码器实现4组中选择一组。

计算机组成原理自学考试试卷

第三章存储系统一、单选题1. 计算机中表示地址时使用(A)A. 无符号数B. 原码C. 反码D. 补码2. 运算器虽有许多部件组成,但核心部分是(B)A.数据总线 B.算术逻辑单元 C.多路开关 D.通用寄存器3、断电后,下列说法中,正确的是( A )。

A.ROM中的数据仍然存在B.DRAM中的数据仍然存在C.SRAM中的数据仍然存在D.CD-ROM中的数据会丢失4、一个8位的微型机系统以16位来表示地址,则该计算机系统有( D )个地址空间。

A.128 B.256 C.1024 D.655365、磁盘存贮器的记录方式一般采用( C )。

A.归零制B.不归零制C.调频制 D.调相制6、相联存贮器是按( B )进行寻址的存贮器。

A.地址指定方式B.内容指定方式C.堆栈存取方式D.地址指定方式与堆栈存取方式结合7、访问存储器时,读出的信息或将写入的信息要经过(A )。

A.数据寄存器B.指令寄存器C.累加器D.地址寄存器8、指令系统中采用不同寻址方式,其目的是( C )。

A.可以直接访问外存B.实现存储程序和程序控制C.缩短指令长度,扩大寻址空间,提高编程灵活性D.提供扩展操作码的可能,并降低指令译码难度9. 主存储器和CPU之间增设高速缓冲器的目的是(A)A. 解决CPU和主存之间的速度匹配问题B. 扩大主存储的容量C. 扩大CPU中通用寄存器的数量D. 扩大CPU中通用寄存器的数量和主存储器的容量10. 某计算机的字长为16位,它的存储容量为64KB,若按字寻址,其寻址范围是( B )A. 0~32KBB. 0~32K-1C. 0~64KBD. 0~64K-111、存储周期( C )存储时间。

A、大于B、小于C、略大于D、略小于12、CPU与主存之间以(B )信号表示一次访存操作结束。

A、BusyB、ReadyC、WriteD、Read13、静态存储器的功耗和集成度比动态存储器要( A )。

A、大、小B、大、大C、小、小D、小、大14、在三层次存储系统中不包括( C )。

计算机组成原理第3章习题参考答案

第3章习题参考答案1、设有一个具有20位地址和32位字长的存储器,问 (1) 该存储器能存储多少字节的信息?(2) 如果存储器由512KX8位SRAM 芯片组成,需要多少片? (3) 需要多少位地址作芯片选择? 解:(1) 该存储器能存储:220 x —= 4M 字节8(3)用512Kx8位的芯片构成字长为32位的存储器,则需要每4片为一组进行字 长的位数扩展,然后再由2组进行存储器容量的扩展。

所以只需一位最高位地址 进行芯片选择。

2、已知某64位机主存采用半导体存储器,其地址码为26位,若使用4MX8位 的DRAM 芯片组成该机所允许的最大主存空间,并选用存条结构形式,问; (1) 若每个存条为16MX64位,共需几个存条? (2) 每个存条共有多少DRAM 芯片?(3) 主存共需多少DRAM 芯片? CPU 如何选择各存条? 解:226x64(1) 共需4条存条16M x64(2) 每个存条共有16;V/- 64 =32个芯片4Mx8⑶ 主存共需多少=128个RAM 芯片,共有4个存条,故CPU 4M x 8 4M x 8 选择存条用最高两位地址临和他5通过2: 4译码器实现;其余的24根地址线用 于存条部单元的选择。

3、用16KX8位的DRAM 芯片构成64KX32位存储器,要求: (1)画出该存储器的组成逻辑框图。

⑵ 设存储器读/写周期为0.5uS, CPL •在luS 至少要访问一次。

试问采用哪种 刷新方式比较合理?两次刷新的最大时间间隔是多少?对全部存储单元刷新一遍 所需的实际刷新时间是多少? 解:(1)用16KX8位的DRAM 芯片构成64KX32位存储器,需要用64/Cx32 = 4x4 = 16 16K x8 个芯片,其中每4片为一组构成16KX32位一一进行字长位数扩展(一组的4个芯片 只有数据信号线不互连——分别接D 。

〜DM 叭D®〜仏和加〜皿其余同名引脚220 x 32 需要冷22O X 322I9X 8=8片互连),需要低14位地址(A°〜AQ 作为模块各个芯片的部单元地址一一分成行、列 地址两次由A 。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第三章习题一、填空题:1.广泛使用的A.______和B.______都是半导体随机读写存储器。

前者速度比后者C.______,集成度不如后者高。

2.CPU能直接访问A.______和B.______,但不能直接访问磁盘和光盘。

3.广泛使用的 ______和 ______都是半导体随机读写存储器,前者比后者速度快, ___ ___不如后者高。

它们断电后都不能保存信息。

4.由于存储器芯片的容量有限,所以往往需要在A.______和B.______两方面进行扩充才能满足实际需求。

5.Cache是一种A______存储器,是为了解决CPU和主存之间B______不匹配而采用的一项重要的硬件技术。

6.虚拟存贮器通常由主存和A______两级存贮系统组成。

为了在一台特定的机器上执行程序,必须把B______映射到这台机器主存贮器的C______空间上,这个过程称为地址映射。

7.半导体SRAM靠A______存贮信息,半导体DRAM则是靠B______存贮信息。

8.主存储器的性能指标主要是存储容量,A.______和B.______。

9.由于存储器芯片的容量有限,所以往往需要在A.______和B.______两方面进行扩充才能满足实际需求。

10.存储器和CPU连接时,要完成A.______的连接;B.______的连接和C.______的连接,方能正常工作。

11.广泛使用的A.______和B.______都是半导体随机读写存储器,它们共同的特点是C.______。

12.对存储器的要求是A.______,B.______,C.______,为了解决这三个方面的矛盾。

计算机采用多级存储器体系结构。

13.虚拟存贮器通常由主存和A______两级存贮系统组成。

为了在一台特定的机器上执行程序,必须把B______映射到这台机器主存贮器的C______空间上,这个过程称为地址映射。

14.多个用户共享主存时,系统应提供A______。

通常采用的方法是B______保护和C______保护,并用硬件来实现。

15.由于存储器芯片的容量有限,所以往往需要在A.______和B.______两方面进行扩充才能满足实际需求。

16.相联存储器是按A.______访问的存储器,在cache中用来存放B.______,在虚拟存储器中用来存放C.______。

在这两种应用中,都需要D.______查找。

17.DRAM存储器的刷新一般有A.___,B.___,C.___三种方式。

18.并行处理技术已成为计算计技术发展的主流。

它可贯穿于信息加工的各个步骤和阶段。

概括起来,主要有三种形式A. ______并行;B. ______并行;C. ______并行。

19.主存与cache的地址映射有A. ______、B. ______、C. ______三种方式。

其中______方式适度地兼顾了前二者的优点,又尽量避免其缺点,从灵活性、命中率、硬件投资来说较为理想。

20.动态半导体存贮器的刷新一般有A.______、B.______和C.______三种方式。

21.根据地址格式不同,虚拟存贮器分为A______、B______和C______三种。

二、选择题:1.EPROM是指______。

A. 读写存储器B. 只读存储器C. 可编程的只读存储器D. 光擦除可编程的只读存储器2.在主存和CPU之间增加cache存储器的目的是______。

A. 增加内存容量B. 提高内存可靠性C. 解决CPU和主存之间的速度匹配问题D. 增加内存容量,同时加快存取速度3.采用虚拟存储器的主要目的是______。

A. 提高主存储器的存取速度B. 扩大存储器空间,并能进行自动管理C. 提高外存储器的存取速度D. 扩大外存储器的存储空间4.存储器是计算机系统的记忆设备,主要用于______。

A. 存放程序B. 存放软件C. 存放微程序D. 存放程序和数据5.在______的计算机系统中,外设可以和主存储器单元统一编址,因此可以不使用I/O指令。

A. 单总线B. 双总线C. 三总线D. 多总线6.CD-ROM光盘是______型光盘,可用做计算机的______存储器和数字化多媒体设备。

A. 重写,内B. 只读,外C. 一次,外D. 只读,内7.在主存和CPU之间增加cache存储器的目的是______。

A. 增加内存容量B. 提高内存可靠性C. 解决CPU和主存之间的速度匹配问题D. 增加内存容量,同时加快存取速度8.某机字长32位,存储容量1MB。

若按字编址,它的寻址范围是______。

A. 0~1MB. 0~512KBC. 0~256KD. 0~256KB9.计算机的存储器系统是指______。

A. RAM存储器B. ROM存储器C. 主存储器D. cache,主存储器和外存储器10.某存储器芯片的存储容量为8K×1位,则它的地址线和数据线引脚相加的和为______A. 12B. 13C. 14D. 1511.存储周期是指______。

A.存储器的读出时间B.存储器的写入时间C.存储器进行连续读和写操作所允许的最短时间间隔D.存储器进行连续写操作所允许的最短时间间隔12.某存储器芯片的存储容量为8K×8位,则它的地址线和数据线引脚相加的和为______。

A. 21B. 20C. 18D. 1613.某计算机字长为32位,其存储器容量为16MB,若按字编址,它的寻址范围是______。

A. 0~8MBB. 0~4MC. 0~4MBD. 0~8M14.某存储器芯片的存储容量为8K×8位,则它的地址线和数据线引脚相加的和为______。

A. 21B. 20C. 18D. 1615.某计算机字长32位,其存储容量为32KB,若按字编址,那么它的寻址范围是______。

A. 0~32KB. 0~16KC. 0~8KD. 0~32KB16.常用的虚拟存储系统由______两级存储器组成,其中______是大容量的磁表面存储器。

A. 快存-辅存,辅存B. 主存-辅存,辅存C. 快存-主存,辅存D. 通用寄存器-主存,主存17.某一RAM 芯片,其容量为1024╳8位,其数据线和地址线分别为______。

A. 3,10B. 10,3C. 8,10D. 10,818.和内存储器相比,外存储器的特点是______。

A. 容量大,速度快,成本低B. 容量大,速度慢,成本低C. 容量小,速度快,成本高D. 容量小,速度快,成本低19.某一SRAM芯片,其容量为1024×8位,除电源端和接地端外,该芯片引出线的最小数目应为______。

A. 13B. 15C. 18D. 2020.某计算机字长16位,其存储容量为2MB,若按半字编址,它的寻址范围是______。

A. 0—8MB. 0—4MC. 0—2MD. 0—1M21.某RAM芯片,其存储容量为1024×16位,该芯片的地址线和数据线数目为______。

A. 20,16B. 20,4C. 1024,4D. 1024,1622.某计算机字长32位,存储容量是8MB,若按双字编址,那么它的寻址范围是______。

A. 0—256KB. 0—512KC. 0—1MD. 0—2M23.和外存储器相比,内存储器的特点是______。

A.容量大、速度快、成本低 B.容量大、速度慢、成本高C.容量小、速度快、成本高 D.容量小、速度快、成本低24.一个256KB的存储器,其地址线和数据线总和为______。

A.16B.18C.26D.2025.某存储器芯片的存储容量为8K×1位,则它的地址线和数据线引脚相加的和为____。

A.11B.12C.13D.1426.机器字长32位,其存储容量为4MB,若按字编址,它的寻址范围是______。

A.0 - 1M B.0 - 1MB C.0 - 4M D.0 - 4MB27.某一SRAM芯片,其容量为512×8位,除电源端和接地端外,该芯片引出线的最小数目应为______。

A.23B.25C.50D.1928.某SRAM芯片,其存储容量为64ⅹ16位,该芯片的地址线和数据线数目为______。

A. 64,16B. 16,64C. 64,8D. 16,629.计算机的存储器系统是指______。

A.RAM存储器 B.ROM存储器 C.主存储器 D.主存储器和外存储器30.某计算机字长16位,它的存储容量是64K,若按字节编址,那么它的寻址范围是______。

A. 0—64KB. 0—32KC. 0—64KBD. 0—32KB31.存储器是计算机系统的记忆设备,主要用于______。

A. 存放程序B. 存放软件C. 存放微程序D. 存放程序和数据32.CPU读/写控制信号的作用是______。

A. 决定数据总线上的数据流方向B. 控制存储器操作(R/W)的类型C. 控制流入、流出存储器信息的方向D. 以上任一作用33.双端口存储器和多模块交叉存储器属于A.______存储器结构。

前者采用B.______技术,后者采用C.______技术。

34.双端口存储器所以能高速进行读写,是因为采用______。

A.高速芯片 B.两套相互独立的读写电路 C.流水技术 D.新型器件35.相联存储器是按______ 进行寻址的存储器。

A.地址指定方式 B.堆栈存取方式C.内容指定方式 D。

地址指定与堆栈存取方式结合36.在虚拟存储器中,当程序正在执行时,由______完成地址映射。

A. 程序员B. 编译器C. 装入程序D. 操作系统37.下列有关存储器的描述中,不正确的是______。

A.多体交叉存储器主要解决扩充容量问题B.访问存储器的请求是由CPU发出的C.cache与主存统一编址,即主存空间的某一部分属于cacheD.cache的功能全由硬件实现38.模4交叉存储器有4个存储模块,它们有各自的______。

A.地址寄存器B.地址寄存器和指令寄存器C.地址寄存器和数据缓冲寄存器D.地址寄存器、数据缓冲寄存器和指令寄存器39.双端口存储器之所以能高速进行读/写,是因为采用______。

A. 新型器件B. 流水技术C. 两套相互独立的读写电路D. 高速芯片40.交叉存储器实质上是一种___存储器,它能___执行___独立的读写操作。

A. 模快式,并行,多个B.模快式,串行,多个C. 整体式,并行,一个D.整体式,串行,多个41.双端口存储器在___情况下会发生读/写冲突。

A.左端口与右端口的地址码不同 B.左端口与右端口的地址码相同C.左端口与右端口的数据码相同 D.左端口与右端口的数据码不同42.没有外存贮器的计算机监控程序可以存放在______。