Vivado设计流程实验报告

Vivado实验03_简单4位ALU仿真实验分析

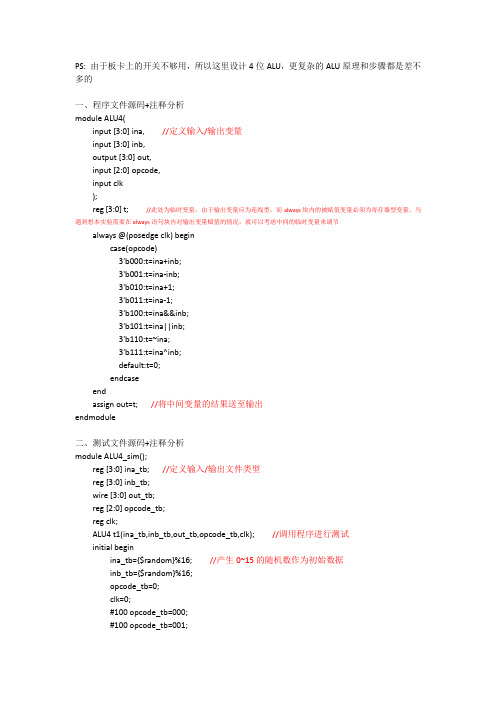

PS: 由于板卡上的开关不够用,所以这里设计4位ALU,更复杂的ALU原理和步骤都是差不多的一、程序文件源码+注释分析module ALU4(input [3:0] ina, //定义输入/输出变量input [3:0] inb,output [3:0] out,input [2:0] opcode,input clk);reg [3:0] t; //此处为临时变量,由于输出变量应为连线型,而always块内的被赋值变量必须为寄存器型变量,当遇到想本实验需要在always语句块内对输出变量赋值的情况,就可以考虑中间的临时变量来调节always @(posedge clk) begincase(opcode)3'b000:t=ina+inb;3'b001:t=ina-inb;3'b010:t=ina+1;3'b011:t=ina-1;3'b100:t=ina&&inb;3'b101:t=ina||inb;3'b110:t=~ina;3'b111:t=ina^inb;default:t=0;endcaseendassign out=t; //将中间变量的结果送至输出endmodule二、测试文件源码+注释分析module ALU4_sim();reg [3:0] ina_tb; //定义输入/输出文件类型reg [3:0] inb_tb;wire [3:0] out_tb;reg [2:0] opcode_tb;reg clk;ALU4 t1(ina_tb,inb_tb,out_tb,opcode_tb,clk); //调用程序进行测试initial beginina_tb={$random}%16; //产生0~15的随机数作为初始数据inb_tb={$random}%16;opcode_tb=0;clk=0;#100 opcode_tb=000;#100 opcode_tb=001;#100 opcode_tb=010;#100 opcode_tb=011;#100 opcode_tb=100;#100 opcode_tb=101;#100 opcode_tb=110;#100 opcode_tb=111;#100 $stop;endalways #50 clk=~clk;endmodule约束文件源码(下板操作需要)## Clock signalset_property PACKAGE_PIN E3 [get_ports clk]set_property IOSTANDARD LVCMOS33 [get_ports clk]##Switchesset_property PACKAGE_PIN J15 [get_ports {ina[0]}]set_property IOSTANDARD LVCMOS33 [get_ports {ina[0]}]set_property PACKAGE_PIN L16 [get_ports {ina[1]}]set_property IOSTANDARD LVCMOS33 [get_ports {ina[1]}]set_property PACKAGE_PIN M13 [get_ports {ina[2]}]set_property IOSTANDARD LVCMOS33 [get_ports {ina[2]}]set_property PACKAGE_PIN R15 [get_ports {ina[3]}]set_property IOSTANDARD LVCMOS33 [get_ports {ina[3]}]set_property PACKAGE_PIN R17 [get_ports {inb[0]}]set_property IOSTANDARD LVCMOS33 [get_ports {inb[0]}] set_property PACKAGE_PIN T18 [get_ports {inb[1]}]set_property IOSTANDARD LVCMOS33 [get_ports {inb[1]}] set_property PACKAGE_PIN U18 [get_ports {inb[2]}]set_property IOSTANDARD LVCMOS33 [get_ports {inb[2]}] set_property PACKAGE_PIN R13 [get_ports {inb[3]}]set_property IOSTANDARD LVCMOS33 [get_ports {inb[3]}] set_property PACKAGE_PIN U12 [get_ports {opcode[0]}]set_property IOSTANDARD LVCMOS33 [get_ports {opcode[0]}] set_property PACKAGE_PIN U11 [get_ports {opcode[1]}]set_property IOSTANDARD LVCMOS33 [get_ports {opcode[1]}] set_property PACKAGE_PIN V10 [get_ports {opcode[2]}]set_property IOSTANDARD LVCMOS33 [get_ports {opcode[2]}] ## LEDsset_property PACKAGE_PIN V15 [get_ports {out[0]}]set_property IOSTANDARD LVCMOS33 [get_ports {out[0]}]set_property PACKAGE_PIN V14 [get_ports {out[1]}]set_property IOSTANDARD LVCMOS33 [get_ports {out[1]}]set_property PACKAGE_PIN V12 [get_ports {out[2]}]set_property IOSTANDARD LVCMOS33 [get_ports {out[2]}]set_property PACKAGE_PIN V11 [get_ports {out[3]}]set_property IOSTANDARD LVCMOS33 [get_ports {out[3]}]三、仿真结果如下图可以看出当opcode的值依次递增时,ina和inb依次做加,减,加1,减1,逻辑与,逻辑或,逻辑非,逻辑异或等操作,结果存放在out里。

vivado工具与verilog语言的使用实验总结

vivado工具与verilog语言的使用实验总结文章标题:深入探讨vivado工具与verilog语言的使用实验总结导言:在数字电路设计与实现的过程中,vivado工具与verilog语言的使用至关重要。

通过一系列的实验,我们能够全面地了解这两者在数字电路设计中的应用,并掌握它们的使用技巧。

本文将以从简到繁、由浅入深的方式,深入探讨vivado工具与verilog语言的使用实验总结,帮助读者全面理解这一主题。

一、vivado工具的基本介绍在数字电路设计中,vivado工具是一款由Xilinx公司推出的集成化开发环境。

它拥有丰富的功能和强大的性能,能够帮助设计者完成从设计到验证的全流程。

在实验中,我们首先对vivado工具的基本操作进行了学习,包括创建工程、添加设计文件、进行综合与实现等一系列步骤。

通过实践,我们能更加熟练地运用vivado工具进行数字电路设计。

二、verilog语言的基础知识verilog语言是一种硬件描述语言,广泛应用于数字电路的设计与验证。

在实验中,我们深入学习了verilog语言的基础知识,包括模块化的设计思想、信号的赋值与传输、行为级建模和结构级建模等内容。

通过对verilog语言的学习,我们能够更好地理解数字电路的工作原理,提高设计的效率和准确性。

三、vivado工具与verilog语言的综合应用在实验的进阶阶段,我们将vivado工具与verilog语言相结合,进行了一系列的综合应用实验。

通过实际的案例学习,我们掌握了如何利用vivado工具进行综合、仿真和验证,并通过verilog语言实现各种功能模块。

这些实验不仅加深了我们对vivado工具和verilog语言的理解,同时也提高了我们的综合应用能力。

总结与回顾:通过以上的实验学习,我们对vivado工具与verilog语言的使用有了更深入的了解。

vivado工具作为一款集成化开发环境,能够为数字电路设计者提供全方位的支持;而verilog语言则作为一种硬件描述语言,能够帮助设计者更加灵活地进行数字电路设计与验证。

Vivado实验01_流水灯仿真实验及下板步骤

一、新建工程1. 打开Vivado ,界面如下:2. 点击上述界面中的Create New Project ,弹出新建工程向导,依次点击Next:3.板卡选项分别为Family: Artix-7Sub-Family: Artix-7Package: csg324Speed grade: -1Temp grade: C于是,Part选择xc7a100tcsg324-1,然后下一步点击Next Finish;二、设计文件输入1.如下图,点击输入设计程序:2.如下图,选择新建文件,依次创建4个verilog文件,文件名依次为:clock_div; ctc; s_74ls138; led_light注意:最后一个为顶层文件,文件名与项目的文件名相同,且所有名称中不能出现中文、空格和符号3.双击打开,然后输入依次设计程序:注意:每次输入一个设计程序最好保存一次,保存操作如下图然后重复步骤,将4个设计程序依次输入保存4.添加仿真文件:5.进入仿真,点击 Run Simulation Run Behavioral Simulation6.调节缩小按钮,将间隔调节为1s,方便观察实验结果,然后点击上方运行按钮进行仿真,接着点击弹出的信息条的Background将其隐藏,即可看到完整的仿真循环结果7.仿真结果如下图:三、下板操作1.仿真完成后,先关闭仿真,操作如下图:2.接着进行下一步综合,如下图操作:3.综合处成功后,要进行实现操作,如下图:4.实现成功后进行下一步,管脚约束,操作如下图:注意:此处需用到板卡手册,请使用老师群共享的文件“Nexys4-DDR_rm”,此为配适的较新版本,否则可能出现错误5.约束文件生成后,更改为I/O操作界面:6.此处不能使用默认电压值,否则会报错,更改电压值为,然后将时钟引脚接至E3,复位引脚接至C12,y0至y7输出接至V16、T15、U14、T16、V15、V14、V15、V11,引脚的连接方式有三种,所有操作如下图:7.约束完成后,关闭保存:8.在源程序文档中的约束文件中可以看到刚才操作生成的约束文件,也可以直接在约束文件中直接输入代码来完成管教的约束和更改:9.约束完成后,生成编程文件:10.此时需要连接板卡到电脑,在此之前需要对板卡进行设置:11.连接电脑,打开电源开关,等待驱动安装完成后,打开Hardware Manager Open a new hardware target 在跳出的提示框中一直点击Next,不需更改,直到Finish Program device 选择板卡xc7a100t_0 在跳出的选择框中点击ok,这时就可以观察到仿真结果中的流水灯效果,以上为识别板卡到把编程文件下载到板卡的无脑操作,具体步骤请看下图:12.观察到板卡上的实验结果正确后,实验到此结束,关闭板卡的电源开关,拔出板卡,以上。

VivadofifoIP完整例程(包括testbench)

VivadofifoIP完整例程(包括testbench)⽹上尽管有各种介绍fifo的⽂章,但⼤部分没有⼀个完整的例程来练习,这⾥给出能够完整演⽰的fifo例程和仿真分析。

⼯程⽂件虽然部分基于xilinx的官⽅例程,但官⽅例程没有testbench,这部分是⾃⼰编写的,并对不同的配置进⾏了分析,完整的⼯程⽂件见如果没有分数下载,认真看本篇,也能做出来。

实验⼀⾃编fifo主程序module Asyn_FIFO#(parameter WIDTH = 8,parameter DEPTH = 4)(input clk_wr,input clk_rd,input rst_n_rd,input rst_n_wr,input wr_en,input rd_en,input [WIDTH-1:0] data_wr,output [WIDTH-1:0] data_rd,output reg rd_empty,output reg wr_full);//definationreg [WIDTH-1 : 0] mem [0 : (1<<DEPTH)-1]; //2^DEPTH numbersreg [DEPTH : 0] wp, rp;reg [DEPTH : 0] wr1_rp, wr2_rp, rd1_wp, rd2_wp;reg [DEPTH : 0] wbin, rbin;wire [DEPTH-1 : 0] waddr, raddr;wire [DEPTH : 0] wbin_next, rbin_next; //bincodewire [DEPTH : 0] wgray_next, rgray_next; //graycodewire rd_empty_val, wr_full_val;//outputassign data_rd = mem[raddr];//inputalways@(posedge clk_wr)if(wr_en && !wr_full)mem[waddr] <= data_wr;/*----------generate waddr and raddr-------------------------*///gen raddr and read gray codealways@(posedge clk_rd or negedge rst_n_rd)if(!rst_n_rd){rbin, rp} <= 0;else{rbin, rp} <= {rbin_next, rgray_next};assign raddr = rbin[DEPTH-1 : 0];assign rbin_next = rbin + (rd_en & ~rd_empty);assign rgray_next = rbin_next ^ (rbin_next >> 1);//gen waddr and write gray codealways@(posedge clk_wr or negedge rst_n_wr)if(!rst_n_wr){wbin, wp} <= 0;elseelse{wbin, wp} <= {wbin_next, wgray_next};assign waddr = wbin[DEPTH-1 : 0];assign wbin_next = wbin + (wr_en & ~wr_full);assign wgray_next = wbin_next ^ (wbin_next >> 1);/*---------------synchro rp and wp--------------------------*///synchro rpalways@(posedge clk_wr or negedge rst_n_wr)if(!rst_n_wr){wr2_rp, wr1_rp} <= 0;else{wr2_rp, wr1_rp} <= {wr1_rp, rp}; //delay two clock//synchro wpalways@(posedge clk_rd or negedge rst_n_rd)if(!rst_n_rd){rd2_wp, rd1_wp} <= 0;else{rd2_wp, rd1_wp} <= {rd1_wp, wp};/*---------------empty and full flags--------------------------*///gen rd_emptyassign rd_empty_val = (rd2_wp == rgray_next);always@(posedge clk_rd or negedge rst_n_rd)if(!rst_n_rd)rd_empty <= 1'b1;elserd_empty <= rd_empty_val;//gen wr_full, two high bit do not equalassign wr_full_val = ({~wr2_rp[DEPTH : DEPTH-1], wr2_rp[DEPTH-2 : 0]} == wgray_next); always@(posedge clk_wr or negedge rst_n_wr)if(!rst_n_wr)wr_full <= 1'b0;elsewr_full <= wr_full_val;endmoduletb程序module Asyn_FIFO_tb;parameter WIDTH = 8;reg clk_wr;reg clk_rd;reg rst_n_rd;reg rst_n_wr;reg [WIDTH-1:0] data_wr;reg wr_en;wire wr_full;wire [WIDTH-1:0] data_rd;reg rd_en;wire rd_empty;Asyn_FIFO fifo_inst(.clk_wr(clk_wr),.rst_n_rd(rst_n_rd),.rst_n_wr(rst_n_wr),.wr_en(wr_en),.data_wr(data_wr),.clk_rd(clk_rd),.rd_en(rd_en),.data_rd(data_rd),.rd_empty(rd_empty),.wr_full(wr_full));initial beginrst_n_rd = 0;rst_n_wr = 0;clk_wr = 0;clk_rd = 0;wr_en = 0;rd_en = 0;#20rst_n_rd = 1;rst_n_wr = 1;#80wr_en = 1;rd_en = 0;#335wr_en = 0;rd_en = 1;endalways #10 clk_wr = ~clk_wr;always #20 clk_rd = ~clk_rd;/* always @(posedge clk_rd)rd_en <= ($random) % 2;always @(posedge clk_wr)wr_en <= ($random) % 2; */always @(posedge clk_wr)data_wr <= ($random) % 256; endmodule将simulate.runtime时间改为1500ns实验⼆调⽤已IP库fifo, 编写testbench, 参考xilinx下⾯的官⽅例程,但⾃⼰编写testbench.双击FIFO下⾯的选项Component Name输⼊char_fifo, Fifo Implementation选Independent Clocks Block RAM.注意这⾥选的是保持Leave Out of context per IP选择, 双击Generate button.⾄此⽣成fifo IP.下⾯制作testbench,拷贝第57⾄63⾏到testbench tb_fifo.v例化char_fifo your_instance_name (.rst(rst), // input wire rst.wr_clk(wr_clk), // input wire wr_clk.rd_clk(rd_clk), // input wire rd_clk.din(din), // input wire [7 : 0] din.wr_en(wr_en), // input wire wr_en.rd_en(rd_en), // input wire rd_en.dout(dout), // output wire [7 : 0] dout.full(full), // output wire full.empty(empty), // output wire empty.wr_rst_busy(wr_rst_busy), // output wire wr_rst_busy.rd_rst_busy(rd_rst_busy) // output wire rd_rst_busy);从图上可以看到full信号拉低需要在复位信号410ns以后,重新修改testbench`timescale 1ns/1psmodule tb_fifo1;//***************************************************************************// Parameter definitions//***************************************************************************parameter WIDTH = 8;parameter DEPTH = 16;//inputsreg rst;reg wr_clk;reg rd_clk;reg [7:0] din;reg wr_en;reg rd_en;//outputswire [7:0] dout;wire full;wire empty;wire [3:0] rd_data_count;wire [3:0] wr_data_count;// Instantiate the Unitchar_fifo your_instance_name (.rst(rst), // input wire rst.wr_clk(wr_clk), // input wire wr_clk.rd_clk(rd_clk), // input wire rd_clk.din(din), // input wire [7 : 0] din.wr_en(wr_en), // input wire wr_en.rd_en(rd_en), // input wire rd_en.dout(dout), // output wire [7 : 0] dout.full(full), // output wire full.empty(empty), // output wire empty.rd_data_count(rd_data_count), // output wire [3 : 0] rd_data_count.wr_data_count(wr_data_count) // output wire [3 : 0] wr_data_count);always #10 wr_clk = ~wr_clk;always #20 rd_clk = ~rd_clk;initial begininitial begin// Initialize Inputswr_clk = 0;rd_clk = 0;rst = 1;din = 1'b1;wr_en = 0;rd_en = 0;// Wait 100 ns for global reset to finish#100rst = 0;#500;repeat (18) beginwr_en = 1;#20;wr_en = 0;#20;din = din + 1'b1;end#290repeat (18) beginrd_en = 1;#40;rd_en = 0;#40;endendendmodule选Standard FIFO时,有效读写深度是15写得时候,din是输⼊,所以不与rd_clk时钟对齐,读的时候是时钟打得出去,所以dout与时钟rd_clk对齐。

电子系统设计实验指导书(FPGA基础篇Vivado版)

实验指导书(FPGA 基础篇 Vivado 版)

东南大学 电子科学 ........................................................................................................................................................... 1

安全使用规范

东南大学 电子科学与工程学院

无论何时,外部电源供电与 USB 两种供电方式只能用其中一种,避免因为电压有所差别而烧坏电路板。 采用电压高于5.5V的任何电源连接器可能造成永久性的损害。 插拔接插件前请关闭电路板总开关,否则易损坏器件。 电路板应在绝缘平台上使用,否则可能引起电路板损坏。 不同编码机制不要混接。 安装设备需防止静电。 液晶显示器件或模块结雾时,不要通电工作,防止电极化学反应,产生断线。 遇到正负极连接时需谨慎,避免接反引起开发板的损坏。 保持电路板的表面清洁。 小心轻放,避免不必要的硬件损伤。

实验目的 ....................................................................................................................................................... 17 实验内容 ....................................................................................................................................................... 17 实验要求 ....................................................................................................................................................... 17 实验步骤 ....................................................................................................................................................... 17 实验结果 ....................................................................................................................................................... 22

数字钟试验设计指导试验目的掌握基于diagram的vivado工程设计流程1.doc

数字钟试验设计指导试验目的掌握基于diagram的vivado工程设计流程1数字钟实验设计指导一、实验目的掌握基于diagram的vivado工程设计流程,学会添加IP目录并调用其中IP二、实验原理介绍本实验实现了一个简单的数字钟,能实现计时的功能。

由于数码管只有4位,因此本数字钟只能计分和秒。

本系统的逻辑部分主要由74系列的IP构成。

三、实验步骤:1、创建新工程1)打开Vivado2014.4设计开发软件,选择Create New Project.2)在弹出的创建新工程的界面中,点击Next,开始创建新工程。

3)在Project Name界面中,将工程名称修改为Digital_Clock,并设置好工程存放路径。

同时勾选上创建工程子目录的选项。

这样,整个工程文件都将存放在创建的Digital_Clock子目录中。

点击Next。

specify sources at this time(不指定添加源文件)勾选上。

点击Next。

5)在器件板卡选型界面中,在Search栏中输入xc7a35tcpg236搜索本次实验所使用的Basys3板卡上的FPGA芯片。

并选择xc7a35tcpg236-1器件。

(器件命名规则详见xilinx官方文档)点击Next。

工程的创建。

2、添加已设计好的IPcore。

工程建立完毕,我们需要将Digital_Clock这个工程所需的IP目录文件夹复制到本工程文件夹下。

本工程需要两个IP目录:74LSXX_LIB与Interface。

74LSXX_LIB和Interface都位于B3_Lab\Lab1\Digital_Clock下。

添加完后的本工程文件夹如下图:1)在Vivado设计界面的左侧设计向导栏中,点击Project Manager目录下的Project Setting。

2)在Project Setting界面中,选择IP选项,进入IP设置界面。

点击Add Respository...添加本工程文件夹下的IP_Catalog目录:3)完成目录添加后,可以看到所需IP已经自动添加。

Vivado实验流水灯仿真实验及下板步骤

一、新建工程1.打开Vivado2014.2,界面如下:2.点击上述界面中的CreateNewProject,弹出新建工程向导,依次点击Next:3.板卡选项分别为Family:Artix-7Sub-Family:Artix-7Package:csg324Speedgrade:-1Tempgrade:C于是,Part选择xc7a100tcsg324-1,然后下一步点击Next✍Finish;二、设计文件输入1.如下图,点击输入设计程序:2.如下图,选择新建文件,依次创建4个verilog文件,文件名依次为:clock_div;ctc;s_74ls138;led_light注意:最后一个为顶层文件,文件名与项目的文件名相同,且所有名称中不能出现中文、空格和符号3.双击打开,然后输入依次设计程序:注意:每次输入一个设计程序最好保存一次,保存操作如下图然后重复步骤,将4个设计程序依次输入保存4.添加仿真文件:5.进入仿真,点击RunSimulation✍RunBehavioralSimulation6.调节缩小按钮,将间隔调节为1s,方便观察实验结果,然后点击上方运行按钮进行仿真,接着点击弹出的信息条的Background将其隐藏,即可看到完整的仿真循环结果7.仿真结果如下图:三、下板操作1.仿真完成后,先关闭仿真,操作如下图:2.接着进行下一步综合,如下图操作:3.综合处成功后,要进行实现操作,如下图:4.实现成功后进行下一步,管脚约束,操作如下图:注意:此处需用到板卡手册,请使用老师群共享的文件“Nexys4-DDR_rm”,此为配适的较新版本,否则可能出现错误5.约束文件生成后,更改为I/O操作界面:6.此处不能使用默认电压值,否则会报错,更改电压值为3.3V,然后将时钟引脚接至E3,复位引脚接至C12,y0至y7输出接至V16、T15、U14、T16、V15、V14、V15、V11,引脚的连接方式有三种,所有操作如下图:7.约束完成后,关闭保存:8.在源程序文档中的约束文件中可以看到刚才操作生成的约束文件,也可以直接在约束文件中直接输入代码来完成管教的约束和更改:9.约束完成后,生成编程文件:10.此时需要连接板卡到电脑,在此之前需要对板卡进行设置:11.连接电脑,打开电源开关,等待驱动安装完成后,打开HardwareManager✍Openanewhardwaretarget✍在跳出的提示框中一直点击Next,不需更改,直到Finish✍Programdevice✍选择板卡xc7a100t_0✍在跳出的选择框中点击ok,这时就可以观察到仿真结果中的流水灯效果,以上为识别板卡到把编程文件下载到板卡的无脑操作,具体步骤请看下图:12.观察到板卡上的实验结果正确后,实验到此结束,关闭板卡的电源开关,拔出板卡,以上。

电子系统设计实验指导书(FPGA基础篇Vivado版)

实验四:状态机 ..................................................................................................................................................... 17 一、 二、 三、 四、 实验目的 ....................................................................................................................................................... 24 实验内容 ....................................................................................................................................................... 24 实验要求 ....................................................................................................................................................... 24 实验步骤 ....................................................................................................................................................... 24

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Vivado设计流程一、实验目的与实验要求1、实验目的本实验的目的是熟悉实验环境,学习如何使用Vivado 2015.4创建、综合、实现、仿真等功能。

2、实验要求(1)学习Vivado-Design-Flow.pdf、约束文件.ppt,在实验报告中回答以下问题:a) 描述Vivado 的设计流程b) 什么是网表c) 什么是约束文件?通过IO planning 完成的是什么方面的约束?d) Vivado 设计流程中,Synthesis 的作用是什么?e) Vivado 设计流程中,Implementation 的作用是什么?(2)在实验报告中提交上述实验内容的Verilog 代码、仿真结果图、RTL 详细设计图(参考Vivado-Design-Flow.pdf 第11 页Open Elaborated Design—>Schematic)、综合实现图(参考Vivado-Design-Flow.pdf 第13 页Open Synthesized Design—>Schematic)以及实验现象图(照片);(3)提交实验报告和完整的工程文件。

二、实验设备(环境)及要求(1)Xilinx Ego1实验平台。

(2)OS:Win7 64位(3)Software:Vivado15.4开发工具三、实验内容与步骤(1)实验内容a)学习视频,了解Vivado设计流程和功能:“EGO五分钟快速上手.mp4”和“EGo五分钟搭建你的数字积木.mp4”。

b)按照“Ego五分钟快速上手——流水灯.pdf”完成流水灯实验。

c)学习Vivado-Design-Flow.pdf、约束文件.ppt,回答问题。

(2)主要步骤a)在Vivado中创建RTL设计,新建一个名为vivado_design_flow的空白工程。

b)模块代码如下:module flowing_light(input clk,input rst,output [15:0] led);reg[23:0]cnt_reg;reg[15:0]light_reg;always@(posedge clk)beginif(rst)cnt_reg<=0;elsecnt_reg<=cnt_reg+1;endalways@(posedge clk)beginif(rst)light_reg<=16'h0001;else if (cnt_reg == 24'hffffff)beginif(light_reg == 16'h8000)light_reg<=16'h0001;elselight_reg<=light_reg<<1;endendassign led = light_reg;endmodulec)RTL门级结构图:图1: RTL门级结构图d)综合Run Synthesis实现图图2:综合最终设计图e)添加约束文件,按照对应管脚,综合、实现进行管脚约束:set_property PACKAGE_PIN F6 [get_ports {led[15]}]set_property PACKAGE_PIN G4 [get_ports {led[14]}]set_property PACKAGE_PIN G3 [get_ports {led[13]}]set_property PACKAGE_PIN J4 [get_ports {led[12]}]set_property PACKAGE_PIN H4 [get_ports {led[11]}]set_property PACKAGE_PIN J3 [get_ports {led[10]}]set_property PACKAGE_PIN J2 [get_ports {led[9]}]set_property PACKAGE_PIN K2 [get_ports {led[8]}]set_property PACKAGE_PIN K1 [get_ports {led[7]}]set_property PACKAGE_PIN H6 [get_ports {led[6]}]set_property PACKAGE_PIN H5 [get_ports {led[5]}]set_property PACKAGE_PIN J5 [get_ports {led[4]}]set_property PACKAGE_PIN K6 [get_ports {led[3]}]set_property PACKAGE_PIN L1 [get_ports {led[2]}]set_property PACKAGE_PIN M1 [get_ports {led[1]}]set_property PACKAGE_PIN K3 [get_ports {led[0]}]set_property PACKAGE_PIN P17 [get_ports clk]set_property PACKAGE_PIN R15 [get_ports rst]set_property IOSTANDARD LVCMOS33 [get_ports {led[15]}] set_property IOSTANDARD LVCMOS33 [get_ports {led[14]}] set_property IOSTANDARD LVCMOS33 [get_ports {led[13]}] set_property IOSTANDARD LVCMOS33 [get_ports {led[12]}] set_property IOSTANDARD LVCMOS33 [get_ports {led[11]}] set_property IOSTANDARD LVCMOS33 [get_ports {led[10]}] set_property IOSTANDARD LVCMOS33 [get_ports {led[9]}] set_property IOSTANDARD LVCMOS33 [get_ports {led[8]}] set_property IOSTANDARD LVCMOS33 [get_ports {led[7]}] set_property IOSTANDARD LVCMOS33 [get_ports {led[6]}] set_property IOSTANDARD LVCMOS33 [get_ports {led[5]}] set_property IOSTANDARD LVCMOS33 [get_ports {led[4]}] set_property IOSTANDARD LVCMOS33 [get_ports {led[3]}] set_property IOSTANDARD LVCMOS33 [get_ports {led[2]}] set_property IOSTANDARD LVCMOS33 [get_ports {led[1]}] set_property IOSTANDARD LVCMOS33 [get_ports {led[0]}] set_property IOSTANDARD LVCMOS33 [get_ports clk]set_property IOSTANDARD LVCMOS33 [get_ports rst]f)测试激励仿真代码:module test( );reg clk;reg rst;wire [3 : 0] led;flowing_light u0(.clk(clk),.rst(rst),.led(led) );parameter PERIOD = 10;always beginclk = 1'b0;#(PERIOD/2) clk = 1'b1;#(PERIOD/2);endinitial beginclk = 1'b0;rst = 1'b0;#100;rst = 1'b1;#100;rst = 1'b0;endendmodule进行行为仿真,得到并验证波形图g)添加时序约束,设置clock的最大和最小的delay timeh)最后进行综合,生成比特流文件,加载到板子上进行调试分析。

四:实验结果与分析(1)通过设计后,利用Vivado自带工具,生成RTL门级结构如下:图3:RTL门级结构(2)仿真得到波形图如下:图4:波型仿真图(3)实验板显示情况如下:图4:FPGA板测试图样图5:FPGA板测试图样五:结论(讨论)1、实验结论通过本次实验的流程和视频的观看,学会了如何使用Xilinx Vivado 2015.4创建、综合、实现、仿真等功能。

通过编写一个流水灯实验来介绍使用Xilinx Vivado 来进行基本的FPGA设计,简单易懂,并能很好的类比其他的设计。

图6 :实验流程图2、讨论在流水灯实验中,由于频率过高,导致了显示频率过快,可以增加分频代码,将频率再进一步降低,使显示更加清楚明了。

现回答报告中所提出的问题:a) 描述Vivado的设计流程:实验流程主要有以下几步:1、通过编写HDL文件的方式创建Vivado设计。

2、进行Verilog HDL语言编写3、写出测试激励,在测试激励中进行仿真4、综合、实现进行管脚约束5、生成bitstream文件,下载到FPGA开发板里b) 什么是网表:xilinx的步骤synphysize(综合)translate(注译),map(映射),和place and route(布局布线)综合以后生成的就为网表文件即一个电路的雏形,之后可以看到RTL(寄存器传输级)电路。

也可以看到technology 电路。

两者区别等你看到就很快明白。

这两张图片是对网表的一种直观的显示。

也就是综合器最后综合出了你的逻辑电路。

放在网表文件中。

c) 什么是约束文件:约束文件是用来指定选用FPGA器件的型号及定义引脚属性的文件。

其中包括管脚约束(将模块的端口和FPGA的管脚对应)、区域约束(将模块放置在FPGA 的特点位置)、时序约束(对数据建立、保持时间进行约束,保证设计在高速时钟下的工作可靠性等)。

通过IO planing完成的是管脚约束。

d) Vivado设计流程中,Synthesis的作用:即综合,作用是将所写的verilog代码通过编译器处理,生成一系列文件,向操作者报告综合的结果。

并且会自动生成门级逻辑结构网表,比源文件更加具体,可以用测试模块调用它做仿真。

e) Vivado设计流程中,Implementation的作用:即实现,作用是在Synthesis(综合)完成后,配合约束文件,实现设计。