基于处理器访存缺失率的节能软件设计与实现

《高性能并行运行时系统:设计与实现》随笔

《高性能并行运行时系统:设计与实现》读书随笔目录一、内容综述 (2)1.1 背景与动机 (3)1.2 高性能并行运行时系统的意义 (3)二、并行运行时系统的基本概念 (4)2.1 并行计算与并行运行时系统 (6)2.2 并行运行时系统的组成部分 (7)三、高性能并行运行时系统的设计要素 (9)3.1 性能优化策略 (10)3.2 可扩展性与可维护性 (12)3.3 容错与稳定性 (13)四、典型高性能并行运行时系统分析 (15)4.1 MapReduce及其应用场景 (16)4.2 Spark的工作原理与应用 (17)4.3 分布式内存计算系统TBB (19)五、并行运行时系统的实现技术 (21)5.1 编程模型与语言支持 (22)5.2 数据存储与管理 (24)5.3 网络通信与通信协议 (25)六、高性能并行运行时系统的测试与调试 (27)6.1 测试方法与工具 (28)6.2 常见问题与解决方案 (30)七、总结与展望 (31)7.1 本书主要内容回顾 (32)7.2 对未来发展的展望 (34)一、内容综述《高性能并行运行时系统:设计与实现》是一本关于高性能并行计算的经典著作,作者是著名的计算机科学家和教授。

本书详细介绍了高性能并行运行时系统的设计与实现过程,旨在为读者提供一套完整的理论框架和技术方法,以便在实际项目中构建高效、可扩展的并行计算系统。

本书共分为五个部分,分别是:并行计算基础、并行编程模型、并行数据结构与算法、并行运行时系统设计及实例分析和总结。

在前三部分中,作者首先介绍了并行计算的基本概念、原理和技术,包括共享内存模型、消息传递接口(MPI)等;接着详细讲解了并行编程模型,如任务划分、同步与互斥、负载均衡等;作者还介绍了一些常用的并行数据结构与算法,如哈希表、B树、红黑树等。

在第四部分中,作者深入探讨了并行运行时系统的设计与实现,包括线程管理、进程管理、资源分配等方面。

通过一系列实例分析,作者展示了如何根据具体问题选择合适的并行计算模型和编程技术,以及如何在实际项目中实现高效的并行运行时系统。

基于MIPS架构的多周期CPU设计

基于MIPS架构的多周期CPU设计柳成;荣静【摘要】为了提高多周期CPU流水线的效率,在指令存储器和数据存储器的数据读取中设计发送地址在上升沿、读取数据在下降沿,从而实现译码和访存在一个周期内完成.在取指级不再单独设置加法器,把PC+4放在ALU中完成.通过大量的多路选择器与数据交互总线来进行数据联通.采用Verilog HDL语言设计出CPU,并在VIVADO平台上实现仿真,最后通过龙芯公司的LS-CPU-EXB-002试验箱来进行验证,结果表明所设计的多周期CPU的有效性.【期刊名称】《软件》【年(卷),期】2018(039)008【总页数】5页(P40-44)【关键词】流水线;VerilogHDL;多周期CPU;LS-CPU-EXB-002试验箱【作者】柳成;荣静【作者单位】扬州大学广陵学院,江苏扬州 225000;扬州大学广陵学院,江苏扬州225000【正文语种】中文【中图分类】TP332MIPS架构是为流水线而生,每条MIPS指令的执行分为五个部分,每一个部分为一个流水级。

MIPS是最简单且内核开源的微处理器之一,相对于其它架构微处理器,相同位数的MIPS架构的时钟频率较低,其运行速度也较慢。

高效的CPU要求流水线的每一个阶段都占用固定的时间,再通过缩短流水线各个阶段的执行时间来提高时钟频率,在此我们通过改进取地址和读数据时钟控制来实现。

传统的MIPS架构多周期CPU的设计中,在发送地址的下一拍才能获得相应的数据,从指令和数据存储器中读取数据就需要等待一个周期,这样往往会造成资源浪费。

为了消除这个闲置时间,将发送地址设计在时钟的上升沿,读取数据放在下降沿,最终实现32位MIPS架构多周期CPU。

MIPS体系结构主要采用了流水线技术[1],它把一条指令的执行分为几个周期来完成。

这样每个周期处理器只做一件事,大大的减轻了处理器的任务,使处理器的频率更快,处理器也更高效。

通过改进文献[2]中的五级流水线得到如图1所示的多周期CPU流水线设计。

嵌入式处理器中访存部件的低功耗设计研究

i r d c d 5 . a e a ey,a d e u ly t ep we ft ewh l r c so sr d c d 2 . a — s e ue 4 3 v rg l n q al h o ro h oe p o e s ri e u e 3 2 v

5. , 理 器 总 功耗 平 均 降 低 了 2. , 关 键 路 径 延 时 反 而 减 少 , 理 器 性 能 略有 提 高 . 43 处 32 而 处

关键 词

访存部件 ; I ; ah ; T C c e低功耗 ; B 龙芯 1号

TP 0 32

中 图 法分 类号

Re e r h o w— we e o y Hi r r hy o s a c n Lo Po r M m r e a c fEm b d d Pr c s o e de o e s r

o oo y b s d o h o aiy i p o o e .J d ig b h it rc lvru l e r d r s ,t e d lg a e n t e lc l s r p s d u gn y t eh so ia it a mo y a d e s h t m

Ab t a t W ih g d o 一 r c s o st er s a c r t t p , e l h p d v l p d b CTCAS, s r c t o s n 1 p o e s ra h e e r h p o o y e a r a i e e o e y I c t i p p r f c s s o h O p we e i n me h d l g fo — h p me r i r r h .By a a y h s a e o u e n t e l W— o rd s t o o o y o n c i mo y h e a c y g n l—

申威众核处理器访存与通信融合编译优化

申威众核处理器访存与通信融合编译优化

方燕飞;李雁冰;董恩铭;王云飞;刘齐

【期刊名称】《软件学报》

【年(卷),期】2024(35)6

【摘要】申威众核片上多级存储层次是缓解众核“访存墙”的重要结构.完全由软件管理的SPM结构和片上RMA通信机制给应用性能提升带来很多机会,但也给应用程序开发优化与移植提出了很大挑战.为充分挖掘片上存储层次特点提升应用程序性能,同时减轻用户编程优化负担,提出一种多级存储层次访存与通信融合的编译优化方法.该方法首先设计融合编译指示,将程序高层信息传递给编译器.其次构建编译优化收益模型并设计启发式循环优化方案迭代求解框架,并由编译器完成循环优化方案的求解和优化代码的变换.通过编译生成的DMA和RMA批量数据传输操作,将较低存储层次空间中高访问延迟的核心数据批量缓冲进低访问延迟的更高存储层次空间中.在3个典型测试用例上进行优化实验测试与分析,结果表明所提出的优化在性能上与手工优化相当,较未优化版程序性能有显著提升.

【总页数】20页(P2648-2667)

【作者】方燕飞;李雁冰;董恩铭;王云飞;刘齐

【作者单位】国家并行计算机工程技术研究中心

【正文语种】中文

【中图分类】TP314

【相关文献】

1.基于申威众核处理器的MD5解密算法优化

2.申威异构众核处理器架构下结构瞬态有限元并行算法

3.面向申威异构众核处理器的矩阵乘分块参数模型

4.面向申威众核处理器的规则处理优化技术

5.申威26010众核处理器上Winograd卷积算法的研究与优化

因版权原因,仅展示原文概要,查看原文内容请购买。

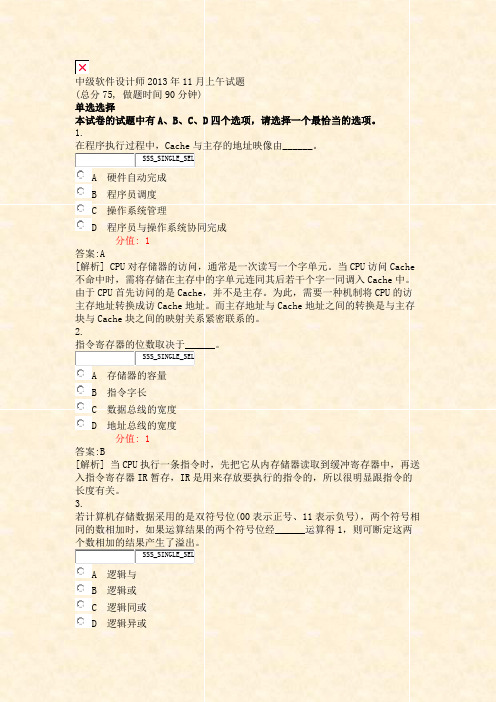

中级软件设计师2013年11月上午试题_真题(含答案与解析)-交互

中级软件设计师2013年11月上午试题(总分75, 做题时间90分钟)单选选择本试卷的试题中有A、B、C、D四个选项,请选择一个最恰当的选项。

1.在程序执行过程中,Cache与主存的地址映像由______。

SSS_SINGLE_SELA 硬件自动完成B 程序员调度C 操作系统管理D 程序员与操作系统协同完成分值: 1答案:A[解析] CPU对存储器的访问,通常是一次读写一个字单元。

当CPU访问Cache 不命中时,需将存储在主存中的字单元连同其后若干个字一同调入Cache中。

由于CPU首先访问的是Cache,并不是主存。

为此,需要一种机制将CPU的访主存地址转换成访Cache地址。

而主存地址与Cache地址之间的转换是与主存块与Cache块之间的映射关系紧密联系的。

2.指令寄存器的位数取决于______。

SSS_SINGLE_SELA 存储器的容量B 指令字长C 数据总线的宽度D 地址总线的宽度分值: 1答案:B[解析] 当CPU执行一条指令时,先把它从内存储器读取到缓冲寄存器中,再送入指令寄存器IR暂存,IR是用来存放要执行的指令的,所以很明显跟指令的长度有关。

3.若计算机存储数据采用的是双符号位(00表示正号、11表示负号),两个符号相同的数相加时,如果运算结果的两个符号位经______运算得1,则可断定这两个数相加的结果产生了溢出。

SSS_SINGLE_SELA 逻辑与B 逻辑或C 逻辑同或D 逻辑异或分值: 1答案:D[解析] 本题考查逻辑运算,两个相同符号位经过异或可以得到1。

4.某指令流水线由4段组成,各段所需要的时间如下图所示。

连续输入8条指令时的吞吐率(单位时间内流水线所完成的任务数或输出的结果数)为______。

SSS_SINGLE_SELA 8/56ΔtB 8/32ΔtC 8/28ΔtD 8/24Δt分值: 1答案:C[解析] 吞吐率是指单位时间里流水线处理机流出的结果数。

对指令而言,就是单位时间里执行的指令数。

基于Cache锁和直接缓存访问的网络处理优化方法

基于Cache锁和直接缓存访问的网络处理优化方法苏文;章隆兵;高翔;苏孟豪【摘要】通过分析计算机系统网络数据处理相关程序的访存行为、局部性特点和系统交互等问题,指出在高速网络环境下传统处理器网络子系统设计存在很大缺陷,并进一步提出一种基于软硬件协同设计的优化方案.该方案具体包括改进的直接缓存访问技术、关键程序的cache锁策略和相应系统互连结构及一致性协议等.实验表明,与传统方案相比,基于该方案的网络TCP传输带宽提高约48%,极限情况下UDP丢包率下降40%,传输延时降低超过10%.网络测试程序在与SPEC2000测试程序并发执行情况下,网络数据带宽提高约44%.此外还讨论了该优化方案与其他网络优化技术共同使用的基本原则和相应策略.【期刊名称】《计算机研究与发展》【年(卷),期】2014(051)003【总页数】10页(P681-690)【关键词】网络处理;直接缓存访问;cache锁;系统互联;I/O优化【作者】苏文;章隆兵;高翔;苏孟豪【作者单位】计算机体系结构国家重点实验室北京 100190;中国科学院计算技术研究所北京 100190;中国石油北京油气调控中心北京100007;龙芯中科技术有限公司北京 100190;计算机体系结构国家重点实验室北京 100190;中国科学院计算技术研究所北京 100190;龙芯中科技术有限公司北京 100190;计算机体系结构国家重点实验室北京 100190;中国科学院计算技术研究所北京 100190;龙芯中科技术有限公司北京 100190;计算机体系结构国家重点实验室北京 100190;中国科学院计算技术研究所北京 100190;龙芯中科技术有限公司北京 100190【正文语种】中文【中图分类】TP302随着近年来高速网络技术的快速发展,现代处理器网络子系统设计面临了许多新的困难和挑战.研究表明[1],基于万兆以太网络(10GbE)的数据传输可以轻易耗尽高端4核处理器中2个核的计算能力.与此同时,网络速度的快速增长导致系统网络数据处理效率显著下降[2].随着云计算、移动服务等新应用的发展,“快网络-慢计算”这一现象越发突出.为了解决这一问题,研究人员从体系结构设计、协议栈设计、系统软件等各方面提出了多种优化方案,例如直接缓存访问(direct cache access,DCA)[3]、网卡集成(integrated NIC)[4]、中断聚集(interrupts coalescing)[5]等技术.但是这些方案无一例外地都只关注于网络处理流程中的某一局部过程,其效果往往受到具体平台结构的制约,不具有通用性.因此处理器计算能力增长慢于网络速度增长这一“剪刀差”问题至今没有被很好地解决.最近的研究表明[6],随着高速网络技术的发展,网络处理的瓶颈问题已经由原来的校验码计算、协议栈操作转向了操作系统中断处理和缓冲区维护等.由于后者的访存行为被证明具有很大的不确定性,所以整个网络处理过程的时间局部性较差[7].这导致传统cache系统在面对网络处理访存操作时效率低下,这一问题已经成为了系统性能提高的巨大障碍.基于上述分析,本文首先研究了网络处理相关程序访存和系统交互的特点,并指出影响性能提高的关键问题,进而提出一种基于体系结构改进和系统软件优化的网络子系统设计方案.该方案通过提高网络处理程序访存效率和系统cache命中率来降低相关数据和指令的访问延迟,并改善局部性,最终提高系统性能.本文的主要贡献如下:1)基于现有主流处理器体系结构讨论了单个数据包处理和多数据包系统交互过程的访存行为和局部性特点,并指出影响网络性能的关键因素.2)提出利用改进DCA和cache锁技术来提高网络处理性能和局部性,并对系统互联结构和一致性协议做出了相应优化设计,给出了具体的软硬件系统实现方案.3)研究了网络处理与系统本地程序并发运行时的交互问题.4)研究并给出了多个网络优化技术协同工作的基本原则和初步方案.实验表明,基于本文方案系统网络带宽较传统系统提高超过40%,通信延迟降低10%以上,并且网络性能在多程序并行环境下有较大提升.1 网络处理访存行为分析本节首先分析了网络处理的一般流程、相关数据结构和时间开销分布,之后讨论了单个和多个网络数据包处理的访存行为和局部性.此外分析了网络处理与其他程序并发执行的系统交互问题.1.1 网络处理流程典型的网络处理流程如图1所示.以数据接收为例,当数据包在物理线路上(本文中为以太网)被网卡检测到后,网卡对其进行地址分析并完成内部流量控制、校验码计算等操作.之后通过DMA引擎将数据传输至预先定义的DMA描述符所指的数据包缓冲区中,更新相关套接字缓冲区(skb_buf)信息,并产生一个系统中断来通知CPU进行处理.CPU收到中断之后,根据skb_buf中的信息对收到数据包进行层次化的协议栈操作.最终操作系统通过系统调用,将保存在发送/接收队列内的数据拷贝至用户应用程序中,并维护相关缓冲区.这一过程反过来即为数据发送过程.为了降低不同缓冲区间的数据拷贝开销,现代操作系统中经常将多个缓冲区共享使用[8].Fig.1 Network packet processing flow.图1 网络数据包处理流程一般认为,网络处理主要包括以下几部分:中断处理、网卡驱动、协议栈处理、操作系统维护、数据拷贝、校验计算等.研究表明[6],近些年来随着网络速度的提高,中断处理、网卡驱动和操作系统维护开销超过了总时间开销的60%.这是由于这些操作内部包含了大量非常耗时的存储空间维护、数据拷贝、I/O寄存器访问等操作.一些研究提出用专用的拷贝加速器来完成数据拷贝过程[9],已经取得了很好的效果;而存储空间维护、中断处理等则通常在操作系统层面进行优化[10].1.2 局部性分析与当前已有的网络处理分析、优化工作不同,本文不仅研究了单个数据包处理中的关键数据结构和访存轨迹,同时重点在系统层面讨论了程序运行时网络处理与其他程序及系统的交互问题.本文认为后者是一直被忽略的影响网络性能的关键问题.单个网络数据包处理过程主要涉及了DMA描述符、skb_buf、包缓冲(data buffer)和发送/接收队列4处存储空间.它们之间的交互关系如图2所示.处理过程主要操作包括:查询更新描述符、包缓冲数据传输、skb_buf生成和描述符维护、协议栈处理、发送/接受队列数据传输等.Fig.2 Interactions among different buffers in single packet processing.图2 单包处理中的存储空间交互关系可以看出:与传统不同,单个数据包的处理过程基本为串行结构,并且没有“主循环”(main loop).以下特点决定了该过程具有较差的局部性:1)通过网卡DMA传输的I/O数据(包括DMA描述符更新信息和数据包)只能保存在内存中,并由CPU通过非缓存的方式进行读取.这一特点决定了大量数据访问无法利用系统cache,而只能通过较慢的内存和I/O访问来完成.尽管目前许多处理器通过一致性硬件[11]实现了相关数据在cache中的映射,但系统仍会产生大量高速缓存强制缺失(compulsory cache miss).另外频繁的一致性操作会降低传输效率,同时数据在网卡一端仍只能通过DMA与内存进行数据传输.2)层次化的协议处理过程具有较差的局部性.由于数据包是按照协议层后进先出(LIFO)规则组织,所以每一层的相关操作都是单向的,不会出现反复访问某一段数据和程序的操作.每一层的相关数据如地址、长度、协议类型等头(header)信息在该层协议处理完毕后将会被丢弃.以上这2点基本上决定了在单个网络数据包处理流程中具有较少的并行、局部性优化机会.与一般程序不同,网络处理是由系统中断触发、并且在操作系统中断上下文(interrupt context)环境中运行.因此在实际系统中其与系统中原有程序并发执行,交替占用CPU,cache等硬件资源,如图3所示.由于每次系统中断处理的数据包个数、类型不固定(这取决于数据包到达的密集程度和上层应用类型),并且中断触发的时机无法预知,这使得整个网络处理过程局部性较差.研究表明[12],在简单网络环境中网络数据包流呈现一定的“流局部性”,即连续的多个包具有相同的源/目的地址以及相关的栈信息.但在当前高速网络背景下,协议栈处理的时间开销占比已经大大降低,因此局部性带来的性能提升并不明显.与此同时,在一次系统中断内多个连续包处理间有一定的时间局部性,但在多次中断之间的包处理基本不具有时间局部性.更重要的是,高速网络环境下频繁的中断会大大降低处理器和cache的运行效率,导致cache命中率降低并产生大量“污染”(cache pollution).这些问题会大幅降低网络传输效率,同时影响CPU的执行效率.Fig.3 Concurrent program executions between network processing and local programs.图3 网络处理与系统原有程序并发执行本文重点针对上述网络处理过程的局部性和系统交互问题进行了系统优化设计和软件改进.2 网络子系统设计本节介绍了基于改进DCA和cache锁技术的网络子系统相关软硬件协同优化方案.其中包括改进的系统互联结构、DCA策略和一致性协议等,以及应用cache锁优化相关系统软件的具体方案.2.1 系统互联架构由于传统处理器设计中网络子系统被当作是一般I/O系统的一部分,这一定位及相应体系结构设计大大限制了许多网络处理优化技术的效果[13].而本文认为,随着高性能计算和云计算等技术的发展,高速网络子系统设计势必要独立于一般的I/O子系统.因此本文在传统处理器架构的基础上对其网络子系统进行了单独设计,将DCA和cache锁技术融入其中并优化相关协议,使得网络处理效率有效提高,图4给出了改进后的处理器系统互联结构.其中主要有以下2点我们经过了详细的设计:1)采用了网卡内集成技术,并将其连接在CPU与L2cache之间.该结构使得网卡到L2cache的数据传输延迟大为减小,同时提高了网络传输带宽并降低其对I/O控制器的压力.2)采用了两级交叉开关结构的片内互联网络.X1-Xbar连接CPU核中的L1cache和网卡,其内部实现了对来自这2个部件访存请求的缓存和调度功能,重新排列过的访存请求被送至L2cache中.X2-Xbar连接了L2cache、I/O控制器(本文中为HT控制器)和内存控制器,完成3者间的数据传输和通信.Fig.4 Improved system interconnection architecture.图4 改进的系统互连结构为了消除1.2节所述网卡DMA操作对程序局部性和性能的不利影响,本文系统采用了一种改进的DCA技术.由网卡发出的数据访问请求通过X1-Xbar直接送至L2cache,其数据通路如图5所示.地址空间内的一段专用连续地址被预先分配以支持DCA传输,网卡驱动和操作系统内DCA相关内存地址分配会被修改并重定向到该地址段内.数据包由DMA形式发出后,在X1-Xbar内的DCA处理模块中经过地址区分,判断是否为DCA传输,并生成相关传输标记(cache或者uncache).如果是DCA传输,则需对请求进一步拆分(因为内存与cache支持的数据访问长度有所不同),系统将原有请求转换为一个或多个cache支持的连续访存请求.之后新的请求会被送入FIFO缓冲区与CPU请求进行缓存并送往L2cache,这一过程如图5所示.Fig.5 DCA data routing mechanism.图5 DCA数据路由机制与此同时,系统在L2cache中实现了一种简单高效的高速缓存锁机制,关键数据结构和程序段在整个网络处理期间被保存在L2cache中,从而利用其拥有较好的空间局部性这一特点,能够有效提高性能(2.3节).与传统网络优化技术不同,本文组合使用了DCA和cache锁这2项技术并对系统互连结构进行了优化,从而提高处理器cache系统对网络数据传输的支持能力.2.2 改进的直接缓存访问技术直接缓存访问(DCA)是由INTEL公司提出的一种通过将I/O数据直接送入cache进而降低数据传输延迟的一种技术,其从本质上来说与内存至cache的数据预取操作等价.由于传统DCA技术被证明有很大的局限性[13],本文系统利用DCA技术将网卡DMA传输的数据保存在L2cache,并且在以下几个方面对其进行了改进.1)一致性协议.原有DCA技术将数据送至高速缓存后,系统一致性硬件会通过snoop操作[11]将数据同步至内存中,本质上来说系统内的数据传输并没有减少.同时由于传统设计中网卡都是通过I/O控制器连接至系统,因此无法单独针对基于DCA传输优化同步操作.由于本文系统将网卡连接至系统X1-Xbar,这为消除多余的同步操作提供了机会.我们修改了相应硬件的一致性策略,让其只对由X2-Xbar写入的数据(即由HT总线写入的I/O数据)进行一致性同步操作,从而忽略了基于DCA传输的网卡DMA操作.其过程如图6所示:Fig.6 Improved cache coherence model.图6 改进的高速缓存一致性模型2)高速缓存污染.DCA最重要的一个问题就是如何安排传输至cache中的数据.由于cache大小有限(L2cache一般不超过512KB)而I/O数据却很庞大(千兆网卡可以达到900Mbps以上的数据传输),显然将I/O数据全部送入cache中会产生大量“cach e污染”,并急剧降低其性能.因此基于对网络处理行为的详细研究,本文提出将被访问最频繁的DMA描述符链发往L2cache;而对于网络数据包,则由于其数据量太大而选择保存在内存中.尽管数据包中的头信息之后会被频繁地访问,但由于其本身数据量并不大,因此在利用了cache技术后,对其的访问过程仅会产生一次性的cache强制缺失(compulsory miss).2.3 基于Cache锁的优化策略尽管网络数据包处理具有较差的时间局部性,但由于DMA描述符和发送或接受队列地址在整个系统运行期间都是固定的,同时动态分配的skb_buf和包缓冲也都在一定地址范围之内,因此整个网络处理过程的空间局部性比较好.基于这一分析,本文采用了cache锁(cache locking)技术来充分利用程序空间局部性提高性能,同时消除较差时间局部性带来的不利影响.cache锁是现代处理器中支持的一项高级功能[14-15],它能够通过控制cache的替换(evict)过程使得特定cache 块中的数据一直存在于cache中.本文利用这一技术对操作系统(文中为Linux 2.6系统)和驱动中网络相关部分的关键函数和数据结构进行了优化.一方面,在系统中网络中断处理和缓冲区维护这两类开销最大的函数将被锁在cache中,从而加速CPU取指的速度;另一方面,我们重点关注了网卡和CPU频繁访问的DMA描述符、skb_buf、包缓冲这3个数据结构.由于我们采用了DCA技术,DMA描述符完全支持cache访问.考虑到描述符本身并不大,我们将整个描述符链锁在cache中.此外随着现代操作系统“零拷贝”技术[8]的发展,对skb_buf的访问越加频繁,而对包缓冲区访问则相对减少.对于skb_buf和包缓冲区,由于包缓冲中的数据段占存储空间较大,因此我们将其中的头信息(header)部分和skb_buf链锁在cache中,如图7所示.应用cache锁需要注意的一个问题是被锁住数据大小与cache大小之间的关系.显然,当被锁住的数据量太大时会显著地降低cache性能,因此需要适当地对其中数据进行调度.在系统网络压力较低或其他程序有更高需求时应关cache 锁,这就要求相关操作必须以极低的系统开销实现[16].Fig.7 Cache locking scheme for skb_buf.图7 应用于skb_buf的cache 锁策略3 实验与结果分析3.1 实验设计本文实验基于改进的单核GODSON3处理器系统[17],我们对其网络带宽、延迟等性能进行了测试分析.GODSON3处理器是一款由中国科学院计算技术研究所研制的可配置多核处理器,主要定位于高性能计算和高吞吐量服务器应用.实验平台在原有GODSON3处理器基础上实现了本文提出的改进网络子系统,芯片内部集成一个64bMIPS架构GS464处理器核,核内实现指令4发射和9级动态流水.一个Synopsys公司的千兆以太网控制器(GMAC)同时集成在处理器内[18].实验平台的具体参数如表1所示:Table 1 Experiment Platform Parameters表1 实验平台相关参数Unit Frequency & Organization CPU 800MHz 4issues Cache 4ways 64KB+64KB L1cache 4ways 512KB L2cache Memory 250MHz,DDR2,1GB Bus 800MHz 128bAXI 200MHz 16bHT1.0 Software Linux 2.6.21 Netperf,Iperf,Ping NIC Synopsys GMAC(proposed)RTL8169Giga Ethernet(conv.)实验采用对比测试方法,即在同一实验平台上分别基于传统方式和本文改进系统运行测试程序并比较性能.传统系统实现如图4所示,利用GODSON3处理器内部HT总线连接外部桥片,并通过桥片内的PCI总线连接一个RTL8169千兆以太网卡进而连接外部以太网络.处理器通过内部总线、I/O子系统与网卡设备进行交互.实验采用了 Netperf[19],Iperf[20]和Ping等领域标准测试工具作为系统网络性能的测试程序,其中重点研究了性能与测试数据包大小、缓冲区大小和不同协议间的关系.同时考虑到真实的应用场景,本文还研究了网络处理与其他程序间的相互影响.实验通过在系统中同时运行网络测试和SPEC2000测试程序集,进而观察其性能变化并得出相关结论.1个DELL 2.6GHz 4核服务器作为网络数据包发送端与待测系统通过千兆以太网络(1GbE)直接相连.3.2 结果分析1)TCP带宽图8给出了Netperf测试基于不同数据包大小的系统TCP传输带宽峰值.可以看出基于本文提出的优化方案,系统带宽平均提升47.9%.另外随着数据包大小的增加,系统传输带宽并没有随之增加,这与文献[2]中的结论有所不同.我们分析认为,一方面由于优化方案大幅减少了中断、缓冲区维护等每包传输开销(per -packet cost),这使得系统面对频繁的小数据包处理仍能够保持较高的效率;另一方面,因为本文方案对包内数据负载的传输优化较少,因此随着包数据增大,其他部分优化所带来的收益占比在降低,这在一定程度上抵消了批量数据传输带来的效率提升.Fig.8 TCP bandwidth.图8 TCP传输带宽2)UDP丢包与保证连接的TCP传输不同,基于UDP协议的传输更关注于网络的拥塞和延迟情况.我们使用Iperf测量了在不同发送带宽压力下的基于UDP协议传输的系统丢包情况,结果如图9所示.可以看出当测试压力较小时,本文提出的优化方案效果并不明显;当发送数据量大于待测系统处理能力时,传统网络处理系统性能显著下降,丢包率大幅上升,而优化过的系统情况则好的多.当发送数据带宽达到900Mbps时,未经优化系统丢包率达到近80%,而优化后的系统丢包率略高于40%.这主要因为一方面本文利用了cache锁将重要的指令和数据保存在缓存中,这样大大降低了由于高测试压力下频繁中断处理带来的访存停顿和cache反复替换;另一方面,改进DCA和cache锁提高了网络处理效率,这使得本文提出的改进系统在较大传输压力下表现较传统系统更好.Fig.9 UDP loss rates under different network bandwidths.图9 不同带宽压力下的UDP丢包率3)延迟与TCP/UDP事务率图10给出了其他测试结果,具体包括:单线程和双线程的TCP传输带宽、UDP传输带宽、TCP/UDP RR和ping测试.可以看到,双线程的TCP传输(Iperf-TBP2)性能提高大幅高于单线程传输(Iperf-TB),这证明了本文所提出优化方案改进了多数据包(多线程)网络传输处理局部性.同时可以看出,本文系统基于TCP协议处理的性能提高要好于基于UDP协议的程序.这说明更为复杂的TCP协议处理对关键数据结构的访问更加频繁,并且局部性也更差,因此本文优化方案效果也更加明显.Ping测试显示出该方案也在一定程度上降低了网络传输延迟.Fig.10 Results of other network benchmarks.图10 其他网络测试结果3.3 多程序并行与系统交互为了评估实际系统中网络处理与其他程序并行执行的情景,我们在基于本文网络加速方案的待测系统上并行运行SPEC2000测试和Netperf-TCP测试,并通过分组分析SPEC程序运行时间变化和系统网络带宽来评估在真实多线程环境下本文方案对网络传输性能和局部性的改善以及对本地程序和操作系统的影响.我们选取了SPEC2000中4个定点和4个浮点测试在train数据集2线程条件下分别与包大小1 024B的TCP测试并行执行,结果如图11所示.可以看出基于本文方案系统的TCP传输带宽(TcpBDCL)比基于传统系统TCP传输带宽(TcpBD-NCL)平均高出44.67%,同时SPEC程序的运行时间(SEPC-CL)较不启用cache锁情况(SPEC-NCL)几乎没有增加.在系统CPU占用率100%的情况下,网络带宽大幅提升,说明本文方案对多网络数据包间处理局部性及系统交互效率改进很大.同时尽管应用于网络处理的cache锁策略一定程度上减少了SPEC程序可用cache大小,但其运行时间并未增加且略为较少,这进一步证明本文方案改进了系统整体cache命中率,降低了系统频繁中断及上下文切换(context switch)造成的交互开销.Fig.11 Performance evaluation between network processing andSPEC2000 testsuit.图11 网络处理与SPEC2000测试并发执行下的性能评测4 讨论由于现实系统中多种网络优化技术经常同时存在并共同作用,本节专门讨论了文中网络优化方案与其他主要优化方法的协同工作策略.图12给出了硬件角度分析的网络处理流程.可以看到本文方案将传统网络处理数据通路上的5个硬件部件(网卡、桥片、内存、cache和CPU)基本简化为3个部件(网卡、cache、CPU).显然,系统网络若达到最大传输带宽,当且仅当相关各部分硬件间数据传输带宽相等,即达到平衡系统.但由于不同部件的结构特性和制造工艺不同,这一目标往往难以达到.因此本文优化方案有效降低了网络系统复杂度,并为其他优化提供了机会.Fig.12 Interactions among different network related hardware units.图12 网络处理相关硬件交互关系我们根据网络处理所涉及的硬件模块提出一个多网络优化方案协同工作的基本原则:多个网络优化方案共同作用时,每个方案所涉及的硬件部件应尽量避免重叠.显然,作用于某一硬件的优化技术带来的性能提升必将降低其他方案的效果,同时多个部件传输带宽应保持平衡.根据该原则我们讨论了本文方案与其他主要优化技术共同作用的策略和效果,包括数据预取、TCP Offload、中断聚集(interrupts coalescing)和TSO/LRO等方案.1)数据预取数据预取这一技术通常在2个方面应用于网络数据处理.一方面在数据包传输阶段,可以利用其完成高速缓存与内存间的数据预取,这与DCA的本质是相同的.但传统预取方案由于其无法避免第1次缓存缺失的开销,且容易产生“过度预取”现象,故其在效率上远远低于DCA[21].此外,可以利用预取技术高效完成数据包在不同缓冲区间的内存拷贝,这在系统没有专用拷贝引擎的情况下能够有效提高数据传输性能.因此在本文优化方案的基础上,适当利用预取提高数据拷贝速度有助于网络整体性能的提高.2)TCP OffloadTCP Offload技术曾经被认为能够显著提高网络性能,但随着高速网络的发展,其渐渐被证明效率低下并具有很多缺陷[22].该技术通过专用硬件模块对TCP协议栈处理和校验码计算进行加速,前者一般需要系统集成相应硬件,而后者在现代网卡中一般得到支持.本文方案由于利用cache锁将协议栈频繁访问的数据包头信息保存在了cache中,加快了包括TCP在内的协议栈处理速度,因此TCP Offload与本文方案共用时效果会有所减弱.但由于包数据传输没有进行专门优化,所以校验码计算仍需要网卡中的校验码计算Offload功能支持.3)中断聚集与TSO/LRO。

一种掉电不丢失内存数据的系统设计方法[发明专利]

专利名称:一种掉电不丢失内存数据的系统设计方法专利类型:发明专利

发明人:庞潇

申请号:CN201710304321.4

申请日:20170503

公开号:CN107133126A

公开日:

20170905

专利内容由知识产权出版社提供

摘要:本发明特别涉及一种掉电不丢失内存数据的系统设计方法。

该掉电不丢失内存数据的系统设计方法,在普通主板的基础上,加入一个电容模块,搭配DRAM颗粒和flash颗粒结合的NVDIMM 内存,相比之前每条NVDIMM单独搭配一个电容模块,大大节省了系统的空间,可以搭配使用任意数量甚至满配的NVDIMM,充分利用NVDIMM掉电不丢失的价值,保护了系统的数据安全,给目前的硬件应用领域添加了新的活力。

申请人:郑州云海信息技术有限公司

地址:450000 河南省郑州市郑东新区心怡路278号16层1601室

国籍:CN

代理机构:济南信达专利事务所有限公司

代理人:姜明

更多信息请下载全文后查看。

2021年宁夏理工学院软件工程专业《计算机组成原理》科目期末试卷B(有答案)

2021年宁夏理工学院软件工程专业《计算机组成原理》科目期末试卷B(有答案)一、选择题1、某一计算机采用主存Cache存储层次结构,主存容量有8个块,Cache容量有4个块,采取直接映射方式。

若主存块地址流为0,1,2,5,4,6,4,7,1,2,4,1,3,7,2,一开始Cache为空,此期间Cache的命中率为()。

A.13.3%B.20%C.26.7%D.33.3%2、采用指令Cache与数据Cache分离的主要目的是()。

A.降低Cache的缺失损失B.提高Cache的命中率C.降低CPU平均访存时间D.减少指令流水线资源冲突3、某数采用IEEE754标准中的单精度浮点数格式表示为C6400000H,则该数的值是()。

A.-1.5×213B.-1.5×212C.-0.5×213D.-0.5×2124、在C语言程序中,下列表达式中值为True的有()。

I.123456789=(int)(float)l23456789Ⅱ.123456==(int)(float)1234561Ⅲ.123456789-(int(double)123456789A.仅I、ⅡB. 仅I、ⅢC.仅Ⅱ、ⅢD. I、Ⅱ、Ⅲ、5、十进制数-0.3125的8位移码编码为()。

A.D8HB.58HC.A8HD.28H6、假设某存储器总线采用同步通信方式,时钟频率为50MHz,每个总线事务以突发方式传输8个字,以支持块长为8个字的Cache行读和Cache行写,每字4B.对于读操作,方式顺序是1个时钟周期接收地址,3个时钟周期等待存储器读数,8个时钟周期用于传输8个字。

请问若全部访问都为读操作,该存储器的数据传输速率为()。

A.114.3MB/sB.126.0MB/sC.133.3MB/sD.144.3MB/s7、在异步通信方式中,一个总线传输周期的过程是()。

A.先传送数据,再传送地址B.先传送地址,再传送数据C.只传输数据D.无法确定8、指令寄存器的位数取决()。

面向机器学习的高性能SIMT处理器cache的设计与实现

面向机器学习的高性能SIMT处理器cache的设计与实现Xu Xiaoyan;Li Tao;Sun Zhe;Xing Lidong【摘要】为了满足机器学习中大数据、并行计算及降低处理器与主存之间的差距等要求,设计基于自主研发的SIMT处理器的流水线cache结构.依据局部性原理与LRU替换算法相结合设计专用的伪LRU替换算法,与通用的轮询、LFU、LRU替换算法共同完成cache替换算法的可配置要求,实现处理器与主存之间的快速交互.采用Xilinx公司virtex ultrascale系列的xcvu440-flga2892-2-e FPGA芯片对设计进行综合.结果表明该结构指令cache最大时延为2.923 ns,数据cache最大时延为3.258 ns,满足SIMT处理器性能要求.【期刊名称】《计算机应用与软件》【年(卷),期】2019(036)007【总页数】6页(P282-286,333)【关键词】SIMT处理器;流水线cache结构;替换算法【作者】Xu Xiaoyan;Li Tao;Sun Zhe;Xing Lidong【作者单位】;;;【正文语种】中文【中图分类】TP3330 引言随着大数据时代的到来,机器学习已经应用到人类生活的各个方面。

机器学习的本质是基于互联网的海量数据以及系统强大的并行运算能力,让机器自主模拟人类学习的过程,通过不断“学习”数据来做出智能决策行为[1]。

为了解决机器学习中大数据、并行运算需求,本文基于SIMT架构进行设计。

SIMT概念首先被GPU制造商NVIDIA在产品微架构中提出[2]。

2006年11月,NVIDIA在其Tesla GPU架构中提出了一条指令同时驱动多个不相关线程的SIMT处理方式[3]。

随后不久,ATI公司在2007年推出了采用类似处理架构的TeraScale引擎,及相关产品R600 GPU芯片[4]。

SIMT架构具有多个执行流程[3],可以利用多线程隐藏存储延时,减少取指、取数开销,而且执行时不需要将数据凑成合适的矢量长度,便可以进行运算,更有利于适应机器学习处理大规模数据的要求。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

ma i n t e n a n c e . S o 。 i n o r d e r t o r e d u c e t h e c o mp u t e r s y s t e m d e p l o y me n t , ma n a g e me n t a n d t h e ma i n t e n a n c e c o s t , a n d i n c r e a s e t h e d e p l o y me n t d e n s i t y ,t h e e n e r y g s a v i n g r e g u l a t i o n o f c o mp u t e r i s t h e k e y p r o b l e m t o s o l v e a t p r e s e n t . Ai me d a t t h e f r e q u e n c y o f me mo r y a c c e s s i n t h e

摘要 : 近年来 , 世界 的能源危机越 来越严重 , 节能减排是 当下世界关注 的焦点。计 算机 系统作 为 当今社会广泛使用的技术 , 也针 对 能源危机提 出了绿 色 计 算以及效 能计 算的研 究方向。 随着处理器处理能力的逐步提 高, 计算机的功耗也飞速增 大。 这加剧 了计算机 系统部 署的难度 , 增加 了运行与维护成本。 因此为 了降低 计算机 系统的部 署、 管理以及维护成本, 同时提 高部署密度 , 对计算机进行节

o p e r a t i o n p r o c e s s o f a p p l i c a t i o n p r o g r a m,t h i s p a p e r p u s f o wa r r d t h e e n e r g y s a v i n g s y s t e m s o f t w a r e C a c h e— O n d e ma n d wh i c h i s t a k e s t h e

Va l ue Eng i ne e r i ng

・2 4 9・

基 于处 理 器 访 存 缺 失 率 的节 能 软 件 设 计 与 实现

De s i g n a nd I m pl e me nt a t i o n o f t he Ene r g y S av i ng So f t wa r e Ba s e d on t he Fe t c hi ng Lo s s Ra t e o f t he Pr oc e s s o r

t h e p r e s e n t w o r l d . As t h e w i d e l y u s e d t e c h n o l o y g i n t h e p r e s e n t s o c i e t y , c o mp u t e r s y s t e m p u t s f o r w a r d t h e r e s e a r c h d i r e c t i o n s o f g r e e n a n d

袁 海 彦 YU AN Ha i - y a n

( 江 苏林 海雅 马 哈摩 托 有 限公 司 , 泰州2 2 5 3 0 0 )

( J i a n g s u L i n h a i Y a m a h a Mo t o r o u 2 2 5 3 0 0 , C h i n a )

c o mp u t e r s a l s o i n c r e a s e d r a p i d l y .I t a g g r a v a t e s t h e d i ic f u l t y o f t h e c o mp u t e r s y s t e m d e p l o y me n t ,i n c r e a s e s t h e c o s t s o f o p e r a t i o n a n d

Ab s t r a c t :I n r e c e n t y e a r s , t h e wo r l d e n e r g y c r i s i s i s mo r e a n d mo r e s e r i o u s , e n e r y g c o n s e r v a t i o n a n d e mi s s i o n s r e d u c t i o n i s t h e f o c u s o f

能调节是 当前需要解 决的关键 问题 。本文针对应用程序运行 过程 中内存访 问的频率 , 提 出以缓存访 问缺失率为节能调节的依据的节 能 系统软件 C a c h e — O n d e m a n d , 使计算机 系统在任 务 负载 1 0 0 %时 , 仍可 以进行节能调节 , 增 大节能空间。通过在 实际平 台的 实现与对 比实验 , 结果表 明, C a c h e — O n d e ma n d系统在保证 7 %性 能损失 的前提下 , 达到了 2 8 %的节能效果 , 具有理论与 实际应用价值

p e fo r r ma n c e c a l c u l a t i o n a i me d a t t h e e n e r g y c i r s i s .W i t h t h e g r a d u a l i mp r o v e me n t o f t h e p r o c e s s i n g a b i l i t y ,t h e p o w e r c o n s u mp t i o n o f