微机原理与接口技术习题答案5章(供参考)

微机原理与接口技术(第三版)课本习题答案

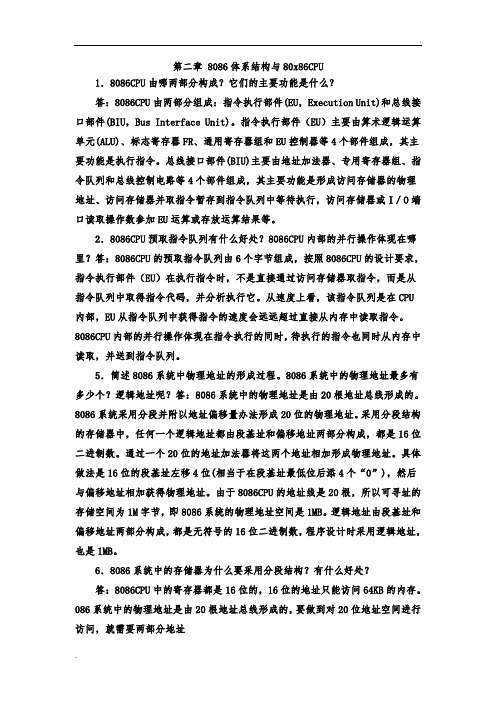

第二章 8086体系结构与80x86CPU1.8086CPU由哪两部分构成?它们的主要功能是什么?答:8086CPU由两部分组成:指令执行部件(EU,Execution Unit)和总线接口部件(BIU,Bus Interface Unit)。

指令执行部件(EU)主要由算术逻辑运算单元(ALU)、标志寄存器FR、通用寄存器组和EU控制器等4个部件组成,其主要功能是执行指令。

总线接口部件(BIU)主要由地址加法器、专用寄存器组、指令队列和总线控制电路等4个部件组成,其主要功能是形成访问存储器的物理地址、访问存储器并取指令暂存到指令队列中等待执行,访问存储器或I/O端口读取操作数参加EU运算或存放运算结果等。

2.8086CPU预取指令队列有什么好处?8086CPU内部的并行操作体现在哪里?答:8086CPU的预取指令队列由6个字节组成,按照8086CPU的设计要求,指令执行部件(EU)在执行指令时,不是直接通过访问存储器取指令,而是从指令队列中取得指令代码,并分析执行它。

从速度上看,该指令队列是在CPU内部,EU从指令队列中获得指令的速度会远远超过直接从内存中读取指令。

8086CPU内部的并行操作体现在指令执行的同时,待执行的指令也同时从内存中读取,并送到指令队列。

5.简述8086系统中物理地址的形成过程。

8086系统中的物理地址最多有多少个?逻辑地址呢?答:8086系统中的物理地址是由20根地址总线形成的。

8086系统采用分段并附以地址偏移量办法形成20位的物理地址。

采用分段结构的存储器中,任何一个逻辑地址都由段基址和偏移地址两部分构成,都是16位二进制数。

通过一个20位的地址加法器将这两个地址相加形成物理地址。

具体做法是16位的段基址左移4位(相当于在段基址最低位后添4个“0”),然后与偏移地址相加获得物理地址。

由于8086CPU的地址线是20根,所以可寻址的存储空间为1M字节,即8086系统的物理地址空间是1MB。

微机原理与接口技术复习5--7章及答案

判断题1.EPROM是指可擦除可编程随机读写存储器。

2.在查询方式下输入输出时,在I/O接口中设有状态寄存器,通过它来确定I/O设备是否准备好。

输入时,准备好表示已满;输出时,准备好表示已空。

3.无条件式的I/O是按先读状态口,再读数据口的顺序传送数据的。

4.I/O数据缓冲器主要用于协调CPU与外设在速度上的差异。

5.查询式输入输出是按先读状态端口,后读/写数据端口的顺序传送数据的。

6.连接CPU和外设的接口电路中必须要有状态端口。

7.总线是专门用于完成数据传送的一组信号线。

8.I/O接口的基本功能之一是完成数据的缓冲。

9.要实现微机与慢速外设间的数据传送,只能利用查询方式完成。

1) Y 2 ) Y3) Y4) Y 5) Y6) X 7) X 8)Y9) X1.单片8259A最多可接8个中断源。

2.在可屏蔽中断的嵌套原则中,不允许低级中断打断高级中断,但允许同级中断相互打断。

3.同一片8259的8个中断源的中断向量在中断向量表中可以不连续存放。

(不要求)4.利用8259A对外中断进行管理时,只能管理8个中断源。

5.在中断接口电路中,由中断请求寄存器来保存外设的中断请求信号。

6.8259A送给CPU的中断请求信号是通过INT发出的。

1Y 2X 3X 4X 5Y 6Y填空题1、在微机系统中,端口编址方式一般有___________和___________两种方式。

2、微机系统与外设间的信息交换方式有————、————、————和————.3.用2K×8的SRAM芯片组成32K×16的存储器,共需SRAM芯片()片。

4.为保证动态RAM中的内容不消失,需要进行( ) 操作。

5.构成64K*8的存储系统,需8K*1的芯片( )片。

1、统一编址,独立编址2、无条件,查询,中断,DMA3、324、定时刷新5、646、8086和8088的地址总线有()根,能寻址()MB的存储器空间。

7.8086CPU从偶地址中按字节读时,存储器数据进入数据总线的( ) ;从奇地址按字节读时,进入数据总线的( )。

微机原理与接口技术习题答案2011..

2. 选择题 (3) 在8086最小方式的读操作时序中,外界

将要输入的数据送上AD线时,在D 的前沿 ,此数据被采样送入CPU。 A. T1 B. T2 C. T3 D. T4

3

(4)逻8辑03地86址有三线种性存地储址地址物空理间地,址它们

是

, 和分段 ,这三种分地页址是

的是 C 。

A. 地址总线B. 数据总线C. 控制总线D. 以上都不对

(5) 通常计算机系统中的外围设备是指 A 。

A. 外存储器、输入设备及输出设备 B. 外存储器、输

入设备 C. 外存储器、输出设备 D. 输入设备、输

出设备

3. 判断题 (1) 计算机中的运算器、控制器和内存储器合称为中

央处理机。 ( × )

由全速总线同CPU内核相连。 (√)

7

4. 简答题

(4) 80386CPU如何从逻辑地址得到线性地址?如何从线性地 址得到物理地址? 答:在保护方式下,Pentium对存储器的组织管理采用两级 存储器管理的策略,即所谓的分段管理和分页管理,分别由 Pentium中的分段部件SU和分页部件PU完成。 分段部件接收到逻辑地址后,根据段选择子的表指示器TI的 值选择全局描述符表(GDT)还是局部描述符表(LDT), 当TI=0时选中GDT,TI=1时选中LDT。选择完描述符表后, 通过段选择子高13位的索引从被选中的描述符表中找出相应 的8个字节的段描述符,从中取出32位段基址(B31~B0) ,32位的段基地址与32位的偏移地址相加后就得到了32位的 线性地址,从而完成了分段部件SU的主要任务。

8

分页部件PU用页目录表和页表实现两级地址转换。 高一级的页目录表中,每一项为一个页目录描述符, 包括了下一级页表的信息,对应于一个页表。低一级 是页表,每一项对应物理存储器中的一页。 控制寄存器中的CR3为页目录表基地址寄存器,用来 保存页目录表在存储器中的物理起始地址。DIR作为 页目录索引从4KB的页目录表中选取一个页目录描述 符(占4个字节, ①页目录描述符所在地址为页目录 索引乘以4与页目录表基地址CR3相加得到),② PAGE作为页表索引从页表中选取一个页描述符(同 样,页描述符所在地址为页表索引乘以4再与页表基 地址相加得到),③而页内偏移量则作为页内的偏移 地址与页描述符提供的页基地址相加产生存储器单元 的32位物理地址。

微机原理和接口技术(第三版)课本习题答案解析

第二章 8086 体系结构与80x86CPU1.8086CPU 由哪两部份构成?它们的主要功能是什么?答:8086CPU 由两部份组成:指令执行部件<EU,Execution Unit>和总线接口部件<BIU,Bus Interface Unit>。

指令执行部件〔EU 主要由算术逻辑运算单元<ALU>、标志寄存器F R、通用寄存器组和E U 控制器等4个部件组成,其主要功能是执行指令。

总线接口部件<BIU>主要由地址加法器、专用寄存器组、指令队列和总线控制电路等4个部件组成,其主要功能是形成访问存储器的物理地址、访问存储器并取指令暂存到指令队列中等待执行,访问存储器或者I/O 端口读取操作数参加E U 运算或者存放运算结果等。

2.8086CPU 预取指令队列有什么好处? 8086CPU 内部的并行操作体现在哪里?答: 8086CPU 的预取指令队列由6个字节组成,按照8086CPU 的设计要求, 指令执行部件〔EU 在执行指令时,不是直接通过访问存储器取指令,而是从指令队列中取得指令代码,并分析执行它。

从速度上看,该指令队列是在C PU 内部,EU 从指令队列中获得指令的速度会远远超过直接从内存中读取指令。

8086CPU 内部的并行操作体现在指令执行的同时,待执行的指令也同时从内存中读取,并送到指令队列。

5.简述8086 系统中物理地址的形成过程。

8086 系统中的物理地址最多有多少个?逻辑地址呢?答: 8086 系统中的物理地址是由20 根地址总线形成的。

8086 系统采用分段并附以地址偏移量办法形成20 位的物理地址。

采用分段结构的存储器中,任何一个逻辑地址都由段基址和偏移地址两部份构成,都是16 位二进制数。

通过一个20 位的地址加法器将这两个地址相加形成物理地址。

具体做法是16 位的段基址左移4位<相当于在段基址最低位后添4个"0">,然后与偏移地址相加获得物理地址。

微机原理与接口技术 第5章课后作业答案

4

D0~ D7 8088系统 BUS

D0~ D7 · · · A0 SRAM 6116

A0 A 10

MEMW

A 10

R/W OE D0~ D7 CS

MEMR

D0~ D7 A0 · · ·

A0 A 10 R/W OE CS

A 10

MEMW MEMR & A 18 A 17 A 19 A 16 A 15 A 14 A 13 A 12 A 11

5.10 74LS138译码器的接线图如教材第245页的图5-47所示,试判断其输出端Y0#、Y3#、Y5#和 Y7#所决定的内存地址范围。

解:因为是部分地址译码(A17不参加译码),故每个译码输出对应2个地址范围: Y0#:00000H ~ 01FFFH 和 20000H ~ 21FFFH Y3#:06000H ~ 07FFFH 和 26000H ~ 27FFFH

5.2 为什么动态RAM需要定时刷新?

解:DRAM的存储元以电容来存储信息,由于存在漏电现象,电容中存储的电荷会逐渐泄漏,从而使信息丢失或出 现错误。因此需要对这些电容定时进行“刷新”。 5.3 CPU寻址内存的能力最基本的因素取决于___________。 解:地址总线的宽度。 5.4 试利用全地址译码将6264芯片接到8088系统总线上,使其所占地址范围为32000H~33FFFH。 解:将地址范围展开成二进制形式如下图所示。 0011 0010 0000 0000 0000 0011 0011 1111 1111 1111

解:

(1)特点是:它结合了RAM和ROM的优点,读写速度接近于RAM,断电后信息又不会丢失。 (2)28F040的编程过程详见教材第222~223页。 5.14 什么是Cache?它能够极大地提高计算机的处理能力是基于什么原理? 解: (1)Cache 是位于CPU与主存之间的高速小容量存储器。 (2)它能够极大地提高计算机的处理能力,是基于程序和数据访问的局部性原理。 5.15 若主存DRAM的的存取周期为70ns,Cache的存取周期为5ns,有它们构成的存储器的平 均存取周期是多少? 解:平均存取周期约为 70×0.1ns + 5×0.9ns =11.5ns。

微机原理课后习题答案第五章习题答案

5.10为什么输人接口的数据缓冲寄存器必须有三态输出功能,而输出接口却不需要?解:输人接口的数据缓冲寄存器的谕出端是直接接在数据总线上的,如果数据寄存器没有三态输出功能,则无论数据寄存器被寻中还是未被寻中,其数据都会被送上数据总线,若此时总线上真正要传送的数据与该输人缓存器的内容不一致时,就会发生总线冲突。

所以输人接口的数据缓冲寄存器必须有三态输出功能,以便接口未被寻中时,其输出端处于高阻态而与总线隔离。

对于输出接口来说,其输人端与数据总线相连,而输出端与外设相连,因此其输出不影响总线状态;并且外设一般只与一个输出数据缓存器相连,所以输出接口的数据缓存器无需三态输出功能。

5.11已知PC 机系统中某接口板的I/O 端口译码电路如图5.4所示,试分析出各I/O 端 口和I/O 芯片的端口地址或地址范围。

解:74LS138使能信号12B G G 、的逻辑表达式为:19G A =27654B G A A A A = 即仅当9754A A A A = 11111时,使能信号1G = 1, 2B G = 0有效。

此时,若328A A A = 000, 0Y =0; 328A A A =001, 1Y =0; 328A A A =111, 7Y = 0;所以,各I/O 芯片的地址范围为: I/O 芯片1:1111110000B —11111100113B 即3F0H 一3F3H;I/O 芯片2: l011110100B--1011110111.即2F4H 一2F7H;I/O 芯片3:1111111100B 一11111111113,即3FCH 一3FFH0Y 译出的地址范围2F0H~2F3H 再经一级74LS139译码器对1A 和0A 进行二次译码。

分 别得到4个读端口和4个写端口。

各I/O 端口的地址为:输出口1和输人口1为2F0H ;输出口2和输入口2为2F1H;输出门3和输入口3为2F2H;输出口4和输入口4为2F3H5.12已知PC.机系统中某接口板的板地址译码电路如图5.5所示。

微机原理与接口技术习题答案(供参考)

源操作数:直接寻址;目的操作数:寄存器寻址

⑸ MOV [BX+SI+8], BX

源操作数:寄存器寻址;目的操作数:基址加变址寻址

2.若AX=0ABCDH,BX=7F8FH,CF=1。求分别执行8086 CPU指令

⑴ ADDAX,BX⑵ ADCAX,BX

⑶ SBBAX,BX⑷ NEGAX

00110010

+01010100

10000110

由于Cs=0,Cp=1,所以有溢出,结果错误

4.请写出下列字符串的ASCII码值。

My name is Zhang san.

4D 79 6E 61 6D 65 69 735A68 61 6E 67 73 61 6E 2E

第2章 80X86微机系统

习题与思考题

DAA

之后,AL=?、标志AF=?、CF=?

⑵ 若执行指令 SUB AL,BL与DAS后,AL=?、标志AF=?、CF=?

解答

⑴ AL=65H, AF=1, CF=1。

⑵ AL=91H, AF=0, CF=1。

4.指出下列指令中哪些是错误的,并指出错在何处?

⑴ MOV DL,[DX]⑵ MOV ES,2000H

MOV AH, 4CH

MOV 21H

CODE ENDS

END BEG

3.对一个给定的N数据,用冒泡排序法进行排序。

解答:.486

Data segment

Buf db‘abcd18437hj’

Lens equ $-buf

Count db lens

Flag db ?

Data ends

Code segment

⑸ AND AX,BX⑹ ORAX,BX

微机原理与接口技术-习题参考答案

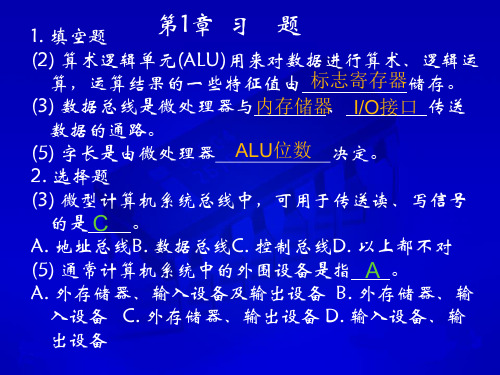

第1章习题答案1.答:计算机硬件的基本组成部分有:运算器、控制器、存储器、输入设备和输出设备五大组成部分;运算器功能:完成各种算术运算或逻辑运算;控制器功能:发出各种控制信息,使计算机各部件协调工作;存储器功能:存储程序和数据;输入设备:将程序和数据输入的部件;输出设备:将结果数据输出的部件。

2.答:以微型计算机为核心,配以鼠标、键盘等外围设备、电源、接口电路,以及控制计算机工作的软件构成微型计算机系统。

3.答:主板与外部设备之间的数据传输必须通过系统总线,所以系统总线包含的信号线必须满足下列各种输入/输出操作的需要:①访问分布于主板之外的存储器;②访问I/O接口;③适应外部中断方式;④适应存储器直接与外部设备交换信息。

总线控制逻辑的任务就是产生和接受这些操作所需要的信号。

4.答:计算机有运算器、控制器、存储器、输入设备和输出设备五大部分组成,计算机内部采用二进制数据的格式表示数据和指令。

程序将事先保存在内存储器中,计算机在工作时,不需要操作人员干预,自动逐条取出指令并执行。

5.答:CPU首先执行主板上BIOS中的自检程序;执行引导装入程序,依次搜寻硬盘、光盘等;读出引导记录,装入引导程序;由引导程序将操作系统装入内存;执行操作系统。

6.答:BIOS是Basic Input Output System的缩写,指的是基本输入输出系统"。

它是一组固化到计算机ROM芯片上的程序,保存着计算机最重要的基本输入输出的程序、系统设置信息、开机后自检程序和系统自启动程序。

7.答:略。

2第3章习题答案1.(1)答:物理地址:物理地址(PA)是20位无符号二进制数,是CPU访问存储器的实际地址。

每个存储单元对应一个物理地址。

8086存储空间的物理地址范围是:00000H~FFFFFH。

逻辑地址:采用分段结构的存储器中,把通过段地址和偏移地址来表示的存储单元的地址称为逻辑地址,记为:段地址:偏移地址。

段地址:8086规定各逻辑段从节的整数边界开始,即段首地址二进制值的低4位是0000,把段首地址的高16位称为段基址或段地址。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第5章 总线及其形成

1. 微处理器的外部结构表现为 数量有限的输入输出引脚 ,它们构成了微处理器级总线。

2. 微处理器级总线经过形成电路之后形成了 系统级总线 。

3. 简述总线的定义及在计算机系统中采用标准化总线的优点。

答:总线是计算机系统中模块(或子系统)之间传输数据、地址和控制信号的公共通道,

它是一组公用导线,是计算机系统的重要组成部分。

采用标准化总线的优点是:

1) 简化软、硬件设计。

2) 简化系统结构。

3) 易于系统扩展。

4) 便于系统更新。

5) 便于调试和维修。

4. 在微型计算机应用系统中,按功能层次可以把总线分成哪几类。

答:在微型计算机应用系统中,按功能层次可以把总线分成:片内总线、元件级总线、

系统总线和通信总线。

5. 简述RESET 信号的有效形式和系统复位后的启动地址。

答:RESET 为系统复位信号,高电平有效,其有效信号至少要保持四个时钟周期,且复

位信号上升沿要与CLK 下降沿同步。

系统复位后的启动地址为0FFFF0H 。

即:(CS )=0FFFFH ,(IP )=0000H 。

6. 8086 CPU 的IO M/信号在访问存储器时为 高 电平,访问I/O 端口时为 低 电平。

7. 在8086系统总线结构中,为什么要有地址锁存器?

答:8086CPU 有20条地址线和16条数据线,为了减少引脚,采用了分时复用,共占了

20条引脚。

这20条引脚在总线周期的T1状态输出地址。

为了使地址信息在总线周期的其

他T 状态仍保持有效,总线控制逻辑必须有一个地址锁存器,把T1状态输出的20位地址信

息进行锁存。

8. 根据传送信息的种类不同,系统总线分为 数据总线 、 地址总线 和 控制总线 。

9. 三态逻辑电路输出信号的三个状态是 高电平 、 低电平 和 高阻态 。

10. 在8086的基本读总线周期中,在1T 状态开始输出有效的ALE 信号;在2T 状态开始输出

低电平的RD 信号,相应的DEN 为__低__电平,R DT/为__低__电平;引脚AD 15 ~ AD 0

上在1T 状态期间给出地址信息,在4T 状态完成数据的读入。

11. 利用常用芯片74LS373构成8086系统的地址总线, 74LS245作为总线收发器构成数

据总线,画出8086最小方式系统总线形成电路。

答:8086最小方式系统总线形成电路如图5.1所示。

图5.1 8086最小方式系统总线形成电路

12. 微机中的控制总线提供 H 。

A. 数据信号流;

B. 存储器和I/O 设备的地址码;

C. 所有存储器和I/O 设备的时序信号;

D. 所有存储器和I/O 设备的控制信号;

E. 来自存储器和I/O 设备的响应信号;

F. 上述各项;

G. 上述C ,D 两项;

H.上述C,D和E三项。

13.微机中读写控制信号的作用是 E 。

A.决定数据总线上数据流的方向;

B.控制存储器操作读/写的类型;

C.控制流入、流出存储器信息的方向;

D.控制流入、流出I/O端口信息的方向;

E.以上所有。

14.8086 CPU工作在最大方式,引脚MX

MN/应接__地__。

15.RESET信号在至少保持4个时钟周期的高电平时才有效,该信号结束后,CPU内部

的CS为 0FFFFH ,IP为 0000H ,程序从 0FFFF0H 地址开始执行。

16.在构成8086最小系统总线时,地址锁存器74LS373的选通信号G应接CPU的 ALE 信

号,输出允许端OE应接地;数据收发器74LS245的方向控制端DIR应接DI/信号,输出允许端E应接DEN信号。

R

17.8086 CPU在读写一个字节时,只需要使用16条数据线中的8条,在一个总线周期

内完成;在读写一个字时,自然要用到16条数据线,当字的存储对准时,可在一个总线周期内完成;当字的存储为未对准时,则要在两个总线周期内完成。

T状态开始检查READY信号,__高_电平时有效,说明存储器或I/O端口准18.CPU在

3

备就绪,下一个时钟周期可进行数据的读写;否则,CPU可自动插入一个或几个等待周期(T W),以延长总线周期,从而保证快速的CPU与慢速的存储器或I/O端口之间协调地进行数据传送。

19.8086最大系统的系统总线结构较最小系统的系统总线结构多一个芯片 8288总线控制

器_。

20.微机在执行指令 MOV [DI],AL时,将送出的有效信号有 B C 。

M/信号 C.WR D.RD

A.RESET B.高电平的IO

21.设指令MOV AX,DATA 已被取到CPU的指令队列中准备执行,并假定DATA为偶地址,

试画出下列情况该指令执行的总线时序图:

(1)没有等待的8086最小方式;

(2)有一个等待周期的8086最小方式。

答:(1)没有等待的8086最小方式时序如图5.2所示。

图5.2 没有等待的8086最小方式时序(2)有一个等待周期的8086最小方式时序图如图5.3所示。

图5.3有一个等待周期的8086最小方式时序图

22.上题中如果指令分别为:

(1)MOV DA TA+1,AX

(2)MOV DA TA+1,AL

(3)OUT DX,AX (DX的内容为偶数)

(4)IN AL,0F5H

重做上题(1)。

答:(1)因为DA TA为偶地址,则DATA+1为奇地址。

故要完成本条指令,需要两个总线周期。

时序图如图5.4所示。

图5.4 执行MOV DA TA+1,AX指令的时序参考图

(2)DA TA+1虽然为奇地址,但是AL为八位存储器,故本条指令需用一个总线周期,时序图如图5.5所示。

图5.5 执行MOV DA TA+1,AL指令的时序参考图

(3)执行OUT DX,AX(DX的内容为偶数)指令的时序图如图5.6所示。

图5.6 执行OUT DX,AX指令的时序参考图

(4)执行IN AL,0F5H指令的时序图如图5.7所示。

图5.7 执行IN AL ,0F5H 指令的时序参考图

23.8086最小方式下,读总线周期和写总线周期相同之处是:在 1T 状态开始使ALE 信号变为有效 高 电平,并输出IO M/信号来确定是访问存储器还是访问I/O 端口,同时送出20位有效地址,在1T 状态的后部,ALE 信号变为 低 电平,利用其下降沿将20位地址和BHE 的状态锁存在地址锁存器中;相异之处从 2T 状态开始的数据传送阶段。