FPGA设计实例 四位加法器(含VHDL源程序)

实验一 4位全加器的设计(1)

实验一4位全加器的设计一、实验目的:1 熟悉QuartusⅡ与ModelSim的使用;2 学会使用文本输入方式和原理图输入方式进行工程设计;3 分别使用行为和结构化描述方法进行四位全加器的设计;4 理解RTL视图和Technology Map视图的区别;5 掌握简单的testbench文件的编写。

二、实验原理:一个4位全加器可以由4个一位全加器构成,加法器间的进位可以串行方式实现,即将低位加法器的进位输出cout与相邻的高位加法器的进位输入信号cin相接。

三、实验内容:1.QuartusII软件的熟悉熟悉QuartusⅡ环境下原理图的设计方法和流程,可参考课本第4章的内容,重点掌握层次化的设计方法。

2.设计1位全加器原理图设计的原理图如下所示:VHDL源程序如下(行为描述):library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity f_add_bev is(A : in std_logic;B : in std_logic;CIN : in std_logic;S : out std_logic;CO : out std_logic);end entity;architecture bev of f_add_bev isbegin(CO,S)<=('0',A)+('0',B)+('0',CIN);end bev;VHDL源程序如下(行为描述)的RTL与technology map视图VHDL源程序如下(数据流描述):library ieee;use ieee.std_logic_1164.all;use ieee.numeric_std.all;entity f_add_fl is(A : in std_logic;B : in std_logic;CIN : in std_logic;S : OUT std_logic;CO : out std_logic);end entity;architecture fl of f_add_fl isbeginS<=A XOR B XOR CIN;CO<=((A XOR B)AND CIN)OR(A AND B);end fl;VHDL源程序如下(数据流描述)的RTL与technology map视图:VHDL源程序如下(结构化描述):library ieee;use ieee.std_logic_1164.all;use ieee.numeric_std.all;entity f_add_con isport(A : in std_logic;B : in std_logic;CIN : in std_logic;S : OUT std_logic;CO : out std_logic );end entity;architecture con of f_add_con is COMPONENT hadd_vhdPORT(a : IN STD_LOGIC;b : IN STD_LOGIC;co : OUT STD_LOGIC;s : OUT STD_LOGIC );END COMPONENT;SIGNAL S1:STD_LOGIC;SIGNAL CO1:STD_LOGIC;SIGNAL CO2:STD_LOGIC;beginh_add1 : hadd_vhdport map(a => a,B => B,S => S1,CO => CO1);h_add2 : hadd_vhdport map(a => S1,B => CIN,S => S,CO => CO2);CO<=CO1 OR CO2;end con;VHDL源程序如下(结构化描述)的RTL与technology map视图:Testbench文件源程序如下:LIBRARY cycloneiii ;LIBRARY ieee ;USE cycloneiii.cycloneiii_components.all ;USE ieee.std_logic_1164.all ;ENTITY f_add_fl_tb ISEND ;ARCHITECTURE f_add_fl_tb_arch OF f_add_fl_tb ISSIGNAL A : STD_LOGIC :='0';SIGNAL CO : STD_LOGIC ;SIGNAL CIN : STD_LOGIC :='0'; SIGNAL B : STD_LOGIC :='0'; SIGNAL S : STD_LOGIC ;COMPONENT f_add_flPORT (A : in STD_LOGIC ;CO : buffer STD_LOGIC ;CIN : in STD_LOGIC ;B : in STD_LOGIC ;S : buffer STD_LOGIC );END COMPONENT ;BEGINDUT : f_add_flPORT MAP (A => A ,CO => CO ,CIN => CIN ,B => B ,S => S ) ;A<=NOT A AFTER 0.25US;B<=NOT B AFTER 0.5US;CIN<=NOT CIN AFTER 1US;END ;功能仿真波形如下:时序仿真波形如下:3.利用层次化原理图方法设计4位全加器(1)生成新的空白原理图,作为4位全加器设计输入(2)利用已经生成的1位全加器作为电路单元,设计4位全加器。

FPGA 4位全加器的设计

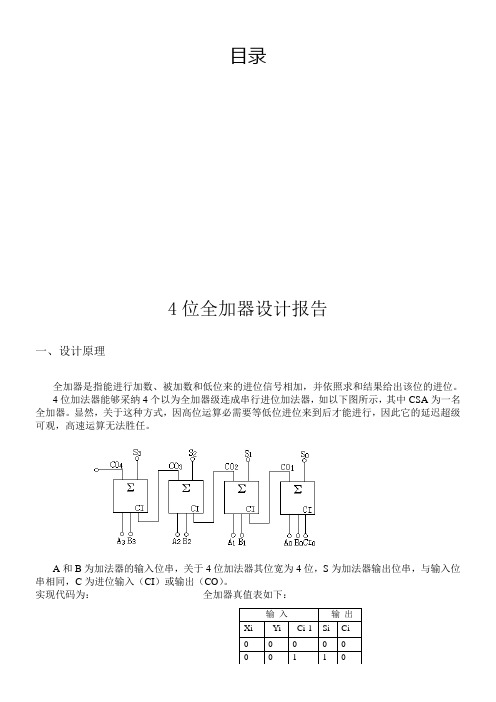

目录4位全加器设计报告一、设计原理全加器是指能进行加数、被加数和低位来的进位信号相加,并依照求和结果给出该位的进位。

4位加法器能够采纳4个以为全加器级连成串行进位加法器,如以下图所示,其中CSA为一名全加器。

显然,关于这种方式,因高位运算必需要等低位进位来到后才能进行,因此它的延迟超级可观,高速运算无法胜任。

A和B为加法器的输入位串,关于4位加法器其位宽为4位,S为加法器输出位串,与输入位串相同,C为进位输入(CI)或输出(CO)。

实现代码为:全加器真值表如下:输入输出Xi Yi Ci-1 Si Ci0 0 0 0 00 0 1 1 0output[3:0]sum;output cout;input[3:0]ina,inb;input cin;assign {count,sum}=ina+inb+cin;endmodule二、设计目的⑴熟悉开发环境,把握工程的生成方式。

⑵熟悉SEED-XDTK XUPV2Pro实验环境。

⑶了解Verilog HDL语言在FPGA中的利用。

⑷了解4位全加器的Verilog HDL语言实现。

三、设计内容用Verilog HDL语言设计4位全加器,进行功能仿真演示。

四、设计步骤1、创建工程及设计输入。

⑴在E:\progect\目录下,新建名为count8的新工程。

⑵器件族类型(Device Family)选择“Virtex2P”器件型号(Device)选“XC2VP30 ff896-7”综合工具(Synthesis Tool)选“XST(VHDL/Verilog)”仿真器(Simulator)选“ISE Simulator”⑶下面一直next和确信。

⑷设计输入:在源代码窗口中单击右键,在弹出的菜单被选择“New Source”,在弹出的对话框被选择“Verilog Moudle”,在右端的“File name”中输入源文件名adder4,下面各步单击“Next”按钮。

四位全加器的VHDL与VerilogHDL实现

entity pro1is

port(A1,B1,G1BAR,A0,B0,G0BAR:instd_logic;

or(cout,m1,m2,m3);

ﻩendmodule

ﻩ/*module add(co,s,a,b,ci);//数据流法

ﻩoutput[3:0] s;

ﻩoutput co;

ﻩinput[3:0] a,b;

ﻩinput ci;

ﻩassign {co,s}=a+b+ci;

ﻩendmodule*/

libraryIEEE;

endmodule

module full_add1(a,b,cin,sum,cout);

ﻩinput a,b,cin;

ﻩoutput sum,cout;

ﻩwire s1,m1,m2,m3;

and(m1,a,b),

(m2,b,cin),

ﻩ(m3,a,cin);

xor(s1,a,b),

ﻩ(sum,s1,cin);

四位全加器的VHDL与VerilogHDL实现

———————————————————————————————— 作者:

———————————————————————————————— 日期:

四位全加器的VHDL/VerilogHDL实现

加法器的分类

(一)半加器

能对两个1位二进制数进行相加而求得和及进位的逻辑电路称为半加器。或:只考虑两个一位二进制数的相加,而不考虑来自低位进位数的运算电路,称为半加器。图1为半加器的方框图。图2为半加器原理图。其中:A、B分别为被加数与加数,作为电路的输入端;S为两数相加产生的本位和,它和两数相加产生的向高位的进位C一起作为电路的输出。

基于FPGA的四位加法器设计

基于FPGA的四位加法器设计4位加法器设计。

取开发板上的4位按键作为4位被加数,取4位拨码开关作为4位被加数,其中8个led灯取5位作为输出结果,led0-led3作为相加的结果,led4作为进位(LED亮表示低电平0,LED灭表示高电平1,)数码管以十进制数显示被加数,加数和相加的结果。

包括vhdl文件、和vwf文件。

利用两组按键作为两个加数输入,用数码管做加数显示和结果显示,开发板上只有4个数码管,但加数都是两位的,所以只能做轮流显示,用“=”键做显示切换。

程序如下:library ieee;use ieee.std_logic_unsigned.all;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;entity adder_4 isport(clk:in std_logic; --时钟输入,应该输入分频后的clkenter:in std_logic; --显示切换,可以理解位“=”键clear:in std_logic; --清除键,预留接口可扩展key_num1:in std_logic_vector(3 downto 0); --加数1key_num2:in std_logic_vector(3 downto 0); --加数2duan:out std_logic_vector(6 downto 0); --输出结果wei:out std_logic_vector(3 downto 0);led5:out std_logic_vector(4 downto 0) --led结果显示);end entity;architecture fun of adder_4 issignal num1,num2:std_logic_vector(3 downto 0); --中间信号定义signal add_num1: integer range 15 downto 0;signal add_num2: integer range 15 downto 0;signal add_sum: integer range 30 downto 0;signal ten_data:integer range 9 downto 0;signal add_num1ge,add_num1shi,add_num2ge,add_num2shi,sumge,sumshi:integer range 9 downto 0;signal wei_data:integer range 0 to 3;beginduan<="1000000"when ten_data=0 else --显示部分,数码管共阳"1111001"when ten_data=1 else"0100100"when ten_data=2 else"0110000"when ten_data=3 else"0111001"when ten_data=4 else"0010010"when ten_data=5 else"0000010"when ten_data=6 else"1111000"when ten_data=7 else"0000000"when ten_data=8 else"0010000";process(clk,clear,enter,key_num1,key_num2,num1,num2,add_num1ge,add_num1shi,add_n um2ge,add_num2shi,sumge,sumshi)beginif clear = '0' thenadd_num1<=0;add_num2<=0;add_sum<=0;else--if key_num1/="1111" or key_num2/="1111" thennum1<=not key_num1;num2<=not key_num2;--加数处理,二进制转十进制。

1数电实验6PLD VHDL 四位串行二进制加法器 樊1

用Quartus II 软件原理图与VHDL 混合编程编写:樊伟敏1. 用Quartus II 软件原理图与VHDL 混合编写四位串行全加器四位串行全加器电路图如图1所示。

图1 四位串行全加器电路2. 新建原理图文件新建项目add4a ,出现如图2所示的界面。

执行【File\New ...】菜单命令,进入如图3所示的新建文件类型选择对话框。

选择Design Files 中的Block Diagram/Schematic file 项。

点击【OK 】按钮,进入如图4所示的新建原理图窗口。

图2 新建项目add4a 界面图3 新建文件类型选择对话框图4 新建原理图窗口3. 顶层原理图绘制3.1绘制图形块符号点击绘图图形块工具图标,在原理图窗口中拖动鼠标绘制出如图5所示的图形块符号。

3.2 图形块属性设置鼠标右键点击图5所示的图形块,弹出的如图6所示的快捷菜单。

选择Block Properties项,弹出模块属性对话框。

在如图7所示的General标签页中输入自定义的模块名,由于串行四位全加器是由4个一位全加器构成,所以在Name栏中输入自定义的一位全加器的名称,例如:add1a。

然后点击I/Os标签页,在该标签页中设置电路模块的输入输出端口的名称和类型,其中BIDIR为双向端口,INPUT为输入端口,OUTPUT为输出端口。

按如图8所示建立三个输入端a(加数)、b(被加数)、c0(低位进位)和两个输出端s(和)、c1(进位)。

在输入第一个名称和类型后点击【OK】,然后输入下一个名称和类型,直至全部输入以上五个端口的名称和类型后点击【OK】,完成图形块属性设置。

图5 在原理图窗口中绘制图形块符号图6 右键快捷菜单图7 在General标签页中输入自定义的模块名add1a图8 建立五个端口的名称和类型。

3.2 复制自定义的图形块符号在原理图窗口中激活自定义的图形块符号,使用右键快捷菜单中选择复制项,然后选择粘贴项,复制符号块,完成后的原理图编辑窗口的显示如图9所示。

4位二进制并行加法器的设计

实验一4位二进制并行加法器的设计1.实验目的:(1)学习使用Quartus II软件的基本用法(2)了解和掌握VHDL语言的语法规则和编程方法及基本流程(3)了解VHDL语言的基本结构2.实验内容用VHDL语言设计一4位二进制并行加法器。

参考设计思路:加法器是数字系统中的基本逻辑器件,减法器和硬件乘法器都可由加法器来构成。

多位加法器的构成有两种方式:并行进位和串行进位方式。

并行进位加法器设有进位产生逻辑,运算速度较快;串行进位方式是将全加器级联构成多位加法器。

并行进位加法器通常比串行级联加法器占用更多的资源。

随着位数的增加,相同位数的并行加法器与串行加法器的资源占用差距也越来越大。

因此,在工程中使用加法器时,要在速度和容量之间寻找平衡点。

实践证明,4位二进制并行加法器和串行级联加法器占用几乎相同的资源。

这样,多位加法器由4位二进制并行加法器级联构成是较好的折中选择。

3.实验要求(1)编写VHDL程序(2)记录系统仿真,画出时序图(3)记录实验过程中遇到的问题及解决办法4.程序设计5.生成RTL电路图6.仿真波形7.实验心得本周的实验是我学习该门课程进行的第一次实验,在实验过程中遇到了很多问题,比如:对Quartus II软件不熟悉,而且全是英文状态,不会使用软件的功能;编写程序时,多次报错,各种各样报错;编写程序完成后,成功编译了,但不会对仿真赋值等。

最后,我通过反复观看老师发的实验操作案例,并通过百度搜索相关的操作流程,翻阅教科书查找相关的解决方案。

第一次实验难免会遇到困难,最后经过我的不懈努力,终于把问题解决了,实验也很成功。

基于VHDL4位加法器的设计

基于VHDL4位加法器的设计实验三基于VHDL 4位加法器的设计⼀、实验⽬的1、进⼀步熟悉QUARTUS II软件的使⽤⽅法和VHDL输⼊的全过程。

2、进⼀步掌握实验系统的使⽤。

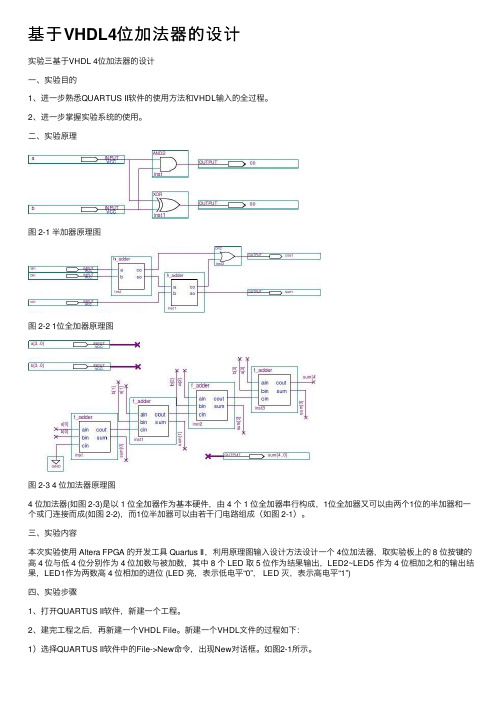

⼆、实验原理图 2-1 半加器原理图图 2-2 1位全加器原理图图 2-3 4 位加法器原理图4 位加法器(如图 2-3)是以 1 位全加器作为基本硬件,由 4 个 1 位全加器串⾏构成,1位全加器⼜可以由两个1位的半加器和⼀个或门连接⽽成(如图 2-2),⽽1位半加器可以由若⼲门电路组成(如图 2-1)。

三、实验内容本次实验使⽤ Altera FPGA 的开发⼯具 Quartus Ⅱ,利⽤原理图输⼊设计⽅法设计⼀个 4位加法器,取实验板上的 8 位按键的⾼ 4 位与低 4 位分别作为 4 位加数与被加数,其中 8 个 LED 取 5 位作为结果输出,LED2~LED5 作为 4 位相加之和的输出结果,LED1作为两数⾼ 4 位相加的进位 (LED 亮,表⽰低电平“0”, LED 灭,表⽰⾼电平“1”)四、实验步骤1、打开QUARTUS II软件,新建⼀个⼯程。

2、建完⼯程之后,再新建⼀个VHDL File。

新建⼀个VHDL⽂件的过程如下:1)选择QUARTUS II软件中的File->New命令,出现New对话框。

如图2-1所⽰。

图2-1 新建设计⽂件选择窗⼝2)在New对话框(图2-1)中选择Design Files页下的VHDL File,点击OK按钮,打开VHDL编辑器对话框,如图2-2所⽰。

图2-2 VHDL编辑窗⼝3、按照实验原理和⾃⼰的想法,在VHDL编辑窗⼝编写1位半加器的VHDL程序。

如图2-3所⽰。

图2-3 1位半加器VHDL程序4、编写完半加器VHDL程序后,保存,⽂件名为h_adder.vhd(注意⽂件名要与实体名保持⼀致),再将半加器⽂件设置为顶层⽂件,然后进⾏编译并仿真,对程序的错误进⾏修改。

四位全加器的VHDL设计

Architecture ax Of adder四 Is

Signal c: std_logic_vector【0 to 四】!!

Component fulladder

Port【Ci!!a!!b : IN std_logic!!

s!! Co : OUT std_logic】!!

End component!!

• sint<= aa+bb+cin!!

• s【三 downto 0】 <= sint 【三 downto 0】!!

• cout<= sint【四】!!

• end beh!!

Cout<=c【四】!!

End ax!!

• library ieee!!

• use ieee.std_logic_一一六四.all!!

• use ieee.std_logic_unsigned.all!!

• entity adder四bit is

• port【cin: in std_logic!!

Begin

c【0】<=Cin!!

U 一 :fulladder Port Map【c【0】!!x 【0】!!y【0】!!sum【0】!!c【一】】!!

--U 一 :fulladderPortMap【Ci=>c 【0】!!a=>x【0】!!b=>y【0】!! s=>sum【0】!!Co=>c【一】】!!

• signal sint: std_logic_vector【四 downto 0】!!

• signal aa!!bb: std_logic_vector【四 downto 0】!!

• begin

• aa<='0' & a 【三 downto 0】!!