Verilog数字系统设计教程[夏宇闻]PPT课件

合集下载

天津大学 Verilog 课件 第一讲概述

44

Verilog与C语言的关系

算法的描述和验证常用C语言来完成。

Verilog用于行为级和RTL级描述。 C语言与Verilog HDL可以配合使用。

C语言与Verilog HDL的语法很像,许多关键字

相同。

45

世界上第一个晶体管是1947年由肖克利和他的两助手布拉顿、巴丁在贝尔实验室工作 时发明的,为此,肖克利三人于1956年获得诺贝尔物理学奖。用晶体管代替电子管制 造电脑,在电脑史上是一次突破性技术飞跃。 1954年,贝尔实验室使用800支晶体管组装成功人类有史以来第一台晶体管计算机 TRADIC

25

45nm四核Core 2 Quad Q9650

3.0GHz时钟频率;NL则代表2 x 6MB共12MB的二级缓存容量 , Yorkfield内核四核心处理器拥有8.2亿个晶体管,这比Kentsfield内核的 5.82亿个晶体管足足多出了2.38亿个之多。其中,50%的二级缓存容量增 长约占据了1.92亿个晶体管,而余下的部分则分别由新增的SSE4多媒体 指令运算单元以及微架构的改良部分所占据。

TJIC

超大规模集成电路设计专用语言

1

选用教材

Verilog 数字系统设计 教程 作者: 夏宇闻编 出版社:北京航空航 天大学出版社 出版日期:2003-7-1 ISBN:7-81077-302-X 定价:38.00元

2

参考资料(一) 参考资料

<<VERILOG HDL硬件描述 语言 >>

37

集成电路的设计流程(1)

TJU. ASIC Center---verilog2008秋

38

集成电路的设计流程(2)

精品课件-Verilog HDL数字系统设计-Verilog HDL数字系统设计-第1章

编程器件的基础上进一步发展的产物,它是作为ASIC领域中的 一种半定制电路而出现的,既解决了定制电路的不足,又克服 了原有可编程器件门电路有限的缺点。

第1章 概 述

26

如前所述,FPGA是由存放在片内的RAM来设置其工作状态的, 因此工作时需要对片内RAM进行编程。用户可根据不同的配置模 式,采用不同的编程方式。FPGA有如下几种配置模式:

第1章 概 述

1

第1章 概

述

1.1 EDA技术简介 1.2 可编程器件 1.3 Verilog HDL简介

第1章 概 述

2

1.1 EDA技术简介

现代电子设计技术的核心已日趋转向基于计算机的电子设 计自动化(EDA,Electronic Design Automation)技术。所谓 EDA技术,就是依赖功能强大的计算机,在EDA工具软件平台上, 对以硬件描述语言(HDL,Hardware Description Language)为 系统逻辑描述手段完成的设计文件,自动地进行逻辑编译、化 简、分割、综合、布局布线以及逻辑优化和仿真测试,直至实 现既定的电子线路系统功能。

6.目标器件的编程/下载 7.硬件仿真与测试

第1章 概 述

18

1.2 可 编 程 器 件

1.2.1 可编程逻辑器件概述 随着数字电路的普及,传统的定制数字集成电路器件已满

足不了应用的需求,可编程逻辑器件(PLD)应运而生,并逐渐地 成为主流产品。PLD与传统定制器件的主要区别是它的可编程性, 它的逻辑功能是由用户设计的,并且一般都可重复编程和擦除, 即PLD是能够为客户提供范围广泛的多种逻辑能力、特性、速度 和电压特性的标准成品部件,而且此类器件的功能可在任何时 间修改,从而实现多种不同的功能。对于可编程逻辑器件,设 计人员可利用价格低廉的软件工具快速开发、仿真和测试其设 计。

《Verilog设计入门》PPT课件

精选PPT

18

3.1 组合电路的Verilog描述

3.1.2 4选1多路选择器及其case语句表述方式 6.赋值操作符 “<=”,只能用于顺序语句,不能用于assign引 导的并行语句

两种过程赋值操作: (1)阻塞式赋值“=”:语句执行结束,右侧表达式的值立刻赋给左侧 目标变量。

对于always引导的块语句中含有多条阻塞式赋值语句时,当执行某 一条语句时,其它语句不允许执行,被阻塞了,具有顺序执行的特点。

精选PPT

23

3.1 组合电路的Verilog描述

3.1.4 4选1多路选择器及其if语句描述方式

精选PPT

24

3.1 组合电路的Verilog描述

3.1.4 4选1多路选择器及其if语句描述方式 1.if_ else条件语句 if(表达式) begin 语句1;语句2;…..语句n; end else begin 语句n+1;语句n+2;…..语句n+n; end

input a,b;

output so,co;

assign so = a ^ b;

assign co = a & b;

endmodule

精选PPT

28

3.1 组合电路的Verilog描述

3.1.5 加法器及其Verilog描述

2.基于always @引导的过程语句和逻辑操作符的描述

module h_adder2(a,b,so,co);

endmodule

精选PPT

34

3.1 组合电路的Verilog描述

3.1.5 加法器及其Verilog描述 5. 全加器描述----用半加器、或门模块及例化语句描述

精选PPT

verilog数字系统设计教程PPT课件

数字系统设计的核心知识

• 复杂数字系统的构成; • 基本电路和 Verilog 的对应关系; • 同步有限状态机在电路中的作用; • 时钟树与自动综合技术

数字逻辑电路的构成

- 组合逻辑:输出只是输入逻辑电平的函

数(有延时),与电路的原始状态无关。

• 时序逻辑:输出不只是输入的逻辑电

平的函数,还与电路所处的状态有关。

8 ‘ d 31

8‘d

t

out[15:0]

202

16 ‘ d

16‘ d

t

Sn 开

93

606

t 关

全局时钟网和平衡树结构

触发器1

全局时钟网络 触发器 图1 全局时钟网示意图

缓冲器

触发器n

图2 平衡树结构示意图

避免冒险和竞争

• 由于组合逻辑和布线的延迟引起

a

c

b

a

b

t

c

t

clock

避免冒险和竞争与流水线

t

t

带寄存器的八位数据通路控制器的波形

ControlSwitch

in[7]

out[7]

CLOCK

out[7]

D Q[7]

ControlSwitch

in[0]

out[0]

CLOCK

out[0]

D Q[0]

带寄存器的八位数据通路控制器的Verilog描述

`define ON 1 ‘b 1 `define OFF 1 ‘b 0 wire ControlSwitch; wire clock wire [7:0] out, in;

ControlSwitch in[7]

out[7]

…... …...

in[0]

• 复杂数字系统的构成; • 基本电路和 Verilog 的对应关系; • 同步有限状态机在电路中的作用; • 时钟树与自动综合技术

数字逻辑电路的构成

- 组合逻辑:输出只是输入逻辑电平的函

数(有延时),与电路的原始状态无关。

• 时序逻辑:输出不只是输入的逻辑电

平的函数,还与电路所处的状态有关。

8 ‘ d 31

8‘d

t

out[15:0]

202

16 ‘ d

16‘ d

t

Sn 开

93

606

t 关

全局时钟网和平衡树结构

触发器1

全局时钟网络 触发器 图1 全局时钟网示意图

缓冲器

触发器n

图2 平衡树结构示意图

避免冒险和竞争

• 由于组合逻辑和布线的延迟引起

a

c

b

a

b

t

c

t

clock

避免冒险和竞争与流水线

t

t

带寄存器的八位数据通路控制器的波形

ControlSwitch

in[7]

out[7]

CLOCK

out[7]

D Q[7]

ControlSwitch

in[0]

out[0]

CLOCK

out[0]

D Q[0]

带寄存器的八位数据通路控制器的Verilog描述

`define ON 1 ‘b 1 `define OFF 1 ‘b 0 wire ControlSwitch; wire clock wire [7:0] out, in;

ControlSwitch in[7]

out[7]

…... …...

in[0]

第4章 Verilog设计初步 数字系统设计与Verilog HDL (第4版)教学课件

qout[0]<=~qout[WIDTH-1];

end

end

endmodule

Synplify Pro新建项目对话框

Synplify Pro新建文件对话框

Implementation Option对话框

约翰逊计数器综合后的RTL级原理图

约翰逊计数器综合后的门级原理图 (MAX7000器件)

begin

if(~reset) begin q<=1'b0;qn<=1'b1; end //异步清0,低电平有效

else if(~set) begin q<=1'b1;qn<=1'b0; end

//异步置1,低电平有效

else

begin q<=d;qn<=~d; end

end

endmodule

4.4 Verilog基本时序电路设计

begin if(~reset) begin q<=1'b0;qn<=1'b1;end

//同步清0,低电平有效 else if(~set) begin q<=1'b1;qn<=1'b0;end //同步置1,低电平有效 else begin q<=d; qn<=~d; end

end endmodule

【例4.11】 带异步清0/异步置1(低电平有效)的D触发器

module dff_asyn(q,qn,d,clk,set,reset);

input d,clk,set,reset; output reg q,qn;

always @(posedge clk or negedge set or negedge reset)

Verilog教程-夏宇闻(共178张)

13

第13页,共178页。

3.2 Verilog HDL基本(jīběn)结构

二、Verilog HDL模块的结构

▪ Verilog的基本设计单元是“模块 (block) ” 。 ▪ Verilog 模块的结构由在module和endmodule关键词

之间的4个主要部分组成:

1 端口定义 2 I/O说明

(3)用 “always” 块语句 结构说明语句

always @(posedge clk) // 每当时钟上升沿到来时执行一遍块内语句

begin

if(load)

out = data; // 同步预置数据 else

out = data + 1 + cin; // 加1计数

end

❖注1:“always” 块语句常用于描述时序逻辑,也可 描述组合逻辑。

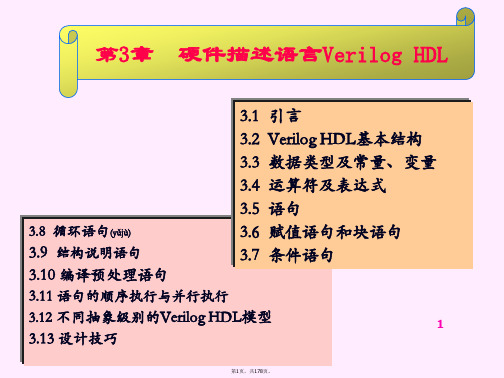

3.12 不同抽象级别的Verilog HDL模型

1

3.13 设计技巧

第1页,共178页。

引言 3.1

(yǐnyán)

内容概要

一、什么是Verilog HDL 二、Verilog HDL的发展历史 三、不同层次的Verilog HDL抽象

四、Verilog HDL的特点

2

第2页,共178页。

3.1 引言(yǐnyán)

❖ Verilog HDL模块的模板(仅考虑用于逻辑综合的部分)

module <顶层模块名> (< 输入输出端口列表>) ;

output 输出端口列表;

input 输入端口列表;

//(1)使用assign语句定义逻辑功能

wire 结果信号名;

assign <结果信号名> = 表达式 ;

第13页,共178页。

3.2 Verilog HDL基本(jīběn)结构

二、Verilog HDL模块的结构

▪ Verilog的基本设计单元是“模块 (block) ” 。 ▪ Verilog 模块的结构由在module和endmodule关键词

之间的4个主要部分组成:

1 端口定义 2 I/O说明

(3)用 “always” 块语句 结构说明语句

always @(posedge clk) // 每当时钟上升沿到来时执行一遍块内语句

begin

if(load)

out = data; // 同步预置数据 else

out = data + 1 + cin; // 加1计数

end

❖注1:“always” 块语句常用于描述时序逻辑,也可 描述组合逻辑。

3.12 不同抽象级别的Verilog HDL模型

1

3.13 设计技巧

第1页,共178页。

引言 3.1

(yǐnyán)

内容概要

一、什么是Verilog HDL 二、Verilog HDL的发展历史 三、不同层次的Verilog HDL抽象

四、Verilog HDL的特点

2

第2页,共178页。

3.1 引言(yǐnyán)

❖ Verilog HDL模块的模板(仅考虑用于逻辑综合的部分)

module <顶层模块名> (< 输入输出端口列表>) ;

output 输出端口列表;

input 输入端口列表;

//(1)使用assign语句定义逻辑功能

wire 结果信号名;

assign <结果信号名> = 表达式 ;

【课件】Verilog教程清华微电所精编版

SystemC and SystemVerilog:面向SOC

VERILOG HDL的设计流程

自顶向下(Top-Down)设计 一个系统由总设计师先进行系统描述

(Spec),将系统划分为若干模块,编写 模块模型(一般为行为级),仿真验证后, 再把这些模块分配给下一层的设计师, 由他们完成模块的具体设计,而总设计 师负责各模块的接口定义

VERILOG教程(1)

清华大学微电子学研究所 2003年9月

提纲

Verilog概述 Verilog程序的基本结构 Verilog上机环境及工具

Verilog概述 Verilog程序的基本结构 Verilog上机环境及工具

VERILOG概述

什么是Verilog HDL? Verilog HDL(Hardware Discription Language)是一种硬件描述语言,用于从 算法级、门级到开关级的多种抽象设计 层次的数字系统建模。

VERILOG HDL与 C语言

虽然Verilog的某些语法与C语言接近,但存在 本质上的区别

Verilog是一种硬件语言,最终是为了产生实际的硬 件电路或对硬件电路进行仿真

C语言是一种软件语言,是控制硬件来实现某些功 能

利用Verilog编程时,要时刻记得Verilog是硬件语 言,要时刻将Verilog与硬件电路对应起来

数据流方式 行为方式 结构方式 上述方式的混合

模块

简单的例子(数据流方式) module HalfAdder(A, B, Sum, Carry);

input A, B; output Sum, Carry;

assign #2 Sum=A^B; assign #5 Carry=A&B; endmodule

VERILOG HDL的设计流程

自顶向下(Top-Down)设计 一个系统由总设计师先进行系统描述

(Spec),将系统划分为若干模块,编写 模块模型(一般为行为级),仿真验证后, 再把这些模块分配给下一层的设计师, 由他们完成模块的具体设计,而总设计 师负责各模块的接口定义

VERILOG教程(1)

清华大学微电子学研究所 2003年9月

提纲

Verilog概述 Verilog程序的基本结构 Verilog上机环境及工具

Verilog概述 Verilog程序的基本结构 Verilog上机环境及工具

VERILOG概述

什么是Verilog HDL? Verilog HDL(Hardware Discription Language)是一种硬件描述语言,用于从 算法级、门级到开关级的多种抽象设计 层次的数字系统建模。

VERILOG HDL与 C语言

虽然Verilog的某些语法与C语言接近,但存在 本质上的区别

Verilog是一种硬件语言,最终是为了产生实际的硬 件电路或对硬件电路进行仿真

C语言是一种软件语言,是控制硬件来实现某些功 能

利用Verilog编程时,要时刻记得Verilog是硬件语 言,要时刻将Verilog与硬件电路对应起来

数据流方式 行为方式 结构方式 上述方式的混合

模块

简单的例子(数据流方式) module HalfAdder(A, B, Sum, Carry);

input A, B; output Sum, Carry;

assign #2 Sum=A^B; assign #5 Carry=A&B; endmodule

VerilogHDL数字系统设计技巧精品PPT课件

module clk ( o_clk, i_clk, rst_n );

output o_clk; input i_clk; input rst_n; parameter N = N_even; // 设置偶数倍分频 parameter M = ?; // M="N/2-1" // bit_of_N: N_even的二进制位宽 reg [(bit_of_N - 1):0] cnt; // 计数器单元 reg o_clk;

cnt <= cnt + 1'b1; end end

恰恰分频:任意整数和小数分频的Verilog实现

// 生成上升沿时钟 // 0~(N/2-1) ↑ -> 1; (N/2)~(N-1) ↑ -> 0 always @ (posedge i_clk, negedge rst_n) begin

if (!rst_n) o_clk <= 0;

偶数分频器的实现非常简单,通过计数器计数 就完全可以实现。 如进行N倍偶数分频,就可以通过由待分频的 时钟触发计数器计数。 当计数器从0计数到N/2-1时,输出时钟进行翻 转,并给计数器一个复位信号,以使下一个时 钟从零开始计数。 以此循环,就可以实现任意的偶数分频。

恰恰分频:任意整数和小数分频的Verilog实现

恰恰分频:任意整数和小数分频的Verilog实现

always@(negedge clk or negedge rst_n) begin if(!rst_n) begin cnt2<=0; end else if(cnt2==2'b10) begin cnt2<=0; end else begin cnt2<=cnt2+1; end end

output o_clk; input i_clk; input rst_n; parameter N = N_even; // 设置偶数倍分频 parameter M = ?; // M="N/2-1" // bit_of_N: N_even的二进制位宽 reg [(bit_of_N - 1):0] cnt; // 计数器单元 reg o_clk;

cnt <= cnt + 1'b1; end end

恰恰分频:任意整数和小数分频的Verilog实现

// 生成上升沿时钟 // 0~(N/2-1) ↑ -> 1; (N/2)~(N-1) ↑ -> 0 always @ (posedge i_clk, negedge rst_n) begin

if (!rst_n) o_clk <= 0;

偶数分频器的实现非常简单,通过计数器计数 就完全可以实现。 如进行N倍偶数分频,就可以通过由待分频的 时钟触发计数器计数。 当计数器从0计数到N/2-1时,输出时钟进行翻 转,并给计数器一个复位信号,以使下一个时 钟从零开始计数。 以此循环,就可以实现任意的偶数分频。

恰恰分频:任意整数和小数分频的Verilog实现

恰恰分频:任意整数和小数分频的Verilog实现

always@(negedge clk or negedge rst_n) begin if(!rst_n) begin cnt2<=0; end else if(cnt2==2'b10) begin cnt2<=0; end else begin cnt2<=cnt2+1; end end

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

设计示例四(续) 用激励信号对进位计数器进行测试

module stimulus; reg clk; reg reset; wire[3:0] q; // instantiate the design block ripple_carry_counter r1(q, clk, reset); // Control the clk signal that drives the design block. initial clk = 1'b0; always #5 clk = ~clk;

设计示例四 带异步复位端的 D 触发器

module DFF(q, d, clk, reset); output q; input d, clk, reset; reg q; always @(posedge reset or negedge clk) if (reset) q <= 1'b0; else q <= d; endmodule

设计示例二

由已设计的模块来构成高一级的模块

q3

q2

q1

q0

d

q

d

f4

clk clr

f3

clk clr

q

d

f2

clk clr

q

d

f1

clk clr

q

clrb

clk

d3

d2

d1

d0

四位寄存器电路结构图

设计示例二 `include “ flop.v ” module hardreg(d,clk,clrb,q); input clk,clrb; input[3:0] d; output[3:0] q; flop f1(d[0],clk,clrb,q[0],), f2(d[1],clk,clrb,q[1],), f3(d[2],clk,clrb,q[2],), f4(d[3],clk,clrb,q[3],); endmodule

设计示例五(续) 设计示例五(续) 用一位全加器组成四位全加器

module ADDER4BIT ( Ain, Bin, SUM, OVF); input [3:0] Ain, Bin; output [3:0] SUM; wire [2:0] CY; output OVF; FullAdder U0 (Ain[0], Bin[0], 0, SUM[0], CY[0]); FullAdder U1 (Ain[1], Bin[1], CY[0], SUM[1], CY[1]); FullAdder U2 (Ain[2], Bin[2], CY[1], SUM[2], CY[2]); FullAdder U3 (Ain[3], Bin[3], CY[2], SUM[3], OVF); endmodule

-------------------------------------------------------------------------------------------------*/ ----*/ `stim 0000; `stim 0001; . . . . . . `stim 1111; #200 -> end_first_pass; //延迟200个单位时间 触发事件end_first_pass 延迟200个单位时间, //延迟200个单位时间,触发事件end_first_pass end $finish; //结束仿真 //结束仿真 end

Verilog 设计举例

结构模块的层次化组成 各种类型模块之间的关系Байду номын сангаас测试和验证

设计示例一

用门级结构描述D 用门级结构描述D触发器

clear a nd3

nd1 clock

c nd5

e nd7

q

data

iv1

nd2

b

nd4

d

nd6

f

nd8

qb

iv2

nclock

设计示例一 module input output nand #10 flop(data,clock,clear,q,qb); flop(data,clock,clear,q,qb); data,clock,clear; data,clock,clear; q,qb; q,qb; nd1 nd1(a,data,clock,clear), nd2 nd2(b,ndata,clock), nd4 nd4(d,c,b,clear), nd5 nd5(e,c,nclock), nd6 nd6(f,d,nclock), nd8(qb,q,f,clear); nd8(qb,q,f,clear); nd3 nd3(c,a,d), nd7(q,e,qb); nd7(q,e,qb); iv1 iv1(ndata,data), iv2(nclock,clock); iv2(nclock,clock);

用户定义的原始元件

前面模块中的nand和not原语元件 primitive) 前面模块中的nand和not原语元件(primitive)在 原语元件( Verilog 语言中是保留词,它们分别表示: 语言中是保留词,它们分别表示: 与非门和非门的逻辑关系。 与非门和非门的逻辑关系。 在Verilog 语法中通过用户定义的原始元件语句 UDP) (即UDP)的真值表和带参数的延迟线模型来表 示。在与具体工艺库的逻辑对应时把具体延迟参 数传入延迟线模型,再加上描述逻辑关系的UDP 数传入延迟线模型,再加上描述逻辑关系的UDP 。 就有了一个与真实情况很接近逻辑模型, 就有了一个与真实情况很接近逻辑模型,仿真器 就可以依据它进行计算, 就可以依据它进行计算,来确定相互连接元件的 逻辑值。 逻辑值。

nand #9 not #10

endmodule

用户定义的原始元件

primitive udp_and (out,a,b); output out; input a,b; table //a b : out; 0 0 : 0; 0 1 : 0; 1 0 : 0; 1 1 : 1; endtable endprimitive

设计示例四(续) 用D触发器构成T触发器

module TFF(q, clk, reset); output q; input clk, reset; wire d; DFF dff0(q, d, clk, reset); // DFF已在上面的模块定义 DFF已在上面的模块定义 not n1(d, q); // not 表示非门是一个Verilog 原语. 表示非门是一个Verilog endmodule

设计示例五(续) 设计示例五(续) 用四位全加器的测试

`timescale 1ns/1ns module ADDER4BIT_TEST; reg [3:0] Ain, Bin; wire [3:0] SUMOUT; wire OVF; ADDER4BIT m ( Ain, Bin, SUMOUT, OVF ); initial begin Ain = 4'b0000; Bin= 4'b0000; #100 Ain = 4'b0111; Bin= 4'b0101; #100 ……….. #100 Ain = 4'b0000; Bin= 4'b0000; #100 $stop; end endmodule

设计示例三 (续)

initial begin repeat(4 repeat(4) begin /*------------------------------------------------/*------------------------------------------------宏定义stim引用, 宏定义stim引用,等同于 #100 data=4'b 注意引用时要用 `符号。 stim引用 符号。

设计示例五(续) 设计示例五(续) 四位全加器的另一种描述

module ADDER4BIT ( Ain, Bin, SUM, OVF); input [3:0] Ain, Bin; output [3:0] SUM; output OVF; assign {OVF, SUM} = Ain +Bin; Endmodule 这种描述方法比较直观,可以直接用综合器转换为门 这种描述方法比较直观, 级组合逻辑互相连接的描述。 级组合逻辑互相连接的描述。仍然用同样的测试模块 测试。这种描述使得逻辑关系更容易明白。 测试。这种描述使得逻辑关系更容易明白。

设计示例三 (续)

always @(end_first_pass) clearb = ~ clearb; //清零信号电平翻转 clearb; //清零信号电平翻转 always @(posedge clock) $display (“ at time %0d clearb= %b data= %b qout= %b ”, $time,clearb,data,qout); time,clearb,data,qout); endmodule

设计示例四(续) 用激励信号对进位计数器进行测试

// Control the reset signal that drives the design block initial begin reset = 1'b1; #15 reset = 1'b0; #180 reset = 1'b1; #10 reset = 1'b0; #20 $stop; end

设计示例三 (续)

hardreg reg_4bit(.d(data),.clk(clock), .clrb(clearb), reg_4bit(.d(data),. q(qout)); .q(qout)); /*--------------------------------------------------/*--------------------------------------------------把本模块中产生的测试信号data clock、clearb输入实例 data、 把本模块中产生的测试信号data、clock、clearb输入实例 reg_4bit以观察输出信号qout.实例reg_ bit引用了 以观察输出信号qout reg_4 引用了hardreg reg_4bit以观察输出信号qout.实例reg_4bit引用了hardreg ---------------------------------------------------*/ ---------------------------------------------------*/ initial begin clock = 0; clearb = 1; end always #50 clock = ~clock; ~clock;