ARM Instruction Set(ARM汇编指令集)

arm32汇编指令手册简要

ARM32汇编指令手册简要:掌握ARM32汇编指令,轻松开发嵌入式系统在嵌入式系统开发中,ARM32汇编指令是必不可少的一部分。

ARM32汇编指令手册简要提供了ARM32汇编指令的基础知识和常用指令的详细介绍,帮助开发人员更好地掌握ARM32汇编指令,从而轻松开发嵌入式系统。

ARM32汇编指令是一种低级语言,它是由CPU直接执行的指令。

掌握ARM32汇编指令对于嵌入式系统开发人员来说非常重要。

了解ARM32汇编指令的基本结构和语法是必要的。

ARM32汇编指令的基本结构包括指令助记符、寄存器、操作数和注释。

指令助记符是指令的名称,寄存器是用来存储数据的地方,操作数是指令的参数,注释是对指令的解释说明。

ARM32汇编指令手册简要中还介绍了一些常用的指令,如MOV、ADD、SUB、CMP、B、BL等。

这些指令涵盖了ARM32汇编指令的大部分功能。

MOV指令可以将一个寄存器的值传递给另一个寄存器;ADD和SUB指令可以进行加法和减法运算;CMP指令可以比较两个值的大小;B和BL指令可以进行跳转操作。

掌握这些指令可以帮助开发人员更好地编写ARM32汇编程序。

除了介绍基本结构和常用指令外,ARM32汇编指令手册简要还介绍了一些高级指令,如LDR、STR、LDM、STM、SWI等。

这些指令可以让开发人员更加灵活地操作内存和系统调用。

例如,LDR和STR指令可以读取和写入内存中的数据;LDM和STM指令可以一次性读取或写入多个寄存器的值;SWI指令可以进行系统调用。

掌握这些高级指令可以让开发人员更加高效地编写ARM32汇编程序。

ARM32汇编指令手册简要提供了ARM32汇编指令的基础知识和常用指令的详细介绍,帮助开发人员更好地掌握ARM32汇编指令,从而轻松开发嵌入式系统。

掌握ARM32汇编指令不仅可以提高开发效率,还可以让开发人员更好地理解计算机底层原理,更加深入地了解嵌入式系统的工作原理。

ARM32汇编指令是嵌入式系统开发中必不可少的一部分。

软考中级嵌入式系统需掌握的英语词汇

软考中级嵌入式系统需掌握的英语词汇一、嵌入式系统基础1. 嵌入式系统:Embedded System2. 硬件:Hardware3. 软件:Software4. 固件:Firmware5. 系统软件:System Software6. 应用软件:Application Software7. 实时操作系统:Real-Time Operating System (RTOS)二、微控制器原理1. 微控制器:Microcontroller2. 中央处理器:Central Processing Unit (CPU)3. 存储器:Memory4. 输入/输出接口:Input/Output Interface5. 时钟系统:Clock System6. 中断:Interrupt7. 外设:Peripheral三、ARM架构与编程1. ARM架构:ARM Architecture2. ARM指令集:ARM Instruction Set3. ARM汇编语言:ARM Assembly Language4. ARM链接器:ARM Linker5. ARM工具链:ARM Toolchain6. ARM Cortex系列:ARM Cortex Series7. ARM内存管理单元:ARM Memory Management Unit (MMU)四、实时操作系统1. 实时操作系统:Real-Time Operating System (RTOS)2. 任务调度:Task Scheduling3. 信号量:Semaphore4. 消息队列:Message Queue5. 内存管理:Memory Management6. 中断处理:Interrupt Handling7. 时间管理:Time Management五、低功耗设计1. 低功耗设计:Low Power Design2. 待机模式:Standby Mode3. 休眠模式:Sleep Mode4. 唤醒机制:Wake-up Mechanism5. 能效比:Energy Efficiency Ratio6. 功率优化:Power Optimization7. 低功耗电路设计:Low Power Circuit Design六、传感器与信号处理1. 传感器:Sensor2. 模拟信号:Analog Signal3. 数字信号:Digital Signal4. 信号调理:Signal Conditioning5. 采样率:Sampling Rate6. 滤波器:Filter7. 数据转换器:Data Converter8. 信号处理算法:Signal Processing Algorithm9. 特征提取:Feature Extraction10. 信号分析:Signal Analysis11. 噪声抑制:Noise Suppression12. 数据融合:Data Fusion13. 动态范围:Dynamic Range14. 量程:Range of Measurement。

arm汇编逻辑指令 -回复

arm汇编逻辑指令-回复ARM汇编逻辑指令ARM汇编逻辑指令是一种基于RISC(Reduced Instruction Set Computing)的指令集架构,在数字电子设备中被广泛使用。

逻辑指令主要用于实现基本的逻辑操作,例如布尔运算、比较和分支跳转等。

本文将深入探讨ARM汇编逻辑指令的各个方面,包括指令格式、操作数和指令示例等。

一、指令格式ARM汇编逻辑指令的指令格式通常包括操作码、目标寄存器和操作数等字段。

下面是一个典型的ARM汇编逻辑指令的格式:<操作码>{xx}{cond} <目标寄存器>, <操作数1>, <操作数2>其中,操作码用于指定具体的逻辑操作,xx字段用于指定操作的类型(例如AND、OR或XOR等),cond字段用于指定条件执行的条件码,目标寄存器用于存储运算结果,操作数1和操作数2分别是参与运算的操作数。

二、操作数ARM汇编逻辑指令的操作数可以是寄存器或立即数。

寄存器是存储在CPU内部的高速存储器单元,用于存储临时数据。

ARM架构通常提供了16个通用寄存器(R0-R15),其中R0-R7用于存储一般性目的数据,R8-R15用于存储特殊用途数据。

立即数是直接写在指令中的常数值,通常用于表示较小的数据。

立即数的宽度取决于具体的指令和操作码。

例如,对于AND指令,立即数可以是8位或32位的。

三、指令示例以下是一些常见的ARM汇编逻辑指令示例:1. AND指令AND指令用于将两个操作数逐位进行与运算,并将结果存储在目标寄存器中。

例如,下面的指令将执行R1 = R2 AND 3:AND R1, R2, 32. OR指令OR指令用于将两个操作数逐位进行或运算,并将结果存储在目标寄存器中。

例如,下面的指令将执行R1 = R2 OR R3:ORR R1, R2, R33. XOR指令XOR指令用于将两个操作数逐位进行异或运算,并将结果存储在目标寄存器中。

arm汇编指令

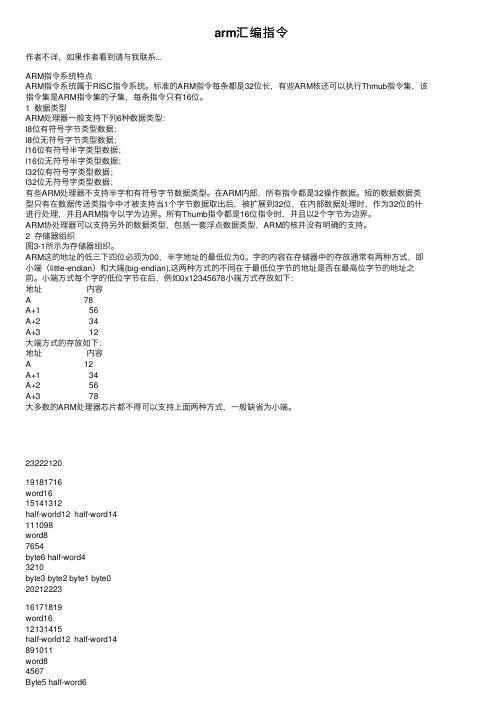

arm汇编指令作者不详,如果作者看到请与我联系...ARM指令系统特点ARM指令系统属于RISC指令系统。

标准的ARM指令每条都是32位长,有些ARM核还可以执⾏Thmub指令集,该指令集是ARM指令集的⼦集,每条指令只有16位。

1 数据类型ARM处理器⼀般⽀持下列6种数据类型:l8位有符号字节类型数据;l8位⽆符号字节类型数据;l16位有符号半字类型数据;l16位⽆符号半字类型数据;l32位有符号字类型数据;l32位⽆符号字类型数据;有些ARM处理器不⽀持半字和有符号字节数据类型。

在ARM内部,所有指令都是32操作数据。

短的数据数据类型只有在数据传送类指令中才被⽀持当1个字节数据取出后,被扩展到32位,在内部数据处理时,作为32位的什进⾏处理,并且ARM指令以字为边界。

所有Thumb指令都是16位指令时,并且以2个字节为边界。

ARM协处理器可以⽀持另外的数据类型,包括⼀套浮点数据类型,ARM的核并没有明确的⽀持。

2 存储器组织图3-1所⽰为存储器组织。

ARM这的地址的低三下四位必须为00,半字地址的最低位为0。

字的内容在存储器中的存放通常有两种⽅式,即⼩端(little-endian)和⼤端(big-endian),这两种⽅式的不同在于最低位字节的地址是否在最⾼位字节的地址之前。

⼩端⽅式每个字的低位字节在后,例如0x12345678⼩端⽅式存放如下:地址内容A 78A+1 56A+2 34A+3 12⼤端⽅式的存放如下:地址内容A 12A+1 34A+2 56A+3 78⼤多数的ARM处理器芯⽚都不得可以⽀持上⾯两种⽅式,⼀般缺省为⼩端。

2322212019181716word1615141312half-world12 half-word14111098word87654byte6 half-word43210byte3 byte2 byte1 byte02021222316171819word1612131415half-world12 half-word14891011word84567Byte5 half-word6Byte0 byte1 byte2 byte3(a)⼩端存储器组织(b)⼤端存储器组织图3-1 存储器组织3 ARM指令特点1.每条指令的多功能ARM指令⼀个重要的特点是它所有的指令都带有条件,例如⽤户可以测试某个寄存器的什但是直到下次使⽤同⼀条件进⾏测试时,才能有条件的执⾏这些指令。

arm 汇编 指令

arm 汇编指令ARM汇编指令是一种用于编写ARM处理器程序的语言。

ARM处理器广泛应用于嵌入式系统和移动设备等领域。

ARM汇编指令与x86汇编指令有所不同,它基于RISC(精简指令集计算机)架构。

下面是一些基本的ARM汇编指令:1. 数据传输指令:用于在寄存器之间传输数据。

例如:- mov:将数据从一个寄存器传输到另一个寄存器。

- ldr:将数据从内存传输到寄存器。

2. 算术指令:用于执行加法、减法、乘法和除法等操作。

例如:- add:加法操作。

- sub:减法操作。

- mull:乘法操作。

- div:除法操作。

3. 逻辑指令:用于执行逻辑操作,如与、或、非等。

例如:- and:与操作。

- or:或操作。

- xor:异或操作。

4. 移位指令:用于对数据进行左移、右移或无符号右移。

例如:- lsr:无符号右移。

- asr:带符号右移。

- ror:循环右移。

5. 比较指令:用于比较两个寄存器的值。

例如:- cmp:比较两个寄存器的值,若相等则返回0,否则返回1。

6. 跳转指令:用于改变程序的执行流程。

例如:- b:条件跳转。

- bl:无条件跳转。

- bx:带状态跳转。

7. 循环指令:用于实现循环操作。

例如:- loop:内部循环。

- ldp:外部循环。

8. 调用指令:用于实现函数调用。

例如:- blx:带状态调用。

- bx:不带状态调用。

9. 系统调用指令:用于实现与操作系统交互的功能。

例如:- swi:执行系统调用。

10. 存储器访问指令:用于访问内存数据。

例如:- str:将数据存储到内存。

- ldr:从内存中加载数据。

以上仅为ARM汇编指令的一部分,实际上,ARM汇编指令还有很多其他功能。

为了更好地理解和使用ARM汇编指令,可以参考相关的教程和手册,并进行实际操作。

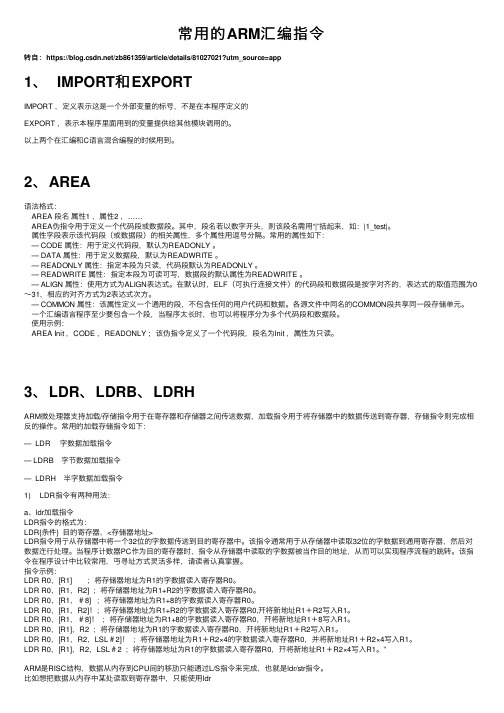

常用的ARM汇编指令

常⽤的ARM汇编指令转⾃:https:///zb861359/article/details/81027021?utm_source=app1、 IMPORT和EXPORTIMPORT ,定义表⽰这是⼀个外部变量的标号,不是在本程序定义的EXPORT ,表⽰本程序⾥⾯⽤到的变量提供给其他模块调⽤的。

以上两个在汇编和C语⾔混合编程的时候⽤到。

2、AREA语法格式:AREA 段名属性1 ,属性2 ,……AREA伪指令⽤于定义⼀个代码段或数据段。

其中,段名若以数字开头,则该段名需⽤“|”括起来,如:|1_test|。

属性字段表⽰该代码段(或数据段)的相关属性,多个属性⽤逗号分隔。

常⽤的属性如下:— CODE 属性:⽤于定义代码段,默认为READONLY 。

— DATA 属性:⽤于定义数据段,默认为READWRITE 。

— READONLY 属性:指定本段为只读,代码段默认为READONLY 。

— READWRITE 属性:指定本段为可读可写,数据段的默认属性为READWRITE 。

— ALIGN 属性:使⽤⽅式为ALIGN表达式。

在默认时,ELF(可执⾏连接⽂件)的代码段和数据段是按字对齐的,表达式的取值范围为0~31,相应的对齐⽅式为2表达式次⽅。

— COMMON 属性:该属性定义⼀个通⽤的段,不包含任何的⽤户代码和数据。

各源⽂件中同名的COMMON段共享同⼀段存储单元。

⼀个汇编语⾔程序⾄少要包含⼀个段,当程序太长时,也可以将程序分为多个代码段和数据段。

使⽤⽰例:AREA Init ,CODE ,READONLY ; 该伪指令定义了⼀个代码段,段名为Init ,属性为只读。

3、LDR、LDRB、LDRHARM微处理器⽀持加载/存储指令⽤于在寄存器和存储器之间传送数据,加载指令⽤于将存储器中的数据传送到寄存器,存储指令则完成相反的操作。

常⽤的加载存储指令如下:— LDR 字数据加载指令— LDRB 字节数据加载指令— LDRH 半字数据加载指令1) LDR指令有两种⽤法:a、ldr加载指令LDR指令的格式为:LDR{条件} ⽬的寄存器,<存储器地址>LDR指令⽤亍从存储器中将⼀个32位的字数据传送到⽬的寄存器中。

ARM汇编指令集

ARM汇编指令集ARM处理器是一种广泛使用的微处理器架构,它被广泛应用于手机、数字嵌入式设备和其他许多领域。

本文将重点介绍ARM汇编指令集的基础知识和常用的指令集。

ARM指令集ARM指令集可分为三个不同的版本:ARMv6指令集,ARMv7指令集和ARMv8指令集。

最新的ARMv8指令集是对先前版本的扩展,其扩展了指令集,增加了更先进的功能。

在本文中,我们将主要关注ARMv7指令集。

ARMv7指令集分类ARMv7指令集被分为三类: A、R和T系列指令。

下面列出了它们的一些主要功能:•A系列指令集:用于应用程序,包括浮点运算指令。

•R系列指令集:用于实时操作系统,包括分支和比较指令。

•T系列指令集:用于低功耗嵌入式设备。

ARMv7常用指令下面是一些常用的ARMv7指令:1.加法指令ADD Rd, Rn, Operand2指令将目标寄存器Rd设置为Rn和Operand2的和。

2.减法指令SUB Rd, Rn, Operand2指令将目标寄存器Rd设置为Rn减去Operand2的差。

3.逻辑运算指令AND Rd, Rn, Operand2ORR Rd, Rn, Operand2AND指令将目标寄存器Rd设置为Rn与Operand2的按位与。

ORR 指令将目标寄存器Rd设置为Rn与Operand2的按位或。

4.移位指令ASR Rd, Rn, Operand2LSL Rd, Rn, Operand2LSR Rd, Rn, Operand2ROR Rd, Rn, Operand2这是移位指令的几种不同类型。

ASR指令将目标寄存器Rd设置为Rn右移Operand2位之后的值。

LSL指令将目标寄存器Rd设置为Rn左移Operand2位之后的值。

LSR指令将目标寄存器Rd设置为Rn右移Operand2位之后的值。

ROR指令将目标寄存器Rd设置为Rn循环右移Operand2位之后的值。

5.分支指令branch label分支指令跳转到指定标签处的指令。

ARM 内核寄存器 和 基本汇编语言讲解

ARM 内核寄存器和基本汇编语言讲解•一、ARM内核寄存器▪ 1.1 M3/M4内核寄存器▪ 1.2 A7内核寄存器▪ 1.3 ARM中的PC指针的值•二、ARM汇编语言▪ 2.1 ARM汇编基础▪ 2.2 汇编伪指令▪ 2.3 ARM汇编指令集•三、代码反汇编简析▪ 3.1 不同编译器的反汇编▪ 3.2 C 和汇编比较分析开头直接来看几个简单的汇编指令:MOV R0,R1MOV PC,R14上面的指令中使用了汇编MOV指令,但是其中的R0,R1,R14,PC分别是什么?哪来的?怎么用?要讲ARM 汇编语言,必须得先了解ARM的内核寄存器,内核处理所有的指令计算,都需要用到内核寄存器,所以ARM汇编里面指令大都是基于寄存器的操作。

文章前推荐韦东山老师的单片机核心视频,视频可以在韦东山老师官网里面找到:百问网ARM版本简单介绍:对于M3/M4而言:R13,栈指针(Stack Pointer)•R13寄存器中存放的是栈顶指针,M3/M4 的栈是向下生长的,入栈的时候地址是往下减少的。

•裸机程序不会用到PSP,只用到MSP,需要运行RTOS的时候才会用到PSP。

•堆栈主要是通过POP,PUSH指令来进行操作。

在执行PUSH 和 POP 操作时, SP 的地址寄存器,会自动调整。

R14 ,连接寄存器(Link Register)•LR 用于在调用子程序时存储返回地址。

例如,在使用BL(分支并连接,Branch and Link)指令时,就自动填充 LR 的值(执行函数调用的下一指令),进而在函数退出时,正确返回并执行下一指令。

如果函数中又调用了其他函数,那么LR将会被覆盖,所以需要先将LR寄存器入栈。

•保存子程序返回地址。

使用BL或BLX时,跳转指令自动把返回地址放入r14中;子程序通过把r14复制到PC来实现返回•当异常发生时,异常模式的r14用来保存异常返回地址,将r14如栈可以处理嵌套中断R15,程序计数器(Program Count)•在Cortex-M3中指令是3级流水线,出于对Thumb代码的兼容的考虑,读取pc时,会返回当前指令地址+4的值。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

[Rn, offset ] [Rn, offset ]! [Rn], offset

•

Memory Reference must be word aligned

Load / Store Byte

•

Load Register with unsigned Byte from memory

Load Register Store Register

Rd, Rd, Rd,

Load Register unsigned Byte Load Register Signed Byte Store Register Byte

Rd, Rd, Rd,

Load Register unsigned Halfword Load Register Signed Halfword Store Register Halfword

Rd, Rm, Rs Rd, Rn, Rd, Rn,

op1 op1

Summary: Memory Access

LDR cc STR cc LDR cc B LDR cc SB STR cc B LDR cc H LDR cc SH STR cc H

Rd, Rd,

op2 op2 op2 op2 op2 op2 op2 op2

Systems Architecture

ARM Instruction Set

Data, Arithmetic and Memory Access

Notations

Rd Destination register d d may be any register R0 – R15 Condition Code Instruction executed under condition Set Condition Codes Instruction sets condition for cc Data-Processing Addressing Mode Immediate / Register / Scaled Memory Access Addressing Mode Offset / Pre-indexed / Post-Indexed

•

Division There is no division instruction

Advanced Arithmetic

• •

Used to calculate values larger than 32-Bits Split value into 32-bit sections Start with the least signification section and work up to the most signification section, using the Carry to bridge sections Add with Carry

• •

Store Register in a Halfword of memory STR cc H Rd, op2 cc : M( op2 ) Memory Reference must be Halfword aligned

← Rd(15:0)

Summary: Movement/Arithmetic

•

Subtraction

SUB cc S

Rd, Rn,

op1

cc

cc : S :

•

Multiplication

MUL cc S

Rd, Rn, Rs cc

cc : S :

Multiplying two 16-bit values (Rn and Rs), produces a 32-bit result (Rd)

cc

S

op1

op2

Instruction Encoding

MOVS

31 · · · 28 cc 000 cc opcode S 24 · · · 21 opcode 20 S 0000

R0, R1

15 · · · 12 Rd 00000000 3···0 Rm

Always = 1110 (0xE) Ignore condition code – Always execute Move = 1101 (0xD) This is a “Move” operation True (1) Set the condition codes (N and Z) N is true if value is Negative Z is true if value is Zero R0 = 0000 Destination Register R1 = 0001 Source Register

MOV Move value MOVS Move value and set condition codes MOV cc S

cc Rd,

op1

cc : Rd ← op1 S : CPSR ← ALU(Flags)

• •

Rd is the destination (must be a register) op1 is the source, may be any of the DataProcessing addressing modes:

Data Movement

MOV cc S

Arithmetic

Rd,

op1

Move Data

ADD cc S SUB cc S MUL cc S ADC cc S SBC cc S

Rd, Rn, Rd, Rn,

op1 op1

Add Subtract Multiply Add with Carry Subtract with Carry

•

ADC cc S

Rd, Rn, op1 cc : Rd ← Rn + op1 cc S : CSPR ← ALU(Flags)

+ CSPR(C)

•

Subtract with Carry SBC cc S Rd, Rn, op1 cc : Rd ← (Rn − op1 ) − CSPR(C) cc S : CSPR ← ALU(Flags)

Memory Access

•

Load Register from memory LDR cc Rd, op2 Store Register in memory STR cc Rd, op2

cc : Rd

← M( op2 )

•

cc : M( op2 ) ← Rd

•

op2 is memory reference, may be any of the Memory Access addressing modes:

Immediate Register Scaled Immediate Scaled Register

#nnn Rn Rn, shift #nnn Rn, shift Rs

Arithmetic

•

Addition

ADD cc S

Rd, Rn,

op1

cc

cc : S :

Rd ← Rn + op1 CPSR ← ALU(Flags) Rd ← Rn − op1 CSPR ← ALU(Flags) Rd ← Rn × Rs CSPR ← ALU(Flags)

Rd Rm

Instruction Groups

1 2 3 4 5 6 Data Movement Arithmetic Memory Access Logical Flow Control System Control

Data Movement

• • •

50% to 70% of a program

Barrel Shifter

IR

Control Unit

CPSR

32-Bit ALU

LDR cc B

Rd,

op2

cc : Rd(7:0) cc : Rd(31:8)

← M( op2 ) ←0

•

Load Register with Signed Byte from memory

LDR cc SB

Rd,

op2

cc : Rd(7:0) cc : Rd(31:8)

← M( op2 ) ← Rd(7)

External Memory

MAR: Memory Address Register

MBR: Memory Buffer Register

Address Incrementer

R15 / PC

R14 / LR

R13 / SP

R11

R10 R9 R8

R7

R6 R5 R4

R3

R2 R1 R0

R12

User Registers Booth&#re Register in a Byte of memory STR cc B Rd, op2 cc : M( op2 ) ← Rd(7:0)

Load / Store Halfword

• • •

Does not work in the ARMulator An ARM word is 32-bits, so a Halfword is 16-bits Load Register with unsigned Halfword from memory

LDR cc H

Rd ,

op2

cc : Rd(15:0) ← M( op2 ) cc : Rd(31:16) ← 0

•

Load Register with Signed Halfword from memory

LDR cc SH

Rd ,

op2

cc : Rd(15:0) ← M( op2 ) cc : Rd(31:16) ← Rd(15)