第六章 dc_shell综合脚本

利用DC 进行逻辑综合(DC课件整理)

1.1概述

芯片综合的过程:芯片的规格说明,芯片设计的划分,预布局,RTL 逻辑单元的 综合,各逻辑单元的集成,测试,布局规划,布局布线,最终验证等步骤。设计 流程与思想概述:一个设计从市场需求到实际应用需要运用工程的概念和方法加 以实现,这需要工程人员遵循一定的规则按一定的设计步骤进行操作。下面我们 给出了一个设计工程通常的工作步骤(请参见设计流程图)。从图中可以看出对 一个完整的设计流程来说,可以将工作划分为两个阶段:前段设计和后端设计。 前端工作主要完成 IC 与通讯整机设计接口问题,以及整个 IC 的内部总体结构设 计;而后端工作则主要是在前段设计的基础上,使用 EDA 工具,遵循设计流程, 完成整个 IC 设计。 1.1.1 逻辑综合简介

Synopsys 的 EDA 软件支持许多变量、对象、和综合流程中的各种属性,使用 这些元素设计者可以写出强有力的综合脚本,完成自动综合的过程。因此必须熟 悉这些术语。设计对象包括以下几个: 1)设计(Design):

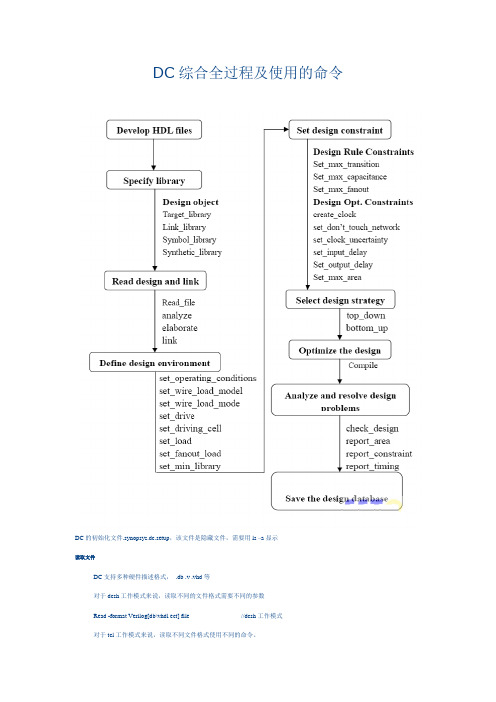

DC综合全过程及使用的命令

DC综合全过程及使用的命令DC的初始化文件.synopsys.dc.setup,该文件是隐藏文件,需要用ls –a显示读取文件DC支持多种硬件描述格式,.db .v .vhd等对于dcsh工作模式来说,读取不同的文件格式需要不同的参数Read -format Verilog[db\vhdl ect] file //dcsh工作模式对于tcl工作模式来说,读取不同文件格式使用不同的命令。

Read_db file.db //tcl工作模式读取db格式Read_verilog file.v //tcl工作模式读取verilog格式Read_vhdl file.v //tcl工作模式读取vhdl格式读取源程序的另外一种方式是配合使用analyzer命令和elaborate命令;Analyzer是分析HDL的源程序并将分析产生的中间文件存于work(用户可以自己指定)的目录下Elaborate则在产生的中间文件中生成verilog的模块或者VHDL的实体缺省情况下,elaborate读取的是work目录中的文件当读取完所要综合的模块后,需要使用link命令将读到DC存储区中的模块或实体连接起来注意:如果在使用link命令后,出现unresolved design reference的警告信息,需要重新读取该模块,或者在.synopsys_dc.setup 文件中添加link_library,告诉DC到库中去找这些模块,同时还要注意search_path中的路径是否指向该模块或单元电路所在的目录Link命令执行后,DC就将模块按照RTL级或者门级的描述将电路连接起来,之后的各种限制条件就可以对该电路的顶层模块施加DC限制条件施加的对象针对以下电路成分:输入输出端口、模块、子模块的实例化、单元电路、连线及电路的引脚。

在使用DC命令的时候,不要使用模糊的对象,例如,如下面的电路:Set_load 3 Clk由于在电路中含有名称为CLK的pin、port和net,因此,DC无法知道该处的load是施加在哪个对象上,注意到一般连线会驱动负载,该命令就改为:Set_load 3 [get_nets Clk] TCL modeSet_load 3 find(net,”Clk”)dc_shell mode路径的划分与合法路径DC综合的时候是基于路径的优化,对于DC来说,合法的路径必须满足以下条件路径的起点为输入端口或者是触发器的数据端路径终点为输出端口或者是触发器的时钟端DC设定的限制条件的值都是无单位的,这些单位都是由工艺库中给定的可以用report_lib lib_name来查看所有在工艺库中设定的各个参数的单位定义电路的工作环境和综合环境1.Set_operating_conditions不同的工作环境对应的单元电路的延迟不相同温度升高、电压降低、电路的特征线宽增大都会使得单元电路的延迟增大电路的工作环境一般在工艺库中都有给定命令格式:set_operating_conditions [–min min_condition] [–max max_condition] [-min_library min_lib] [–max_library max_lib]命令使用说明指定DC进行优化时使用的工作环境,其中工作环境的指定必须在库中指定,或者在link_library中的其中一个库中指定,如果不指定operating_conditions,DC自动搜索link_library中的第一个库的工作环境作为优化时使用的工作环境可以用get_attributes语句取得库中缺省的工作环境-max选项指定电路最大延迟分析(分析电路是否满足触发器建立时间set up的要求)的工作环境-min选项用于指定电路最小延迟分析(分析电路是否满足触发器保持时间hold time的要求)的工作环境,该选项不能单独使用,必须与-max同时使用如果不指定用于分析最小延迟的库,则只使用-max中指定的库用于电路的延迟分析-min_library选项指定用于电路最大延迟分析的工艺库-max_library选项指定用于电路最小延迟分析的工艺库2.set_min_libraryVendor可能提供多个不同的工艺库,用于分析电路的时序,不同工艺库定义了不同的工作环境、不同的线负载模型、不同的单元延迟时间,这是可以将这些苦都指定用于分析电路的延迟命令格式:set_min_library max_library –min_version min_library | -none命令的使用说明:该命令指定max_library用于分析电路的最大延迟,min_library用于分析电路的最小延迟。

启动dc_shell工具的.synopsys.setup文档

设置启动dc_shell-t工具的.synopsys.setup文件Author:周建伟Company:西安邮电大学SOC组Date:2013.10.30摘要:若你在读不进你的库,即在你的运行报告中总是有:warning:Can‟t read link_library file …your_library.db‟,这边文档会对你有一定的帮助逻辑综合环境启动文件启动文件用来指定综合工具所需要的一些初始化信息。

DC使用名为“.synopsys_dc.setup”的启动文件(位置:inst_dir/admin/setup/.synopsys_dc.setup)。

启动时,DC会以下述顺序搜索并装载相应目录下的启动文件:DC安装目录($DC_PATH/admin/setup)用户主目录工具启动目录注意:后装载的启动文件中的设置将覆盖先装载的启动文件中的相同设置本文档重在讲述怎么设置工具启动目录1、把inst_dir/admin/setup/.synopsys_dc.setup文件拷贝到你DC脚本目录下(也就是和你脚本在同个目录下)2、在.synopsys_dc.setup文件的第92行,即set link_force_case “check_reference”命令下修改内容如下:A、set lib_path /library/smic18/feview~2/version2.2(注:lib_path为你smic18库安装目录,不同于DC安装目录)B、set link_library [list * $lib_path/STD/Synopsys/smic18_ss.db \$lib_path/IO/Synopsys/smic18IO_line_ss.db \$lib_path/IO/Synopsys/smic18IO_stagger_ss.db ]C、set search_path [list . ${synopsys_root}/libraries/syn ${synopsys_root}/dw/syn_ver \${synopsys_root}/dw/sim_ver \$lib_path/STD/Synopsys $lib_path/IO/Synopsys ]D、set target_library [list $lib_path/STD/Synopsys/smic18_ss.db \$lib_path/IO/Synopsys/smic18IO_line_ss.db \$lib_path/IO/Synopsys/smic18IO_stagger_ss.db ]E、set synthetic_library “”set command_log_file “./command.log”set designer “zjw”set company “soc of xupt”set find_converts_name_lists “false”F、set symbol_library $lib_path/STD/Symbol/synopsys/smic18.sdb。

高级asic芯片综合.doc

高级ASIC芯片综合翻译者:阿信使用Synopsys公司的Design Compiler Physical Compiler 和PrimeTime第二版目录写在前面前言前言事实证明,相对于集成电路IC设计规模半导体产业是相对??。

作为一个团体,80年代中期,每个芯片集成了大约1000个晶体管,我们称之为大规模集成电路(LSI),仅仅在大约两年后,每个芯片的晶体管集成数量就达到了1万~10万个,我们所用的术语也迅速的变成了甚大规模集成电路(VLSI)。

Preface 前言这本书的第二版描述了一些使用Synopsys公司的一套工具在ASIC芯片设计中的高级概念和技术,包括ASIC芯片综合,物理综合,形式验证和静态时序分析等。

另外,对ASIC的整个设计流程和沈亚微米(Very-Deep-Sub-Micron)设计技术作了详细的介绍。

这本书的重点是在Synopsys 工具的实时使用上,用工具去解决在深亚微米尺寸领域的各种问题。

将展示给读者解决在亚微米ASIC设计复杂问题的有效设计方法。

重点就在HDL的编码风格,综合和优化,动态仿真,形式验证,可测性设计DFT扫描链的插入,版图设计的连接,物理综合和静态时序分析。

在每一步,确定设计流程中每一段的问题,问题的解决方法并围绕此问题展开详细的论述。

另外,关于版图设计的关键问题,比如时钟的综合和最后的集成也作了较长篇幅的讨论。

最后,这本书深入的讨论了基本的Synopsys技术库和编码风格,综合优化技术。

这本书的读者对象是刚刚工作的ASIC设计工程师和学习过ASIC大规模集成电路设计与可测性设计课程的高年级学生。

这本书并不是想取代Synopsys的参考手册,而是为任何参与ASIC设计的人员而写。

同时,这本书对那些没有版图能力或者自己有技术库但是需要其他公司来做后端集成和最终制造器件的计者(和公设司)都是很有用。

因为到深亚微米技术会遇到各种各样的问题,本书提供了可选择的;这本书同时也介绍了设计人员对不同EDA工具商提供的各种工具时所面临常见问题的解决方法。

shell脚本教程详细讲解(很好)

2021/10/10

19

2、一般步骤: (1)编辑文件 (2)保存文件 (3)将文件赋予可执行的权限 (4)运行及排错

2021/10/10

20

注意:

1. 一般以.sh为文件后缀。没有也能执行。 2. 常见的两种执行方式

./文件名 在当前目录下写明路径执行,要求文 件必须有执行权限,如 chmod 755 run.sh ./run.sh

} echo "programme starts here..." 主过程

sayhello

echo "programme ends."

2021/10/10

22

二、Shell中的特殊符号

1、注释符#

除了#!/bin/bash里的#特殊

2、美元符 $

变量符。与反斜杠转义符相反,使其后的普通字符作 为变量名,如$a表示变量a的值。变量字符长度超 过1个时,用{}括起来

2021/10/10

13

7、设置vi

全局的配置文件位于/etc/vim/vimrc(或者/etc/vimrc) 也可以拥有自己独立的配置文件,配置文件位

“~/.vimrc”,如果没有该文件,也可以直接用如下命 令创建并编辑 比如: set nu ‘显示行号 set ruler ‘显示光标位置 set undolevel ‘显示光标位置 set smartindent ‘智能缩进 syntax on(或syn on) ‘语法高亮

把文档中所有SEARCH替换成REPLACE;

:#,# s /SEARCH /REPLACE /g

#号表示数字,表示从多少行到多少行,把 SEARCH替换成REPLACE;

:s /SEARCH /REPLACE /g

shell脚本语言

∙Shell简介∙几种常见的Shell∙Shell脚本语言与编译型语言的差异∙什么时候使用Shell∙第一个Shell脚本∙Shell变量∙Shell特殊变量∙Shell替换∙Shell运算符∙Shell注释∙Shell字符串∙Shell数组∙Shell echo命令∙shell printf命令∙Shell if else语句∙Shell case esac语句∙Shell for循环∙Shell while循环∙Shell until循环∙Shell break和continue命令∙Shell函数∙Shell函数参数∙Shell输入输出重定向∙Shell文件包含Shell简介:什么是Shell,Shell命令的两种执行方式Shell本身是一个用C语言编写的程序,它是用户使用Unix/Linux的桥梁,用户的大部分工作都是通过Shell完成的。

Shell既是一种命令语言,又是一种程序设计语言。

作为命令语言,它交互式地解释和执行用户输入的命令;作为程序设计语言,它定义了各种变量和参数,并提供了许多在高级语言中才具有的控制结构,包括循环和分支。

它虽然不是Unix/Linux系统内核的一部分,但它调用了系统核心的大部分功能来执行程序、建立文件并以并行的方式协调各个程序的运行。

因此,对于用户来说,shell是最重要的实用程序,深入了解和熟练掌握shell 的特性极其使用方法,是用好Unix/Linux系统的关键。

可以说,shell使用的熟练程度反映了用户对Unix/Linux使用的熟练程度。

Shell有两种执行命令的方式:∙交互式(Interactive):解释执行用户的命令,用户输入一条命令,Shell 就解释执行一条。

∙批处理(Batch):用户事先写一个Shell脚本(Script),其中有很多条命令,让Shell一次把这些命令执行完,而不必一条一条地敲命令。

Shell脚本和编程语言很相似,也有变量和流程控制语句,但Shell脚本是解释执行的,不需要编译,Shell程序从脚本中一行一行读取并执行这些命令,相当于一个用户把脚本中的命令一行一行敲到Shell提示符下执行。

dc使用教程

d c使用教程-CAL-FENGHAI.-(YICAI)-Company One1DC使用说明文件说明:在进行下面的演示时需要用到两个文件,一个是,它是描述一个电路的verilog代码,我们的目标就是用DC综合这个代码得到满足约束条件的电路网表;另一个是,它是综合的脚本文件。

这两个文件都在/home/student1000目录下,大家把它们拷贝到自己的目录下,以备使用。

DC既可使用图形界面,也可不使用图形界面而直接运行脚本来综合电路。

一、DC图形界面的使用。

1.DC图形界面的启动打开一个终端窗口,写入命令 dv –db_mode,敲入回车。

则DC图形界面启动,如下图所示红框处是DC的命令输入框,以下在图形界面上的操作都可以在命令输入框中输入相应的命令来完成。

选择Help-----Man Pages可以查看DC的联机帮助。

相应指令:man。

例:man man表示查看man命令的帮助。

man create_clock表示查看creat_clock命令的帮助。

2.设置库文件选择File----Setup需要设置以下库文件,如下图。

相应指令:set search_path [list /tools/lib/smic25/feview_s/version1/STD/Synopsys \ /tools/lib/smic25/feview_s/version1/STD/Symbol/synopsys]set target_library { }set link_library { }set symbol_library { }点OK,设置完成。

3.读入verilog文件选择File---Read在打开文件对话框中选中要打开的文件,在这里我们选中文件。

在Log框中出现successfully字样表明读入文件成功。

相应命令:read_file点击红色箭头所指的按钮可以查看该电路的symbol图。

4.设置约束条件4.1设置时钟约束在symbol图上选中clk端口选择Attributes-----Specify Clock出来设置时钟约束的对话框,按下图设置,给时钟取名为clock,周期20ns,上升沿0ns,下降沿10ns。

学习使用Shell脚本编程进行自动化任务和系统管理

学习使用Shell脚本编程进行自动化任务和系统管理Shell脚本是一种能够自动执行一系列命令的脚本语言,在Linux和UNIX系统中被广泛使用。

通过编写Shell脚本,可以实现自动化任务和系统管理,提高工作效率和减少人力成本。

本文将按照以下几个章节进行讲解。

第一章:Shell脚本的基础知识Shell脚本是由一系列Shell命令组成的文本文件,可以通过解释器来执行。

常见的解释器有bash、csh、ksh等。

在编写Shell脚本之前,我们需要了解一些基础知识,比如如何声明变量、如何进行条件判断和循环等。

只有掌握了这些基础知识,才能更好地进行Shell脚本编程。

第二章:Shell脚本的文件操作在日常工作中,我们经常需要进行文件的复制、移动、删除等操作。

通过Shell脚本,我们可以完成这些繁琐的文件操作。

在本章中,将介绍如何使用Shell脚本进行文件的创建、复制、重命名等操作。

同时,还将介绍如何使用正则表达式来匹配文件名,实现批量操作。

第三章:Shell脚本的系统管理Shell脚本不仅可以用来操作文件,还可以用来进行系统管理。

比如,我们可以通过Shell脚本来创建用户、设置权限、安装软件等。

本章将详细介绍如何使用Shell脚本来进行系统管理,包括如何添加新用户、如何创建和管理进程等。

第四章:Shell脚本的网络管理随着互联网的快速发展,网络管理变得越来越重要。

通过Shell 脚本,我们可以实现对网络的监控和管理。

本章将介绍如何使用Shell脚本来进行IP地址管理、路由管理、网络流量监控等操作。

同时,还将介绍如何通过Shell脚本实现远程登录和文件传输。

第五章:Shell脚本的定时任务定时任务是指在特定的时间或条件下自动执行某个任务。

通过Shell脚本,我们可以实现定时任务的自动化。

本章将介绍如何使用Shell脚本来实现定时任务,包括如何设置定时任务的时间、如何执行定时任务的命令等。

第六章:Shell脚本的错误处理和日志记录在编写Shell脚本时,我们经常会遇到一些错误。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第六章dc_shell命令解释程序第一节设计目标6-1-1背景介绍dc_shell 是Synopsys Design Compiler的shell(命令解释程序),与unix的shell 类似。

Unix的C shell 和Bourne-shell作为命令解释程序,在用户和unix 核之间实现了功能极强的接口程序。

相同地,Dc_shell最为Synopsys Design Compiler的功能极强的命令解释程序。

象unix shell 提供程序设计语言在unix 文件系统中操作一样,dc_shell 提供script(脚本)语言在Design Compiler 的设计中操作,且仿造unix shell 的相同的结构。

用dc_shell 脚本综合设计有许多优点:首先,脚本执行速度比象design analyzer 交互式的界面快得多,脚本也用来证明综合设计的过程。

更重要的是,脚本提供一个重复编译的机制,这不仅对设计的再利用重要,而且对于当要求一项函数改变时,再次产生设计文件的所要求的时间最小化也很重要。

所有的这些优点源于使用脚本自动走完综合流程。

但是,dc_shell 脚本能够做的远不只这些,它能扩展Design Analyzer和Design Compiler的功能。

一些Design compiler命令的顺序由脚本得出。

大多数经验丰富的Synopsys的用户将脚本和Design analyzer结合使用来分析和优化设计。

6-1-2 目标程序类型的审阅dc_shell脚本生成设计目标程序和编译属性来引导综合流程。

当编写dc_shell脚本时,考虑正在运行的目标程序/信息的类型是很重要的。

这一节从“Design Compiler Family Reference Manual”的章节中总结了“design compiler”的概念。

6-1-2-1 实例、网络、端口原理图由三个基础的构件组成:实例、网点、端口。

实例是代表逻辑子程序或层次的符号,网络是代表在实例之间有电气连续性的导线,端口是用来代表层次连续性的线路终结器。

这些都是标准的术语。

使设计者感到新颖的是reference 的概念。

6-1-2-2 单元、引用、设计如果一实例代表一逻辑子程序,则它能代表什么类型的子程序呢?一实例能代表一库元件或一设计。

用许多术语描述设计是必须的因为一设计可能包含同一库元件(或子设计)的多重实例。

举例说,一典型设计包含与非门,设计中的每一门实例都被赋予唯一的单元名用来在非唯一的实例中彼此区分。

同样的,一设计可能包含多个加法器,与与非门不同,加法器一般来说不是库元件,加法器是一个可逐步分解成库元件和网络且相互连接后执行加法器功能的完全设计。

与库元件相同,每一子设计的实例都被赋予唯一的单元名。

库元件是无形的设计子程序且在设计中常被做为节点单元引用。

设计是逻辑块,它们可作为独立的设计或作为更大设计的子设计。

作为其它设计中连接上下关系的子模块,设计中每一个唯一的实例被作为一个分层次的单元引用。

在一个单独设计的上下关系中,每一个实例具有唯一的单元名,这些单元引用库元件或设计。

设计者可以对每个单元单独地进行优化,也可以通过布置属性或约束(在以下定义)对每个库元件或设计进行优化。

但是,属性被直接加至库元件或设计中,这可能影响包含引用这些库元件或设计的每一个设计。

图6.1 单元、引用、设计之间的关系假设你想要影响一个单独设计中的每一个与非门的优化而没有影响其它设计中的与非门则将会如何呢?引用的概念使这成为可能,设计中的每一个单元不仅是库元件中或设计中唯一命名的实例,而且是引用库元件或设计的一系列单元中的一员。

参考以下图6.2的设计:图6.2脉动计数器:count_16这个分层次设计的顶层是一个16位的计数器,顶层设计由与非门、或非门、8位计数器组成。

在这层次设计的关系中,有6个单元、3个引用、2个设计。

这些单元是u1、u2、u3、u4、u5、u6,引用是一个三输入与非门、一个三输入或非门和一个count8的设计。

设计包含count6和count8的设计。

第二节收集和控制信息一些dc_shell的构件是用来收集和控制信息。

变量和属性是特殊方法、指定设计信息的主要知识宝库。

别名提供创建自定义的命令或改变一个命令的行为的技巧。

如find、filter、list命令对提取变量或设计目标程序中的信息有相当大的作用。

6-2-1 变量:储存信息变量在dc_shell的章节中用来存储信息。

一些变量被事先定义了,它们对于desing compiler 有特殊的意义。

比如search_path这一变量,告诉design compiler 到哪里去找Unix文件系统下的用户的设计文件及库。

事先定义的变量分为11组。

组是组织变量履行相似功能的便捷方法。

比如说,系统组的变量包含design compiler 用来和Unix交互的信息。

由于变量可被任意分配给哪个组,所以可用group_variable命令创建或改变组。

表6.1列出11个事先定义好的组以及组包含的变量举例。

的单词一个值时,变量则自动产生了。

选择一个没有保存过的名字代表呢想要保存的值,然后使它与值相等,创建变量的句法与改变变量值的句法相同,给variable_name=value。

6-2-1-1变量介绍所有的dc_shell变量都是全局的dc_shell变量。

变量不和设计数据库一起保存,一旦一段dc_shell结束了,所有在这段赋值的变量都不存在了。

所有的变量都是全局变量,没有局部变量(对当前脚本或当前设计使关系独立的)。

变量是严格分类的,也就是说,当一个变量创建后,它将保存某一类型的值。

变量能保存字符串、数字(整型或浮点型)、设计目标程序或列表。

设计目标程序包括设计、库、端口、总线、管脚、单元、引用、网络、时钟、根目录(也称为DB文件)。

列表是一组字符串、数字,设计目标程序可能在列表中被混淆。

一旦变量被创建后用来保存某一类型的值时,它只能被赋予那种类型的值。

如果两个脚本用相同的变量名来引用不同类型的信息,那么两个脚本是不相容的。

在这种情况下脚本是不相容的,而且在相同的dc_shell端不能共存。

当脚本赋予一个已存在的变量一个错误类型的值,将会报错且脚本会退出。

然而这种情况是容易避免和改正的。

首先,选择有代表性的要保存的值的类型以及要保存的值的含义来创建变量。

比如说,如果你想要保存当前驻留在内存中的设计列表时,你会键入:active_design_list=find(design,”*”),这命令搜寻所有驻留在内存中的设计并保存列表到active_design_list变量中(此例中的find命令将在以后做详细解释)。

其次,若你想用存储错误类型的变量,则删除此变量,然后保存需要的类型。

Remove_variable variable_name;variable_name=value.变量能维持设计具有唯一的性能。

如果在变量中存储的设计从内存中被删除了,那么也将从变量中被删除。

无论变量维持一设计还是包括设计的列表,这都是正确的。

以下的例子帮助阐明这种特性的原因。

启动dc_shell(或从design analyzer的命令窗口启动),读入设计,键入以上命令来初始化active_design_list变量。

List新变量查看它的内容,即list active_design_list。

active_design_list变量保存内存中所有变量的列表。

要从内存中删除一个设计,利用你刚才创建的变量来删除内存中所有的设计,即remove_design active_design_list。

发出以下的命令来验证当一个设计从内存中删除时,它们将从所有的变量中删除:find design“*”list active_design_list为什么会发生这种情况?当设计从内存中删除时design compiler 删除了所有的引用,这保证未来的命令对不存在的设计目标程序不产生操作(一项实践操作可能对当前的dc_shell产生致命的牵连)。

6-2-1-2 事先定义的变量这节描述一些重要的事先定义的变量。

1、dc_shell_status每次dc_shell命令执行时,一个值返回到命令窗口(在命令提示之前立即返回)。

对于大多数命令来说,这值是整型的。

如果命令成功地完成了,则返回1,否则返回0。

返回值不只返回到命令窗口,它也赋予变量dc_shell_status。

这使调节后来命令的执行结果与前面命令执行结果一致成为可能。

这种特性的流程控制含意详细地描述如下。

不是所有地命令都返回一个整型值,举例说,find命令返回一个值地列表。

为了适应象这样的命令,dc_shell_status变量没有严格分类。

这种特性非常功能非常强大,但它要求设计者在利用dc_shell_status写脚本时清楚要返回dc_shell_status变量的类型。

2、current_design大多数命令、约束、属性不像变量,它们没有全局的含义。

大多数命令对current_design是指定环境的。

基本说来,设计是可独立编译的单元,current_design变量告诉design compiler编译哪个设计。

象compile命令,大多数命令在current_design变量的环境中操作。

这对于design compiler的初学者来说是容易混淆的地方因为所有设计都彼此独立存在。

从技术上来说,一个设计可能包含另一个设计的引用,但它不会全部包含那个设计。

对于高层设计来说,引用的设计是独立存在的。

考虑前面介绍过的16位的计数器。

发出命令current_design count8,则接下来的所有的命令应用于8位的计数器而不是16位的计数器。

8位计数器可能在几个可能包含或不包含16位计数器的设计中被用到,在这种情况下,16位计数器是32位计数器的子设计吗?它能作为一个32位设计的实例,但它一直都作为一个16位的计数器而独立存在的(除非设计取消组)。

有两个原因希望指定设计的引用和独立设计之间存在差异。

首先,它促进了设计的重复利用;其次,它提供了有细密纹理的优化的机制。

在大型设计中,一些子模块可能对时间有严格的要求而另一些子模块可能对面积有严格的要求,通过定义每一子模块为一个设计,那么子设计能够单独地优化从而满足它们单独的设计目标。

3、current_instance和current_reference设计者通常希望在current_design层次中进入一实例从而应用约束条件或观察层次路径的时序。

current_instance 命令允许设计者在不改变current_design的情况下改变特定实例命令的层次重点。