2014年辽宁省电赛E题报告--FPGA部分

2014电子设计大赛

2014年全国大学生电子设计竞赛(D题)编号:题目:电能消耗计量装置 (D题)学校:学院:信息科学与电气工程学院参赛学生:联系方式:2014年月日电能消耗计量装置的设计报告摘要:本设计以ATMEGA16A为控制核心,通过交流整形电路连接AD637KQ真有效值转换芯片量锰铜电阻,实现负载电流有效值检测;市电电压有效值的监测是通过连接市电电压的负载分压之后,由AD637KQ真有效值转换器实现测量;通过功率因数测量电路,市电电压经过二极管电桥正弦波变为方波,经单片机捕获测量出负载的功率因数和市电频率;单片机连接键盘和12864B v2.0液晶显示屏,通过中断服务模式实现控制负载用电时间、电能消耗、二氧化碳排放量的显示,以及显示市电电压有效值和市电频率、负载的工作电流有效值和有功功率、负载的功率因数;该装置还具备最大门限值设置、过流保护功能,进行了大量试验和测试,验证了设计的有效性,完成了基本部分和发挥部分功能要求。

关键词:电能消耗计量装置,ATMEGA16A,AD637,低能耗,精度1.系统方案1.1系统要求设计一款用于市电的电能消耗计量装置,该装置能耗低,由非分体式独立供电结构供电,具备过流保护功能和声光报警功能,并可设置被测负载最大门限值。

能够监测所在电网的市电电压有效值和市电频率,以及连接负载的工作电流有效值和有功功率值,并显示出负载的功率因数、用电时间和负载用电量对应的二氧化碳排放量及电能消耗值,1.2 方案论证1.2.1 控制器模块采用ATMEGA16A控制器。

ATmega 16A是基于增强的AVRRISC结构的低功耗8位CMOS微控制器。

由于其先进的指令集以及单时钟周期指令执行时间,ATmega16的数据吞吐率高达1MIPS/MHz,功能强大,性价比高,使用方便。

1.2.2电压有效值测量模块和电流有效值测量模块方案一:带有AD637KQ真有效值转换器,AD637BQ可以计算各种杂波形的真有效值,最大3dp宽带可达8MHZ,可选择测量直流信号和交流信号,带载能力强。

2014年西门子杯全国大学生工业自动化挑战赛工程应用型赛项高校组工程设计文件

2014年西门子杯全国大学生工业自动化挑战赛工程设计文件工程应用型赛项高校组参赛队伍名称:XXXXXXXX参赛学校名称:XXXXXXXX年月日一、方案设计依据、范围及相关标准二、系统分析(包括甲方需求分析、对象特性分析、系统安全分析等)三、控制系统设计(包括控制逻辑、控制回路、控制算法等的选择,开机、停机等控制逻辑以流程图表达)一、控制逻辑流程图二、控制回路三、控制算法的选择双馈机组风电场控制系统采用PI控制和HCC算法。

1、PI控制算法:发电机并网时的变桨系统功率控制功率控制系统如下图所示,它由两个控制环组成外环是功率控制环,根据发电机实际功率值调整发电机的电流设定值。

内环是一个功率伺服环,它通过转子电流控制器对发电机转差率进行控制,使发电机功率跟踪功率给定值。

如果功率低于额定功率值,这一控制环将通过改变转差率,进而改变桨叶桨距角,使风轮获得大功率。

如果功率参考值是恒定的,电流参考值也是恒定的。

变滑差发电机主要控制与输出功率成正比的转子电流。

控制器向转子电流控制器发送要求电流基准值,然后实际转子电流会与基准值比较进而做相应调整,使用IGBT 作为直流开关,用转子电流控制单元的外部转子电阻的PWM 可获得转子电流。

切换频率接近3kHz,这使得平均外部电阻在0 到100%之间几乎连续可调,发电机的转差率相应地能够从0.6%(转子自身电阻)到10%(转子电阻为自身电阻与外接电阻之和)之间连续变化。

当功率变化即转子电流变化时,PI 调节器迅速调整转子电阻,使转子电流跟踪给定值,如果从主控制器传出的电流给定值是恒定的,它将保持转子电流恒定,从而使功率输出保持不变。

与此同时,发电机转差率却在作相应的调整以平衡输入功率的变化。

2、HCC算法:HCC 算法是一种人工智能算法,可用于寻找未知函数的极大值点。

该算法最基本的思想是连续地对控制对象应用一系列规则、约束,同时检验自身的输出,确保输出逐步接近极大值。

如果利用HCC 算法寻找风力发电机组的输出功率极大值,根据偏航误差角与电机功率关系来控制偏航电机动作,可精确地实现偏航控制。

23电赛e题报告模板

23电赛e题报告模板下面是一个电赛E题报告的模板,根据具体情况可以适当调整和扩展。

报告模板:标题,电赛E题报告。

一、问题描述:在这一部分,详细描述电赛E题的问题背景和要求。

包括题目中给出的具体条件和限制,以及需要解决的具体问题。

二、问题分析:在这一部分,对问题进行深入分析和理解。

可以从以下几个角度进行分析:1. 输入输出分析,分析题目给出的输入和输出的格式、范围、约束条件等,了解问题的输入输出特点。

2. 数据结构和算法分析,分析问题的本质,确定可能用到的数据结构和算法。

可以考虑使用的数据结构包括数组、链表、栈、队列等,算法包括排序、查找、动态规划等。

3. 算法设计,根据问题的特点,设计解决问题的算法。

可以详细描述算法的思路、步骤和关键代码。

三、解决方案:在这一部分,详细描述解决问题的具体方案。

可以从以下几个方面进行描述:1. 算法实现,将算法设计转化为具体的代码实现。

可以给出伪代码或具体的编程语言代码。

2. 输入数据处理,根据题目要求,对输入数据进行适当的处理。

包括数据读取、解析和存储等。

3. 算法运行和结果分析,对实现的算法进行运行测试,并分析结果的正确性和效率。

可以给出具体的测试数据和结果展示。

四、优化改进:在这一部分,对解决方案进行优化改进。

可以从以下几个方面进行考虑:1. 时间复杂度和空间复杂度分析,分析算法的时间复杂度和空间复杂度,找出可能的优化点。

2. 算法改进,根据分析结果,对算法进行改进,提高算法的效率和性能。

3. 实验对比,对优化后的算法与原算法进行对比实验,分析改进效果。

五、总结与展望:在这一部分,对解决问题的过程进行总结,并展望未来可能的改进和发展方向。

可以对解决问题的方法和结果进行评价,并提出进一步的研究方向。

以上是一个电赛E题报告的模板,您可以根据具体情况进行适当调整和扩展。

希望对您有所帮助!。

2007全国电子设计大赛E题获奖论文报告

题目:开关稳压电源(E题)摘要本设计综合考虑题目基本部分和发挥部分的指标要求,系统采用简单的boost 升压电路作为DC-DC变换器主电路;PWM控制器采用低压型专用集成芯片UC3843; 主开关管采用IRF540;由内置12位A/D、D/A的高性能、低功耗单片机C8051F021组成系统测控与显示单元,采用液晶显示器作为系统的状态和运行数据显示屏。

通过实际测试,作品的性能指标中,输出纹波完全达到了要求;电压调整率,整体效率,负载过流故障排除后自恢复功能,输出电压键控1V步进,电流、电压实时测量及数显功能等几项指标达均到了发挥部分要求;负载调整率也接近发挥部分指标要求。

另外,系统还增加了实时输出功率数据显示和负载过流状态下的声、光报警等实用功能。

一、引言为了满足题目发挥部分规定的电压调整率、负载调整率以及效率等几项指标要求,我们在设计中主要是尽量减少辅助控制电路的损耗。

通过单片机和脉宽调制电路来稳定输出电压,并通过单片机的控制实现对整个电路的过流保护功能,排除过流故障后,电源能自动恢复为正常工作状态。

同时,当输出电压与设定电压误差较大时,单片机能对输出电压进行一定调节,以提高负载调整率;通过单片机实现了输出电压的键盘设定和步进调整(步进为1V)。

系统具有测量和数字显示输出电压、电流的功能。

此外,还增加了实时输出功率测量与显示、在输出过流的时候系统发出声、光报警信号等功能。

二、方案论证与比较1.DC-DC主回路拓扑方案论证方案一:采用变压器升压的隔离型PWM直流-直流变换器电路,此电路效率较低,开关辐射/纹波较大,电路较复杂。

方案二:采用非隔离型BOOST升压电路,控制电路用专用集成芯片UC3843A,这种电路使用的外部原件最少、调试容易、成本低、效率高。

因此,采用此种方案。

2. 控制方法及实现方案方案一:采用电压型脉宽调制技术,产生频率固定,脉冲宽度可调整的方波脉冲,采用电压反馈环控制系统,它的反馈信息取自输出电压,用反馈电压调整控制器的输出脉冲宽度,改变脉冲占空比,实现开关电源的稳定。

E题设计报告2

简易数字信号传输性能分析仪(E题)设计报告摘要:本系统利用FPGA产生m序列及其曼彻斯特编码,并产生伪随机序列作为系统的噪声,以及相应的时钟信号,由运放实现的比较器、分压器实现了曼彻斯特编码的单-双极性变换,由二阶低通滤波器和增益控制电路实现了增益可调的低通滤波器作为模拟信道,接收端的数字信号分析电路有低通滤波器、运放实现的双-单极性变换电路、FPGA实现的位同步提取电路构成,该位同步提取算法利用曼彻斯特码型特点生成位同步信号,最后将接收信号和提取出的位同步信号接到示波器,即可观察到眼图。

一、方案论证与比较1、数字信号与伪随机信号产生方案选择方案一:采用分立元件实现此方案采用分立元件构成线性移位寄存器电路,实现数字信号发生器、曼彻斯特编码器和伪随机信号发生器,以及相应的时钟信号。

此方案存在以下几个缺点:信号频率不便于调节,以至于m序列数据率步进调节不方便,且信号频率不稳定会影响序列数据率。

在传输过程中,分立器件构成的电路会对数字信号产生干扰。

方案二:采用FPGA实现此方案采用FPGA产生m序列及其曼彻斯特编码,并产生伪随机序列作为系统的噪声,以及相应的时钟信号。

此方案通过FPGA内部锁相环,能提高输入时钟信号的稳定性,且调节频率方便,产生的数字信号在传输过程中更稳定,码元数据率调节方便。

基于以上比较,选用方案二。

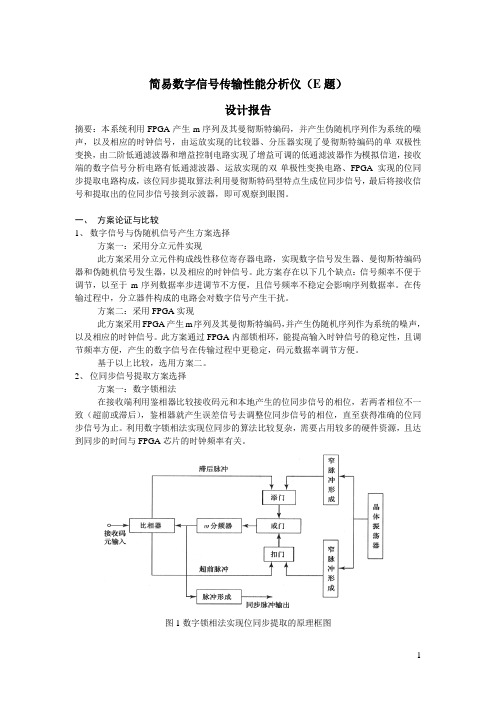

2、位同步信号提取方案选择方案一:数字锁相法在接收端利用鉴相器比较接收码元和本地产生的位同步信号的相位,若两者相位不一致(超前或滞后),鉴相器就产生误差信号去调整位同步信号的相位,直至获得准确的位同步信号为止。

利用数字锁相法实现位同步的算法比较复杂,需要占用较多的硬件资源,且达到同步的时间与FPGA芯片的时钟频率有关。

图1数字锁相法实现位同步提取的原理框图方案二:滤波法首先将单极性非归零脉冲的数字信号变换为单极性归零脉冲,则该序列中就有位同步信号分量,经一个窄带滤波器,可滤出此信号分量,再将它通过一移相器调整相位后,就可以形成位同步脉冲。

FPGA习题集及参考答案

FPGA习题集及参考答案习题集及参考答案一、填空题1.一般把技术的发展分为()个阶段。

2.有如下设计步骤:①原理图文本输入、②适配、③功能仿真、④综合、⑤编程下载、⑥硬件测试,正确的设计顺序是①()⑤⑥。

3.在工具中,能完成在目标系统器件上布局布线的软件称为()。

4.设计输入完成之后,应立即对文件进行()。

5.基于硬件描述语言的数字系统设计目前最常用的设计方法称为()设计法。

6.将硬件描述语言转化为硬件电路的过程称为()。

7.核在技术和开发中具有十分重要的地位,以方式提供的被称为()。

8.系统又称为()系统。

系统又称为()系统。

9.将硬核和固核作为()核,而软核作为()核。

10.核在技术和开发中具有十分重要的地位,以方式提供的被称为()。

11.综合器就是逻辑综合的过程,把可综合的转化成硬件电路时,包含了三个过程,分别是()、()、()。

12.软件工具大致可以由五个模块构成,分别是设计输入编辑器、()、()、()和()。

13.按仿真电路描述级别的不同,仿真器分为()仿真、()仿真、()仿真和门级仿真。

14.系统仿真分为()、()和()。

15.()仿真是对设计输入的规范检测,这种仿真通过只能表示编译通过,说明设计满足一定的语法规范,但不能保证设计功能满足期望。

16.()仿真是对综合后的网表进行的仿真,它验证设计模块的基本逻辑功能,但不带有布局布线后产生的时序信息,是理想情况下的验证。

17.()仿真是布局布线后进行的后仿真,仿真时考虑了布线延时,和芯片实际的工作情况更加接近。

18.目前公司生产的主要采用了()配置存储器结构。

19.描述测试信号的变化和测试工程的模块叫做()。

20.现代电子系统设计领域中的采用()的设计方法。

21.有限状态机可分为()状态机和()状态机两类。

22.中的端口类型有三类:()、()、输入/输出端口。

23.常用两大数据类型:()、()。

24. / 设计流程为:原理图文本输入→()→综合→适配→()→编程下载→硬件测试。

2014年辽宁省数据概述要领

1、我们用l代表最长平台的长度,用k指示最长平台在数组b中的起始位置(下标)。

用j 记住局部平台的起始位置,用i指示扫描b数组的下标,i从0开始,依次和后续元素比较,若局部平台长度(i-j)大于l时,则修改最长平台的长度k(l=i-j)和其在b中的起始位置(k=j),直到b数组结束,l即为所求。

void Platform (int b[ ], int N)//求具有N个元素的整型数组b中最长平台的长度。

{l=1;k=0;j=0;i=0;while(i<n-1){while(i<n-1 && b[i]==b[i+1]) i++;if(i-j+1>l) {l=i-j+1;k=j;} //局部最长平台i++; j=i; } //新平台起点printf(“最长平台长度%d,在b数组中起始下标为%d”,l,k);}// Platform2、本题应使用深度优先遍历,从主调函数进入dfs(v)时,开始记数,若退出dfs()前,已访问完有向图的全部顶点(设为n个),则有向图有根,v为根结点。

将n个顶点从1到n编号,各调用一次dfs()过程,就可以求出全部的根结点。

题中有向图的邻接表存储结构、记顶点个数的变量、以及访问标记数组等均设计为全局变量。

建立有向图g的邻接表存储结构参见上面第2题,这里只给出判断有向图是否有根的算法。

int num=0, visited[]=0 //num记访问顶点个数,访问数组visited初始化。

const n=用户定义的顶点数;AdjList g ; //用邻接表作存储结构的有向图g。

void dfs(v){visited [v]=1; num++; //访问的顶点数+1if (num==n) {printf(“%d是有向图的根。

\n”,v); num=0;}//ifp=g[v].firstarc;while (p){if (visied[p->adjvex]==0) dfs (p->adjvex);p=p->next;} //whilevisited[v]=0; num--; //恢复顶点v}//dfsvoid JudgeRoot()//判断有向图是否有根,有根则输出之。

2014年TI杯辽宁省电子设计竞赛获奖名单

董志强 董壮 于晗程 王昊 吴昊 王震宇 李国钦 陈海明 甄昌健 付强 王飞鹏 刘阳 杜子晗 丁权 李成 金相宇 李鑫 于鹏飞 雷明海 陈嘉华 田野 王倩 伍文辉 于奇 王宇 杨恒赞 许可 徐刚 郭恒哲 蔣云晔 李硕 廖启超 于孔明 丁光帅 殷立磊 李明雪 张洪嘉 王玉玺 游川 陈龙 陈诗楠 王晓东 张楠楠 聂东元 王博洋 周宏 陈星年 李函轩 王博实 张胜军 崔国梁 王发

陈思 李轩辕 王自明 曹继雷 刘宁 何亚男 张帅 乔可可 李宏宇 张志鹏 刘 睿 宫东旭 何 杨 谭耿营 李曙光 张志洋 王永强 章璐 金岩君 曹玥琳 于永星 郝彦武 程宇辉 宋志强 韩浩 赵金 薛汉卿 马万里 陈龙喜 张林 张志东 田俊强 李旺 张增铄 胡小玲 韩光江 王鑫鑫 李炳君 陈阳 贝为炬 隋国际 赵小娜 张志杰 张磊 王然 刘柳 吴冀平 赵志军 汪云强 郭琳琳 夏洋洋 郭华东 张浩杰

刘旸 李善光 赵天豪 白泽明 王燕妮 张健 赵雪霞 路春雷 王皓承 冯申 王晓飞 张莉楠 叶浩 郭红宇 耿振超 苏志泽 张超峰 李伟 李星磊 宋慧慧 单泽 李青松 薛洪新 赵欣国 富彬彬 李德海 姚茂江 李敏 柏合 李显凤 潘潇 王海波 刘浩伯 李宗卿 蒙文龙 曹天麟 赵爽 宋硕 冀昊 周佳禹 王之涛 王强 肖开提·吾甫尔 韦福洪 劳少神 黄若山 李永华 慕翔 胡美玉 陈齐 谌炳汉 石成玉 王雷 李松凯 胡兵 李治华 崔玉 徐丽阳 宋旻雨 王诗涵 包绍瑛 张祝祥 张君豪 刘大川 徐承成 张天琪 叶再本 张昆杰 汤扬 朱世鹏 张永洪 黄显芮 胡涛 毛怡云 赖俊伟 唐鹏 黄辉 陈赛 金雪皎 张新邦 王海宇 谢帅 黄炜 袁程磊 周磊 潘添祺 胡光发 薛昭洋 郑名洋 姜先达 郭恒开 王继超 申浩 杨永胜 李瑞娟 孙涛 杨苏辉 林宴任 林钰涵 唐前龙 苏峻 冯新成

FPGA期末考试题目

FPGA期末考试题目预览说明:预览图片所展示的格式为文档的源格式展示,下载源文件没有水印,内容可编辑和复制F PG A期末考试题目LEKIBM standardization office【IBM5AB- LEKIBMK08- LEKIBM2C】四、简答题1.简述EDA技术的发展历程2.什么是EDA技术?3.在EDA技术中,什么是自顶向下的设计方法?4.自顶向下的设计方法有什么重要意义?5.简要说明目前现代数字系统的发展趋势是什么?6.简述现代数字系统设计流程。

7.简述原理图设计法设计流程。

8.简述原理图设计法设计方法的优缺点。

9.什么是综合综合的步骤是什么10.什么是基于平台的设计现有平台分为哪几个类型11.目前,目前数字专用集成电路的设计主要采用三种方式各有什么特点12.什么是SOC技术含义是什么什么是SOPC13.SOPC技术含义是什么SOPC技术和SOC技术的区别是什么14.SOPC技术是指什么SOPC的技术优势是什么15.简要说明一下功能仿真和时序仿真的异同。

设计过程中如果只做功能仿真,不做时序仿真,设计的正确性是否能得到保证?16.综合完成的主要工作是什么实现(Implement)完成的主要工作是什么17.主要的HDL语言是哪两种Verilog HDL 语言的特点是什么18.简述阻塞赋值与非阻塞赋值的不同。

19.简述过程赋值和连续赋值的区别。

20.什么叫做IP核IP在设计中的作用是什么21.什么是IP软核,它的特点是什么?22.根据有效形式将IP分为哪几类根据功能方面的划分分为哪两类23.比较基于查找表的FPGA和CPLD系统结构和性能上有何不同? 24.什么是数据流级建模什么是行为级建模25.timescale指令的作用是什么。

26.采用HDL完成设计后,必须应用测试程序(testbench)对设计的正确性进行验证。

测27.什么是FPGA,CPLD他们分别是基于什么结构的可编程逻辑结构28.CPLD是基于什么结构的可编程逻辑器件?其基本结构由哪几部分组成。

2014电子设计竞赛题目全(本科组)

2014年TI杯大学生电子设计竞赛题A题:四旋翼飞行器1.任务设计制作一架能够自主飞行的四旋翼飞行器。

2.要求四旋翼飞行器能够完成以下飞行动作:(1)飞行器能够根据起飞前预置的指令起飞,飞离地面高度应超过30cm,飞行距离(水平)应超过60cm,然后飞行器应能平稳降落。

(30分)(2)飞行器能够根据指定(键盘设定)的飞行高度及降落地点(方向及距离)连续稳定地完成起飞、指定高度水平飞行、平稳降落等动作。

(20分)(3)飞行器能够根据起飞前预置的指令垂直起飞,起飞后能够在50cm以上高度平稳悬停5s以上,然后再平稳缓慢降落到起飞地点;起飞与降落地点水平距离不超过30cm。

(30分)(4)其他自主发挥设计的飞行动作。

(20分)(5)设计报告(20分)项目主要内容分数系统方案方案比较,方案描述 5设计与论证飞行器姿态测量方法飞行控制器控制方法与参数计算8测试测试方法与测试结果 5设计报告结构及规范性摘要,正文结构完整性、内容规范性 2小计203.说明(1)飞行器的姿态检测及飞行控制必须使用TIV A M4、C2000或MSP430等系列控制器。

(2)飞行器在完成每一项飞行动作期间不得以任何方式人为干预,如遥控等。

(3)飞行器的尺寸可自行选定。

(4)飞行方向以正北方向为0°、东北方向为45°、正东方向为90°等,以此类推;距离的单位为厘米(cm)。

(5)指定的降落地点是指降落地点距起飞地的水平距离及方向。

(6)平稳降落是指在降落过程中无明显的跌落、弹跳及着地后滑行等现象。

(7)能够完成要求(2)时,要求(1)可以免测。

(8)为确保安全,飞行器应在安全网中或在系留方式下工作(即以绳索将飞行器拴在地面固定物上)。

2014年TI 杯大学生电子设计竞赛题B 题:金属物体探测定位器4. 任务设计并制作一个可自主移动的金属物体探测定位器(以下简称探测器),可探测置于玻璃板下的金属物体并给出定位指示。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

FPGA实现Sigma-DeltaADC数字抽取滤波器一.数字抽取滤波器的原理分析因为Sigma-DeltaADC调制器的输出频率很高,需要在数字滤波处理时降低输出频率。

即通过抽取完成降频任务。

时域上,序列经过M倍采样,每间隔M-1个点被保留下来,最终形成降频后的新序列。

在频域上,输出信号频谱是由输入信号频谱在w轴上每间隔2pi/M的移位叠加,再进行M 倍的扩展而成,输出信号频谱为周期为2pi/M的周期信号。

数字抽取滤波器的基本作用就是滤波与降频,采用抽取频率的方法将信号频率降至原始采样频率,即原始信号的奈奎斯特频率。

抽取可以有效去除采样过程中产生的多余信号。

为了满足奈奎斯特采样定理,防止信号发生混叠,抽取倍率M要小于或等于采样倍率K。

二.数字抽取滤波器的理论计算输入信号(即1位的高速数据流)的频率fclk=Kfs,最后输出的信号频率为fs,所以要进行K倍抽取。

即在本课题中抽取倍率M等于过采样倍率K。

令K=128,对于模式一,fs=100Hz,所以输入信号频率为fclk=Kfs=12800Hz。

对于模式二,fs=1600Hz,所以输入频率为fclk=Kfs=204.8KHz。

要进行128倍抽取,可以将滤波器三级级联,前两级的抽取因子为8,第三级的抽取因子为2,即K=8X8X2。

模式一每级需要的时钟频率为:第三级输入时钟f3=100HzX2=200Hz;第二级时钟f2=200HzX8=1600Hz;第一级输入时钟f1=1600HzX8=12800Hz=Kfs.模式二每级需要的时钟频率为:第三级输入频率f3=1600HzX2=3200Hz;第二级频率f2=3200HzX8=25.6KHz;第一级的输入时钟频率f3=25.6KHzX8=204.8KHz。

三.程序功能描述与设计思路1.程序功能描述根据题目要求,程序实现了(1)模式选择功能:通过拨动开关来实现模式一与模式二的选择功能。

(2)采样数据显示功能:显示A/D转换电路连续采样数据波形,在波形上显示一个光标,以及实时显示数据的方差与电压值。

2.设计思路(1)通过FPGA实现数字滤波器的降频与滤波功能。

抽取型CIC滤波器同时具有这两个功能,所以选QUartus II中自带的IP核CIC滤波器宏模块。

而滤波器的阶数受限于系统硬件资源,因此数字抽取器一般不会采用单级高阶数的结构,而是采用多级滤波器级联的结构。

本题中选用3级CIC级联。

为了克服CIC滤波器的通带下降,我们需要一个FIR滤波器,它具有与CIC相逆的幅频特性,将其与CIC滤波器级联,这样就可以得到比较平缓的通带特性。

因此每级滤波器都有CIC滤波器与FIR滤波器相连而成。

在一些速率转换系统中,FIR补偿滤波器也可实现降采样,通常其降采样因数不大于2。

在本题中,FIR滤波器不实现降采样,仅仅为了补偿CIC的通带下降,所以参数设置时选择single rate.(2)通过单片机实现显示功能。

三.FPGA程序实现数字抽取滤波器的功能1. FPGA原理图如上所述,降频128倍由三个如下的模块级联而成时钟选择模块:通过一个二选一模块分别将两路输入时钟送到滤波器级联模块。

与单片机的接口模块:软件仿真测试:以模式一为例说明:联合Matlab仿真得到各级FIR滤波器的系数导入其中,最后得到各级的幅频响应如下所示:第一级的幅频响应:第二级的幅频响应:第三级的幅频响应:附件:FPGA程序时钟选择模块:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;entity MUX21 isport (A:in std_logic;B:in std_logic;SEL:in std_logic;C:out std_logic);end MUX21;architecture behave of MUX21 isbeginprocess(SEL,a,b)begincase SEL iswhen '0' => c<=A; --Hzwhen '1'=> C<=b; --KHzwhen others=> NULL;end case;end process;end behave;八分频模块:library IEEE;use IEEE.STD_LOGIC_1164.ALL;use IEEE.STD_LOGIC_ARITH.ALL;use IEEE.STD_LOGIC_UNSIGNED.ALL;entity fenpin8 isPort ( clkin : in STD_LOGIC;Clkout : out std_logic);end fenpin8;architecture Behavioral of fenpin8 is signal clk : integer :=0;beginprocess(clkin)beginif clkin'event and clkin ='1' thenif clk = 7 thenclk<=0;else clk<=clk+1;end if;end if;if clk<=3 thenclkout<='0';else clkout<='1';end if;end process;end Behavioral;数据有效位截取模块:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;entity form isport (A0:in std_logic_VECTOR(11 DOWNTO 0);SEL:in std_logic;C0:out std_logic_VECTOR(11 DOWNTO 0));end form;architecture behave of form isbeginprocess(SEL,a0)begincase SEL iswhen '0' => C0<=A0;when '1'=> C0<="0000"&A0(11 DOWNTO 4);when others=> NULL;end case;end process;end behave;与单片机的接口协议模块:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY jiekou ISPORT(CLK:IN STD_LOGIC;D:in std_logic_vector(11 downto 0);Q:OUT STD_LOGIC_VECTOR(11 DOWNTO 0);F:BUFFER STD_LOGIC;M:in STD_LOGIC);END jiekou;ARCHITECTURE BEHAVE OF jiekou ISBEGINPROCESS(CLK,M)BEGINIF RISING_EDGE(CLK) THENQ<=D;F<='1';END IF;IF F='1' AND M='1' THENF<='0';END IF;END PROCESS;END BEHAVE;第一级CIC模块:library IEEE;use IEEE.std_logic_1164.all;ENTITY CIC_1A ISPORT (clk : IN STD_LOGIC;clken : IN STD_LOGIC;reset_n : IN STD_LOGIC;in_data : IN STD_LOGIC;in_valid : IN STD_LOGIC;out_ready : IN STD_LOGIC;in_error : IN STD_LOGIC_VECTOR (1 DOWNTO 0);out_data : OUT STD_LOGIC_VECTOR (9 DOWNTO 0);in_ready : OUT STD_LOGIC;out_valid : OUT STD_LOGIC;out_error : OUT STD_LOGIC_VECTOR (1 DOWNTO 0) );END CIC_1A;ARCHITECTURE SYN OF CIC_1A ISCOMPONENT CIC_1A_cicPORT (clk : IN STD_LOGIC;clken : IN STD_LOGIC;reset_n : IN STD_LOGIC;in_data : IN STD_LOGIC;in_valid : IN STD_LOGIC;out_ready : IN STD_LOGIC;in_error : IN STD_LOGIC_VECTOR (1 DOWNTO 0);out_data : OUT STD_LOGIC_VECTOR (9 DOWNTO 0);in_ready : OUT STD_LOGIC;out_valid : OUT STD_LOGIC;out_error : OUT STD_LOGIC_VECTOR (1 DOWNTO 0) );END COMPONENT;BEGINCIC_1A_cic_inst : CIC_1A_cicPORT MAP (clk => clk,clken => clken,reset_n => reset_n,in_data => in_data,out_data => out_data,in_valid => in_valid,out_ready => out_ready,in_ready => in_ready,out_valid => out_valid,in_error => in_error,out_error => out_error);END SYN;第一级FIR模块:library IEEE;use IEEE.std_logic_1164.all;ENTITY fir_1A ISPORT (clk : IN STD_LOGIC;reset_n : IN STD_LOGIC;ast_sink_data : IN STD_LOGIC_VECTOR (9 DOWNTO 0);ast_sink_valid : IN STD_LOGIC;ast_source_ready : IN STD_LOGIC;ast_sink_error : IN STD_LOGIC_VECTOR (1 DOWNTO 0);ast_source_data : OUT STD_LOGIC_VECTOR (9 DOWNTO 0);ast_sink_ready : OUT STD_LOGIC;ast_source_valid : OUT STD_LOGIC;ast_source_error : OUT STD_LOGIC_VECTOR (1 DOWNTO 0) );END fir_1A;ARCHITECTURE SYN OF fir_1A ISCOMPONENT fir_1A_astPORT (clk : IN STD_LOGIC;reset_n : IN STD_LOGIC;ast_sink_data : IN STD_LOGIC_VECTOR (9 DOWNTO 0);ast_sink_valid : IN STD_LOGIC;ast_source_ready : IN STD_LOGIC;ast_sink_error : IN STD_LOGIC_VECTOR (1 DOWNTO 0);ast_source_data : OUT STD_LOGIC_VECTOR (9 DOWNTO 0);ast_sink_ready : OUT STD_LOGIC;ast_source_valid : OUT STD_LOGIC;ast_source_error : OUT STD_LOGIC_VECTOR (1 DOWNTO 0) );END COMPONENT;BEGINfir_1A_ast_inst : fir_1A_astPORT MAP (clk => clk,reset_n => reset_n,ast_sink_data => ast_sink_data,ast_source_data => ast_source_data,ast_sink_valid => ast_sink_valid,ast_sink_ready => ast_sink_ready,ast_source_valid => ast_source_valid,ast_source_ready => ast_source_ready,ast_sink_error => ast_sink_error,ast_source_error => ast_source_error );END SYN;。