12数电ch6寄存器

合集下载

CH6 存储器

二、存储器的分类

只读存储器(ROM)

掩模ROM UVEPROM

PROM

E2PROM

第

EPROM 快闪存储器

六

从存、取功能上分

章

(FLASH)

SRAM

半

导

随机存储器(RAM)

体

DRAM

存

储

双极型

器

从制造工艺上分

MOS型

中南大学信息科学与工程学院

三、存储器的主要技术指标

第 1.存储容量:所存放信息的多少,用Bit表示

六 章

2.存储时间:用读(写)周期表示

半 导 体 存 储 器

中南大学信息科学与工程学院

6.2 只读存储器ROM

定义:只读存储器ROM(Read—Only

第

memory)是存储固定信息的存储器件,即

六

先把信息和数据写入到存储器中,在正常工

章

作时它存储的数据是固定不变的,只能读出,

半

不能迅速写入,故称为只读存储器。

中南大学信息科学与工程学院

2、SRAM的静态存储单元 (六管NMOS静态存储单元)

第 静态存储 六 单元=触 章 发器+控 半 制电路

导 体 存 储 器

中南大学信息科学与工程学院

原理:

• 1)当地址译码后, Xi=1,Yj=1

第 Xi=1,则T5、T6导通,使Q与Bj及Q与Bj接通;

六 章

Yj=1,则T7、T8导通,使位线可输入/输出。

的。

中南大学信息科学与工程学院

第 六 章

半 导 体 存 储 器

中南大学信息科学与工程学院

原理(写入过程):

第

• 1)输入地址,选中字线;

CH6 存储器和可编程逻辑器件解析

SRAM RAM

2018/10/16

DRAM

Lab of CVPR of West AnHui University 孔敏

2

2018/10/16

第2页

6.1 半导体存储器

双极型

半导体存储器 数 字 MOS型 电 路 对存储器的操作通常分为两类: 与 写——即把信息存入存储器的过程。 逻 读——即从存储器中取出信息的过程。 辑 设 计 两个重要技术指标: 存储容量—存储器能存放二值信息的多少。单位是位或 10 10 20 比特(bit)。1K=2 =1024,1M=2 K=2 。 存储时间—存储器读出(或写入)数据的时间。一般用 读(或写)周期来表示。

2018/10/16 3 Lab of CVPR of West AnHui University 孔敏

按制造工艺来分:

2018/10/16

第3页

6.1 半导体存储器

二、掩膜只读存储器(ROM)

数 特点: 字 ①只能读出,不能写入; 电 路 ②存储的数据不会因断电而消失,具有非易失性。 与 逻 1. ROM的基本结构 辑 设 ROM主要由地址译码器、存储矩阵和输出缓冲器三部 计 分组成,其基本结构如图所示。

数 字 电 路 与 逻 辑 设 计

第六章 存储器和可编程逻辑器件

6.1 半导体存储器 6.2 可编程逻辑器件基础 6.3 低密度可编程逻辑器件 6.4 高密度可编程逻辑器件

2018/10/16

1 Lab of CVPR of West AnHui University 孔敏

2018/10/16

第1页

Lab of CVPR of West AnHui University

第8页

6.1 半导体存储器

2018/10/16

DRAM

Lab of CVPR of West AnHui University 孔敏

2

2018/10/16

第2页

6.1 半导体存储器

双极型

半导体存储器 数 字 MOS型 电 路 对存储器的操作通常分为两类: 与 写——即把信息存入存储器的过程。 逻 读——即从存储器中取出信息的过程。 辑 设 计 两个重要技术指标: 存储容量—存储器能存放二值信息的多少。单位是位或 10 10 20 比特(bit)。1K=2 =1024,1M=2 K=2 。 存储时间—存储器读出(或写入)数据的时间。一般用 读(或写)周期来表示。

2018/10/16 3 Lab of CVPR of West AnHui University 孔敏

按制造工艺来分:

2018/10/16

第3页

6.1 半导体存储器

二、掩膜只读存储器(ROM)

数 特点: 字 ①只能读出,不能写入; 电 路 ②存储的数据不会因断电而消失,具有非易失性。 与 逻 1. ROM的基本结构 辑 设 ROM主要由地址译码器、存储矩阵和输出缓冲器三部 计 分组成,其基本结构如图所示。

数 字 电 路 与 逻 辑 设 计

第六章 存储器和可编程逻辑器件

6.1 半导体存储器 6.2 可编程逻辑器件基础 6.3 低密度可编程逻辑器件 6.4 高密度可编程逻辑器件

2018/10/16

1 Lab of CVPR of West AnHui University 孔敏

2018/10/16

第1页

Lab of CVPR of West AnHui University

第8页

6.1 半导体存储器

ch6-1 CPU的组成和功能

人是活的,书是死的。活人读死书,可以把书读活。 死书读活人,可以把人读死。郭沫若

5

6.1 中央处理器的功能和组成

2.专用寄存器 专用寄存器是专门用来完成某一种特 殊功能的寄存器。CPU中至少要有五个专 用的寄存器。它们是:程序计数器(PC)、 指令寄存器(IR)、存储器地址寄存器 (MAR)、存储器数据寄存器(MDR)、 状态标志寄存器(PSWR)。

死书读活人,可以把人读死。郭沫若

8

6.1 中央处理器的功能和组成

⑷ 存储器地址寄存器 存储器地址寄存器用来保存当前 CPU 所访问的主存单元的地址。由于主存和 CPU 之间存在着操作速度上的差别,所以 必须使用地址寄存器来保持地址信息,直 到主存的读/写操作完成为止。 当 CPU 和主存进行信息交换,无论是 CPU向主存存/取数据时,还是CPU从主存 中读出指令时,都要使用存储器地址寄存 器和数据寄存器。

人是活的,书是死的。活人读死书,可以把书读活。 死书读活人,可以把人读死。郭沫若

13

6.1 中央处理器的功能和组成

3.外部工作频率 由主板为CPU提供的基准时钟频率。 内频=外频×倍频 4. 前端总线频率 前端总线FSB(Front Side Bus是CPU 和外界交换数据的最主要通道,主要连接主 存、显卡等数据吞吐率高的部件,因此前端 总线的数据传输能力对计算机整体性能作用 很大。

第 6章

中央处理器

人是活的,书是死的。活人读死书,可以把书读活。 死书读活人,可以把人读死。郭沫若

1

6.1 中央处理器的功能和组成

6.1.1 CPU的功能 在控制器的控制下按照事先编制的程序逐条 执行。 指令流指的是处理器执行的指令序列。 数据流指的是根据指令操作要求依次存取数 据的序列。

5

6.1 中央处理器的功能和组成

2.专用寄存器 专用寄存器是专门用来完成某一种特 殊功能的寄存器。CPU中至少要有五个专 用的寄存器。它们是:程序计数器(PC)、 指令寄存器(IR)、存储器地址寄存器 (MAR)、存储器数据寄存器(MDR)、 状态标志寄存器(PSWR)。

死书读活人,可以把人读死。郭沫若

8

6.1 中央处理器的功能和组成

⑷ 存储器地址寄存器 存储器地址寄存器用来保存当前 CPU 所访问的主存单元的地址。由于主存和 CPU 之间存在着操作速度上的差别,所以 必须使用地址寄存器来保持地址信息,直 到主存的读/写操作完成为止。 当 CPU 和主存进行信息交换,无论是 CPU向主存存/取数据时,还是CPU从主存 中读出指令时,都要使用存储器地址寄存 器和数据寄存器。

人是活的,书是死的。活人读死书,可以把书读活。 死书读活人,可以把人读死。郭沫若

13

6.1 中央处理器的功能和组成

3.外部工作频率 由主板为CPU提供的基准时钟频率。 内频=外频×倍频 4. 前端总线频率 前端总线FSB(Front Side Bus是CPU 和外界交换数据的最主要通道,主要连接主 存、显卡等数据吞吐率高的部件,因此前端 总线的数据传输能力对计算机整体性能作用 很大。

第 6章

中央处理器

人是活的,书是死的。活人读死书,可以把书读活。 死书读活人,可以把人读死。郭沫若

1

6.1 中央处理器的功能和组成

6.1.1 CPU的功能 在控制器的控制下按照事先编制的程序逐条 执行。 指令流指的是处理器执行的指令序列。 数据流指的是根据指令操作要求依次存取数 据的序列。

ch6 时序电路

广东工业大学 自动化学院

6.2 时序电路的分析方法

(5)状态转换图

CLK A

(6)根据状态转换表(图), 画出波形图

Q0 Q1 Y

1 0

0 1

1

1

0 0

1

1

0

1

1

0

广东工业大学 自动化学院

6.2 时序电路的分析方法

*二、异步时序逻辑电路的分析

TTL电路

广东工业大学 自动化学院

6.3 若干常用的时序逻辑电路

广东工业大学 自动化学院

6.2 时序电路的分析方法

一、同步时序电路的分析

• 目的:根据给定的逻辑电路,通过分析找出电路的逻辑功能。 • 一般步骤:

1. 写输出方程和每个触发器的驱动方程 2. 将驱动方程代入触发器的特性方程,得到状态方程 3. 进行状态计算,画出电路的状态转换表(图)或时 序图 4. 分析电路的功能

广东工业大学 自动化学院

6.3 若干常用的时序逻辑电路

1.基本寄存器

基本寄存器可以接收、暂存、传递数码。它是 在时钟脉冲(接收脉冲)CLK作用下,将数据存入 对应的触发器。由于D触发器的特性方程是Q* = D, 因此以D作为数据输入端组成寄存器最为方便。

例1:

74LS 75 clk高电平期间 Q随D改变

广东工业大学 自动化学院

6.3 若干常用的时序逻辑电路

二、 计数器

计数器-是通过电路的状态来反映输入脉冲数目的电路 计数器的基本功能是对输入时钟脉冲进行计数。 它也可用于分频、定时、产生节拍脉冲和脉冲序列 及进行数字运算等等。 • 计数器的分类 同步计数器和异步计数器 加法计数器、减法计数器和可逆计数器 二进制计数器、十进制计数器、任意进制计数器等

数字电子技术--时序电路+寄存器

(CP 有效) (Q0 有效) (CP 有效)

Q1n 1 Q1n n n n Q2 1 Q1 Q0

求状态转换表

现态 次态 输出

Q2nQ1nQ0n 0 0 0 0 0 1 0 1 0 0 1 1 1 0 0 1 0 1 1 1 0 1 1 1

Q2n+1Q1n+1Q0n+1 0 0 1 0 1 0 0 1 1 1 0 0 0 0 0 0 1 0 0 1 0 1 0 0

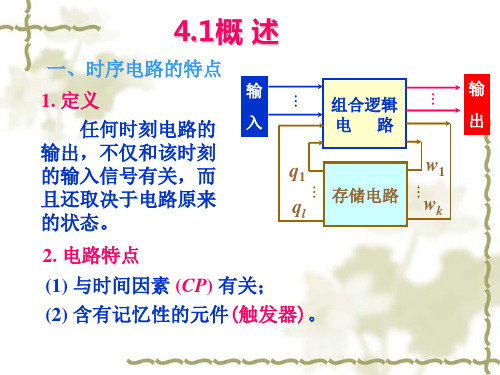

4.1概 述

一、时序电路的特点 1. 定义 任何时刻电路的 输出,不仅和该时刻 的输入信号有关,而 且还取决于电路原来 的状态。 2. 电路特点 (1) 与时间因素 (CP) 有关; (2) 含有记忆性的元件(触发器)。

…

x 入i q1

…

组合逻辑 电 路

…

…

输1

x

y1 输

…

出 yj

w1

存储电路

…

ql

2 3 4 5

0 1

0 0 0 1 1 1

0 0 1 1 1 0

0 1 1 1 0 0

1 1 1 1 1 0

画状态转换图 /1 /1 /1 /1 /1 000 001 011 111 110 100 /0 有效状态和有效循环 010 /1 /1 101

n n n Y Q2 Q1 Q0

无效状态和无效循环

000 /0

n1 Q n Q n Q0 1 1 0 1 2

n Q2

00 01 11

10

0

1 0 0 1 1 0

0 0 1

0 1

1 0

n Q0 1 Q 0 n 1 Q1 Q 2 Q1Q0 Q1 Q 0 n 1 Q2 Q1Q0 Q2 Q 0

数字电路与逻辑设计第6章-2-寄存器-移位寄存器

0

—————

1

1 ————

2

0 1 ———

3

0 0 1 ——

4

1 0 0 1—

5

11001

并行输出 1 1 0 0 1

波形:

并行输 出脉冲 移存脉冲

Q1

Q2

Q3 Q4 Q5

1 00 1

1

1 0

0

1

B 并行转换为串行(输入是并行,输出是串行)

组成: 右移移位寄存器和输入电路 分析:由于是D触发器,有Qn+1=D

三、 寄存器,移位寄存器。

寄存器是一种常用的时序逻辑电路,用来存储多位二进 制代码。这些代码可以是数据,指令,地址或其他信 息。由于一个触发器只能存放一位二进制代码,因此, 用n个触发器和一些起控制作用的门电路,可以组成 n位寄存器。

按功能划分,寄存器可分为: 数码寄存器 移位寄存器

1 、 数码寄存器

1、 环形计数器

1. 连接方法: ——将移位寄存器的最后一级输出Q反馈到第一级 的J、K输入端; 2. 判断触发器个数n : ——计数器的模为M=n(n为所需移位寄存器的位 数)

移位寄存器构成的移位计数器

2.扭环形计数器

为了增加有效计数状态,扩大计数器的模,可用扭环形计数器。

一般来说,N位移位寄存器可以组成模2N的扭环形计数器,只需将

电路结构分析:

串行输入数据DI加到片Ⅰ的J,K和D0端。

片Ⅰ的D1端接0,作为标志码,片Ⅰ其余 的D2,D3接1。

片Ⅱ的串行数据输入端J, K接片Ⅰ的Q3。 片Ⅱ的输入端D0~D3均接1。片Ⅱ的Q3输出作 片Ⅰ和片Ⅱ的SH/LD输入。

工作过程:

①器件通过CR清0,使所有Q输出均为0, 包括片Ⅱ的Q3=0。

数电 第二节 寄存器

扭环形计数器设计

(1)连接方法: 将移位寄存器的输出Q3经反相器后

反馈到J、K输入端。

(2)判断触发器个数:

计数器的模M=2 n (n为移位寄存器的

位数)。

分频器

第四节 序列码发生器

按一定规则 排列的周期性串

一行、二进反制馈码。型序列码发生器

二、计数器型序列码发生器

任意长度的序列码

二、计数器型序列码发生器

Q0n Q0n Q1n Q2n Q2n 0 Q0n Q1n Q2n Q2n 1 Q0n Q1n Q2n Q2n Q0 Q0n Q1n Q2n Q2n

(三)四位双向移位寄存器74194 1. 逻辑符号 2. 功能

SRG4

(输(低(为135))出)高电左保清寄电平移持零存平):::M器),MC2,置无模0T模=关“式关0式联不0时联0时数0受(数0(字”任字M是M(何A,当A为2关和,保低低联M又电持,MB,考平输将 为B

1.七位串行并行转换 串行并行

R

SRG4

CT=0 (1)

C4

CP

1→/ 2←

1 MA MB

0 M 0 74194

1

3

串行输入

DSR 1,4D

3,4D

0

3,4D

1

3,4D

1

3,4D

2,4D

1 MA MB

SRG4

CT=0 (2)

C4

1→/ 2←

0 M 0 74194

1

3

Q0 DD001

1,4D

Q1 0D00

当数C字P3,时那,就执是行C3右有移效:(CP

Q2 Q3

的到上输输升出出沿Q)0,由将J即、输K入当决端定R数=, 据1 送,

数电课件 ch06-6时序可编程通用阵列逻辑器件(GAL)

现PAL 的5种输出工作模式。器件的通用性强;

3、GAL工作速度快,功耗小

6.7.1 时序可编程逻辑器件中的宏单元

CLK OE

D

Q

输出

输 入

>C

Q

6.7.2 时序可编程逻辑器件的主要类型

1. 通用阵列逻辑(GAL)

在PLA和PAL基础上发展起来的增强型器件.电路设计者可根据

需要编程,对宏单元的内部电路进行不同模式的组合,从而使输 出功能具有一定的灵活性和通用性。 2. 复杂可编程逻辑器件(CPLD) 集成了多个逻辑单元块,每个逻辑块就相当于一个GAL器件。 这些逻辑块可以通过共享可编程开关阵列组成的互连资源,实现 它们之间的信息交换,也可以与周围的I/O模块相连,实现与芯片 外部交换信息。

反馈数据选择器(4选1)——OMUX

FMUX: 根据AC0和AC1(n)的不同编码,使反向传输的电信号也对应不同。

功 能 组合 专用输入 专用组合 输出

SYN

AC0 AC1 XOR 输出相位 (n) (n) 0 0 1 0 — 0 1 — 反相 同相

备 注 1,11脚为数据输入端,输 出三态门禁止 1,11脚为数据输入端,组 合输出,三态门选通

行,即所谓的SOC技术。

6.7.3通用阵列逻辑GAL

GAL的电路结构与PAL类似,由可编程的与逻辑阵列、 固定的或逻辑阵列和输出电路组成,但GAL的输出端增设了 可编程的的输出逻辑宏单元(OLMC)。通过编程可将 OLMC设置为不同的工作状态,可实现PAL的所有输出结构, 产生组合、时序逻辑电路输出。

三态缓冲器

AC0 AC1(n) 0 0 0 1 1 0 1 1TX(输出)源自VCC 地电平 OE第一乘积项

的工作状态

CH5-3寄存器

时钟方程 驱动方程 状态方程

CP0 = CP1 = CP2 = CP3 = CP

n n n D0 = Di、D1 = Q0 、D2 = Q1 、D3 = Q2

n n n n n Q0 +1 = Di , Q1n+1 = Q0 , Q2 +1 = Q1n , Q3 +1 = Q2

右 移 寄 存 器

第5章 时序逻辑电路 Q0 Q1 Q2 Q3

第5章

时序逻辑电路

数字电子技术

主要内容

时序逻辑电路的基本概念 电路的基本分析和设计方法 计数器 寄存器

第5章

时序逻辑电路

数字电子技术

5.4 寄存器(Register)

寄存器常用于接收、暂存、 寄存器常用于接收、暂存、传递数码和指令等 常用于接收 信息。 信息。 一个触发器有两种稳定状态 , 可以存放一位 一位二 一个触发器有 两种稳定状态, 可以存放 一位 二 两种稳定状态 进制数码。 存放n位二进制数码需要n个触发器。 进制数码 。 存放 n 位二进制数码需要 n 个触发器 。

第5章 时序逻辑电路

数字电子技术

单向移位寄存器的主要特点: 单向移位寄存器的主要特点:

(1)输入数码在 CP 控制下,依次右移或左移; (2)寄存 n 位二进制数码。n个CP完成串行输入, 并可从Q0∼Q3 端获得并行输出,再经 n 个CP 又获得串行输出。

第5章 时序逻辑电路

数字电子技术

2.双向移位寄存器(P352)(了解)

第5章 时序逻辑电路

数字电子技术

5.4.4 读/写存储器 写存储器——RAM 写存储器 一、RAM 的结构

地 址 码 输 入 CS 片选 R / 控制 读 /写 W I / 输入/输出 输入/O 地 址 译 码 器

ch6

S(0V)

浮栅

D(-30V)

P N—Si

+

P

+

PN 结反偏

Vss

(五)EEPROM

• EEPROM是采用电将全部信息一次擦除的 是采用电将全部信息一次擦除的ROM。 是采用电将全部信息一次擦除的 。 • EEPROM的存储单元是由叠栅管组成的。 的存储单元是由叠栅管组成的。 的存储单元是由叠栅管组成的

④

ALU实现减法功能 K3K2K1K0=0010,K(A,B)= AB P3P2P1P0=1001, P(A,B)= AB + AB = A⊕B R3R2R1R0=0110, R(P,Cin)=PCin+PCin=P⊕Cin= A⊕B⊕Cin 根据函数发生器的运算情况考虑进位链的处理情况。 Cin=0 表示有借位,Cin=1 表示无借位。 当A= 1,B=1时, P=1 ,K=0, Cout=Cin。 R=Cin 当A= 0,B=0时, P=1 ,K=0, Cout=Cin。 R=Cin 当A= 1,B=0时, P=0 ,K=0, Cout=1,(高阻)无借位。 R=Cin 当A= 0,B=1时, P=0 ,K=1, Cout=0, 有借位。 R=Cin 从以上分析可以知道在给定的控制码条件下,实现(A-B)运算。 运算 A+B A+B+Cin A-B B-A A-B-Cin K 1 1 2 4 2 P 6 6 9 9 9 R 6 6 6 6 6

2、超前进位链加法器 S=A⊕B⊕Ci-1 Cout=AB+Ci-1(A+B)

令Gi=AiBi, 进位产生信号 Pi=Ai+Bi 进位传输信号

,则 Cout=Gi+Pi Ci-1

四位全加器的进位链逻辑可以表示为如下 C1=G1+P1C0 C2=G2+P2G1+P2P1C0 C3=G3+P3G2+P3P2G1+P3P2P1C0 C4=G4+P4G3+P4P3G2+P4P3G2+P4P3P2G1+P4P3P2P1C0 我们可以改写为: C1=G1(P1+C0) C2=G2(P2+G1)(P2+P1+C0) C3=G3(P3+G2)(P3+P2+G1)(P3+P2+P1+C0) C4=G4(P4+G3)(P4+P3+G2)(P4+P3+G2)(P4+P3+P2+G1)(P4+P3+P2+P1+C0)

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

常用时序逻辑功能器件

寄存器和移位寄存器 一、 寄存器 寄存器:是数字系统中用来存储代码或数据的逻辑部 寄存器 是数字系统中用来存储代码或数据的逻辑部 它的主要组成部分是触发器。 件。它的主要组成部分是触发器。 一个触发器能存储1位二进制代码, 一个触发器能存储 位二进制代码,存储 n 位二进 位二进制代码 个触发器组成。 制代码的寄存器需要用 n 个触发器组成。寄存器实际 上是若干触发器的集合。 上是若干触发器的集合。

n Q0 +1 = D0 = DSR S=1 n Q1 +1 = D1 = Q 0

Q n +1 = D 2 = Q 1 2 n Q3 +1 = D3 = Q 2

n Q1 +1 = D1 = Q 2 n +1 3

低位移向高位

n S=0 Q0 +1 = D 0 = Q1

Q

n +1 2

= D2 = Q 3

n+1

00001011

n

0 1 0 1 0 1

0 0

0 0

0

= Q0 =Qn

1CP 后 1 2CP 后 1 3CP 后 0 4CP 后 1

1 2

1 1 0

0 1 1

0 0 1

=Qn

DSI =D3 D2 D1 D0 =1101,从高位开始输入 从高位开始输入

经过7个 CP脉冲作用后,从 SI 端串行输入的数码 经过4个 脉冲作用后 脉冲作用后, 经过 个CP脉冲作用后,从DDSi 端串行输入的数 经过 个 脉冲作用后, 脉冲作用后 码就可以从Q Q1 Q2 Q3并行输出。 D 行输出。 并行输出 串入→ 并出 串入→ 码就可以从SO0 端串行输出。输出。 就可以从D O 串入→串出 串入→

工作原理(电路分析) (2). 工作原理(电路分析) 1、了解电路组成 、 2、写出驱动方程: 、写出驱动方程:

D0=DSI D1=Q0n

3、写出状态方程: 、写出状态方程: D触发器的特性方程 触发器的特性方程

D2=Qn1

D3=Qn2

Q0n+1=DSI Q2n+1 =Qn1

D0 D2 D1 D3 FF0

CP Q m–1 Qm Q m+1

计算机 B

4位单向移位寄存器

(1)电路 串行数据输入端 并行数据输出端

DSI

Q0 FF1 Q1 FF2 1D 1D 1D >C1 Q0 >C1 Q1 >C1 FF0

移位脉冲

Q2 Q2

FF3 1D >C1

Q3 DSO Q3

CP

串行数据输出端

∵ 触发器有延迟时间 t pd 到达时, ∴ cp ↑ 到达时,各触发器按前 一级触发器原来的状态 翻转

1 C DSI 1

Q0 0 Q1 0 Q2 0 Q3(DSO) 0

2 1 0

3 1

4

5

6

7

8

1 0 0 0

1 1 0 0

0 1 1 0

1 0 1 1

0 1 0 1

0 0 1 0

0 0 0 1

串行输出

并行输出 DPO

2. 双向移位寄存器

S

DSR 1 1

还可实现串行输入/并行输出。 还可实现串行输入 并行输出。 并行输出

Qn+1=D Q1n+1 = Q0n Q3n+1 =Qn2

Q2 Q2 FF3 1D >C1 Q3 DSO Q3

DSI

Q0 FF1 Q1 FF2 1D 1D 1D >C1 Q0 >C1 Q1 >C1

CP

Q0 FF1 Q1 FF2 00001011 DSI 1D 1D 1D >C1 Q0 >C1 Q1 >C1 FF0 CP

FF0 FF1 FF2 FF3

Q2 Q2

序 号 0 1 2 3 4 5 6 7 8

FF3 1D >C1

Q3 DSO Q3

Q3 0 0 0 0 1 1 0 1 0

Q2 0 0 0 1 1 0 1 0 0

Q1 0 0 1 1 0 1 0 0 0

Q0 0 1 1 0 1 0 0 0 0

Q0n+1=DSI Q1n+1 Q2n+1 Q3

3D

1D

3Q

> C1

R

H H × × × × H L × × × ×

4Q

4D CP 1

1D

> C1

R

RD

1

二、 移位寄存器

•移位寄存器的逻辑功能 移位寄存器的逻辑功能 移位寄存器是既能寄存数码, 移位寄存器是既能寄存数码,又能在时钟脉冲的作用下使数 码向高位或向低位移动的逻辑功能部件。 码向高位或向低位移动的逻辑功能部件。 •移位寄存器的逻辑功能分类 移位寄存器的逻辑功能分类 单向移位寄存器 按移动方式分 双向移位寄存器 右移位寄存器 左移位寄存器

S0

通过控制 S 1 S 0 就可以选择 194的工作状态

RD S S 1 0 0 1 1 1 1 X X 0 0 1 1 0 1 0 1 工作 状态 置零 保持 右移 左移 并行 输入

74194的扩展 的扩展 (用两片 用两片74194组成 位双向移位寄存器 组成8位双向移位寄存器 用两片 组成 位双 + S Q1 D1 = SQ0 + S Q2

D 2 = S Q1 + S Q 3 D 3 = S Q 2 + S D SL

CP CR DOL Q0 Q1 Q2 DOR Q3 &

≥

& FF0 1D > C1 R

≥

& FF1 1D > C1 R

≥

1D >C1 R

&

≥

FF3 1D >C1 R

数据传输方式的转换 串入串出 串入并出 并入并出

并入

串出

串入 左移

串入 右移 并出 并出

并入循环串出

并入 串入 右移 并入 循环右 移串出

串出

串出 右移

移位寄存器在串行通信中的应用

并行数据线 串行通讯线 移 位 寄存器 B 串入-并出 和 并入-串出

并行数据线

计算机 A

移 位 寄存器 A 并入-串出 和 串入-并出

D0 D1D2D3 D4 D5 D6D7

D0 D1D2D3

D4 D5 D6D7

S1 S0 =11 S1 S0 =01

S1 S0 =10 S1 S0 =00 不变

实现多种功能双向移位寄存器的一种方案(仅以FF 为例) 实现多种功能双向移位寄存器的一种方案(仅以FFm为例)

S1S0=00 S1S0=01

Q

Q

n+1 m

= Q

=Q

n m

不变

S1S0=10 Q m

n+1

=Q

n+1 m

n m +1

高位移 向低位

m

n+1 m

n m −1

低位移 向高位

Dm

S1S0=11 Q

= D

并行 输入

S0 S1 FFm–1 D m–1 1D C1

0 3 2 1 0 1 MUX MUX m FFm D m 1D C1

FFm+1 D m+1 1D C1

Q

= D3 = QSL

高位移向低位

器件实例:74LS 194,左/右移,并行输入,保 器件实例: 194, 右移,并行输入, 异步置零等功能 持,异步置零等功能

D1

S1

S1

S0

S Q 1 = S 1 S 0 ⋅ Q1 + S 1 S 0 ⋅ Q0 + S 1 S 0 Q2 + S 1 S 0 D1 RQ 1 = S Q 1 Q1n+1 = S Q 1

4位集成寄存器 位集成寄存器—74LS175 位集成寄存器

1D

1D

1Q

74LS175的功能表 的功能表

输 入 输 出 RD CP 1D 2D 3D 4D 1Q 2Q 3Q 4Q L × × × × × H L L L L

> C1

R

2D

1D

2Q

> C1

R

1D 2D 3D 4D 1D 2D 3D 4D 保 持 保 持

寄存器和移位寄存器 一、 寄存器 寄存器:是数字系统中用来存储代码或数据的逻辑部 寄存器 是数字系统中用来存储代码或数据的逻辑部 它的主要组成部分是触发器。 件。它的主要组成部分是触发器。 一个触发器能存储1位二进制代码, 一个触发器能存储 位二进制代码,存储 n 位二进 位二进制代码 个触发器组成。 制代码的寄存器需要用 n 个触发器组成。寄存器实际 上是若干触发器的集合。 上是若干触发器的集合。

n Q0 +1 = D0 = DSR S=1 n Q1 +1 = D1 = Q 0

Q n +1 = D 2 = Q 1 2 n Q3 +1 = D3 = Q 2

n Q1 +1 = D1 = Q 2 n +1 3

低位移向高位

n S=0 Q0 +1 = D 0 = Q1

Q

n +1 2

= D2 = Q 3

n+1

00001011

n

0 1 0 1 0 1

0 0

0 0

0

= Q0 =Qn

1CP 后 1 2CP 后 1 3CP 后 0 4CP 后 1

1 2

1 1 0

0 1 1

0 0 1

=Qn

DSI =D3 D2 D1 D0 =1101,从高位开始输入 从高位开始输入

经过7个 CP脉冲作用后,从 SI 端串行输入的数码 经过4个 脉冲作用后 脉冲作用后, 经过 个CP脉冲作用后,从DDSi 端串行输入的数 经过 个 脉冲作用后, 脉冲作用后 码就可以从Q Q1 Q2 Q3并行输出。 D 行输出。 并行输出 串入→ 并出 串入→ 码就可以从SO0 端串行输出。输出。 就可以从D O 串入→串出 串入→

工作原理(电路分析) (2). 工作原理(电路分析) 1、了解电路组成 、 2、写出驱动方程: 、写出驱动方程:

D0=DSI D1=Q0n

3、写出状态方程: 、写出状态方程: D触发器的特性方程 触发器的特性方程

D2=Qn1

D3=Qn2

Q0n+1=DSI Q2n+1 =Qn1

D0 D2 D1 D3 FF0

CP Q m–1 Qm Q m+1

计算机 B

4位单向移位寄存器

(1)电路 串行数据输入端 并行数据输出端

DSI

Q0 FF1 Q1 FF2 1D 1D 1D >C1 Q0 >C1 Q1 >C1 FF0

移位脉冲

Q2 Q2

FF3 1D >C1

Q3 DSO Q3

CP

串行数据输出端

∵ 触发器有延迟时间 t pd 到达时, ∴ cp ↑ 到达时,各触发器按前 一级触发器原来的状态 翻转

1 C DSI 1

Q0 0 Q1 0 Q2 0 Q3(DSO) 0

2 1 0

3 1

4

5

6

7

8

1 0 0 0

1 1 0 0

0 1 1 0

1 0 1 1

0 1 0 1

0 0 1 0

0 0 0 1

串行输出

并行输出 DPO

2. 双向移位寄存器

S

DSR 1 1

还可实现串行输入/并行输出。 还可实现串行输入 并行输出。 并行输出

Qn+1=D Q1n+1 = Q0n Q3n+1 =Qn2

Q2 Q2 FF3 1D >C1 Q3 DSO Q3

DSI

Q0 FF1 Q1 FF2 1D 1D 1D >C1 Q0 >C1 Q1 >C1

CP

Q0 FF1 Q1 FF2 00001011 DSI 1D 1D 1D >C1 Q0 >C1 Q1 >C1 FF0 CP

FF0 FF1 FF2 FF3

Q2 Q2

序 号 0 1 2 3 4 5 6 7 8

FF3 1D >C1

Q3 DSO Q3

Q3 0 0 0 0 1 1 0 1 0

Q2 0 0 0 1 1 0 1 0 0

Q1 0 0 1 1 0 1 0 0 0

Q0 0 1 1 0 1 0 0 0 0

Q0n+1=DSI Q1n+1 Q2n+1 Q3

3D

1D

3Q

> C1

R

H H × × × × H L × × × ×

4Q

4D CP 1

1D

> C1

R

RD

1

二、 移位寄存器

•移位寄存器的逻辑功能 移位寄存器的逻辑功能 移位寄存器是既能寄存数码, 移位寄存器是既能寄存数码,又能在时钟脉冲的作用下使数 码向高位或向低位移动的逻辑功能部件。 码向高位或向低位移动的逻辑功能部件。 •移位寄存器的逻辑功能分类 移位寄存器的逻辑功能分类 单向移位寄存器 按移动方式分 双向移位寄存器 右移位寄存器 左移位寄存器

S0

通过控制 S 1 S 0 就可以选择 194的工作状态

RD S S 1 0 0 1 1 1 1 X X 0 0 1 1 0 1 0 1 工作 状态 置零 保持 右移 左移 并行 输入

74194的扩展 的扩展 (用两片 用两片74194组成 位双向移位寄存器 组成8位双向移位寄存器 用两片 组成 位双 + S Q1 D1 = SQ0 + S Q2

D 2 = S Q1 + S Q 3 D 3 = S Q 2 + S D SL

CP CR DOL Q0 Q1 Q2 DOR Q3 &

≥

& FF0 1D > C1 R

≥

& FF1 1D > C1 R

≥

1D >C1 R

&

≥

FF3 1D >C1 R

数据传输方式的转换 串入串出 串入并出 并入并出

并入

串出

串入 左移

串入 右移 并出 并出

并入循环串出

并入 串入 右移 并入 循环右 移串出

串出

串出 右移

移位寄存器在串行通信中的应用

并行数据线 串行通讯线 移 位 寄存器 B 串入-并出 和 并入-串出

并行数据线

计算机 A

移 位 寄存器 A 并入-串出 和 串入-并出

D0 D1D2D3 D4 D5 D6D7

D0 D1D2D3

D4 D5 D6D7

S1 S0 =11 S1 S0 =01

S1 S0 =10 S1 S0 =00 不变

实现多种功能双向移位寄存器的一种方案(仅以FF 为例) 实现多种功能双向移位寄存器的一种方案(仅以FFm为例)

S1S0=00 S1S0=01

Q

Q

n+1 m

= Q

=Q

n m

不变

S1S0=10 Q m

n+1

=Q

n+1 m

n m +1

高位移 向低位

m

n+1 m

n m −1

低位移 向高位

Dm

S1S0=11 Q

= D

并行 输入

S0 S1 FFm–1 D m–1 1D C1

0 3 2 1 0 1 MUX MUX m FFm D m 1D C1

FFm+1 D m+1 1D C1

Q

= D3 = QSL

高位移向低位

器件实例:74LS 194,左/右移,并行输入,保 器件实例: 194, 右移,并行输入, 异步置零等功能 持,异步置零等功能

D1

S1

S1

S0

S Q 1 = S 1 S 0 ⋅ Q1 + S 1 S 0 ⋅ Q0 + S 1 S 0 Q2 + S 1 S 0 D1 RQ 1 = S Q 1 Q1n+1 = S Q 1

4位集成寄存器 位集成寄存器—74LS175 位集成寄存器

1D

1D

1Q

74LS175的功能表 的功能表

输 入 输 出 RD CP 1D 2D 3D 4D 1Q 2Q 3Q 4Q L × × × × × H L L L L

> C1

R

2D

1D

2Q

> C1

R

1D 2D 3D 4D 1D 2D 3D 4D 保 持 保 持