Cortex M3学习笔记 02 寄存器,中断控制器

第9章-Cortex-M3异常和中断

第九章Cortex-M3异常和中断9.1Cortex-M3异常91C t M39.2NVIC与中断控制929.1.1 异常类型异常。

CM3支持为所有能打断正常执行流的事件都称为CM3支持为数众多的系统异常和外部中断。

异常是另一种形式的中断,它是由内部fault引起的,或者内核的SysTick、SVCall等。

而中断是由随机的外部事件引发的。

件引发的编号为1~15的对应系统异常;编号为16~255的对应外部中断。

除了个别异常的优先级被定死外,其它异常的优先级都是可编程的。

可编程的当前运行的异常编号,是由特殊寄存器IPSR或NVIC的中断控制状态寄存器来给出的。

断控制状态寄存器来给出的异常表异常号异常类型优先级描述0N/A N/A没有异常在运行1复位-3 (最高)复位2NMI-2 不可屏蔽中断(外部NMI 输入)3硬件fault-1各种fault情况4内存管理fault可编程内存管理fault;MPU 访问非法地址5总线fault可编程总线fault,比如预取终止6用法fault可编程由于程序fault或尝试访问协处理器导致的异常7-10保留N/A—11SVCall可编程系统服务调用12调试监视器可编程调试监视器(续)13保留N/A—14PendSV可编程可挂起系统设备申请15SysTick可编程系统时钟定时器16外部中断#0可编程外部中断17外部中断#1可编程外部中断…………255外部中断#239可编程外部中断当一个被使能的异常发生时,如果它不能够被立即执行,它将被挂起(pending)。

9.1.2 优先级定义在CM3中优先级对于异常来说很关键的它决定一个 在CM3中,优先级对于异常来说很关键的,它决定个异常是否能被屏蔽,以及在未被屏蔽的情况下何时可以响应。

应优先级的数值越小,则优先级越高。

CM3支持中断嵌套,使得高优先级异常会抢占(preempt)低优先级异常。

3个系统异常:复位、NMI以及硬fault有固定的优先级,并且它们的优先级号是负数,从而高于所有其它异常。

Cortex-M3寄存器等基础知识

Cortex-M3寄存器等基础知识1.寄存器 CM3拥有R0~R15通⽤寄存器和⼀些特殊功能寄存器 R0~R12这些通⽤寄存器,复位初始值都是不可预料的2.CM3有R0到R15的通⽤寄存器组注:绝⼤部分的16位thumb只能访问R0到R7,⽽32位thumb-2可以访问全部寄存器3.特殊功能寄存器3.1程序状态寄存器组(应⽤程序PSR+中断号PSR+执⾏PSR)3.2中断屏蔽寄存器组:⽤于控制异常的除能和使能3.3控制寄存器:⽤于定义特权级别和当前使⽤哪个堆栈指针4.操作模式和特权级别:两种操作模式(处理器模式):Handler模式和线程模式(⽤于区分异常服务例程的代码和普通程序的代码)两种特权等级:特权级和⽤户级(是指在硬件层⾯上对存储器访问权限的设置)注:CM3在运⾏主程序(即线程模式)可以使⽤特权级别和⽤户级别;但是异常服务例程(即handler模式)只能使⽤特权级别。

当处于线程+⽤户模式时⼀些访问权限将被禁⽌将代码区分成⽤户级和特权级,有利于程序架构的稳定,如某⼀个⽤户代码出问题,不会使其成为害群之狗,因为⽤户级别的代码是禁⽌对⼀些要害寄存器操作的。

5.异常处理5.1CONTROL[0]=0;5.2CONTROL[0]=1;CONTROL[0]只有在特权级别下可以访问,若在⽤户级别想访问先通过"系统服务呼叫指令(SVC)"来触发SVC异常,然后在该异常的服务例程中可以修改CONTROL[0]。

6.下⾯是各操作模式的转换7.异常和中断可以有11个系统异常和最多240个外部中断(IRQ),具体芯⽚使⽤了多少要看芯⽚制造⼚商。

作为中断功能的强化,NVIC 还有⼀条NMI输⼊信号线,具体做什么由芯⽚制造商决定,NMI(not masked interrupted)8.向量表:当⼀个异常被CM3内核接受。

对应的异常Handler就会执⾏,向量表⽤来决定Handler的⼊⼝地址。

CortexM3处理器异常事件相关寄存器

0xE000_E100

SETENA1 ……

SETENA7

0xE000_E104 0xE000_E11C

类型 R/W R/W

R/W

复位值 0 0

描述 中断 0-31 的使能寄存器,共 32 个使能控制位[n],中断 n 使能 (异常号 16+n) 中断 32-63 的使能寄存器,共 32 个使能控制位

类型 复位值

描述

PRI_4

0xE000_ED18 R/W

存储器管理 fault 异常事件模块的优先级

PRI_5

0xE000_ED19 R/W

总线 fault 异常事件模块的优先级

PRI_6

0xE000_ED1A R/W

用法 fault 异常事件模块的优先级

——

0xE000_ED1B —— ——

——

0xE000_ED1C —— ——

12 USGFAULTPENDED R/W

0

用法 fault 悬起,当前有更高优先级的异常执行中。

2) 中断控制及状态寄存器(地址:ICSR 0xE000_ED04)。以存储器映射的方式来访问。

位段

名称

类型

复位值

描述

31

NMIPENDSET

R/W

0

写 1 悬起 NMI,立即进入 NMI 服务例程(因为 NMI 不可能被屏蔽)。

说明:51 系列无此特性。

位段

名称

类型 复位值

描述

23

ISRPREEMPT

R

0 如为 1,表示一个悬起的异常将在下一时刻进入活动状态。

22

ISRPENDING

R

0 如为 1,表示当前正有外部中断被悬起(不包括 NMI)

ARMCortex-M3学习笔记

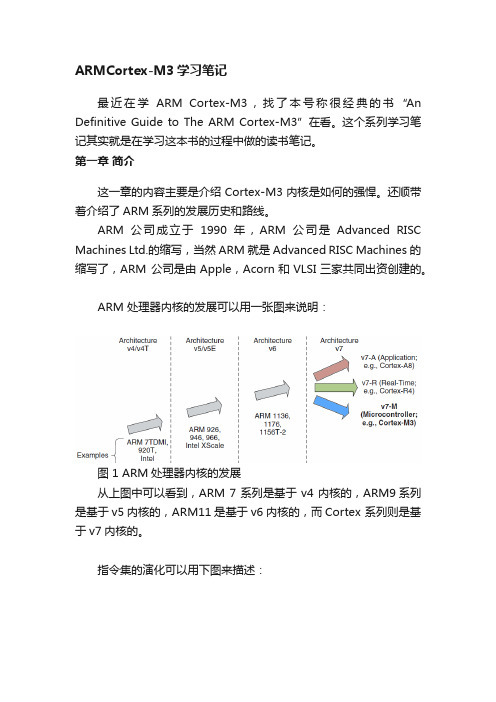

ARMCortex-M3学习笔记最近在学ARM Cortex-M3,找了本号称很经典的书“An Definitive Guide to The ARM Cortex-M3”在看。

这个系列学习笔记其实就是在学习这本书的过程中做的读书笔记。

第一章简介这一章的内容主要是介绍Cortex-M3内核是如何的强悍。

还顺带着介绍了ARM系列的发展历史和路线。

ARM公司成立于1990年,ARM公司是Advanced RISC Machines Ltd.的缩写,当然ARM就是Advanced RISC Machines的缩写了,ARM 公司是由Apple,Acorn和VLSI三家共同出资创建的。

ARM 处理器内核的发展可以用一张图来说明:图 1 ARM处理器内核的发展从上图中可以看到,ARM 7 系列是基于 v4 内核的,ARM9系列是基于v5内核的,ARM11是基于v6内核的,而Cortex 系列则是基于v7内核的。

指令集的演化可以用下图来描述:图 2指令集演进图Cortex-M3 采用Thumb-2指令集,不支持ARM指令集,对Thumb-2指令集其实也只是部分的支持,有很少一部分Thumb-2指令是不支持的。

由于不支持ARM指令集,也就没有了处理器状态在Thumb和ARM之间来回的切换,省去了很多麻烦。

第二章 Cortex-M3 概述Cortex M3 内核的组成可以用一张简图来表示:图 3 Cortex-M3内核简图内核寄存器组包括R0-R15,R0-R12是通用寄存器,部分Thumb 指令只能访问R0-R7。

R13是堆栈指针,实际上有两个,一个是主堆栈指针(MSP)另一个是进程堆栈指针(PSP),堆栈要求4字节对齐。

R14存放程序的返回地址。

R15是PC,记录程序当前的执行地址。

特殊功能寄存器包括:程序状态字寄存器组(PSRs)中断屏蔽寄存器组(PRIMASK, FAULTMASK, BASEPRI)控制寄存器(CONTROL)运行模式和特权级别两种运行模式:handler mode和thread mode。

ARMCortex-M3处理器学习总结

ARMCortex-M3处理器学习总结ARMCortex-M3处理器学习总结在学习了《嵌入式Linux系统》这门课后,本人简单学习了ARMCortex-M3处理器,有了一点粗略的认识,下面将从性能,特性,用途这三方面来介绍ARMCortex-M3处理器。

1性能参数Cortex‐M3是一个32位处理器内核。

内部的数据路径是32位的,寄存器是32位的,存储器接口也是32位的。

CM3采用了哈佛结构,拥有独立的指令总线和数据总线,可以让取指与数据访问并行不悖。

这样一来数据访问不再占用指令总线,从而提升了性能。

为实现这个特性,CM3内部含有好几条总线接口,每条都为自己的应用场合优化过,并且它们可以并行工作。

但是另一方面,指令总线和数据总线共享同一个存储器空间(一个统一的存储器系统)。

比较复杂的应用可能需要更多的存储系统功能,为此CM3提供一个可选的MPU,而且在需要的情况下也可以使用外部的cache。

另外在CM3中,Both小端模式和大端模式都是支持的。

CM3内部还附赠了好多调试组件,用于在硬件水平上支持调试操作,如指令断点,数据观察点等。

另外,为支持更高级的调试,还有其它可选组件,包括指令跟踪和多种类型的调试接口。

2特性ARMCortex-M3的特性总结为以下几方面:●功耗低。

延长了电池的寿命——这简直就是便携式设备的命门(如无线网络应用)。

●实时性好。

采用了很前卫甚至革命性的设计理念,使它能极速地响应中断,而且响应中断所需的周期数是确定的。

●代码密度得到很大改善。

一方面力挺大型应用程序,另一方面为低成本设计而省吃俭用。

●使用更方便。

现在从8位/16位处理器转到32位处理器之风刮得越来越猛,更简单的编程模型和更透彻的调试系统,为与时俱进的人们大大减负。

●低成本的整体解决方案。

让32位系统比和8位/16位的还便宜,低端的Cortex‐M3单片机甚至还卖不到1美元。

●遍地开花的优秀开发工具。

免费的,便宜的,全能的,要什么有什么。

CortexM3处理器异常事件相关寄存器

6

——

—— —— ——

5

——

—— —— ——

4

——

—— —— ——

3

USGFAULTACT

R

0 用法 fault 异常事件模块处于活动状态

2

——

—— —— ——

1

BUSFAULTACT

R

0 总线 fault 异常事件模块处于活动状态

0

MEMFAULTACT

R

0 存储器管理 fault 异常事件模块处于活动状态

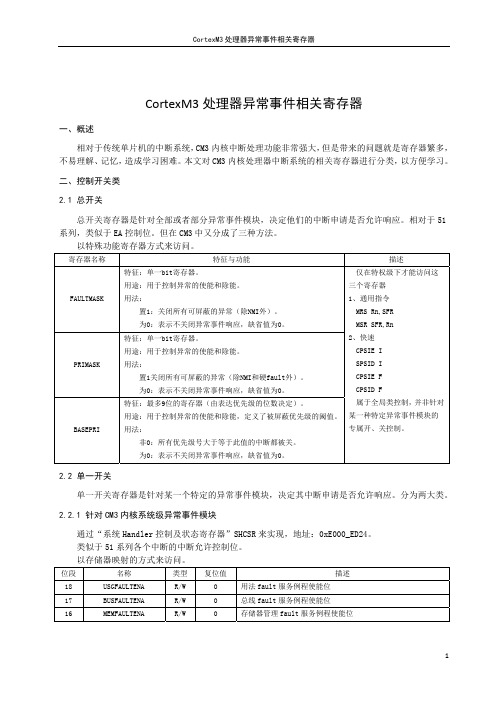

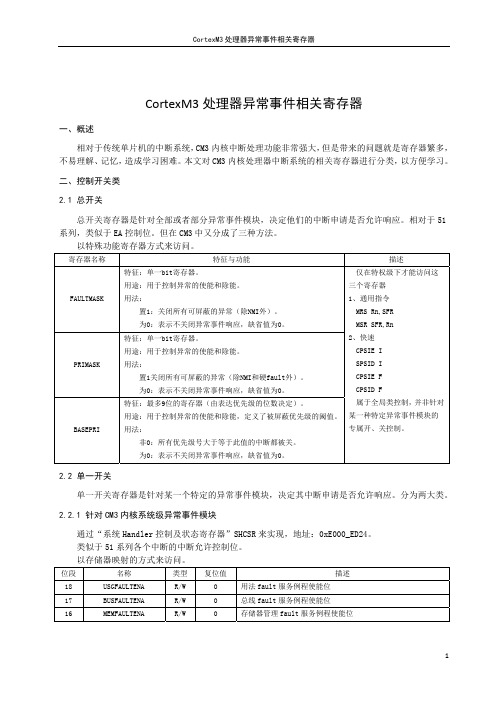

CortexM3 处理器异常事件相关寄存器

CortexM3 处理器异常事件相关寄存器

一、概述

相对于传统单片机的中断系统,CM3 内核中断处理功能非常强大,但是带来的问题就是寄存器繁多, 不易理解、记忆,造成学习困难。本文对 CM3 内核处理器中断系统的相关寄存器进行分类,以方便学习。

二、控制开关类

2.1 总开关

1) 总标识:是内核提供的申请标识。 2) 子标识:是外设模块自己提供的具体中断申请标识(参见具体芯片手册)。

注 1:类似于 51 系列的各个中断的中断标识位。

注 2:可以人工写 1 来产生软件中断申请。

3.1 针对 CM3 内核系统级异常事件模块

1) 系统 Handler 控制及状态寄存器 SHCSR(地址:0xE000_ED24)。以存储器映射的方式来访问。

位段

名称

类型

复位值

描述

15 SVCALLPENDED R/W

0

SVC 悬起,当前有更高优先级的异常执行中。

14 BUSFAULTPENDED R/W

0

总线 fault 悬起,当前有更高优先级的异常执行中。

13 MEMFAULTPENDED R/W

STM32中用到的- Cortex M3寄存器说明

vu32 VTOR;

vu32 AIRCR;

vu32 SCR;

vu32 CCR;

vu32 SHPR[3];

vu32 SHCSR;

vu32 CFSR;

vu32 HFSR;

vu32 DFSR;

vu32 MMFAR;

vu32 BFAR;

一、NVIC寄存器组

STM32的固件库中有如下定义:

typedef struct

{

vu32 ISER[2];

u32 RESERVED0[30];

vu32 ICER[2];

u32 RSERVED1[30];

vu32 ISPR[2];

u32 RESERVED2[30];

IABR = ACTIVE寄存器族(Interrupt Active Bit Register)

IPR = 中断优先级寄存器阵列(Interrupt Priority Registers)

二、系统控制寄存器组

STM32的固件库中有如下定义:

typedef struct

{

vuc32 CPUID;

CCR = 配置与控制寄存器 (Configuration Control Register)

SHPR = 系统异常优先级寄存器(System Handlers Priority Register)

SHCSR = 系统Handler控制及状态寄存器(System Handler Control and State Register)

STM32中用到的Cortex-M3寄存器说明

在STM32中用到了Cortex-M3定义的三组寄存器,有关这三组寄存器的说明不在STM32的技术手册中,需要参考ARM公司发布的Cortex-M3 Technical Reference Manual (r2p0)。

armcortexm3权威指南读书笔记

armcortexm3权威指南读书笔记chapterI 介绍ARMv7 A:用于高性能的“开放应用平台”——越发接近电脑R:用于高端嵌入式系统,尤其是那些带有实时要求的——既要快又要实时M:用于深度嵌入的、单片机风格的系统中Chapter II CORTEX-M3概览哈佛结构拥有独立的指令总线和数据总线,但这两条总线共享一个存储器空间CM3拥有R0~R15的寄存器组,其中R13作为堆栈指针SP。

SP 有两个,但在同一时刻只能看到一个,这就是所谓的"banked"寄存器。

1.R0~R12是32位通用寄存器,用于数据操作。

!!:绝大多数16位的thumb指令只能访问R0~R7,而32位的thumb指令可以访问全部寄存器。

2.banked R13:两个堆栈指针主堆栈指针(MSP):复位后默认使用进程堆栈指针(PSP):由用户的应用程序代码使用堆栈指针的最低两位永远是0,这意味着堆栈总是4字节对齐的。

实际上,R13的最低两位被硬线连接到0。

3.R14:连接寄存器:当调用一个子程序时,由R14存储返回地址4.R15:程序计数寄存器:只向当前程序地址5.特殊功能寄存器:程序状态子寄存器组(PSR)中断屏蔽寄存器组(primask,faultmask,besepri)控制寄存器(control)还支持两级特权操作:特权级和用户级在CM3运行主应用程序时(thread mode),既可以使用用户特权级,也可以使用用户级;但是异常服务例程必须在特权级下执行。

复位后,默认进入thread mode,特权级访问。

在特权级下,程序可以访问所有范围的存储器(如果有MPU,则必须在MPU规定范围之外),并且可以执行所有指令。

一旦进入用户级,想要进入特权级必须:执行一条系统调用指令(SVC),这会出发SVC异常,然后由异常服务例程接管,如果批准进入,则异常服务例程修改control寄存器,才能在用户级的thread mode 下重新进入特权级。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Cortex M3学习笔记 02寄存器,中断控制器好像百度看了我的文章一样,上次笔记中写了一些对抱怨审核太慢的内容,结果第二天就审核好了,不知道这次速度怎么样……1、名词定义MSP:主堆栈指针;PSP:进程堆栈指针;2、寄存器通用寄存器:32位一个,不多说,一共22个。

R0~R15,其中R13是个有两个堆栈指针寄存器的功能,一共17个;另外还有5个特殊功能寄存器。

下面来理解。

a) 通用寄存器R0~R12:用于数据操作,使用Thumb-2可以全部访问,使用Thumb只能访问R0~R7。

R13:堆栈指针(SP):包括主堆栈指针(MSP),进程堆栈指针(PSP)PUSH和POP指令的用法解释:PUSH {R0} // *(--R13)=R0;R13是long*型指针POP {R0} // R0=*R13++R13的最低两位强制为0,且读取同样也为0;R14:连接寄存器(LR):保存子程序返回时的地址;R15:程序计数器(PC):PC返回的地址是当前那指令的地址+4。

例如: 0x4000 MOV R0 , PC ; //R0=0x4004;当针对执行一条写入R15指令时,写入R15的地址被当成一个指令地址,程序从这个地址处开始执行,但是不更新LR寄存器,相当于引发一次跳转;PC的LSB读回内容始终为0,不论是直接写入PC的值,还是使用分支跳转命令,都要求加载到PC的值是奇数(LSB=1),用以表明处理器是在Thumb状态下执行。

若写入0,则视为企图跳转到ARM模式,Cortex-M3将产生一个fault异常。

b) 特殊功能寄存器程序状态寄存器组(PSRs);分为:应用状态寄存器(APSR)为[27~31];中断状态寄存器(IPSR)为[0~8];执行状态寄存器(EPSR)为[10~15],[24~26];共计32位自己画个0~31的寄存器 “位”表格,很直观。

中断屏蔽寄存器组(PRIMASK、FAULTMASK、BASEPRI);PRIMASK相当于中断总开关,当PRIMASK=1时,屏蔽所有中断(除NMI和fault外)。

FAULTMASK屏蔽错误中断。

BASEPRI优先级屏蔽寄存器中断。

控制寄存器(CONTROL)。

第1.定义特权级别:特权级线程模式,用户级线程模式;CONTROL[0]=0是特权级;CONTROL[0]=1是用户级;第2.选择当前堆栈指针:主堆栈MSP,备用堆栈。

CONTROL[1]=0是主堆栈(复位缺省);CONTROL[1]=1是备用堆栈,特殊功能寄存器不存在地址,只能被专用的MSR和MRS指令访问。

使用方式:MRS <gp_reg> , <special_reg>;读特殊功能寄存器的值到通用寄存器;MSR <special_reg> , <gp_reg>;写通用寄存器的值到特殊功能寄存器;其中<gp_reg>是通用寄存器,<special_reg>是特殊寄存器;例如:· MOV R0,#0x01;MOV RPIMASK,R0;· MOV R0,0x60;MOV BASEPRI,R0;3、CortexM3操作模式和特权级别分为两种模式;两种级别:a) 操作模式:线程模式(Thread mode),处理模式(handlermode);线程模式:在此模式中程序指令逐一运行;处理模式:在程序执行过程中,触发了一个异常后,处理器将进入到处理模式;处理结束后返回之前的状态。

b) 特权级别:特权级,用户级;特权级:系统开启后默认进入。

无限制。

用户级:处理器将禁止对系统控制区域(SCS)(包含配置寄存器和调试组建的存储区域)的访问。

画个表格:代码作用特权级用户级异常handler代码Handler模式错误,不可操作线程模式主应用程序代码线程模式(复位后默认进入的模式)这样可以直观的看出,处理模式下,只提供特权级的代码才能访问。

好处不多说了,保护关键区域代码安全,防止有意无意的篡改。

·思考一下,上面说过CONTROL寄存器的可以更改特权;程序启动后,线程模式会在CONTROL的指引下进入从特权级转为用户级运行,如果在用户级下面MSR命令自然是不能更改CONTROL特权的,那么如何解决?答案:刚才表格中说了handler模式下肯定是特权级的,那么我们就利用handler模式来解决这个问题。

在中断处理的时候(handler mode),加入代码:MRS R0,CONTROL;//读取CONTROL;BIC.W R0,R0,#0x01;//清零CONTROL[0];MSR CONTROL,R0;//将清零的内容写入CONTROL;这样CONTROL[0]就等于0了,变成特权级;程序返回后,继续往下执行,就是在特权级下的指令执行了。

记得利用MSR+CONTROL返回用户级;如此再加上MPU设备,书上这样形容:安全,健壮……4、CortexM3的异常、中断及向量表“中断”和“异常”,经常被混合使用,强调他们对主程序的执行所体现的“中断”性质。

书本不强调他们之间的区别。

若一定要区别:可以理解“异常”由指令执行或访问存储器时产生,例如:存储单元的值改变;而“中断”可以理解为“中断请求信号”一般由外部产生,例如:外设信息处理请求;Cortex M3处理器在内核水平上搭载了一个中断控制器——嵌套向量中断控制器NVIC(Nested Vectored Interrupt Controller),可实现非常高校的异常处理。

取消FIQ(快速中断处理),取而代之的是“嵌套中断支持”和“优先级管理”。

1. 嵌套中断支持,在下面的“优先级分组”中介绍。

2. 向量中断支持,Cortex M3会自动定位一张向量表,根据中断号从表中找出相应中断的入口地址,然后跳转过去执行。

3. 异常类型,支持11种系统异常和240种外部中断输入。

其中1~15对应的是系统异常,大于等于16的则全是外部中断。

大部分异常的优先级是可编程的,出了部分固定的。

编号类型优先级描述1复位-3(最高)复位2NMI-2不可屏蔽中断(来自外部NMI引脚)3Hard fault-1所有被除能的fault,都将上访(escalation)成硬fault。

只要FAULTMASK没有置位,硬fault服务例程就会被强制执行。

Fault被除能的原因包括被禁用,或者FAULTMASK被置位。

4存储器管理fault可编程存储器管理fault,MPU访问违规或访问非法位置均可引发。

企图在“非执行区”取指也会引发此fault。

5总线fault可编程总线错误,当AHB接口收到总线系统的错误响应时发生(也称为预取中止或是数据中止)。

6用法fault可编程由于程序错误或企图访问协处理器(Cortex M3不支持协处理器)导致的异常。

7~10保留NA NA11SVCall可编程执行系统服务调用指令(SVC)引发的异常。

12调试监视器可编程调试监视器(断点,数据观察点或外部调试请求)13保留NA NABit[7]Bit[6]Bit[5]Bit[4]Bit[3]Bit[2]Bit[1]Bit[0]用于表达优先级不执行,读回为零14PendSV 可编程为系统设备而设的“挂起请求”(pendablerequest )15SysTick 可编程系统节拍定时器16~255外部中断可编程Cortex M3内核之外产生的中断(0~239)上边的“优先级表”中-3,-2,-1始终会高于0,所以画个数轴,就明白了“数值越小,优先级越高”的道理,但是“可编程”的优先级不存在负数……。

系统异常是Cortex M3内核支持的基本异常,与具体芯片无关,而外部中断则与芯片相关,芯片厂商会根据需要和用途设计中断源数目(1~240)和优先级的位数。

例如:NXP 公司的LPC1752支持35个外部中断和32个中断优先级。

注4. 异常优先级,优先级数值越小,则级别越高(前面提过,批注A7)。

Cortex M3中:复位、NMI 、硬fault 是固定优先级。

5. 优先级配置寄存器,理论上一个字节Bit[0~7],可以表示256个优先级,但是实际上为了精简设计芯片设计商会裁剪掉部分低端有效位。

注例如:Bit[7]Bit[6]Bit[5]Bit[4]Bit[3]Bit[2]Bit[1]Bit[0]用于表达优先级不执行,读回为零优先级为:0x00(最高)、0x20、0x40、0x60、0x80、0xA0、0xC0、0xE0。

或者6. 优先级分组:·思考一下,既然中断响应的优先级已经分了,为什么还要分组呢?书本上介绍并不详细,看了一些资料,才弄明白,这个部分其实很重要。

简单分析一下,我们知道,程序在运行时,当多个中断来的时候,根据优先级的高低来处理中断请求的。

那么问题来了,如果正在响应一个异常时,突然来了一个优先级比较高的异常,那么我们是放下当前正在响应的异常,去执行新来的这个?还是继续响应当前的异常,直到处理完毕,再去考虑那个新异常的优先级呢?Bit[7]Bit[6]Bit[5]Bit[4]Bit[3]Bit[2]Bit[1]Bit[0]抢占优先级子优先级不执行,读回为零Bit[7]Bit[6]Bit[5]Bit[4]Bit[3]Bit[2]Bit[1]Bit[0]抢占优先级子优先级不执行,读回为零Bit[7]Bit[6]Bit[5]Bit[4]Bit[3]Bit[2]Bit[1]Bit[0]抢占优先级抢占优先级(不执行)子优先级(不执行)分组位置Bit[7]Bit[6]Bit[5]Bit[4]Bit[3]Bit[2]Bit[1]Bit[0]7Bit[7]Bit[6]Bit[5]Bit[4]Bit[3]Bit[2]Bit[1]Bit[0]6Bit[7]Bit[6]Bit[5]Bit[4]Bit[3]Bit[2]Bit[1]Bit[0]5Bit[7]Bit[6]Bit[5]Bit[4]Bit[3]Bit[2]Bit[1]Bit[0]4Bit[7]Bit[6]Bit[5]Bit[4]Bit[3]Bit[2]Bit[1]Bit[0]3Bit[7]Bit[6]Bit[5]Bit[4]Bit[3]Bit[2]Bit[1]Bit[0]2Bit[7]Bit[6]Bit[5]Bit[4]Bit[3]Bit[2]Bit[1]Bit[0]答案:Cortex M3提供了“抢占式优先级”和“子优先级”来解决这个问题。

(有地方对“子优先级”叫做“副优先级”或“响应优先级”,无所谓叫什么,关键是通途)看看下表,Cortex M3将“优先级配置寄存器”划分为两组,这样的分组信息保存在AIRCR 中。