直接数字合成器通信原理课程设计

直接数字式频率合成器

实验八 直接数字式频率合成器(DDS )程序设计与仿真实验1 实验目的(1) 学习利用EDA 技术和FPGA 实现直接数字频率合成器的设计。

(2) 掌握使用Quartus Ⅱ原理图输入设计程序。

2 实验仪器(1)GW48系列SOPC/EDA 实验开发系统(2)配套计算机及Quartus II 软件3 实验原理直接数字频率合成技术,即DDS 技术,是一种新型的频率合成技术和信号产生方法。

其电路系统具有较高的频率分辨率,可以实现快速的频率切换,并且在改变时能够保持相位的连续,很容易实现频率、相位和幅度的数控调制。

传统的生成正弦波的数字是利用—片ROM 和一片DAC ,再加上地址发生计数器和寄存器即可。

在ROM 中,每个地址对应的单元中的内容(数据)都相应于正弦波的离散采样值,ROM 中必须包含完整的正弦波采样值,而且还要注意避免在按地址读取ROM 内容时可能引起的不连续点,避免量化噪音集中于基频的谐波上。

时钟频率f clk 输入地址发生计数器和寄存器,地址计数器所选中的ROM 地址的内容被锁入寄存器,寄存器的输出经DAC 恢复成连续信号,即由各个台阶重构的正弦波,若相位精度n 比较大,则重构的正弦波经适当平滑后失真很小。

当f clk 发生改变,则DAC 输出的正弦波频率就随之改变,但输出频率的改变仅决定于f clk 的改变。

为了控制输出频率更加方便,可以采用相位累加器,使输出频率正比于时钟频率和相位增量之积。

图1所示为采用了相位累加方法的直接数字合成系统,把正弦波在相位上的精度定为n 位,于是分辨率相当于1/2n 。

用时钟频率f P 依次读取数字相位圆周上各点,这里数字值作为地址,读出相应的ROM 中的值(正弦波的幅度),然后经DAC 重构正弦波。

这里多了一个相位累加器,它的作用是在读取数字相位圆周上各点时可以每隔M 个点读一个数值,M 即力图1中的频率字。

这样,DAC 输出的正弦波频率f sin 就等于“基频” f clk 1/2n 的M 倍,即DAC 输出的正弦波的频率满足下式:)2(sin n clk f M f (1)这里,f clk 是DDS 系统的工作时钟,式(6-1-1)中的n 通常取值在24~32之间,由图1可知,相位分辨率至少是1/16777216,相当于2.146x10-5度。

通信原理实验报告

实验1 DDS信号源实验一、实验目的1.了解DDS信号源的组成及工作原理;2.掌握DDS信号源使用方法;3.掌握DDS信号源各种输出信号的测试。

二、实验器材1.DDS信号源(位于大底板左侧,实物图片如下)2. 20M双踪示波器1台三、实验原理直接数字频率合成(DDS—Digital Direct Frequency Synthesis),是一种全数字化的频率合成器,由相位累加器、波形ROM、D/A转换器和低通滤波器构成。

时钟频率给定后,输出信号的频率取决于频率控制字,频率分辨率取决于累加器位数,相位分辨率取决于ROM的地址线位数,幅度量化噪声取决于ROM 的数据位字长和D/A转换器位数。

DDS信号源模块硬件上由cortex-m3内核的ARM芯片(STM32)和外围电路构成。

在该模块中,我们用到STM32芯片的一路AD采集(对应插孔调制输入)和两路DAC输出(分别对应插孔P03、P04)。

PWM信号由STM32时钟配置PWM模式输出,调幅、调频信号通过向STM32写入相应的采样点数组,由时钟触发两路DAC同步循环分别输出其已调信号与载波信号。

对于外加信号的AM调制,由STM32的AD对外加音频信号进行采样,在时钟触发下当前采样值与载波信号数组的相应值进行相应算法处理,并将该值保存输出到DAC,然后循环进行这个过程,就实现了对外部音频信号的AM调制。

实验箱的DDS信号源能够输出脉宽调制波(PWM)、正弦波、三角波、方波、扫频信号、调幅波(AM)、双边带(DSB)、调频波(FM)及对外部输入信号进行AM 调制输出。

四、各测量点的作用调制输入:外部调制信号输入铆孔(注意铆孔下面标注的箭头方向。

若箭头背离铆孔,说明此铆孔点为信号输出孔;若箭头指向铆孔,说明此铆孔点为信号输入孔)。

P03:DDS各种信号输出铆孔。

P04:20KHZ载波输出铆孔。

P09:抽样脉冲输出铆孔。

SS01:复合式按键旋纽,按键用来选择输出信号状态;旋纽用来改变信号频率。

直接数字合成器DDS设计

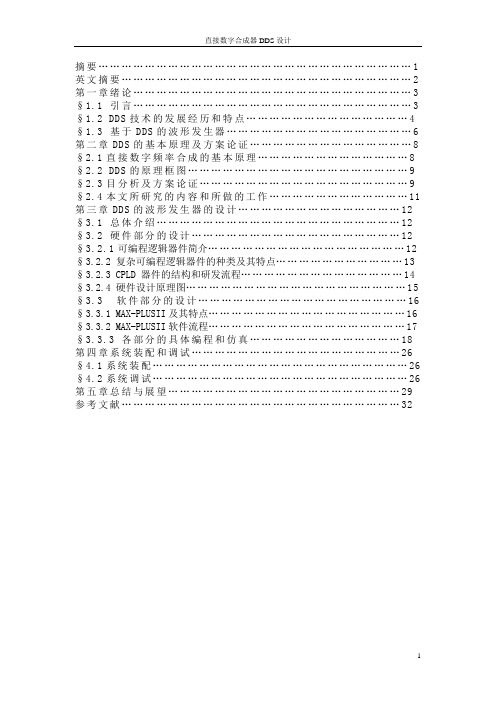

摘要 (1)英文摘要 (2)第一章绪论 (3)§1.1 引言 (3)§1.2 DDS技术的发展经历和特点 (4)§1.3 基于DDS的波形发生器 (6)第二章DDS的基本原理及方案论证 (8)§2.1直接数字频率合成的基本原理 (8)§2.2 DDS的原理框图 (9)§2.3目分析及方案论证 (9)§2.4本文所研究的内容和所做的工作 (11)第三章DDS的波形发生器的设计 (12)§3.1 总体介绍 (12)§3.2 硬件部分的设计 (12)§3.2.1可编程逻辑器件简介 (12)§3.2.2 复杂可编程逻辑器件的种类及其特点 (13)§3.2.3 CPLD 器件的结构和研发流程 (14)§3.2.4 硬件设计原理图 (15)§3.3 软件部分的设计 (16)§3.3.1 MAX-PLUSII及其特点 (16)§3.3.2 MAX-PLUSII软件流程 (17)§3.3.3 各部分的具体编程和仿真 (18)第四章系统装配和调试 (26)§4.1系统装配 (26)§4.2系统调试 (26)第五章总结与展望 (29)参考文献 (32)摘要本文主要研究了基于直接数字合成器(Direct Digital Synthesizer)技术的波形发生器(Arbitrary Waveform Generator)的整体方案和核心部分的硬软件设计。

同时,对整个系统的性能进行了理论分析。

文中讨论了DDS的基本概念和理论,在理论研究的基础上,设计了整个系统的完成方案,用复杂可变成逻辑器件(CPLD)完成了DDS主要部分的设计,其中涉及到软件设计的部分都进行了仿真和说明,从完成电路的性能和综合指标看,基本达到了课题的要求。

关键词:直接数字合成波形发生器输出信号频率:1hz-20MHZ的信号(正弦波、方波、三角波),频率可调、可预置。

毕业设计(论文)-直接数字频率合成器设计[管理资料]

![毕业设计(论文)-直接数字频率合成器设计[管理资料]](https://img.taocdn.com/s3/m/fe683c28ce2f0066f433225f.png)

直接数字频率合成器设计The Design of Direct Digital Frequency Synthesizer摘要利用可编程逻辑阵列FPGA(Field Programmable Gate Array)实现DDS专用电路芯片,主要特点是能满足用户对特殊功能的要求,而且在使用过程中也灵活地改变系统结构。

,并不能满足所有的要求。

本文在对现有DDS技术的大量文献调研的基础上,提出了符合FPGA结构的DDS设计。

方案利用QuartusⅡ开发工具在ALTERA FLEX10K系列器件上进行了实现。

关键词直接数字频率合成器单片机数模转换温度漂移补偿AbstractThe main features of realization of dedicated direct digital frequency synthesizer circuit chips using FPGA are the ability to meet user requirements for special functions, but also flexibility change structural of the system in the use of the process. Although commercial DDS dedicated chip circuit provide a lot of opportunities for the designers and meet the needs of many occasions, there are its limitations and cannot meet all the requirements. On a large number of investigation of existing research literature,the papers involves the proposed structure of the direct digital frequency synthesizer FPGA design. The Programmer uses the Quartus II development tool for designing the Altera FLEX10K series devices.Keywords DDS MCU DAC Temperature drift compensation目录前言 (1)第1章设计思路及原理 (2)研究意义 (2)总体设计任务 (2)设计思路及原理 (3)DDS工作原理框图 (3)具体工作过程 (3)第2章系统电路的设计及原理 (5)系统框图 (5)各模块具体实现原理分析和说明 (5)相位累加器模块 (5)ROM查找表模块 (10)单片机输入输出控制模块 (12)温漂误差补偿 (13)D/A转换模块 (18)滤波输出电路模块 (19)软件仿真结果 (19)第3章硬件电路的构建 (21)FPGA芯片的选择与使用 (21)硬件连接电路图 (23)第4章实验开发系统系统 (25)实验开发系统的选择与使用 (25)实验过程与结果分析 (27)总结....................................................................................... 错误!未定义书签。

EDA课程设计直接数字频率合成器(DDS)

,a click to unlimited possibilities

汇报人:

目录

01 添 加 目 录 项 标 题

02 D D S 的 原 理

03 D D S 的 硬 件 实 现

04 D D S 的 应 用

05 D D S 的 软 件 仿 真 与实现

06 D D S 的 优 化 与 改 进

医疗领域:用于 医疗设备的信号 处理和传输

军事领域:用于 雷达、通信、电 子对抗等设备的 信号处理

工业领域:用于 工业自动化设备 的信号处理和控 制

Part Five

DDS的软件仿真与 实现

软件仿真工具介绍

MATL AB:强大的数学计算和图形处理 能力,适合进行信号处理和仿真

Simulink:MATL AB的扩展工具,可以 进行系统级仿真,支持DDS模块

DDS的动态范围扩展

动态范围扩展原理:通过调整DDS的输出电压和频率,实现动态范围的 扩展 动态范围扩展方法:采用数字信号处理技术,如滤波、放大、压缩等

动态范围扩展效果:提高DDS的输出信号质量,降低噪声和失真

动态范围扩展应用:在通信、雷达、电子对抗等领域具有广泛应用

THANKS

汇报人:

DDS的频率分辨率优化

频率分辨率定义:衡 量DDS性能的重要参 数,表示输出信号的 频率精度和稳定度。

优化方法1:采用高 精度的参考时钟源, 提高时钟频率,减小 DDS的相位截断误差。

优化方法2:增加相 位累加器的位数,扩 大频率调制的范围, 提高频率分辨率。

优化方法3:采用数 字滤波技术,对DDS 输出信号进行滤波处 理,减小杂散分量, 提高频率分辨率。

实际应用:通过对DDS的相位噪声 进行降低,可以提高信号的纯度, 减小干扰和失真,从而提高通信、 雷达、电子对抗等系统的性能。

FPGA技术-直接数字频率合成器

COMPONENT REG32B PORT ( LOAD : IN STD_LOGIC; DIN : IN STD_LOGIC_VECTOR(31 DOWNTO 0); DOUT : OUT STD_LOGIC_VECTOR(31 DOWNTO 0) );

END COMPONENT; COMPONENT REG10B

接下页

PORT ( LOAD : IN STD_LOGIC;

DIN : IN STD_LOGIC_VECTOR(9 DOWNTO 0);

DOUT : OUT STD_LOGIC_VECTOR(9 DOWNTO 0) );

END COMPONENT;

COMPONENT ADDER32B

PORT ( A : IN STD_LOGIC_VECTOR(31 DOWNTO 0);

B : IN STD_LOGIC_VECTOR(31 DOWNTO 0);

S : OUT STD_LOGIC_VECTOR(31 DOWNTO 0) );

END COMPONENT;

COMPONENT SIN_ROM

PORT ( address : IN STD_LOGIC_VECTOR(9 DOWNTO 0);

inclock

: IN STD_LOGIC ;

接下页

q

: OUT STD_LOGIC_VECTOR(9 DOWNTO 0) );

END COMPONENT;

SIGNAL F32B,D32B,DIN32B : STD_LOGIC_VECTOR(31 DOWNTO 0);

为了对进行数字量化,把切割成2N份,由此每个clk周期的 相 为整数

直接数字合成器

第二章DDS的基本理论DDs的基本结构包括:相位累加器、正弦查询表ROM、数模转换器DAC及低通滤波器等。

本章从介绍DDS的工作原理和基本结构出发,分析了它的主要特点及其频谱分布规律。

DDS有两个主要的缺点:一个是输出频率低,另一个是输出频谱中杂散比较多。

输出频谱低主要受DDS工作频率的限制,但随着微电子技术的发展这个缺陷会渐渐地得到弥补。

而DDS输出谱中的杂散是DDS所固有的,是由十DDS的工作方式决定的。

因此了解DDS的杂散分布及幅度大小对DDS的系统设计有很重要的意义,所以本章着重讨论DDS的杂散问题。

2.1 DDS技术的工作原理和主要特点正弦输出DDS的原理框图如下图2.1所示,下面分别加以详细介绍【5】。

相位累加器PA (Phase Accumulator)在K位频率控制字FCW(Frequency Control Word)的控制下,以参考时钟频率关为采样频率,产生待合成信号的数字线性相位序列,将相位累加器的高n位作为地址码通过正弦查询表ROM变换,产生m 位对应信号波形的数字序列,再由数模转换器DAC将其转化为阶梯模拟电压波形,最后由具有内插作用的低通滤波器LPF将其平滑为连续的正弦波形作为输出,这就是DDS的基本工作原理。

当DDS中的相位累加器计数大十2N时,累加器自动溢出其最高位,而累加器输出后面的N比特数字将保留在相位寄存器中,即相当于做2N的模余运算。

可以看出:该相位累加器平均每2N /K个时钟周期溢出一次我们知道,ƒ=ω/2π=Δθ/(2π,Δt),其中Δθ为一个采样周期Δt之间的相位增量,Δt=1/ƒc,Δθ=K×2π/2N。

所以,K和时钟频率ƒc共同决定着DDS输出信号的频率ƒ0,他们之间的关系满足:ƒ0=K2׃c(2-1)DDS的最小频率分辨率满足:Δƒmin =12׃C(2-2)由此可见,DDS相当十一个小数分频器。

最小频率分辨率是指K的最低为“1" 其余位均为“0”时DDS的输出频率。

EDA 课程设计 江西理工 应科院 直接数字频率合成器(DDS)

SOPC/EDA综合课程设计直接数字频率合成器学院:江西理工大学应用科学学院指导老师:王忠峰专业班级:电气081姓名:qq411523540学号:时间:2011年1月目录第一章直接数字频率合成器与设计任务 (3)1.1关于直接数字频率合成器 (3)1.2直接数字频率合成器的设计要求 (3)第二章系统设计方案 (4)2.1 DDS的工作原理 (4)2.2模块的功能 (6)2.3选择器件 (7)2.4功能模块 (8)2.5系统的整体组装 (13)第三章设计的心得体会 (16)附录一参考文献 (17)第一章直接数字频率合成器与设计任务1.1 关于直接数字频率合成器1971年,美国学者J.Tierncy、C.M.Reader和B.Gold提出了以全数字技术从相位概念出发直接合成所需波形的一种新的频率合成原理。

随着技术和水平的提高,一种新的频率合成技术——直接数字频率合成(DDS,Direct Digital Synthesis)技术得到了飞速发展。

DDS技术是一种把一系列数字形式的信号通过DAC转换成模拟形式的信号合成技术,目前使用最广泛的一种DDS方式是利用高速存储器作查找表,然后通过高速DAC输出已经用数字形式存入的正弦波。

DDS技术具有频率切换时间短(<20 ns),频率分辨率高(0.01 Hz),频率稳定度高,输出信号的频率和相位可以快速程控切换,输出相位可连续,可编程以及灵活性大等优点,它以有别于其他频率合成方法的优越性能和特点成为现代频率合成技术中的佼佼者。

DDS广泛用于接受机本振、信号发生器、仪器、通信系统、雷达系统等,尤其适合跳频无线通信系统。

1.2 直接数字频率合成器的设计要求直接数字频率综合技术,即DDS技术,是一种新型的频率合成技术和信号产生方法。

利用EDA技术和FPGA实现直接数字频率合成器DDS的设计。

设计要求:1.利用QuartusII软件实验箱实现DDS的设计;2.通过实验箱上的开关输入DDS的频率和相位控制字,并能用示波器观察加以验证;3.系统具有清零和使能的功能;4.DDS中的波形存储器模块用Altera公司的Cyclone系列FPGA芯片中的ROM实现。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

课程设计课程名称:通信原理课程设计设计名称:基于400MSPS 14-Bit,1.8VCMOS直接数字合成器AD9951专业:班级:姓名:学号:400 MSPS 14-Bit, 1.8 V CMOS直接数字合成器AD9951Abstract:The AD9951 is a direct digital synthesizer (DDS) featuring a 14-bit DAC operating up to 400 MSPS. The AD9951 uses advanced DDS technology, coupled with an internal high speed, high performance DAC to form a digitally programmable, complete high frequency synthesizer capable of generating a frequency-agile analog output sinusoidal waveform at up to 200 MHz. The AD9951 is designed to provide fast frequency hopping and fine tuning resolution (32-bit frequency tuning word). The frequency tuning and control words are loaded into the AD9951 via a serial I/O port. The AD9951 is specified to operate over the extended industrial temperature range of –40°C to +105°C.Synchronizing Multiple AD9951s , The AD9951 product allows easy synchronization of multiple AD9951s. There are three modes of synchronization available to the user: an automatic synchronization mode, a software controlled manual synchronization mode, and a hardware controlled manual synchronization mode. Applications, Agile LO frequency synthesis, Programmable clock generators, Test and measurement equipment ,Acousto-optic device drivers. T he AD9951 supports various clock methodologies. Support for differential or single-ended input clocks and enabling of an on-chip oscillator and/or a phase-locked loop (PLL) multiplier are all controlled via user programmable bits.摘要:AD9951是一个直接数字频率合成器(DDS),其特色是有一个工作在400MSPS的14位数/模转换器(14-bit DAC). AD9951采用了先进的DDS技术,芯片内部有一个高速的,高性能的DAC,能够形成一个数位可编程的,完整的高频合成器DDS系统,有能力产生频率达200 MHz 的模拟正弦波。

AD9951可提供快速频率跳变和高精度分辩率(32位频率控制字)。

频率调谐和控制字经并行口或串行口输入到AD9951。

在工业应用中,AD9951的工作温度为–40°C到+105°C。

同时并联发生AD9951,存在三种可能得到的同步方式电路∶自动同步方式,软件控制手控同步方式,硬件控制手控同步方式。

AD9951可以应用于本机振荡频率合成,可编程时钟发生器,测试和测量装置,声光器件驱动装置。

AD9951在不同的时钟脉冲下有不同的操作方法。

适合于差动或单端输入时钟脉冲并启动芯片内部振荡器及锁相环路(锁相环)放大器全部控制经由用户可编程序的位。

Key words: automatic synchronization modesoftware controlled manual synchronization modea hardware controlled manual synchronization modeSupport for differential input clocksCommon-mode noise increased signal-to-noise ratio关键字:自动同步方式软件控制手控同步方式硬件控制手控同步方式差动输入时钟脉冲共模噪声信噪比主要特性速率为400 MSPSDAC分辨率为14 – bit32位代码相位噪声≤–120 dBc / Hz 1 kHz偏移量( DAC输出功率)有良好的动态特性AOUT >80 dB 160 MHz (±100 kHz偏移量)串联的I / O控制1.8 V电源软件和硬件可控制低功耗采用48引脚 TQFP / EP封装最大导通输入电平5 VPLL REFCLK放大器( 4×- 20×)内部振荡器可以是由单个晶体管驱动具有调相能力多片同步应用本机振荡频率合成可编程时钟发生器测试和测量装置声光器件驱动装置内部结构框图图1Rev.0通过模拟装置调幅被认为是精确的和可靠的装备的资料。

然而、通过模拟装置适合于或非门、其他的三分之一用户可以由它的使用引起。

规格由厂商确定,模拟装置的技术要求明确给出。

标志和安装是由有关技术员确定的。

目录1.芯片简介 (5)2.AD9951的主要电气特征 (5)3.绝对最大额定值 (9)4.AD9951的芯片封装与引脚功能 (9)4.1引脚封装形式 (9)4. 2引脚功能描述 (10)5.内部结构与工作原理 (12)5. 1典型工作动态特征 (12)5. 2工作原理 (17)5. 3工作模式 (22)5. 4AD9951的编程 (22)5. 5串行端口 (26)5. 6指令字节 (27)5. 7串行接口引脚描述 (28)5. 8最高有效位/最小有效位转接 (28)6. 应用电路 (29)7. 封装尺寸 (31)8. 注意ESD (31)9.规则手册 (31)10.设计总结 (32)修改记载修改∶初始的版本1.芯片简介AD9951是一个直接数字频率合成器(DDS),其特点是有一个工作在400MSPS的14位数/模转换器(14bit DAC). AD9951采用了先进的DDS技术,芯片内部有一个高速的,高性能的DAC,能够形成一个数位可编程的,完整的高频合成器DDS系统,有能力产生频率达200 MHz 的模拟正弦波。

AD9951可提供快速频率跳变和高精度分辩率(32位频率控制字)。

频率调谐和控制字经并行口或串行口输入到AD9951。

在工业应用中,AD9951的工作温度为–40°C到+105°C。

2.AD9951的主要电气特性AD9951的主要电气特性如表1所列。

测试条件:若无特别说明, AVDD, DVDD = 1.8 V±5%, DVDD_I / O = 3.3 V±5%, R SET= 3.92 kΩ,基准时钟频率为20 MHz,放大器启动20×.DAC1实现可能达到最好的相位噪声,该振幅可能应用在时钟脉冲上。

减少该时钟输入振幅将减少该相位噪声信息装置。

2、起始时间恢复从模拟断电方式(看该节)。

最长的定时要求该基准钟放大器PLL到该参数值。

该初始值假定是没有电容在DACBP引脚而且最好使用推荐的PLL环路滤波器。

3、SYSCLK 周期引用该实际的时钟脉冲频率应用芯片内通过该DDS。

如果该基准时钟放大器与外部参考时钟脉冲频率并联、该SYSCLK频率是该外部的频率乘以该基准时钟倍增因数。

如果该基准钟放大器没有应用,该SYSCLK频率就等于外部参考时钟脉冲频率。

4、SYNC_CLK = 1/4SYSCLK比率。

因为 SYNC_CLK比率≥50 MHz、用该高速的同步启动位、设置CFR2<11>、。

5、这个参数指出那数字同步特征不能克服在系统时钟上升边之间的相位延迟(定时失真)。

如果该系统时钟边缘是定位、该同步功能在两个之间边缘将不会增加该失真。

3.绝对最大额定值强调超过绝对最大额定值可以永久性损坏该装置。

这是强调额定值和函数运算在该装置其他的情况指出在该操作技术要求明确指出。

超出绝对最大额定值的使用延长周期将会影响器件的可靠性。

图2.输入,输出等效电路4.AD9951的芯片封装与引脚功能4.1引脚封装形式图3引脚封装形式注意接通封装底部裸过露焊盘应当尽可能接近DAC的模拟地,引脚43, DVDD_I/ O,可以是提高到1.8 V或3.3 V;然而, DVDD引脚(引脚2和引脚34)只能是升幂1.8 V。

4.2引脚功能描述AD9951的引脚功能如表3所示。

5.内部结构与工作原理5.1动态曲线特征图4 F OUT = 1 MHz FCLK = 400 MSPS, WBSFDR图5. FOUT =10 MHz, FCLK = 400 MSPS ,WBSFD图6 FOUT = 40 MHz, FCLK = 400 MSPS, WBSFDR图7. FOUT = 80 MHz ,FCLK = 400 MSPS, WBSFDR图8 FOUT = 120 MHz, FCLK = 400 MSPS, WBSFDR图9. FOUT = 160 MHz, FCLK = 400 MSPS, WBSFDR图10. FOUT = 1.1 MHz, FCLK = 400 MSPS, NBSFDR,±1 MHz图11. FOUT = 10 MHz, FCLK = 400 MSPS, NBSFDR,±1 MHz图12. FOUT = 39.9 MHz, FCLK = 400 MSPS, NBSFDR,±1 MHz图13. FOUT = 80.3 MHz, FCLK = 400 MSPS, NBSFDR,±1 MHz图14. FOUT = 120.2 MHz, FCLK = 400 MSPS, NBSFDR,±1 MHz图15. FOUT = 160 MHz, FCLK = 400 MSPS, NBSFDR,±1 MHz图16.残留相位噪声 FOUT = 159.5 MHz, FCLK = 400 MSPS(绿色), 4×100 MSPS(红色), 20× 20MSPS(蓝色)图17.残留相位噪声FOUT = 9.5 MHz, FCLK = 400 MSPS(绿色),4×100MSPS(红色), 20× 20 MSPS(蓝色)5.2工作原理元件区1.数字直接频率合成器的核心(DDS core)输出信号的频率由用户的可编程的频率调谐字(FTW)确定。