DSP第四章 DSP程序流程控制

7第四章 数字音频非编的操作流程

第四章数字音频工作站学习要点:1、掌握数字音频工作站工作流程;2、了解数字音频工作站的各个构成部分以及各部分的功能;目前我国的广播、电视、电影、影像制品的节目制作正逐步的从模拟技术向数字技术方面过渡,那么,数字音频节目的制作目前应该用哪种数字音频设备呢?——数字音频工作站第一节什么是数字音频工作站数字音频工作站的英文缩写为DAW-Digital Audio workstation,是一种很好的声音处理工具。

它是以计算机控制的硬磁盘为主要载体的非线性数字音频系统,由计算机中央处理器、数字音频处理器、软件功能模块、音源外设、存储器等部分所构成的一个工作系统。

它对音频信号加工处理成数字方式,来实现对信号的获取、记录、储存、重放。

它包含录放音、多轨合成、调音、均衡、不变调时间压扩、混响、延时、降噪等简单到复杂的声音剪辑的所有系统功能。

数字音频工作站使众多操作繁琐的音频制作过程集成在多媒体电脑上完成,与传统的数字音频制作相比,省去了大量周边辅助数字音频设备,省去了大量设备的连接、安装与调试,而且性能价格比高,操作也比较简单。

第二节数字音频工作站的主要功能数字音频工作话提供了录音棚制作所需的全部功能。

它实际上就是一台非线性数字编辑多声轨录音机,官集录音、放音、混合录音、多轨合成、波形显示、编辑对位对形等功能于一身,还可利用MIDI软件创作、修改音乐。

一、录音、放音与合成数字音频工作站的录音、放音、合成与普通制作多声轨节目一样,但不同的是录放音时既听到声音,同时还可看到DAW屏幕上描绘出的彩色信号波形,更直观、更有效,包括所有操作界面均可同屏显示,操作状态一目了然。

从屏幕上可见到精确到帧的声音波形,需要补录时,可根据显示器波形精确地选择人、出点。

如果需要对某一段声音进行多种形式的录音,可以在同一时河、同一轨上进行无损伤的、多层次的录音,所有被记录下的音频段被自动编号、存储保留,为后期制作挑选最佳的声音资料提供了极大的余地。

数字信号处理EXPIV型教学实验系统实验四常规实验exp4_常规

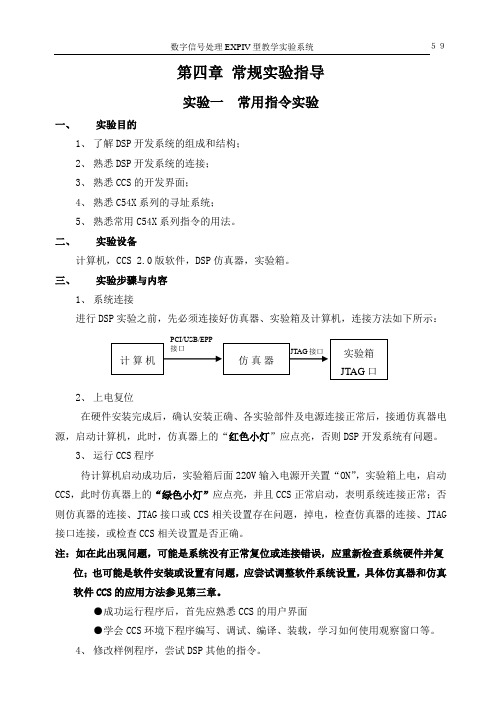

第四章常规实验指导实验一常用指令实验一、实验目的1、了解DSP开发系统的组成和结构;2、熟悉DSP开发系统的连接;3、熟悉CCS的开发界面;4、熟悉C54X系列的寻址系统;5、熟悉常用C54X系列指令的用法。

二、实验设备计算机,CCS 2.0版软件,DSP仿真器,实验箱。

三、实验步骤与内容1、系统连接进行DSP实验之前,先必须连接好仿真器、实验箱及计算机,连接方法如下所示:2、上电复位在硬件安装完成后,确认安装正确、各实验部件及电源连接正常后,接通仿真器电源,启动计算机,此时,仿真器上的“红色小灯”应点亮,否则DSP开发系统有问题。

3、运行CCS程序待计算机启动成功后,实验箱后面220V输入电源开关置“ON”,实验箱上电,启动CCS,此时仿真器上的“绿色小灯”应点亮,并且CCS正常启动,表明系统连接正常;否则仿真器的连接、JTAG接口或CCS相关设置存在问题,掉电,检查仿真器的连接、JTAG 接口连接,或检查CCS相关设置是否正确。

注:如在此出现问题,可能是系统没有正常复位或连接错误,应重新检查系统硬件并复位;也可能是软件安装或设置有问题,应尝试调整软件系统设置,具体仿真器和仿真软件CCS的应用方法参见第三章。

●成功运行程序后,首先应熟悉CCS的用户界面●学会CCS环境下程序编写、调试、编译、装载,学习如何使用观察窗口等。

4、修改样例程序,尝试DSP其他的指令。

注:实验系统连接及CCS相关设置是以后所有实验的基础,在以下实验中这部分内容将不再复述。

5、填写实验报告。

6、样例程序实验操作说明仿真口选择开关K9拨到右侧,即仿真器选择连接右边的CPU:CPU2;启动CCS 2.0,在Project Open菜单打开exp01_cpu2目录下面的工程文件“exp01.pjt”注意:实验程序所在的目录不能包含中文,目录不能过深,如果想重新编译程序,去掉所有文件的只读属性。

用下拉菜单中Project/Open,打开“exp01.pjt”,双击“Source”,可查看源程序在File Load Program菜单下加载exp01_cpu2\debug目录下的exp01.out文件:加载完毕,单击“Run”运行程序;实验结果:可见指示灯D1定频率闪烁;单击“Halt”暂停程序运行,则指示灯停止闪烁,如再单击“Run”,则指示灯D1又开始闪烁;注:指示灯D1在CPLD单元的右上方关闭所有窗口,本实验完毕。

DSP开发系统使用说明书

条件执行和单步执行使用户可以完全控制程序的执行。用鼠标或键入命令的方式设置或取消断点。存储器的分布与目标系统一致,以便调试器访问和定义。调试器可以执行从批处理文件来的命令,从而容易进入经常使用的命令序列。

该调试器的主要特性包括:

支持多操作

对于C2XX、C4X、C5X、C54X、C6X、C8X,C/汇编调试器并行处理的能力(多处理器debugger、断点、单步)。

说明:

根据上述的例子,共定义了5个段。

.text包含若干条32位字的目标代码;

.data包含6个字的目标代码;

vectors在.sect命令中定义的命名段;

.bss在存储器中预留了44个字节的空间;

newvars在.usect命令中定义的命名段,在存储器中占了8个字节的空间。

2.2软件开发工具简介

DSP的软件开发工具简介如下:

包含ANSI标准运行支持函数、编译器公用程序函数、C输入/输出函数。

十六进制转化公用程序(Hex Conversion Utility)

将COFF目标文件转化为TI-Tagged、ASCII-hex、Motorola-s等目标格式,从而可以将文件装载到可擦除程序存储器中。

绝对列表器(Ab4

ect“newvars”,4

*****************************************************

**在.text段放置其余程序代码**

*****************************************************

TMS320调试接口(C/Assembly source debugger)

TMS320调试接口为嵌入式的系统开发提供了新的功能和灵活性。他是软仿真、评估模块、硬仿真的标准接口。

dsp基本系统设计

04

同时,随着人工智能、物联网等技术的快速发展, DSP技术将与这些技术进行更紧密的结合,以实现更 高效、智能的数据处理和分析。

THANKS FOR WATCHING

感谢您的观看

算法实现与优化

总结词

DSP系统的核心是实现各种数字信号处理算法,因此算法实现与优化是DSP系统软件设计的关键环节 。

详细描述

在算法实现与优化方面,需要考虑算法的复杂度、运算量、存储需求等因素,并采用适当的优化技术 ,如循环展开、流水线设计、并行计算等,以提高DSP系统的性能。

程序结构与流程控制

总结词

存储器与I/O接口设计

存储器设计

根据DSP系统的需求,设 计适当的存储器容量和类 型,如SRAM、DRAM、 Flash等。

I/O接口设计

根据应用需求,设计适当 的I/O接口,如GPIO、SPI、 I2C、UART等。

考虑因素

在存储器和I/O接口设计时, 需要考虑容量、速度、功 耗以及与处理器的兼容性 等因素。

信号的频域分析

频域分析是将信号从 时域转换到频域进行 分析的方法。

频谱分析可以揭示信 号的频率成分、频率 范围和频率变化等特 性。

傅里叶变换是频域分 析的基础,可以将信 号表示为不同频率分 量的叠加。

04 DSP系统硬件设计

硬件平台选择

通用硬件平台

选择通用的DSP硬件平台,如TI 的TMS320系列或ADI的Blackfin 系列,这些平台具有成熟的开发 工具和丰富的应用案例。

05 DSP系统软件设计

软件开发环境选择

总结词

选择合适的软件开发环境是DSP系统设计的重要步骤,它影响着软件开发的效 率、可维护性和可扩展性。

基于dsp控制流程

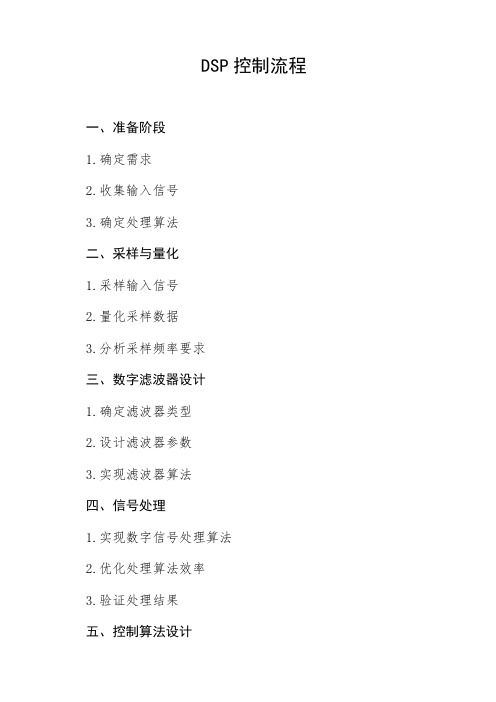

DSP控制流程

一、准备阶段

1.确定需求

2.收集输入信号

3.确定处理算法

二、采样与量化

1.采样输入信号

2.量化采样数据

3.分析采样频率要求

三、数字滤波器设计

1.确定滤波器类型

2.设计滤波器参数

3.实现滤波器算法

四、信号处理

1.实现数字信号处理算法

2.优化处理算法效率

3.验证处理结果

五、控制算法设计

1.选择控制算法类型

2.设计控制算法参数

3.仿真验证控制效果

六、实时性考虑

1.确定系统实时性要求

2.优化系统响应时间

3.测试系统实时性

七、数据输出

1.生成输出信号

2.数字信号转模拟信号

3.输出结果分析

八、系统集成与调试

1.硬件与软件集成

2.调试系统功能

3.确保系统正常运行。

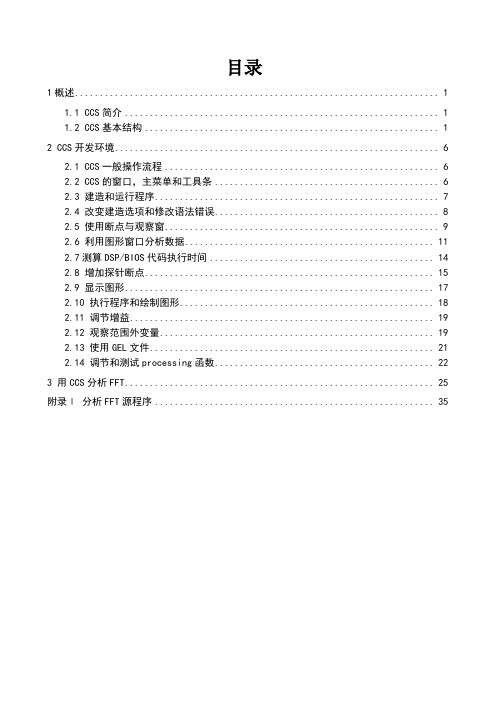

DSP开发环境和流程的简单例程

图1-3典型的软件开发流程图

1.2.3硬件仿真和实时数据交换

TI DSPs提供在片仿真支持,它使得CCS能够控制程序的执行,实时监视程序运行。增强型JTAG连接提供了对在片仿真的支持,它是一种可与任意DSP系统相连的低侵扰式的连接。仿真接口提供主机一侧的JTAG连接,如TI XSD510。为方便起见,评估板提供在板JTAG仿真接口。

图2-2装载程序

图2-3反汇编(Disassembly)窗口

现在可以开始运行我们的程序:在主菜单中单击“Debug”,选择“Go Main”,让程序从主函数开始执行。程序会停在main()处,并会有一个黄色的箭头标记当前要执行的C语言代码。如果希望同时看到C语言代码和对应编译生成的汇编代码,在主菜单中单击“View”,选择“Mixed Source/ASM”,此时会有一个绿色的箭头量标记当前要执行的汇编代码,如图2-4所示。

此时,在浅灰色显示的汇编指令上单击鼠标,然后按F1键,CCS会对该汇编指令进行搜索并弹出帮助窗进行解释。可以利用该功能来了解不熟悉的汇编指令。

在主菜单中单击“Debug”,选择“Run”,或单击工具条图标(Run),让程序全速执行。在主菜单中单击“Debug”,选择“Halt”,或单击工具条(Halt),让程序退出运行。

工程窗口用来组织用户的若干程序构成一个项目,用户可以从工程列表中选中需要编译和调试的特定程序。在源程序编译/调试窗口中用户既可以编译程序又可以设置断点、探针,调试程序。反汇编窗口可以帮助用户查看机器指令,查找错误。内存和寄存器显示窗口可以查看、编辑内存单元和寄存器。图形显示窗口可以根据用户需要直接或经过处理后显示数据。用户可以通过主菜单Windows条目来管理窗口。

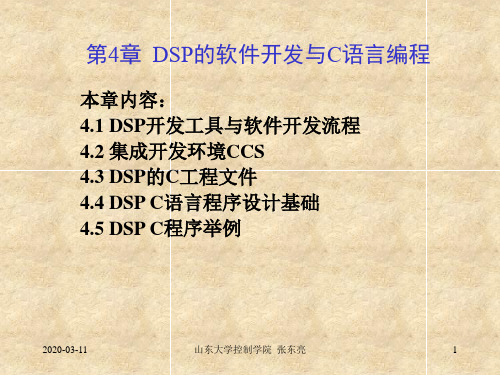

DSP软件开发与C语言编程

2020-03-11

山东大学控制学院 张东亮

5

2020-03-11

山东大学控制学院 张东亮

6

2. 软件开发流程

2020-03-11

山东大学控制学院 张东亮

软件开发流程框图

7

软件开发流程

1)编辑:生成源程序(*.asm, *.c)、头文件(*.h) 与命令文件(*.cmd)。 2)编译与汇编:生成目标文件(*.obj ,公共目标文件

• Allows you to halt in non-critical code for debug while time-critical interrupts continue to be serviced.

• Access memory and registers without stopping the processor.

开发系统 与评估板

2020-03-11

山东大学控制学院 张东亮

4

2812 EVM板的主要性能指标如下:

(1) TMS320F2812,运行速度150MIPS。 (2) 片内RAM 18K字。 (3) 扩展RAM 64K字。 (4) 片内16路12位A/D转换器, 最大采样速率12.5MSPS。 (5) 扩展的4路12位D/A转换器DAC7617。 (6) 两路UART串行接口,符合RS-232C标准。 (7) 16路PWM输出。 (8) CAN总线标准接口。 (9) 用户开关与指示灯。 (10) 片内128K字Flash存储器,带128位加密位。 (11) IEEE1149.1兼容的逻辑扫描电路即JTAG接口,用于仿真调试。 (12) +5V电源输入, 板上3.3V, 1.8V电源管理。

目标文件 .bss .data .text

DSP技术liuguoman_第四讲[1].C6000+DSP最小系统设计

![DSP技术liuguoman_第四讲[1].C6000+DSP最小系统设计](https://img.taocdn.com/s3/m/56f77423ed630b1c59eeb52e.png)

原理图软件 PCB软件 自动布线器 仿真软件

SI、EMI、POWER/GND、HEAT

DSP硬件系统组成 DSP芯片的选择 DSP最小系统设计 DSP板设计流程

3.电源—加电顺序需求

DSP的一些I/O管脚是双向的,方向由内核 控制。I/O电压一旦被加上以后,I/O管脚就立即 被驱动,如果此时还没加核电压,那么I/O的方 向可能就不确定是输入还是输出。如果是输出, 且这时与之相连的其它器件的管脚也处于输出状 态,那么就会造成时序的紊乱或者对器件本身造 成损伤。这种情况下,就需要核电压比I/O电压 先加载,至少是同时加载。

DSP板级设计流程

PowerLogic

HyperLynx

PowerPCB BlazeRouter SPECCTRA

HyperLynx

概念

方案 论证

原理图 设计

前仿真

PCB图 绘制

后仿真

制板

原型 调试 测试

方案论证

rst

SBSRAM 3.3v

1.8v 1.2v CE3 CE0,CE2 INT4~7

Date: Tuesday May 20, 2003 Time: 22:25:40

实物

EDA软件

Altium / PROTEL Mentor / PADS Mentor / Expedition Mentor / BoardStation Cadence / Allegro Cadence / OrCAD

4.时钟-输入

OSC

4.时钟-输出

SRAM SRAM C6000 244 SRAM C6000 CY2308 SRAM SRAM SRAM

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

程序流程:指的是指令的执行顺序。 C55x中影响指令执行顺序的主要有: 程序跳转(分支) 指令重复执行 条件执行 中断

程序调用

程序的流程控制主要与指令缓冲单元(I单元)和程序流程单元(P 单元)有关。

第四章 程序流程控制

P单元产生24位的程序地址,并放到PAB总线上。

1=255

举例: RPTCC #7, AC1 > #0 ADD #1,AC0 ;AC0=AC0+1

第四章 程序流程控制

以下指令不能用做单指令循环体: B ;跳转 IDLE ;空闲指令 RPTBLOCAL ;块重复 RESET;软件复位 MOV RPTC, TAx ;RPTC单指令重复计数器

TRAP ;软件陷阱 MOV dbl(Lmem), RETA

RPTBLOCAL和RPTB区别

RPTBLOCAL被定义为指令缓冲队列(IBQ)的本地循环,即直接 从IBQ中获取循环体指令,这样可以减少功率消耗,但是循环 体指令的字数不能超过56个字节。 当循环体指令超过56个字节时,使用RPTB块循环。

第四章 程序流程控制 支持两层块循环 一层循环(外循环):BRC0, RSA0, REA0; 二层循环(内循环): BRC1, RSA1, REA1,BRS1;

第四章 程序流程控制

vector: (4) 执行中断服务程序 rs b _c_int00 nop ISR包含中断返回指令,当中断返回时,自动恢复以前保存 nop nmi b __ret 在寄存器中的内容。 nop nop 3、中断矢量及其优先级 int0 b __ret CPU接受和响应中断请求后,产生一个中断矢量地址,地址 nop nop 指向相关中断服务程序的中断矢量。书中表4-2。 . 多个中断同时发生时,CPU按照事先定义的优先级进行处理。 . . 优先级为0的优先权最高,随着优先级数的逐步增加,优先 dmac5 b __ret 权逐步减小。 nop nop

第四章 程序流程控制

二、指令重复 指令重复:指重复执行一定次数的一条或者一段指令。包括无条 件单指令重复,有条件单指令重复,块重复三种形式。 1、无条件单指令重复:

(1) RPT #; 将下一条指令重复执行n+1次

(2) RPT CSR; CSR单重复寄存器,下一条指令重复CSR+1次 (3) RPTADD CSR, TAx;下一条指令重复CSR+1次后,TAx +CSR->CSR (4) RPTADD CSR, k4;下一条指令重复CSR+1次后,CSR+k4->CSR (5) RPTSUB CSR, k4;下一条指令重复CSR+1次后,CSR-k4->CSR

四、中 断

中断是为DSP具有对外界异步事件的处理能力而设置的。当 DSP的外界异步事件发生时,CPU暂停当前的工作去处理外界 异步事件,当处理完成后,再回到原来被中断的地方,继续执 行原来的工作。 1、中断 (1)由硬件或软件信号产生的,它使DSP暂停当前程序转而去执 行中断服务程序(ISR),从而可以实时的进行事件处理。 (2) TMS320C5509支持32个ISR,有的即可以用软件触发也可 以由硬件触发,有的只能由软件触发。 软件中断:由程序指令产生,如:INTR、TRAP、RESET 硬件中断:由设备的信号产生,可以是外部引脚信号(外部中 断),也可以是片内外设信号(内部中断)。

主机中断矢量指针(IVPH)

指向包含主机中断矢量的256字节的程序页。主机中断矢量序号 是16~23,这些矢量可以被映射到分配给DSP和主机共享的存储 空间。 若IVPD和IVPH内容相同,则32个中断矢量均位于相同的256字

节程序页中。

第四章 程序流程控制

DSP的硬件复位:使这两个指针都指向FFFFh,即指向 0xFFFF00的地址,软件复位对这两个指针没有影响。 一般在程序初始化时设定中断矢量指针的值,防止取非法指令 代码,在修改中断矢量指针(IVPD,IVPH)前应当确定:

RPTB ;块重复 CALL ;子程序调用

RPT ;单指令重复 INTR ;中断陷阱 XCC ;条件执行 RET ;从子程序返回

第四章 程序流程控制

3、块重复:同时重复多条指令。 块重复(块循环)的语法形式为: (1) RPTBLOCAL label (2) RPTB label

执行步骤:

(1) 重复执行次数由块重复计数器(BRC0或BRC1)定义。

内循环完成后跳到外循环执行。如果再次进入内循环, 则不需要初始化BRC1,块重复备份寄存器(BRS1) 自动保存内循环块的重复次数。 任何一个块循环内都可以嵌套单指令重复。所以 C55x可以支持三层指令循环。

第四章 程序流程控制

块重复举例

MOV #31,BRC0 ;对外循环块重复计数器BRC0赋值,重复32次。 MOV #127,BRC1 ;对内循环块重复计数器BRC1赋值,重复128次。 RPTB OuterLoop ;定义外循环块的起始地址。 MOV #0,AC0 …… RPTB InnerLoop ;定义内循环块的起始地址。 MAC *AR0,*CDP+,AC0 MOV *AR3+,T0 …… InnerLoop: ;内循环块的结束地址。 SUB #(127*2),AR0

第四章 程序流程控制

(3) 中断可分为可屏蔽中断和非屏蔽中断两类。 可屏蔽中断:用软件将其设置为禁止中断或允许中断。 非屏蔽中断:不能被禁止,一旦产生,CPU立即响应中断。 2、中断处理的四个步骤 (1) CPU接收中断请求,挂起当前程序; (2) 响应中断请求:可屏蔽中断须满足某些条件,非屏蔽中断立 即响应。 (3) 准备中断服务程序 CPU完成当前的指令执行,清除流水线中未译码的指令。 在数据堆栈和系统堆栈中保存相关寄存器的内容, 从中断矢量表中取出中断矢量,中断矢量指针(IVPD、IVPH) 指向中断服务程序。

中断标志寄存器(IFR)和中断使能寄存器(IER) 它们包含所有的可屏蔽中断的标志位和使能位。

IFR0和IER0寄存器

IFR1和IER1寄存器

第四章 程序流程控制

当CPU接收到一个可屏蔽中断请求时,CPU将IFR中的相应标 志位置1,表明此中断被挂起或等待CPU响应,因此可以通过读 IFR来识别挂起中断。 中断标识寄存器的修改 可以写入0来清除挂起中断 响应硬件中断请求能清除IFR中相应的标志位; RESET能清除所有IFR中的标志位。

(1) BCC 14, cond ;4比特长相对PC的无符号偏移

(2) BCC L8, cond ;8比特长相对PC的有符号偏移 (3) BCC L16, cond ;16比特长相对PC的有符号偏移 (4) BCC P24, cond ;24比特的绝对地址。

第四章 程序流程控制

在指令流水线的读(R)环节判断条件cond; cond条件可以是寄存器ACx,ARx,Tx与0值的比较,也可以 是测试位TCx以及进位标志CARRY的值。 若条件为真,就把l4、L8、L16、P24指定的程序地址装入PC中, 完成分支跳转。 跳转指令不能重复执行。 举例: 程序地址 004055 BCC branch, *AR0 != #0 004056 …… 00F05A branch: ….

(1) 禁止所有的可屏蔽中断(ST1_55): BSET INTM

(2) 要求每个硬件非屏蔽中断对新旧IVPD值分别有一个中断矢量

和一个中断服务程序。

第四章 程序流程控制

中断矢量地址的形成 CPU将16比特的中断矢量指针与5比特的中断矢量序号级联然后

左移三位形成中断矢量地址。

第四章 程序流程控制

第四章 程序流程控制

4、中断管理寄存器 C55x芯片有8个中断管理寄存器。 Interrupt Vector Pointers (IVPD, IVPH) Interrupt Flag Registers (IFR0, IFR1)

Interrupt Enable Registers (IER0, IER1)

成立与否,AR2都会被修改。 条件满足:即T0!=#0,执行ADD指令, AR2被修改 条件不满足:执行MOV指令,但在执行该指令前, AR2指针已被修改了。

第四章 程序流程控制

例2: XCC label,T0!=#0 ADD *AR2+, AC0 label: MOV *AR2,AC1 使用XCC指令时,从流水线的寻址(AD)到执行(X)阶段都是 有条件的。所以只有当条件满足时,AR2和AC0的值才能被修 改。本例中,条件不满足,所以AR2和AC0的值没有被修改。

假设AR0的值为3000,AR0的值不等于0 ,条件为真,跳转到 标号为branch处执行,这时PC=00F05A

第四章 程序流程控制

2、无条件跳转 不需要满足任何条件,直接将目标地址装入PC。 (1) B ACx ;把ACx的低24位的值装入到PC中 (2) B L7 ;7比特长相对PC的有符号偏移 (3) B L16 ;16比特长相对PC的有符号偏移 (4) B P24 ;24比特的绝对地址

第四章 程序流程控制

举例:RPTADD CSR, T1 MOV *AR0+, T0 ;重复 CSR + 1次后,T1的值加到CSR中。 执行流水线分为8个环节:F/,D, AD,AC1,AC2,R,X,W 2、有条件单重复指令 RPTCC k8,cond;当条件为真时,下一条指令重复K8+1次 每次重复在流水线的执行(X)阶段检查cond定义的条件,当 条件不满足时,停止单指令重复。最大重复执行次数为2^8-

Debug Interrupt Enable Registers (DBIER0, DBIER1)

中断矢量指针(IVPD,IVPH)

均为16比特的寄存器,指向程序空间的中断矢量(中断服务表IST 的基地址)。