简易频谱分析仪设计报告

DSP课程设计(课题二fft的频谱分析仪)报告

DSP课程设计报告课题:基于FFT的频谱分析仪设计班级:电子信息工程0901班小组成员:陈湛国200930410103谢海200930410124 指导老师:徐梅宣华南农业大学珠江学院信息工程系一、设计原理(1)实现输入数据的比特反转输入数据的比特反转实际上就是将输入数据进行位码倒置,以便在整个运算后的输出序列是一个自然序列。

在用汇编指令进行位码倒置时,使用位马导致寻址可以大大提高程序执行速度和使用存储器的效率。

在这种寻址方式下,AR0存放的整数N是FFT点的一半,一个辅助寄存器指向一个数据存放的单元。

当使用位码倒置寻址将AR0加到辅助寄存器时,地址将以位码倒置的方式产生。

(2)实现N点复数FFTN点复数FFT算法的实现可分为三个功能块,及第一级蝶形运算、第二级蝶形运算、第三级至log2N级蝶形运算。

在运算过程中,为了避免运算结果的溢出,可对每个蝶形的运算结果右移一位。

(3)功率谱的计算计算功率谱时只需将FFT变换好的数据,按照实部X R(k)和虚部X I(k)求它们的平方和,然后对平方和进行开平方运算。

(4)输出FFT结果二、操作步骤1、运行软件打开Setup CCStudio v3.3,在Family中选择C54XX,Platform中选择simulator,此时在My System中出现C54xx Rev.x CPU Cycle Accurate Simulator,点击,然后再点击“Save&Quit”,此时有窗口“Code Composer Studio Setup”出现,点击“Yes”,然后进入CCStudio:Parallel Debug Manager,在“Open”选项中选择“C54xx Rev.x CPU Cycle Accurate Simulator”,则进入设计的操作界面。

2、载入程序代码,编译并执行首先,点击“Project”,建立新文件;然后点击“File”,建立源文件,后缀名分别为“.C”、“.cmd”;其次,把编好的FFT程序放入“.C”文件中,命令文件也编入“.cmd”中;再次,加载文件“.C”及“.cmd”文件;接着点击“Project”中的“Rebuild Aall”,无错误出现,则继续操作;点击“File”中的“Load Program”,把后缀为“.out”的文件加载进来;然后点击“Run”,最后,点击“View”,“Graph”,进入“time/Frequency”,修改设置后,点击“ok”,则出现图像。

手提式频谱分析仪的设计研究的开题报告

手提式频谱分析仪的设计研究的开题报告一、选题背景频谱分析仪是一种广泛应用于科研、生产、检测等领域的测试设备。

目前市面上的大多数频谱分析仪都采用桌面型或机架式结构,不方便携带和移动使用。

但是在现场测试、采集以及故障排查等场景下,需要频谱分析仪具备便携性和快速响应的特点,因此需要设计一款手提式的频谱分析仪。

二、选题意义手提式频谱分析仪可以满足用户在现场测试和采集时的需求,且其便携性可以使其广泛用于各类行业。

这种频谱分析仪相较于桌面型或机架式结构的频谱分析仪,具有更小巧、轻便的特点,用户可以方便地移动、携带甚至操作,且其响应速度也能跟上生产、故障排查等现场应用的需求。

三、研究内容本文将主要研究手提式频谱分析仪的设计和实现。

具体包括:1.对现有的桌面型和机架式频谱分析仪进行研究和分析,确定手提式频谱分析仪的要求和设计方案。

2.针对手提式频谱分析仪特点,结合用户的使用场景和需求,分析选型和设计硬件电路,以确保其具有足够的性能和稳定性。

3.设计合适的软件系统,包括数据处理、分析和可视化。

4.实现手提式频谱分析仪的原型,进行性能测试和优化。

五、预期成果完成手提式频谱分析仪的设计和实现,具有以下特点:1.小巧、轻便、易于携带和操作。

2.具有高容量、高速度、高精度等优势,能够满足用户对频谱分析仪的性能要求。

3.软件系统具有较好的用户体验和易用性,并提供多种数据处理和可视化方式。

4.有较高的经济价值和社会意义。

六、研究方法本文采用文献综述、理论分析、设计和实验等多种方法,具体包括:1.收集和分析相关的文献和信息,了解频谱分析仪的基本原理、结构和应用情况,确定手提式频谱分析仪的要求和设计方案。

2.进行硬件电路方案设计,选型和测试。

采用模块化设计思路,压缩整体体积的同时,保证硬件系统的高性能。

3.设计软件系统,包括图形用户界面设计,数据采集及处理等。

4.通过对原型机性能的测试以及实验数据的分析,最终得出一个具备优异性能和可行性的手提式频谱分析仪原型。

于基dsp的简易频谱分析仪设计 --本科毕业设计

基于DSP的简易频谱分析仪设计摘要我们对一个信号的认识只在时间域是远远不够的,所以还要在频域去认识和分析它。

在电子测量中,测量网络阻抗特性以及传输特性是经常遇到的问题问题,其中,幅频特性、增益和衰减特性、相频特性等是属于传输特性内的。

它很大程度方便了调整,校准被测网络及排除故障。

本此设计制作了一个简易频谱分析仪从而可以更直观的看到信号的特性。

为了实现这一目标,我们需要利用快速傅里叶变换(FFT)来实现对信号的频谱分析。

由于DSP可以处理比较复杂的算法本次设计采用FFT算法通过DSP分析显示输入波形的频率值。

关键词:频谱分析DSP FFT 显示频率The Simple Spectrum Analyzer Design Based on DSP AbstractWe can’t know a signal only in the time domain .It is far from enough, so we also recognize and analyze it in the frequency domain. In the electronic measurement, impedance and transmission characteristics of the network are often encountered in the measurement problems; Transmission characteristics include the gain characteristics, attenuation characteristics, amplitude-frequency characteristic and phase frequency characteristics. It provides a great convenience for the adjustment of the network under test, calibration and troubleshooting.We design a simple spectrum analyzer to see the characteristics of the signal more intuitively. In order to achieve this goal, we need to use the fast Fourier transform ,that is FFT which make spectrum analysis of the signal. Since the DSP can solve the more complex algorithms than others. Hence, we designed a simple spectrum analyzer using the FFT algorithm by DSP to show the frequency of the input waveform.Key word s: Spectrum Analyzer ; DSP; FFT ; Frequency Display目录第1章概述 (1)1.1 引言 (1)1.2 定点DSP的数据格式 (2)1.3 TMS320F2812 DSP介绍 (2)1.3.1 TMS320F2812概述 (2)1.3.2 TMS320F2812芯片结构及性能描述 (3)第2章总体设计思路 (4)2.1 系统指标 (4)2.2 系统方案 (4)2.2.1 信号发生器模块 (5)2.2.2 DAC转换模块 (5)2.2.3 陷波网络模块 (6)2.2.4 信号调理模块 (6)2.2.5 AD采集模块 (6)2.2.6 FFT计算处理模块 (7)第3章具体设计 (7)3.1 工程建立 (7)3.2 正弦波发生模块 (9)3.2.1 定时器模块 (10)3.2.2 中断模块 (12)3.2.3 GPIO模块 (14)3.3 DAC转换模块 (15)3.4 陷波网络模块 (16)3.5 信号调理电路模块 (18)3.6 AD采集模块 (19)3.6.1 事件管理器定时设置 (20)3.6.2 ADC设置模块 (22)3.7FFT模块 .............................................................................. .. (24)第4章实验结果 (31)第5章总结与展望 (37)5.1 总结 (37)5.2 展望 (38)参考文献 (38)致谢 (39)第1章概述1.1 引言DSP的2种理解:广义理解:digital signal processing——数字信号处理狭义理解:digital signal processor——数字信号处理器数字信号处理的概念是利用计算机或者专用的处理设备,对连续的数字信号进行各种数学运算,最终得到我们想要的分析结果。

专业综合课程设计报告--数字频谱分析仪

专业综合课程设计报告课设题目:数字频谱分析仪学院:信息与电气工程学院专业:电子信息工程班级:姓名:学号:指导教师:一、设计任务1.1Matlab实现FFT和滤波器两种方式频谱分析方法;用Matlab GUI设计频谱分析仪界面,界面上包括类似与实际频谱分析仪的参数设置和显示功能,例如:频谱分析范围、频谱物理分辨率、频谱视觉分辨力等参数的设置,信号频谱的显示等;界面上还应包括对这两种频谱分析方法的切换键;1.2要求设计的频谱分析仪具有对窄带信号分析的能力;1.3仿真产生一个信号,其中包含如下频率的正弦信号:1MHz,1.5MHz,2.1MHz,2.2MHz;各频率成分的正弦信号幅度分别为:1V,3V,2V,4V。

对其进行分析;要求的物理频谱分辨力为0.1MHz1.4个窄带信号,载频10GHz,信号带宽为10MHz的线性调频信号,使用频谱分析仪分析其频谱;二、方案设计MATLAB是Mathworks公司推出的数学软件,它将数值分析、矩阵计算、信号处理和图形显示结合在一起,为众多学科领域提供了一种简洁、高效的编程工具。

它提供的GUIDE工具为可视化编程工具,使得软件的界面设计像VB一样方便。

故本文采用MATLAB作为编程语言实现声音信号频谱分析仪,以下所讲的都是在MATLAB 2013b环境中。

为了实现预期的功能,设计界面如图所示:图1 图形用户界面界面分为三部分组成,左面为输出区,显示信号时域、频域波形,右边分为信号输入区和操作区。

信号输入分为三种输入方式,第一种为信号发生器输入,如图,信号发生器可以产生正弦、锯齿以及窄带信号波形及其叠加信号。

默认采样频率为2MHz,采样时间为6us。

单击start按键可以显示由信号发生器设置的波形时域或频谱图。

第二种为wav文件输入,可以对wav文件信号进行分析。

单击showWav按键,可以显示wav信号的时域以及频域处理后的波形。

第三种为声卡采集,通过计算机声卡采集声音信息进行频谱分析。

简易频谱分析仪

简易频谱分析仪摘要:本系统采用TI 公司的16位单片机MSP430F149作为控制核心,采用外差原理设计并实现频谱分析仪,基于DDS 技术得到10 kHz 步进的本机振荡器,采用AD835进行混频,通过低通滤波器取出差频信号分量,再配合放大、检波电路得到各个频点的信号有效值。

单片机MSP430F149与扫频同步输出锯齿波扫描电压,利用示波器X-Y 方式显示信号频谱分布。

测量频率范围覆盖1MHz-30MHz ,可设定中心频率和带宽,还可以识别调幅,调频和等幅波信号。

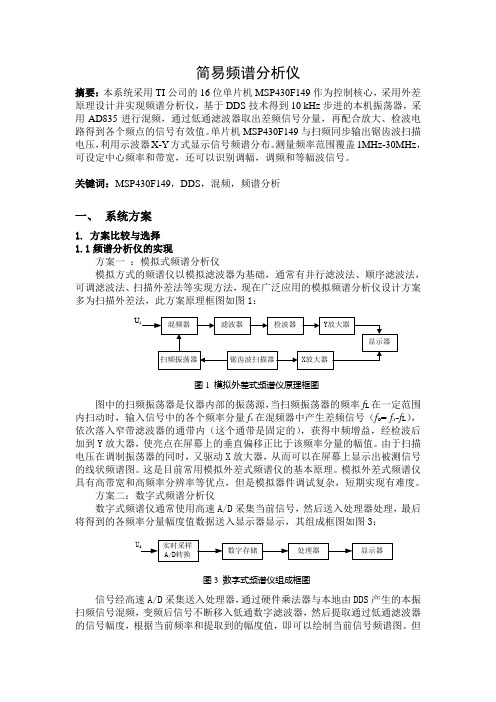

关键词:MSP430F149,DDS ,混频,频谱分析一、 系统方案1. 方案比较与选择 1.1频谱分析仪的实现方案一 :模拟式频谱分析仪模拟方式的频谱仪以模拟滤波器为基础,通常有并行滤波法、顺序滤波法,可调滤波法、扫描外差法等实现方法,现在广泛应用的模拟频谱分析仪设计方案多为扫描外差法,此方案原理框图如图1:U 图1 模拟外差式频谱仪原理框图图中的扫频振荡器是仪器内部的振荡源,当扫频振荡器的频率f L 在一定范围内扫动时,输入信号中的各个频率分量f x 在混频器中产生差频信号(f o = f x -f L ),依次落入窄带滤波器的通带内(这个通带是固定的),获得中频增益,经检波后加到Y 放大器,使亮点在屏幕上的垂直偏移正比于该频率分量的幅值。

由于扫描电压在调制振荡器的同时,又驱动X 放大器,从而可以在屏幕上显示出被测信号的线状频谱图。

这是目前常用模拟外差式频谱仪的基本原理。

模拟外差式频谱仪具有高带宽和高频率分辨率等优点,但是模拟器件调试复杂,短期实现有难度。

方案二:数字式频谱分析仪数字式频谱仪通常使用高速A/D 采集当前信号,然后送入处理器处理,最后将得到的各频率分量幅度值数据送入显示器显示,其组成框图如图3:图3 数字式频谱仪组成框图信号经高速A/D 采集送入处理器,通过硬件乘法器与本地由DDS 产生的本振扫频信号混频,变频后信号不断移入低通数字滤波器,然后提取通过低通滤波器的信号幅度,根据当前频率和提取到的幅度值,即可以绘制当前信号频谱图。

通信系统课程设计 数字频谱分析仪 设计报告

手持式数字频谱分析仪设计报告2011级通信一班孙静平、孙鸿儒、孙冬航、杨泰1 设计目的频谱分析仪是微电子测量领域中最基础、最重要的测量仪器之一,是从事各种电子产品研发、生产、检验的重要工具,它能够帮助电子工程师完成频谱观测、功率测量以及复杂信号解调分析等工作。

高分辨率、宽频带数字频谱分析的方法和实现一直是该领域的研究热点。

基于快速傅里叶变换(FFT)的现代频谱分析仪,通过傅里叶运算将被测信号分解成分立的频率分量,达到与传统频谱分析仪同样的结果。

这种新型的频谱分析仪采用数字方法直接由模拟/数字转换器(ADC)对输入信号取样,再经FFT处理后获得频谱分布图。

这是一种较为先进的频谱分析仪架构。

我们本次课程设计计划设计一款便携式的频谱分析仪,采用FPGA进行信号频谱的分析,可以作为较高精度且便于携带的频谱分析工具。

2 设计思路我们的设计思路是采用Xilinx公司的Spartan-6型FPGA 作为运算主芯片,对输入信号进行信号的采集、模-数转换并输入FPGA,进行数字信号FFT算法处理。

系统设计需要遵循抽样定理,在时域内截取一段适当长度信号,对这一段信号抽样进行AD转换,按照快速傅里叶算法具体的步骤求取信号的频谱,并通过VGA接口将频谱显示在电脑显示屏上,对频谱进行观测。

在进行快速傅里叶变换FFT时,我们有两种方案可以选择:一是直接采用数值运算的方式,利用FFT的表达式直接对被分析的时域信号进行运算,得出其频谱;二是可以利用Xilinx 公司为其FPGA产品提供的用于完成FFT功能的IP核,进行DFT得到频谱。

基于设计完整性和缩短设计周期的考虑,目前我们倾向于采取第二种方式。

由于在频谱分析的前端需要进行混频,我们预计采用AD9850芯片构成DDS芯片作为本地载波产生器,与输入信号进行乘法运算,达到混频的效果。

3 模块组成根据我们的设计,本系统由四个模块组成,分别为信号放大采集模块、信号处理模块、微处理器软核及人机交互界面。

频谱仪实验报告

频谱仪实验报告频谱仪实验报告引言频谱仪是一种用于测量和分析信号频谱的仪器。

它可以将复杂的信号分解成不同频率的成分,并以图形化的方式展示出来。

频谱仪在通信、无线电、音频等领域有着广泛的应用。

本实验旨在通过使用频谱仪,了解其原理和使用方法,并通过实际操作来验证其功能和精度。

实验目的1. 了解频谱仪的基本原理和工作方式;2. 掌握频谱仪的使用方法;3. 验证频谱仪的测量精度和稳定性。

实验器材和方法器材:频谱仪、信号发生器、电缆等;方法:根据实验步骤进行操作,记录实验数据并进行分析。

实验步骤1. 连接信号发生器和频谱仪:将信号发生器的输出端与频谱仪的输入端通过电缆连接起来。

2. 设置信号发生器:根据实验要求,设置信号发生器的频率、幅度等参数。

3. 打开频谱仪:按下频谱仪的开关,等待其启动。

4. 调整频谱仪参数:根据实验要求,调整频谱仪的参考电平、分辨率带宽等参数。

5. 观察频谱仪显示:通过频谱仪的显示屏,观察信号的频谱分布情况。

6. 记录实验数据:记录频谱仪显示的数据,包括频率、幅度等信息。

7. 分析实验结果:根据实验数据,分析信号的频谱特征和分布规律。

实验结果与分析在实验中,我们选择了一个简单的正弦信号作为输入信号,通过信号发生器将其输入到频谱仪中进行分析。

通过观察频谱仪的显示屏,我们可以清晰地看到信号的频谱分布情况。

实验数据显示,输入信号的频率为1kHz,幅度为2V。

频谱仪显示了信号的频谱特征,其中包括主频率分量和谐波分量。

主频率分量位于1kHz处,幅度为2V,而谐波分量则以倍频的形式出现在主频率的整数倍处。

通过对实验结果的分析,我们可以得出以下结论:1. 频谱仪能够准确地显示信号的频谱分布情况,包括主频率和谐波分量。

2. 频谱仪的测量精度较高,能够准确地测量信号的频率和幅度。

3. 频谱仪的稳定性较好,能够在长时间的实验过程中保持较高的测量精度。

实验总结通过本次实验,我们深入了解了频谱仪的原理和使用方法,并通过实际操作验证了其功能和精度。

简易频谱分析仪的设计

摘要频谱分析仪的基本功能是测量信号的幅度/频率响应,可以完成诸如频谱成分分析、失真测量、调制信号谱分析、信号衰减测量、电子组件增益测量等。

其基本工作原理是,扫频本振的频率随锯齿波发生器的输出在一定范围内扫描,使不同频率的输入信号与本振混频后,依次落入分辨率带宽滤波器通带内,进一步放大、检波后加到Y放大器,亮点在屏幕上的垂直偏移正比于该频率分量的幅值。

由于扫描电压在调制振荡器的同时,又驱动X放大器,从而可以在屏幕上显示出被子测信号的频谱。

本系统是根据外差原理设计并实现的频谱分析仪。

利用DDS芯片生成10KHZ步进的本机振荡器,AD835做混频器实现频率的合成,通过滤波器取出各个频点(相隔10KHZ)的值,再配合放大,检波电路收集采样值,经单片机SPCE061A处理,最后送给示波器显示频谱。

测量频率范围覆盖1—30MHZ,该系统也可以根据用户的需要设定显示频谱的中心频率和带宽,还可以识别调幅,调频和等幅波信号。

关键词频谱分析,混频,滤波,外差原理AbstractSpectrum analyzer to measure the signal is the basic function of the amplitude/frequency response can be finished such as spectrum composition analysis, distortion measuring, modulation signal spectrum analysis, signal attenuation measure, electronic component gain measurements. Basic working principle is, sweep frequency this the vibration of the frequency with the output of sawtooth wave generator in a certain range of different frequency scanning, make the input signal and the resonance frequency mixing, ordinal fall within bandpass filter bandwidth resolution, further amplification, after detection of amplifier, highlights added to Y in screen is proportional to the vertical migration of the amplitude frequency components. Due to scan voltage in modulation oscillator, and meanwhile, thus can drive X amplifier is shown on the screen in the spectrum of the measured signal quilt.This paper adopts heterodyne principle design and realize the spectrum analyzer. Use 10KHZ DDS chip generation step of this machine oscillators, AD835 do mixers, through the filter remove each frequency (10KHZ) value apart, coupled with amplifier, detection circuit to collect samples values of sunplus SPCE061A processing by MCU, finally send oscilloscope display spectrum. Measure frequency range covers 1-30MHZ according to user need to set the display spectrum of center frequency and bandwidth, still can identify am, FM and amplitude wave signal.KEY WORDS Spectral analysis,mixing,smoothing,heterodyne principle目录摘要 (I)Abstract (II)1 绪论............................................................................................................................... - 1 -1.1 频谱分析仪的简介............................................................................................... - 1 -1.2 总体设计方案比较............................................................................................... - 2 -1.3 底层电路方案比较与选择................................................................................... - 2 -1.3.1本机振荡电路.............................................................................................. - 2 -1.3.2 混频电路..................................................................................................... - 3 -1.3.3 滤波电路..................................................................................................... - 3 -1.3.4 检波电路..................................................................................................... - 3 -1.3.5 扫频发生器电路......................................................................................... - 4 -1.4 本课题研究的意义............................................................................................... - 4 -1.5 本课题设计思路................................................................................................... - 4 -2 频谱分析仪的硬件设计................................................................................................. - 6 -2.1 频谱分析仪的整体结构....................................................................................... - 6 -2.2 频谱分析仪的各模块电路设计........................................................................... - 7 -2.2.1 本机振荡器模块......................................................................................... - 7 -2.2.2 混频器模块................................................................................................. - 9 -2.2.3 放大器模块................................................................................................. - 9 -2.2.4 滤波器模块............................................................................................... - 10 -2.2.5 检波器模块............................................................................................... - 12 -2.2.6 扫频发生器模块....................................................................................... - 13 -2.2.7 电源保护模块........................................................................................... - 16 -3 软件设计....................................................................................................................... - 18 -3.1 软件设计要求..................................................................................................... - 18 -3.2 主程序的软件设计............................................................................................. - 19 -4 系统调试与指标测试................................................................................................... - 20 -4.1 硬件调试............................................................................................................. - 20 -4.2 软件调试............................................................................................................. - 20 -4.3 软硬联合调试..................................................................................................... - 20 -4.4 指标测试............................................................................................................. - 20 -4.4.1 仪器测试................................................................................................... - 20 -4.4.2 指标测试................................................................................................... - 20 -结论................................................................................................................................. - 23 -致谢................................................................................................................................. - 24 -参考文献........................................................................................................................... - 25 -附录................................................................................................................................. - 26 -1 绪论1.1 频谱分析仪的简介频谱分析仪是对无线电信号进行测量的必备手段,是从事电子产品研发、生产、检验的常用工具,在各种振动、噪声、电声、发动机、建筑、生物、医学等领域也起着重要作用。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

简易频谱分析仪

摘要:本简易频谱分析仪以单片机为核心,采用外差原理设计并实现频谱分析仪:利用DDS芯片生成10KHz步进的本机振荡器,AD835做集成混频器,通过开关电容滤波器取出各个频点(相隔10KHz)的值,再配合放大,检波电路收集采样值,经单片机处理,最后送示波器显示频谱。

测量频率范围覆盖1MHz-30MHz,可根据用户需要设定显示频谱的中心频率和带宽。

关键词:单片机;DDS;混频器

一、系统方案设计

1.方案论证与选择

(1)本机振荡器

方案一:采用LC正弦波振荡器与变容二极管产生本振频率,通过改变变容二极管两端电压,使振荡电路输出频率发生改变。

这是传统的振荡器电路形式,组成电路繁琐而且不易实现频率线性步进,而且要实现30M的频率变化范围难以实现。

方案二:采用FPGA实现。

将正弦波信号的一个周期的离散样点的幅度数值量存于RAM中,以一定的地址间隔读出,经DA转换器转换输出,再经低通滤波滤除D/A带来的高次谐波,即可获得所需要的波形。

但采用FPGA产生正弦波,通过改变地址步进间隔即可实现不同频率输出,但要以较小失真度产生30M正弦信号,比较困难

方案三:采用AD9850 DDS集成芯片来产生正弦波。

芯片内部的DDS核与高速、高性能的DAC和比较器组合,构成了一个数字可编程的频率合成器和时钟信号发生器。

外接一个精密的时钟源,AD9850可产生一个非常纯净的、频率和相位幅度可编程的正弦波信号输出。

采用DDS电路只需少量外围元件就能构成一个完整的信号源,而且控制方便。

综上所述,我们选择方案三。

(2)混频电路

方案一:选用MC3362搭建混频电路。

MC3362是MOTOROLA公司生产的单片窄带载频信号从MC3363的2脚输入,进行第一级混频后将差频为10.7MHz的第一中频信号从23脚输出,经中频为10.7M的陶瓷滤波器选频后再由21脚送到内部的第二混频级,将差频为0.455MHz的第二中频信号从7脚输出,经455kHz 陶瓷滤波器选频,再经9脚送入MC3363的限幅放大器进行高增益放大。

该方案只需一块集成芯片即可实现混频和中频输出,但其外围电路过于复杂,对输出噪声的抑制能力也较差。

方案二:采用AD835乘法器专用芯片。

将本振信号和输入信号相乘得到二者频率的和差信号,达到混频的效果。

AD835对小信号的乘法精度较高,不易产生输出新的频率分量,有250M 的混频带宽,低噪声系数,简单的传输函数,只需要极少的外围元件。

综上所述,我们选择方案二来完成混频输出。

2.系统方案描述

本简易频谱分析仪由混频器、滤波器、有效值检波器、本机振荡器、扫描发生器、D/A 转换器、信号处理电路、显示电路、示波器组成。

其系统原理框图如图1所示。

混频器

滤波器

AD637有效值检波器

示波器

信号处理

电路

显示电路

本机振荡器

扫频发生器

D/A 转换器

X

Y

f x

f L -f x

f L

图1 系统原理框图

二、理论分析与计算

1.高中频原理

所谓高中频原理就是在混频中把频谱往上搬移,使中频信号高于要分析信号的频谱宽度,这样混频就不会出现频谱混乱,然后在用多级混频将频谱往下搬移至较低的频率,以便降低滤波器带宽和提高检波精度。

混频器把信号x1(t)和本振x2(t)相乘得到:

11()c o s (11)t A t x ω

θ=

+ (1) 2

2

()cos(22)t A t x ωθ=+ (2)

1212121212212()()()cos[()]/2cos[()(1)]y t t t A A t A A t x x ωωθθωωθθ=⨯=++++-+-

(3)

有(3)式可知道混频后输出信号的频率成分是f2+f1和f2-f1,我们采用的下变频方式会将f2-f1取出,如果该中频在信号频带范围之内的时候,中频信号将含有f2+f1信号功率成分,形成镜像干扰,影响谱仪的分析精度,若是谱仪的中频高

于信号的最高频率,则不会产生镜像干扰。

所以我们把中频设置在30几M 以抗镜像干扰。

但高的中频也带来了一些问题:滤波器的截止频率难以做窄,检波难以实现等。

于是我们选择了多次变频的方式,将中频从30多M 分两次下变频到455k,这样就可以利用455k 的各种带宽的陶瓷滤波器来进行滤波。

当要实现倍频时,我们将同一路信号进行乘方:

22()cos()cos()cos(22)/2/2y t A t A t A wt A ωθωθθ=+⨯+=++ (4) 通过一个高通滤波或者隔直电容之后的输出信号就是原输入信号频率的两倍,幅度通过放大器调整。

三、硬件电路设计

1.混频电路

采用AD835乘法器专用芯片,所构成的乘法器原理图如图2所示。

AD835但是一个电压输出四象限乘法器电路,能完成W=XY+Z 功能,缩放比例系数U 可利用在引脚端W 和Z 之间的电阻分压进行调节。

乘法器的输出信号幅度可以随信号频率的升高略有增加,很好的弥补了DDS 输出信号的幅度随频率的增加而小幅度降低的缺陷。

图2 AD835构成的乘法电路

2.低通滤波电路

本设计要求频谱分辨率为10kHz,所以每个间隔点为10kHz ,以此频点作为中心,左右各5kHz 范围内为有效值,所以滤波器需要5kHz 的带宽。

我们采用了低通滤波器,原理图如图3所示。

图3 低通滤波器

3.有效值检波器

为了提高检波精度,我们采用了AD637作为转换芯片构成的有效值检波器。

AD637是一块高精度单片TRMS/DC转换器,可以计算各种复杂波形的真有效值。

采用了峰值系数补偿,在测量峰值系数高达10的信号时附加误差仅为1% 。

频带宽度在2V输入时可达8MHz。

由于AD637芯片可以对输入的正弦信号峰值直接计算并输出其有效值,因此可以采用该芯片实现信号的峰值检测。

其原理图如图4所示。

图4 有效值检波电路图

四、软件电路设计

在软件控制上,由于方案要求产生的10KHz频率步进增加,所以对AD9850频率调制字改变也应是快速的。

AD9850调制字(Tuning Words)的装入采用异步串行接口UART,同时兼顾到单片机I/O口的分配和对调制字装入速度的要求,

为了加快扫频和扫描速度,将系统时钟改成最大值49MHz,以加快扫频和扫描速度。

另外,由于硬件采集系统无法达到全频段的稳定性,在收集频谱样值后我们通过软件对其进行一定的校准处理:根据固定输入信号的幅值,对全频段扫描结果并记录比较,设计校准曲线,来达到良好的稳定性,弥补硬件频率失真带来的误差,提高频谱测量仪的精度。

软件还对数据进行分析,根据频谱特性判别是AM、FM或单频波,计算调制深度或调频系数。

主程序流程图如图5所示。

系统初始化

开始

键盘扫描

是否有键按下

点频预置

扫频

全范围

扫频

N

Y

key12key13key14其他

图5 主程序流程图

五、数据测试与分析

1.测试仪器与环境

示波器:Tektionix TDS1001双通道数字示波器 100MHz

信号发生器:DDS函数信号发生器 30MHz

直流电源:电源电压220V市电,加到自制线性稳压电源上。

有±5V、±12V 和±15V可选。

测试环境:室温25℃

2.数据记录与分析

(1)频率范围测试

测试条件为输入信号有效值20mV,数据记录如表1所示。

表1 频率范围测试

次数输入频率 fi

/MHz

示波器显示电

压 /V

测得输入信号有

效值 /mV

1 10 4.

2 21

2 12 4.2 21

3 1

4 4.0 20

4 16 4.0 20

5 18 3.8 19

6 20 3.8 19

7 22 4.0 20

8 24 3.8 19

9 26 4.0 20

10 30 4.0 20

结果:最大误差2mV

(2)幅度精度测试

测量结果如表2所示。

表2 幅度精度测试

输入幅度

有效值

Fo=1MHz Fo=10MHz Fo=20MHz Fo=30MHz 15mV 3.2V/16mV 3V /15mV 3.2V/16mV 2.6V/13mV 20mV 4.1V/20.5mV 4V/20mV 4V/20mV 3.8V/19mV 25mV 4.6V/23mV 4.9V/24.5mV 5V/25mV 4.6V/23mV 结果:在测量范围内,幅度精度较高,误差在2mV以内。

六、结论。