Verilog HDL 课程设计报告 四人抢答器电路设计 河海大学

四人抢答器设计报告

四人抢答器设计报告一、设计任务及要求1、设计用于竞赛的四人抢答器(1)有多路抢答器,台数为四;(2)具有抢答开始后20秒倒计时,20秒倒计时后无人抢答显示超时,并报警;(3)能显示超前抢答台号并显示犯规报警;2、系统复位后进入抢答状态,当有一路抢答键按下时,该路抢答信号将其余各路抢答封锁,同时铃声响起,直至该路按键放松,显示牌显示该路抢答台号;3、用VHDL语言设计符合上述功能要求的四人抢答器,并用层次设计方法设计该电路;4、完成电路全部设计后,通过系统实验箱下载验证设计课题的正确性。

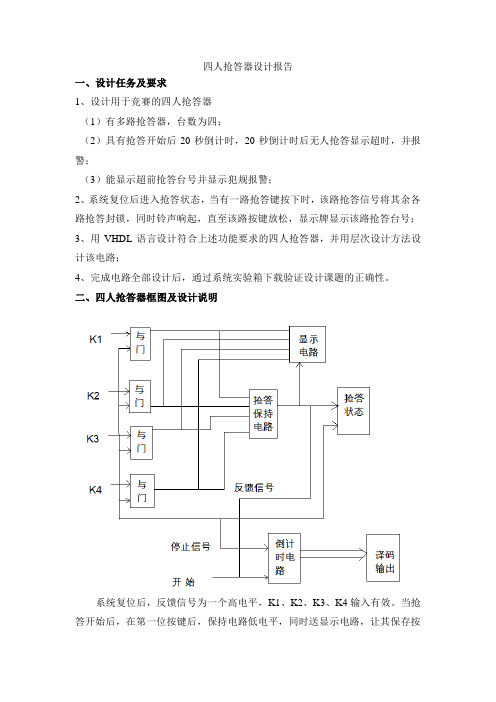

二、四人抢答器框图及设计说明系统复位后,反馈信号为一个高电平,K1、K2、K3、K4输入有效。

当抢答开始后,在第一位按键后,保持电路低电平,同时送显示电路,让其保存按键的台号并输出,同时反馈给抢答台,使所有抢答台输入无效,计时电路停止;当在规定的时间内无人抢答时,倒计时电路输出超时信号;当主持人开始说话未说完有人抢先按键时,显示犯规信号。

当选手回答正确时加分,回答错误时减分。

由主持人控制加减分数。

三、设计思路:根据设计框图和设计要求,本次实验可以采用模块化设计方法来实现智力竞赛四人抢答器。

将抢答器划分为抢答鉴别保持模块,倒计时模块,记分模块和判断显示模块。

再利用元件例化语句将这四个模块组成总的抢答器的设计电路。

选用模式五进行程序的下载。

四、VHDL语言设计与分析1、鉴别模块library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity jianbie isport(nu1,nu2,nu3,nu4:in std_logic;clk,en,rst:in std_logic;warn:out std_logic;back:buffer std_logic;s:out std_logic_vector(3 downto 0));end jianbie;architecture jianbiebeh of jianbie issignal num,warnd:std_logic;signal cnt:std_logic_vector(2 downto 0);beginnum<=nu1 or nu2 or nu3 or nu4;p1:process(rst, nu1,nu2,nu3,nu4,back) --判断抢答信号beginif rst='1' then back<='1';s<="0000";elsif back='1' thenif nu1='1' then s<="0001";back<='0'; --一号台抢答,输出S为1 elsif nu2='1' then s<="0010";back<='0'; --二号台抢答,输出S为2elsif nu3='1' then s<="0011";back<='0'; --三号台抢答,输出S为3 elsif nu4='1' then s<="0100";back<='0'; --四号台抢答,输出S为4 else back<='1'; s<="0000"; --无人抢答,输出S为0end if ;end if;end process p1;p2:process(clk,en,back,rst,cnt)beginif rst='1' then cnt<="000";warnd<='0';elsif clk'event and clk='1' thenif en='0' and back='0' thenif cnt<"111" then warnd<=not warnd; cnt<=cnt+1;else warnd<='0';end if; end if;end if;end process p2;warn<=warnd;end jianbiebeh;鉴别保持模块由两个进程组成,进程一主要用于鉴别强大信号,进程二用于鉴别是否为超前抢答,若是超前抢答,则输出报警信号。

数字电子技术实验报告范文-基于FGPA的4位智能抢答器(verilogHDL)

数字电子技术实验报告范文-基于FGPA的4位智能抢答器(verilogHDL)基于FPGA的4位智能抢答器一、设计任务要求基于EDA/SOPC系统开发平台,运用QuartuⅡ可编程逻辑器件开发软件,设计一个4位智能抢答器,在开发箱上,本系统使用频率为1000赫兹的时钟脉冲。

要求如下:2、系统上电和按下“复位”按键后4位数码管显示“0000”,此时只有“开始”按键有效,其他按键不起作用;4、抢答的有效时间为10秒,如果定时抢答的时间已到而没有选手抢答,本次抢答无效,封锁输入电路,禁止抢答,数码管左边显示“10”,右边显示“00”;此状态一直保持到主持人将系统复位为止;二、设计步骤本次设计主要采用VerilogHDL语言,总体编程思路采用模块化设计方式,主要分为3个模块,一个主控制及按键输入模块,一个计时显示模块,一个抢答组号显示模块,分别对这3个子模块进行独立编程设计,编译仿真通过并生成元件,在顶层使用原理图或者VerilogHDL语言的方式将3个模块连接起来三、模块设计思路对于这个任务来说,计时显示模块和抢答组号显示模块的模块并不复杂,复杂的模块是主控制及按键输入模块,所以我决定再将主控制模块拆分成两个小的模块——按键输入模块、按键输入判断输出模块。

后者使用4个D触发器来实现,当游戏开始的时候4个D触发器都会接收按键按下的信息,并且判断是否出现问题,下面我就真实的程序来进行说明。

1、主控制模块的按键输入模块LED3=how0;LED4=how0;endendEndmodule总体的电路图如下:(有些模糊,是因为电路图的连线过长,截图的时候不得不截成一个明显的长方形图形)四、实验总结:通过这次的实验任务,学习了一些verilogHDL语言的知识,也复习了数字电子技术相关的知识。

以前只是在纸上画过一些原理图,如果需要改动某一个点的时候就会出现牵一发而动全身的现象,对于比较复杂的电路设计,纸上的勾勾画画很显然会很浪费时间,所以对于程序设计电路的方式我相信大多数人是持欢迎态度的。

课程设计(四人抢答器)实验报告

课程设计(四人抢答器)实验报告课题:四人智力抢答器专业:班级:学号:姓名:指导教师:设计日期:成绩:电气学院四人智力抢答器设计报告一、设计目的作用1.掌握四人智力竞赛抢答器电路的设计、组装与调试方法。

2.熟悉数字集成电路的设计和使用方法。

二、设计要求设计一台可供4名选手参加比赛的智力竞赛抢答器。

当主持人说开始时,四人开始抢答,电路能判别出四路输入信号中哪一路是最先输入信号,并给出声、光、数码显示。

(1) 4名选手编号为:1,2,3,4。

各有一个抢答按钮,按钮的编号与选手的编号对应,也分别为1,2,3,4。

(2) 给主持人设置一个控制按钮,用来控制系统清零和抢答的开始。

(3) 抢答器具有数据锁存的功能。

抢答开始后,若有选手按动抢答按钮,该选手指示灯亮并立即锁存,同时扬声器给出音响提示,禁止其他选手抢答。

抢答选手的指示灯一直保持到主持人将系统清零为止。

(4)选择B题的除了具有上述功能外,还要在声、光显示的同时,在数码管上显示选手的编号,编号一直保持到主持人将系统清零为止。

三、设计的具体实现1、系统概述电路主要由脉冲产生电路,锁存电路,编码及译码显示电路和音响产生电路。

当有选手抢答时首先锁存,防止其他选手抢答,然后编码,再经4线7段译码器将数字显示到显示器上同时产生音响,电路结构系统如图:(1)以锁存其为中心的编码显示器抢答信号的判断和锁存可以采用触发器或锁存器。

若以四D触发器74LS175为中心构成编码锁存系统,编码的作用是把锁存器的输出转化为8421BCD码,进而送给7段显示译码器。

其真值表为:锁存器输出编码器输出Q4 Q3 Q2 Q1 D C B A0 0 0 0 0 0 0 00 0 0 1 0 0 0 10 0 1 0 0 0 1 00 1 0 0 0 0 1 11 0 0 0 0 1 0 0(2)脉冲产生电路:采用555组成的振荡器做触发器的时钟脉冲。

(3)音响电路:可以利用555组成的振荡器输出脉冲,接入蜂鸣器,当选手按下按键时鸣叫,知道主持人清零为止。

课程设计报告(四人智力抢答器)

智力竞赛抢答计时器一、设计要求与任务1设计任务智力竞赛抢答器是一名裁判员,他的任务是从若干竞赛者中确定最先抢答者,并要求参赛者在规定的时间里回答完问题。

本设计要求设计一个四人参加的智力竞赛抢答器,每个参赛者控制一个按钮,用按动按钮发出抢答信号;竞赛主持人另有一个按钮,用于将电路复位,竞赛开始后,先按动按钮者将对应的一个发光二级管点亮,此后其他三人再按动按钮对电路不起作用,同时电路具有回答问题时间控制功能,要求回答时间小于60秒(显示0~59),时间显示选用倒计时方式,当达到规定时间时给出警告(警告灯闪烁)。

2设计要求1)4名选手编号分别为1,2,3,4;各有一个按钮,按钮的编号与选手编号灯对应,也分别为1,2,3,4;2)给主持人设置一个控制开关按钮,用来控制系统清零(抢答显示灯,数码管灭灯)和抢答的开始。

3)抢答器具有数据锁存和显示功能。

抢答开始后,若有选手按动抢答按钮,该选手编号立即补锁存,并输入编码电器,并在抢答显示器上显示时钟倒计时,封锁其他选手抢答。

直到抢答倒计时回到“0”后,回答时间到,由主持人将系统清零;4)抢答器具有定时(60秒)回答功能,当主持人按下开始按钮,并有选手第一时间抢答时,定时器开始计时,并在数码管上显示倒计时时间,倒计时结束时,回答时间到,蜂鸣器音响持续1秒,由主持人手动清零,进入下一道题的抢答环节;5)计时器采用频率为1HZ的脉冲信号作为定时计数器的CP信号,抢答电路中74LS161,CP则采用1KHZ,观察较为明显些。

二、硬件电路设计及描述由于设计任务是倒计时器,所以要用到减法器,又因为是十进制的所以我选择的主要芯片是74LS192两片,抢答功能,我利用了74LS161的预置功能,若有选手抢答时,74LS161不断反馈,不断循环预置功能,预置后,其他选手再按下抢答开关,也显示不出来,被封锁;接下来是实现显示的功能,我用的是74LS48芯片和共阴极七段显示器个两片,再根据需要我还用了74LS00(与非门)、74LS04(非门)。

Verilog HDL 课程设计报告 四人抢答器电路设计 河海大学

河海大学计算机与信息学院(常州)课程设计报告题目四人抢答器电路设计学号 1062510130 授课班号 274302 学生姓名王聪同组成员 1062510135 张恒指导教师奚吉完成时间2013.01.04四人抢答器电路设计摘要Verilog HDL课程设计的主要动机是1.培养综合运用知识和独立开展实践创新的能力;2.通过完成四人抢答器电路设计,使学生不但能够将课堂上学到的理论知识与实际应用结合起来,而且能够对分析、解决实际的数字电路问题进一步加深认识,为今后能够独立进行某些数字应用系统的开发设计工作打下一定的基础;3.通过搭建调试电路,进一步熟悉相关仪器设备的使用;4.通过Verilog程序的编写,进一步熟悉Verilog HDL的语法知识;5.规范化训练学生撰写技术研究报告,提高书面表达能力。

四人抢答器电路设计的主要问题在于各个模块的正确分配,从而使设计出的电路更加符合要求。

为了使各个模块能够正确分配,在程序开始设计之前,必须反复推敲本组的设计方案并设计好各个模块的方框图。

如果一切都设计好之后,那么最后的电路会具有抢答第一信号鉴别和锁存功能、主持人清屏功能、30秒倒计时功能、蜂鸣器报警功能。

实现四人抢答器的预期功能需要:1.将任务分成若干模块,查阅相关论文资料,分模块调试和完成任务;2.遇到本组内解决不了的问题,及时和其他小组交流或询问老师;3.进行模块调试时,根据试验箱上现象的不同及时调整相关程序的内容。

本次课程设计的实现的重要结果1.完成了实验环境搭建;2.实现了一四人抢答器,有人抢答成功后,其他人再抢答无效;3.通过蜂鸣器响1秒来提示抢答成功,并在数码管上显示抢答者的序号;4.主持人通过按键清除抢答信息,并开始30秒的答题倒计时,当倒计时结束时,通过蜂鸣器响1秒来提示回答问题时间到,此时可以开始新一轮的抢答。

当然,本次课程设计还有诸多不足之处,我们已经力求改进以求设计的实用性及完美性。

基于fpga的四路抢答器课程设计报告

一、课题设计的基础和实验条件1.工作基础(1)数字电路,模拟电路的学习;对所需使用的芯片管脚及功能的了解;掌握了基本的数字电路设计流程。

(2)学会使用MAX+PLUS 软件设计数字电路;了解EDA实验开发系统。

2.实验条件(1)提供有目标芯片:FPGA-型号EP7128SLC84-15的实验开发系统、数码显示器、二极管、三极管、钮子开关;(2)电路设计器件:AND4、NOT、D触发器等二、设计目标1. 4人抢答器(四名选手分别为:R1,R2,R3,R4);2. 主持人启动及复位开关HT;3. 七段显示码显示选手的编号;4. 抢答器具有“互锁”功能;三设计电路图及仿真该设计属于较为复杂的中小规模数字系统设计,按照系统的功能要求和自顶向下的层次化设计思想,该抢答器可以分为三个模块,他们分别为:抢答器控制模块——IN,该模块用于控制选手及主持人的动作;编码模块——qiwei,用于将选手的编号编码以便用数码管显示输出;(1)抢答器控制模块IN的设计:该模块在任意一位选手首先按下抢答键后,其输出高电平给D锁存器,并将输出结果送至编码器qiwei, 该模块的主持人按键HOST按钮可以实现系统的复位。

其原理图为:选手的输出信号发出之后,需要把输出转换为数字,故需要加一个七位译码器。

(2)七位译码器的设计:通过编程定义生成了一个七位译码器:生成此七位译码器的程序如下:(3)生成完整设计图:两个模块进行连接即得到最终的实验电路图:(4)设计图的仿真:对设计的电路进行仿真得到仿真图如下:从仿真结果可以看出符合功能要求。

(5)连接引脚图:根据设计图选择适当的引脚连接得到下图的引脚图连接完引脚图后,通过PROGRAMER即可通过开发板来进行调试验证。

最终通过多次的调试与验证,终于完成了实验。

四心得体会:本次实践我认为完成的比较艰辛,首先在上第一节课的时候,听老师讲到这门课程设计需要学到一些先修课程。

但是单片机,PLC,FPGA我之前都没学过,而且之前学的数电和模电也很多知识都有些记不清了。

用VerilogHDL编写四路抢答器

always@(*) begin case(qiang_da) 1:bian_ma=3'b001; 2:bian_ma=3'b010; 4:bian_ma=3'b011; 8:bian_ma=3'b100; default:bian_ma=3'b000; endcase end

assign suo=(~bian_ma_cun[0])&(~bian_ma_cun[1])&(~bian_ma_cun [2]);

assign suo_1=suo&fankui;

always@(*) begin if(qing_ling==1) bian_ma_cun<=3'b000; else if(suo_1==0) bian_ma_cun<=bian_ቤተ መጻሕፍቲ ባይዱa_cun; else bian_ma_cun<=bian_ma; end

output wire [6:0]a_to_g; output wire [3:0]A_TO_D; input wire clk;//50MHz时钟 wire [3:0]qian; wire [3:0]bai; wire [2:0]shi; wire [2:0]ge; wire cp;//1s时钟 input wire [3:0]qiang_da; input button; wire suo_1; wire [2:0]bian_ma_cun; wire fankui; output wire xuan; shumaguan shumaguan0(a_to_g,A_TO_D,clk,qian,bai,shi,ge); cp_1s cp_1s0(clk,cp); xuan_shou xuan_shou0(qiang_da,button,suo_1,bian_ma_cun,fankui); wei_xuan wei_xuan0(bian_ma_cun,xuan,shi,ge); fuwei_kongzhi fuwei_kongzhi0(button,xuan); jishu_kongzhi jishu_kongzhi0(bai,qian,cp,suo_1,xuan,fankui); endmodule

四人竞赛抢答器电路设计

四人竞赛抢答器的设计

一、电路设计框图

二、电路设计总图

三、电路各部分的设计

四人竞赛抢答器的设计

技能目标

1.能根据需要选用适当的触发器进行设计。

2.能正确使用逻辑分析仪或示波器进行数字信号分析。

知识目标

1. 集成触发器的使用。

2. 组合逻辑电路和实序电路的综合设计。

3. 逻辑分析仪的使用方法。

0

1

1

0

0

1

0

2

0

0

1

1

3

0

1

0

0

4

三、电路各部分的设计

5. 数码显示电路

A、B 、C 、 用组合逻辑电路设计方法设计一个由抢答的逻辑状态到

8421BCD码的转换电路。

D分别表示

第1、2、3、

4 队对应的

JK触发器的输出 Q

JK触发器

(U1A、U1B、

U2A、U2B)

的输出

,

Q

用Y3、Y2、Y1、Y0分

4. 声音报警电路设计

蜂鸣器是一种一体化结构的电子音响器,采用直流电压

供电,广泛应用于计算机、报警器、电子玩具、汽车电子设

备、电话机、定时器等电子产品中作发声器件。

分为压电式蜂鸣器和电磁式蜂鸣器两种类型。

三、电路各部分的设计

5. 数码显示电路

Y3

Y2

Y1

Y0

显示

Y3 Y2 Y1 Y0

0

0

0

0

0

0

0

数码管显示队号

三、电路各部分的设计

1. 按键输入部分:抢答键

主持人按键:

抢答键:

三、电路各部分的设计

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

河海大学计算机与信息学院(常州)课程设计报告题目四人抢答器电路设计学号 1062510130 授课班号 274302 学生姓名王聪同组成员 1062510135 张恒指导教师奚吉完成时间2013.01.04四人抢答器电路设计摘要Verilog HDL课程设计的主要动机是1.培养综合运用知识和独立开展实践创新的能力;2.通过完成四人抢答器电路设计,使学生不但能够将课堂上学到的理论知识与实际应用结合起来,而且能够对分析、解决实际的数字电路问题进一步加深认识,为今后能够独立进行某些数字应用系统的开发设计工作打下一定的基础;3.通过搭建调试电路,进一步熟悉相关仪器设备的使用;4.通过Verilog程序的编写,进一步熟悉Verilog HDL的语法知识;5.规范化训练学生撰写技术研究报告,提高书面表达能力。

四人抢答器电路设计的主要问题在于各个模块的正确分配,从而使设计出的电路更加符合要求。

为了使各个模块能够正确分配,在程序开始设计之前,必须反复推敲本组的设计方案并设计好各个模块的方框图。

如果一切都设计好之后,那么最后的电路会具有抢答第一信号鉴别和锁存功能、主持人清屏功能、30秒倒计时功能、蜂鸣器报警功能。

实现四人抢答器的预期功能需要:1.将任务分成若干模块,查阅相关论文资料,分模块调试和完成任务;2.遇到本组内解决不了的问题,及时和其他小组交流或询问老师;3.进行模块调试时,根据试验箱上现象的不同及时调整相关程序的内容。

本次课程设计的实现的重要结果1.完成了实验环境搭建;2.实现了一四人抢答器,有人抢答成功后,其他人再抢答无效;3.通过蜂鸣器响1秒来提示抢答成功,并在数码管上显示抢答者的序号;4.主持人通过按键清除抢答信息,并开始30秒的答题倒计时,当倒计时结束时,通过蜂鸣器响1秒来提示回答问题时间到,此时可以开始新一轮的抢答。

当然,本次课程设计还有诸多不足之处,我们已经力求改进以求设计的实用性及完美性。

关键字:Verilog HDL 方框图 QuartusII 抢答器AbstractThe main motivations of the Verilog HDL curriculum design including five aspects. The first of them is cultivating the capabilities of integrated use of knowledge and carrying out practical innovation independently. Secondly, by completing four people Responder circuit design, students can not only apply the theories what they have learned in classes to the practical application, but also deepen the understanding of analyzing and solving the question about practical digital circuit, which can form the foundation for carrying out the development and design work of some digital applications systems in the future. Thirdly, we become more familiar with the use of the equipment by building debug circuitry. Fourthly, by writing Verilog program, we will be more skilled in Verilog HDL syntax knowledge. The last one of them is training students to write a technical report standardized to improve writing skills.The main problem of it is that the correct allocation of the various modules, so that the circuit is more in line with the requirements. In order to assign each module correctly, we must scrutiny the design repeatedly and finish the block diagram of each module before we began the program. If all designed are ok, the final circuit will have the abilities in identifying and latching the first signal, clearing screen with the host, 30-second countdown function, buzzer alarm function.Achieving the intended function of the four-person Responder need: 1. Task is divided into a number of modules and having access to relevant information papers, sub-module debugging and completing the task; 2. Solving the problem in a timely manner and communicating with other groups or asking a teacher; 3. When debugging module, we should adjust of the contents of the relevant procedures on the time depending on the different phenomenon.The curriculum design achieved important results including: pleting structures of experimental environment; 2. Achieving a four people Responder and others cannot answer in invalid after someone answered in success; 3. With buzzer seconds to prompt answer in success, and display the answer in the serial number on the digital; 4. The host clears the information, and begin to answer 30 seconds countdown time prompted to answer questions by one second buzzer, when the countdown is end, a new round will start.Of course, during the curriculum design, there are still many inadequacies, we have sought to improve the practicality and perfection.Key word: Verilog HDL Block diagram QuartusII Responder1 系统设计1.1 要求的设计目标(1)实现一四人抢答器,有人抢答成功后,其他人再抢答无效;(2) 通过蜂鸣器响1秒来提示抢答成功,并在数码管上显示抢答者的序号;(3)主持人通过按键清除抢答信息,并开始30秒的答题倒计时,当倒计时结束时,通过蜂鸣器响1秒来提示回答问题时间到,此时可以开始新一轮的抢答。

1.2 方案的对比分析与确定我们通过搜索资料,并且依据所学知识,为清晰明了简便的设计出想达到的目标,最终我们采用设计的总体方案是将整个任务分成3个模块即分频模块、抢答及报警模块、倒计时并报警模块。

1.3 电路方框图及说明图1电路方框图及说明1.4 电路设计及说明1.4.1 分频模块因为试验箱上的时钟是50M 的,而倒计时模块中要用到1hz 和1khz 的时钟,所以要对50M 时钟进行分频产生1hz 和1khz 的时钟,分频模块程序如下: module fenpin(rst,clk,clk_1khz,clk_1hz);input rst,clk;output clk_1khz,clk_1hz;reg clk_1khz,clk_1hz;reg[24:0] count1;reg[14:0] count2;always @(posedge clk or negedge rst)beginif(!rst)count1 = 0;else if(count1==25'd2*******)beginclk_1hz = ~clk_1hz;count1 = 0;endelsecount1 = count1+25'b1;endalways @(posedge clk or negedge rst)beginif(!rst)count2 = 0;else if(count2==15'd25000)beginclk_1khz = ~clk_1khz;count2 = 0;endelsecount2 = count2+15'b1;endendmodule1.4.2抢答模块、倒计时模块抢答模块中,要具有第一信号鉴别、锁存功能。

第一信号鉴别锁存的关键是准确判断出第一抢答者并将其锁存,在得到第一信号后,将输入端封锁,使其他组的抢答信号无效,可以用触发器或锁存器实现。

设置抢答按钮din1、din2、din3、din4,主持人复位信号judge。

judge=0时,第一信号鉴别、锁存电路、答题计时电路复位;judge=1时,开始抢答,由第一信号鉴别锁存电路形成第一抢答信号,并进行组别显示。