曼彻斯特解码器

曼彻斯特解码程序

曼彻斯特解码1、变量定义 (2)2、Manchest初始化 (2)3、Manchest解码信号翻转 (3)4、过滤错误的卡号 (4)5、获取正确的卡号 (5)6、Manchest获取卡号数据 (6)7、通过中断采样获取刷卡数据 (9)1、变量定义#define TH1_370US_H 0XFE //晶振11.0592MHZ,12T模式#define TL1_370US_L 0XAB#define SIGNAL_FLIP_TIME 10 //每隔100ms翻转一次读卡信号#define REPEAT_TIME 5 //500ms后重复读卡#define CLEAR_CARD_TIME 20 //2S后清除卡号数据#define MANCHEST_TIME 5sbit PULSE = P3^2;sbit RFEN = P3^5; //曼彻斯特解码脉冲信号sbit MANCHEST0= P3^2; //wiegand0sbit MANCHEST1= P3^3; //wiegand1uchar code CheckingTab[32]={ //接收到10组卡号的偶校验0X00,0X01,0X01,0X00,0X01,0X00,0X00,0X01, //这里数值是低五位的偶校验值0X01,0X00,0X00,0X01,0X00,0X01,0X01,0X00,0X01,0X00,0X00,0X01,0X00,0X01,0X01,0X00,0X00,0X01,0X01,0X00,0X01,0X00,0X00,0X01};uchar WGCardBuf[5]; //卡号uchar CopyCardBuf[5]; //备份卡号uchar ManchestBuf[11]; //暂存接收到的11组数据uchar idata g_ucManchestTime = MANCHEST_TIME; //uchar idata g_ucDWithCardTime= 0; //隔500ms处理该卡号uchar idata g_ucPreambleFlag = 0;uchar idata g_ucERAgainTimer = 0; //每隔100ms翻转一次RFENuchar idata g_ucStoreGroupCnt= 0; //接收到几组数据,这里为11组才可能正确uchar idata g_ucEGroupBitCnt = 0; //每组数据有5个为,5=4位卡号+1位偶校验uchar idata g_ucPreambleCount= 0; //9位为1的引导码uchar idata g_ucRemvoeCardTime=0; //隔多久清除以前的卡号数据,这里为3s2、Manchest初始化/******************************************************************** 函数原型:ManchestInit功能:曼彻斯特解码变量初始化输入:无输出:无说明:无*-------------------------------------------------------------------- *修改时间| 修改者| 备注*-------------------------------------------------------------------- *2012-02-14 Oscar First********************************************************************/ void ManchestInit(void) //初始化读卡参数{RFEN = 1;g_ucPreambleFlag = 0;g_ucStoreGroupCnt = 0;g_ucEGroupBitCnt = 5;g_ucPreambleCount = 9;g_ucERAgainTimer = SIGNAL_FLIP_TIME;}3、Manchest解码信号翻转/******************************************************************** 函数原型:ProcessManchestSignal功能:manchest解码的翻转信号输入:无输出:无说明:无*-------------------------------------------------------------------- *修改时间| 修改者| 备注*-------------------------------------------------------------------- *2012-02-14 Oscar First********************************************************************/ void ProcessManchestSignal(void){if((g_ucDWithCardTime!=0)&&(--g_ucDWithCardTime==0)){}if((g_ucRemvoeCardTime!=0)&&(--g_ucRemvoeCardTime==0)){CopyCardBuf[0] = 0; //清除卡号缓冲区CopyCardBuf[1] = 0;CopyCardBuf[2] = 0;CopyCardBuf[3] = 0;CopyCardBuf[4] = 0;}RFEN = ~RFEN;g_ucPreambleFlag = 0;g_ucPreambleCount= 9;if(RFEN){EX0 = 1;EX1 = 1;}else{EX0 = 0;EX1 = 0;}}4、过滤错误的卡号/******************************************************************** 函数原型:CalibrationCardData功能:一张卡号,如果出现全部相同的数字或者该卡号只有两种数据,则认为是错误的卡号。

【2017年整理】一种简便的ID卡曼彻斯特解码方法

一种简便的ID卡曼彻斯特解码方法我这里介绍的是常用的125KHz的ID卡。

ID卡内固化了64位数据,由5个区组成:9个引导位、10个行偶校验位“PO~P9′’、4个列偶校验位“PC0~PC3”、40个数据位“D00~D93”和1个停止位S0。

9个引导位是出厂时就已掩膜在芯片内的,其值为“111111111”,当它输出数据时,首先输出9个引导位,然后是10组由4个数据位和1个行偶校验位组成的数据串,其次是4个列偶校验位,最后是停止位“0”。

“D00~D13”是一个8位的晶体版本号或ID识别码。

“D20~D93”是8组32位的芯片信息,即卡号。

注意校验位都是偶校验,网上有些资料写的是奇校验,很明显是错的,如果是奇校验的话,在一个字节是FF 的情况下,很容易就出现9个1,这样引导位就不是唯一的了,也就无法判断64位数据的起始位了。

数据结构如下图:我读的一个ID卡数据是111111111 10001 00101 00000 00011 00000 01010 00000 11011 00110 01100 01100,对应的ID卡号是01050d36。

ID卡数据采用曼彻斯特编码,1对应着电平下跳,0对应着电平上跳。

每一位数据的时间宽度都是一样的(1T)。

由于电路参数的差别,时间宽度要实际测量。

解码芯片采用U2270B,单片机采用89S52。

U2270B的输出脚把解码得到的曼彻斯特码输出到89S52的INT脚。

在89S52的外部中断程序中完成解码。

在没有ID卡在读卡器射频范围内时,U2270B的输出脚会有杂波输出,ID卡进入读卡器射频范围内后,会循环发送64位数据,直到ID卡离开读卡器的有效工作区域。

根据ID卡的数据结构,64位数据的最后一位停止位是0。

最开始的9位引导位是1,可以把0111111111做为引导码。

也就是说在ID卡进入读卡器工作范围后,丢掉ID卡发送的第一个64位码,检测最后1位0,然后检测ID卡发送的第2个64位码的9个引导码111111111,引导码检测成功后,解码剩余的55位码。

基于CPLD的曼彻斯特编码技术_王奇

语 言进 行设 计 , 使 用 , 仿真 图形

是 发送端 的并行 信 号 的 时钟 信 号 , 在 切 的 二倍 频 时 钟 信 可 以看 出 ,

进行 仿真 , 仿 真 的数 据编 码速 率设 为

以 是 由外 部提供 的 中进 行 分频 , 产生需要的 号

在 倍频时钟的 几 升沿

几 分频 频 位 计数 器

曼彻 斯特码

在曼 彻斯 特编码 〔 '一 冲 , 每一 位 的中间 有一 个跳 变 ,

位 中间 的跳变 既作 时钟信 号 , 又 作数 据信 号 。 从 高 到低 跳变 表示 “ ” , 从低 到高 跳变表 示 “ ” 。

从 曼 彻 斯特 码 的特 点 可 以看 出曼彻 斯 特 码 是一 种

间节 点更 加可靠 , 进 而通 信成 功的概 率不 断地提 高 。 本文 提 出 了一 种基 于反 馈评 价 信任 机制 的模 型 , 通

' , 一

过 节点 间在通 信 结 束后 互 相反 馈 信任 信 息来 计 算 节 点

的信 任 度 , 同时也 考 虑 到节 点 的信 任 率 , 通 过 仿 真试 验 看 出 , 信 任机 制模 型通信 成功 的概 率还 是很 高 的 。 相 较 于改 进前 的模 型 , 系统在 抑制 恶意 节点 的效 率也 有所 提 高 。 参考 文献

N 6t w or k

and C O m m u ni Ca t i on

基于

的曼彻斯特编码技术

王 奇 , 王英 民 , 牛 奕龙 , 陶林 伟

西北 工 业 大 学 , 陕西 西 安

摘 要

研 究 了曼彻 斯 特 编 解码 方 法 , 采 用

语 言在

上 实现 了编 解 码 , 使 系统 的功 能 高 仿真 了 速 率 下 的编 解 码 , 结果 和

曼彻斯特解码原则+125K EM4100系列RFID卡解码源程序分析

曼彻斯特解码原则+125K EM4100系列RFID卡解码源程序分析曼彻斯特解码原则1.曼彻斯特编码曼彻斯特编码(Manchester Encoding),也叫做相位编码(PE),是一个同步时钟编码技术,被物理层使用来编码一个同步位流的时钟和数据。

曼彻斯特编码被用在以太网媒介系统中。

曼彻斯特编码提供一个简单的方式给编码简单的二进制序列而没有长的周期没有转换级别,因而防止时钟同步的丢失,或来自低频率位移在贫乏补偿的模拟链接位错误。

在这个技术下,实际上的二进制数据被传输通过这个电缆,不是作为一个序列的逻辑1或0来发送的(技术上叫做反向不归零制(NRZ))。

相反地,这些位被转换为一个稍微不同的格式,它通过使用直接的二进制编码有很多的优点。

曼彻斯特编码,常用于局域网传输。

在曼彻斯特编码中,每一位的中间有一跳变,位中间的跳变既作时钟信号,又作数据信号;从高到低跳变表示"1",从低到高跳变表示"0"。

还有一种是差分曼彻斯特编码,每位中间的跳变仅提供时钟定时,而用每位开始时有无跳变表示"0"或"1",有跳变为"0",无跳变为"1"。

对于以上电平跳变观点有歧义:关于曼彻斯特编码电平跳变,在雷振甲编写的<<网络工程师教程>>中对曼彻斯特编码的解释为:从低电平到高电平的转换表示1,从高电平到低电平的转换表示0,模拟卷中的答案也是如此,张友生写的考点分析中也是这样讲的,而《计算机网络(第4版)》中(P232页)则解释为高电平到低电平的转换为1,低电平到高电平的转换为0。

清华大学的《计算机通信与网络教程》《计算机网络(第4版)》采用如下方式:曼彻斯特编码从高到低的跳变是0 从低到高的跳变是1。

两种曼彻斯特编码是将时钟和数据包含在数据流中,在传输代码信息的同时,也将时钟同步信号一起传输到对方,每位编码中有一跳变,不存在直流分量,因此具有自同步能力和良好的抗干扰性能。

基于FPGA的曼彻斯特码编解码器的实现

编码 过程具 体可 分 为三部 分 :1 检测 编码周 期 是 ()

否 开始 , 辨别 同步 头信 号 ( 令/ 据 ) 生相 应 的同 并 命 数 产 步信 号 ;2 对 1 数 据进 行 编 码 ;3 附加 奇 偶 校 验 () 6位 ()

1 Vei gHDL硬 件 描 述 语 言 r o l

V ro D ei gH L是 目前 应 用最 为广 泛 的 硬 件 描 述 语 l

图 1 曼彻 斯 特 码 Ⅱ编 码 的码 型 结 构

2 1 编 码设 计与 实现 .

言 , 以在算 法级 、 可 门级 到 开关级 的多 种抽 象设 计层 次

O 引 言

在油 田测 井 中 , 多 种 仪 器 都 采用 曼 彻 斯 特 码 将 很 所采 集 的大 量信 息传送 给 地面测 井 系统 。曼彻 斯特 编

码是 串行数 据传 输 的一 种 重 要 的 编码 方 式 , 有 很 好 具 的抗 干 扰性 能 , 常情况 下 通过 HD15 0曼 彻斯 特 码 通 3 5

不必 过 多考 虑 门级及 工 艺 实 现 的具 体 细 节 , 只需 根 据 系统 设计 的要 求施 加 不 同的 约束 条 件 , 可设 计 出 实 即

际 电路 J 。

2 曼 彻 斯 特 码 编解 码 器 的 总体 设 计

图 2 编 码 状 态 转 换 图

本文 的设 计遵 循 曼 彻 斯 特码 编 译 码 规 则 , 现 了 实

编译 码器 来 实 现 。利 用 F G P A来 实 现 H 5 3 D1 5 0的 功

变 原来通 讯 电路 的情 况 下 , 将该 模 块 与 脉 冲 中子 能 谱 测 井仪通 讯 系统 对 接 , 现 了用 F G 实 P A替 代 HD 53 150

Verilog_VHDL_曼彻斯特编码器

1.5.什么叫“综合”?一般“综合”包含哪些过程?答:在电子设计领域中“综合”的概念可以表示为:将用行为和功能层次表达的电子系统转换为低层次的便于具体实现的模块组合装配的过程。

综合包含的过程:对VHDL或Verilog HDL进行处理分析,并将其转换成电路结构或模块,这时不考虑实际器件实现,即完全与硬件无关,这个过程是一个通用电路原理图形成的过程:第2步,对实际实现目标器件的结构进行优化,并使之满足各种约束条件,优化关键路径,等等。

2.10 使用Quartus II的 Mega Wizard Plug-In Manager宏功能模块中的PLL设计一个能实现图题2.10波形的电路元件(包括一个VHDL文件和一个*.bsf原理图图标)。

其中:inclk0为电路的主频输入端,频率为50MHz;areset为异步置位端,c2和主频inclk0同频率。

c1为主频inclk0的倍频输出信号。

C0为c2的反相信号。

Locked为相位控制信号,也是输出使能控制信号。

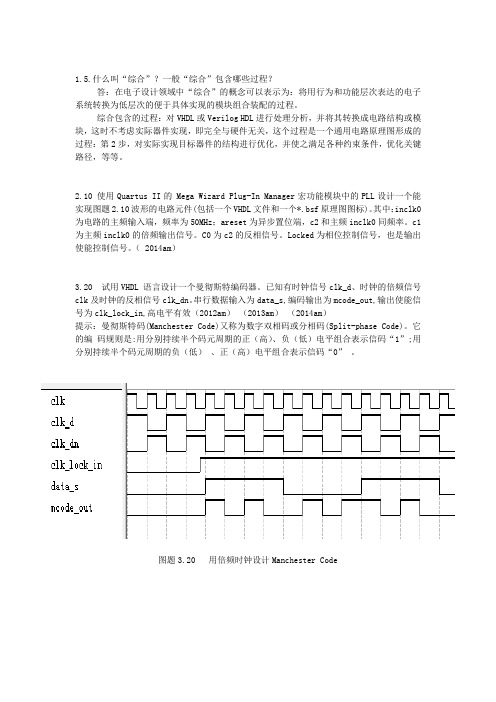

( 2014am)3.20 试用VHDL 语言设计一个曼彻斯特编码器。

已知有时钟信号clk_d、时钟的倍频信号clk及时钟的反相信号clk_dn。

串行数据输入为data_s,编码输出为mcode_out,输出使能信号为clk_lock_in,高电平有效(2012am)(2013am)(2014am)提示:曼彻斯特码(Manchester Code)又称为数字双相码或分相码(Split-phase Code)。

它的编码规则是:用分别持续半个码元周期的正(高)、负(低)电平组合表示信码“1”;用分别持续半个码元周期的负(低)、正(高)电平组合表示信码“0”。

图题3.20 用倍频时钟设计Manchester Code图题3.20 用双时钟设计Manchester Code 的仿真结果hsu_manchester_code_vmodule hsu_manchester_code_v ( clk,clk_d,clk_dn,data_s,clk_lock_in,mcode_out); input clk,clk_d,clk_dn,data_s,clk_lock_in;output mcode_out;reg mcode_out;reg temp_mcode_out;reg temp_mcode_out_ddn;always ( posedge clk or posedge clk_lock_in )beginif (clk_lock_in==1'b1)if (data_s==1'b1)temp_mcode_out<=clk_d;elsetemp_mcode_out<=1'b0;elsetemp_mcode_out=1'b0;endalways ( posedge clk or posedge clk_lock_in )beginif (clk_lock_in==1'b1)if (data_s==1'b0)temp_mcode_out_ddn<=clk_dn;elsetemp_mcode_out_ddn<=1'b0;elsetemp_mcode_out_ddn=1'b0;Endalways ( posedge clk or posedge clk_lock_in )beginif (clk_lock_in==1'b1)mcode_out<=temp_mcode_out;temp_mcode_out_ddn;elsemcode_out<=1'b0;endendmodule3.21 试用VHDL 语言设计一个求两个数中最大值的程序,要求用函数调用的方法设计。

曼彻斯特解码原则 125K EM4100系列RFID卡解码源程序分析资料

曼彻斯特解码原则+125K EM4100系列RFID卡解码源程序分析曼彻斯特解码原则1.曼彻斯特编码曼彻斯特编码(Manchester Encoding),也叫做相位编码(PE),是一个同步时钟编码技术,被物理层使用来编码一个同步位流的时钟和数据。

曼彻斯特编码被用在以太网媒介系统中。

曼彻斯特编码提供一个简单的方式给编码简单的二进制序列而没有长的周期没有转换级别,因而防止时钟同步的丢失,或来自低频率位移在贫乏补偿的模拟链接位错误。

在这个技术下,实际上的二进制数据被传输通过这个电缆,不是作为一个序列的逻辑1或0来发送的(技术上叫做反向不归零制(NRZ))。

相反地,这些位被转换为一个稍微不同的格式,它通过使用直接的二进制编码有很多的优点。

曼彻斯特编码,常用于局域网传输。

在曼彻斯特编码中,每一位的中间有一跳变,位中间的跳变既作时钟信号,又作数据信号;从高到低跳变表示"1",从低到高跳变表示"0"。

还有一种是差分曼彻斯特编码,每位中间的跳变仅提供时钟定时,而用每位开始时有无跳变表示"0"或"1",有跳变为"0",无跳变为"1"。

对于以上电平跳变观点有歧义:关于曼彻斯特编码电平跳变,在雷振甲编写的<<网络工程师教程>>中对曼彻斯特编码的解释为:从低电平到高电平的转换表示1,从高电平到低电平的转换表示0,模拟卷中的答案也是如此,张友生写的考点分析中也是这样讲的,而《计算机网络(第4版)》中(P232页)则解释为高电平到低电平的转换为1,低电平到高电平的转换为0。

清华大学的《计算机通信与网络教程》《计算机网络(第4版)》采用如下方式:曼彻斯特编码从高到低的跳变是0 从低到高的跳变是1。

两种曼彻斯特编码是将时钟和数据包含在数据流中,在传输代码信息的同时,也将时钟同步信号一起传输到对方,每位编码中有一跳变,不存在直流分量,因此具有自同步能力和良好的抗干扰性能。

电视话语中的编码与解码

其次,霍尔强调了受众在传媒文化研究中的重要性。他突破了传统的受众研 究范式,将受众视为具有主动性和创造性的个体,而非被动接受信息的容器。这 种对受众的重新定义,为我们理解传媒文化的传播效果提供了新的视角。

再次,霍尔将社会政治批判引入传媒文化研究中。在《电视话语的编码与解 码》中,他揭示了电视话语背后的权力结构和意识形态,揭示了电视话语对社会 文化和价值观的影响。这种批判性的研究方法为我们认识传媒文化的社会功能提 供了重要思路。

霍尔的文化研究方法论强调社会批判性思考,倡导媒介素质教育,对于我们 发展具有中国特色的文化产业模式具有重要的借鉴意义。

在借鉴霍尔文化理论的实践中,我们需要反思并中国本土的社会、文化和历 史背景。只有这样,我们才能真正发挥其理论的指导作用,推动中国特色的文化 产业发展。我们应坚持社会批判为前提,运用霍尔的理论来深入分析和理解中国 的传媒文化现象

三、解码方式

解码是编码的逆过程,即将编码后的数据还原成原始形式的过程。在电视话 语中,解码方式也可分为静态解码和动态解码两种。

1、静态解码

静态解码主要针对语音、文字、图像等固定编码方式进行解码。解码过程中, 需要根据编码方式和参数,将数字信号还原成原始信号。对于语音信号,需要通 过解码器将其还原成人类可听的语音;对于文字信号,需要将其还原成人类可读 的文字;对于图像信号,需要将其还原成人类可看的图像。

其次,霍尔的文化理论对于具体文化议题有很强的解释力。例如,他运用编 码/解码理论来解释大众传媒中的文化认同问题。他指出,媒体通过特定的编码 方式传递信息,而受众则根据自己的解码方式来理解和接受这些信息。这种差异 可能导致受众对媒体信息的误读,进而影响他们的文化认同。

总的来说,斯图亚特·霍尔的文化理论和方法论贡献对于我们理解传媒文化 现象具有重要的启示作用。他的理论不仅为我们提供了理解文化传播复杂过程的 新视角,也为我们研究不同受众群体的文化认同提供了有力的分析工具。更重要 的是,

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

DS01470A_CN 第 2 页

© 2013 Microchip Technology Inc.

AN1470

图 3: CLC 功能

与 - 或- OR AND 或 - 异或 OR - XOR

lcxg1 lcxq lcxg2 lcxg3 lcxg4 lcxq

lcxg1 lcxg2 lcxg3 lcxg4

图 7:

数据捕捉

© 2013 Microchip Technology Inc.

DS01470A_CN 第 5 页

AN1470

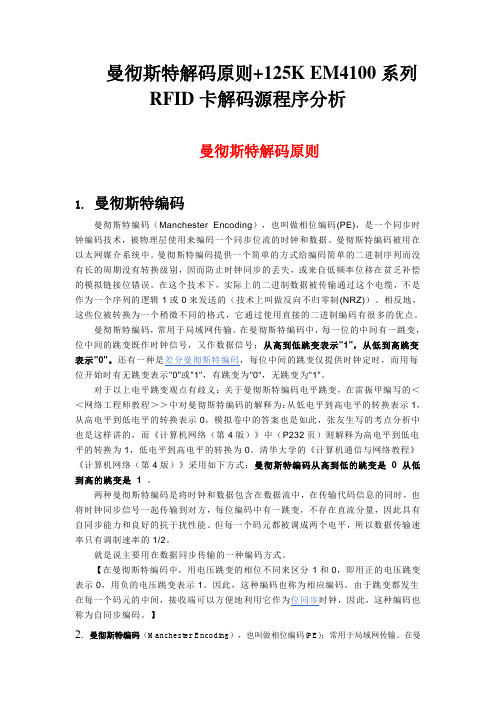

或 - 异或配置中的 CLC 模块用于从此配置中提取时钟 (图 8)。

图 8:

时钟提取

这本质上就是曼彻斯特解码器,其中 CLC OR-XOR 为 时钟,D 为数据。如果使用时钟信号的上升沿捕捉 D 的

AN1470

曼彻斯特解码器

本节和下文所介绍的方法均基于图1所示的符合G.E.Thomas 标准的曼彻斯特编码。该方法很灵活,可轻松移植到 IEEE 802.3。 根据模块的空闲状态、 单片机引脚的上电配 置以及接收的第一个位,首次电平转换会存在一些差异 并需要考虑某些事项 (转换基于编码方法) 。启动和空 闲状态将在本文档的 “同步”一节中讨论。 CLC 模块非常灵活,通过对各个模块的输入或输出极性 进行取反即可轻松应用到各种场合。还可以在软件中控 制NCO模块的空闲状态。 下文讨论的方法假定数据在每 个位时间的前半部分可用。 下面是一个符合 G.E. Thomas 编码标准的编码位流示例 (图 5)。 此信号将被解码成时钟线和数据线,如图 6 所示。

LCxMODE<2:0> = 000 000 LCxMODE<2:0>=

LCxMODE<2:0> = 001 001 LCxMODE<2:0>=

4 输入与 AND 4-Input

SR 锁存器 S-R Latch

lcxg1 lcxg2 lcxg3 lcxg4 lcxq

lcxg1 lcxg2 lcxg3 lcxg4 R S Q

第 3 级 ——NCO + 与 - 或(CLC1)

PIC16F1509 的 NCO 模块用于生成 ¾ 位时间以捕捉数据 值。在低电平有效脉冲频率模式下,在 ¾ 位时间结束时 使用 NCO 输出一个脉冲。可以使用特殊功能寄存器控 制脉冲宽度。该模块还需要一个时钟源,便于以指定的 时钟速率将一个固定值重复添加到累加器,该时钟将由 CLC1 提供。

数据,会注意到除第一个位以外的每个位都被解码。该 问题有多种解决方法,这将在“同步”一节中讨论。

图 9:

曼彻斯特解码器

上述时序图(图 9)解码成以下框图(图 10)。该框图 分为五个级: • 第 1 级 —— 传入的曼彻斯特信号 • 第2级——在触发NCO时捕捉输入数据的D型触发器

• 第 3 级——为 NCO 提供起始时间的异或门 • 第 4 级 —— 为 NCO 提供时钟的与 - 或门,还用于确 保时钟持续完整的 ¾ 位时间 • 第 5 级——用于生成 ¾ 位时间的 NCO,在上一个位 的位中转换时启动。

DS01470A_CN 第 6 页

© 2013 Microchip Technology Inc.

AN1470

图 10: 完整的解码器框图

CLC4 CLC2 CLC1 数据输出 数据输入 S D Q1

R

FOSC

NCO CLK OUT

时钟输出

PIC16F1509 实现

为此实现选择的器件为 PIC16F1509。该器件具有四个 可实现组合逻辑的CLC模块,以及一个可生成特定位时 间的 NCO。以下部分将介绍如何使用该器件上的可用 资源实现这些模块。

图 3 中给出了这些逻辑功能。每个逻辑功能有四个输入 和一个输出。四个输入是上一级的四个数据门输出。

CLC 配置工具

CLC 是含有多个组合电路和时序电路的复杂外设,这些 电路既可以预先编程,也可以动态编程。这实现了灵活 性,但也增加了配置和设置的复杂度。Microchip 提供 的CLC配置工具可以使CLC模块的设置过程更容易实现 和理解。值得一提的是,任何含有未连接输入的门都 将读 为 逻 辑 零 。 要 输 入 逻 辑 1 作 为 门 控 或 锁 存器的 输 入,可以对 0 取反。有关此工具的配置截屏,请参 见 “附录 A”。

图 5:

编码位流

图 6:

数据线和时钟线

对于该位流,需要注意两个关键点,即,位值存在于每 个位时间的前半部分,位中转换之前。每个位周期的中 间位置都会发生转换。这样,我们可以使用位中转换作

为 NCO 的触发信号,并使用 ¾ 位时间来溢出和捕捉下 一个位值(图 7)。该 ¾ 位时间最多允许 +/- ¼ 位时间的 误差。

带复位功能的双输入 D 型触发器 2-Input D Flip-Flop with R

D

Q

lcxq

lcxg1 lcxg3

lcxg1 R lcxg3

R

LCxMODE<2:0> = 100 LCxMODE<2:0>=

LCxMODE<2:0> = 101 101 LCxMODE<2:0>=

带复位功能的 J-K 触发器 J-K Flip-Flop with R

图 2:

曼彻斯特编码数据(符合 IEEE 802.3 标准)

2013 Microchip Technology Inc.

DS01470A_CN 第 1 页

AN1470

可配置逻辑单元

本节介绍使用 PIC16F150x 单片机的 CLC 模块来实现曼 彻斯特解码。可配置逻辑单元(CLC)提供的可编程 逻辑在工作时不受 CPU 执行的限制。该逻辑单元允许 复用其他外设、输入引脚或寄存器位的信号,这通过能 驱动可选单输出逻辑功能的可配置门来实现。每个CLC 模块的输出都可以在内部送至外设、其他CLC模块以及 输出引脚。可以配置以下八种逻辑功能: • • • • • • • • 与-或 或 - 异或 与 SR 锁存器 带置位和复位功能的 D 型触发器 带复位功能的 D 型触发器 带复位功能的 J-K 触发器 带置位和复位功能的透明锁存器

第 1 级 ——D 型触发器(CLC4)

此级在时钟信号的下降沿锁存曼彻斯特数据。输出为将 馈入单片机的恢复数据。数据在时钟下降沿进行采样, 并且可在时钟上升沿稳定读取,因为数据线在时钟上升 沿不会发生变化。

方法。

第 2 级 —— 异或门(CLC2)

由于曼彻斯特编码可确保在每个位的中间位置发生转 换,因此可使用异或门来确保每个位中转换都会为第 3 级提供一个上升沿。这意味着在每个位的中间位置同 步解码器。

摘要

曼彻斯特解码器可基于 Microchip 广受赞誉的可配置逻辑 单元(Configurable Logic Cell,CLC)模块和数控振荡 器(Numerically Controlled Oscillator,NCO)构建, PIC16F150x 器件中提供了这两个模块。PIC16F150x 器 件是Microchip新推出的采用低功耗XLP技术的增强型内 核器件。解码器只需要很少的固件支持,因此在模块 初始化之后,只需要非常少的 CPU 周期。数据和时钟 可以直接送至内部 SPI 模块,从而实现速率最高为 500 kbps 的数据捕捉。

这两个模块共同构成了解码器中最重要的部分。它们在 来自第 2 级的每个上升沿产生一个固定长度的脉冲。 NCO 的输出将反馈给与 - 或门,这样当第 2 级的输出变 为零时,NCO 将继续提供时钟,直到溢出为止。 首次配置该部分时,它将输出一个 ¾ 位长度的脉冲。将 NCO 置于低电平有效状态需要此脉冲。当 NCO 有效 时,NCO 会等待 NCOCLK 寄存器中配置的输出脉冲 宽度时钟。* 一旦提供时钟源,NCO 便完成其有效脉冲 并重新开始计数。 * 设计技巧:通过移除 NCO 的时钟源并将 NCO 保持在 有效状态,这实质上已创建一种控制 NCO 占空比的

简介

曼彻斯特编码广泛用于各种电信和数据存储应用。由 于其具有简单和同步的优势,因此应用于多种系统。

图 1:

曼彻斯特编码数据(符合 G.E. Thomas 标准)

符合 IEEE 802.3 标准的曼彻斯特编码信号(图 2 )与 G.E. Thomas 定义的编码规则相反,从高电平到低电平 的转换表示 0:

图 4:

NCO 框图

递增 Increment

16

(1)

缓冲器 Buffer

16

中断事件 Interrupt event

将 NCOxIF 标志置 Set NCOxIF flag 1

6

NCO1CLK LC1OUT FOSC HFINTOSC

11 10 01 00

2

20

NCOxOUT D

溢出 Overflow NCOx 时钟 NCOx Clock

Q

至 和 CWG ToCLC CLC, CWG

累加器 Accumulator

20

NxOE

Q

0 1

TRIS TRIS控制 Control

NxEN

NCOx

NxCKS<2:0>

溢出 Overflow

NxPFM

S

Q

NxPOL

RQ3Fra bibliotekNxPWS<2:0>

NCOx NCOx时钟 Clock 复位 Reset

Ripple Counter 纹波计数器

LCxMODE<2:0> = 111 111 LCxMODE<2:0>=

© 2013 Microchip Technology Inc.

DS01470A_CN 第 3 页

AN1470

数控振荡器

图4所示的NCO模块是一个定时器,该定时器使用16位 增量寄存器与 20 位累加器相加来对输入频率进行分 频。对于在固定占空比下要求频率精度和精确分辨率 的应用,NCO 是非常有用的。NCO 的特性包括: • • • • • • • 16 位递增功能 固定占空比(Fixed Duty Cycle,FDC)模式 脉冲频率(Pulse Frequency,PF)模式 输出脉冲宽度控制 多个时钟输入源 输出极性控制 中断功能