基于FPGA的水声信号采集与存储系统设计

一种基于FPGA的水声通信调制解调系统EDA设计

~ 一 一 一 一 一 一 ~ 一 一 一 一 ~ 一 ~ ~ 一 ~ 一 一 一 一 一

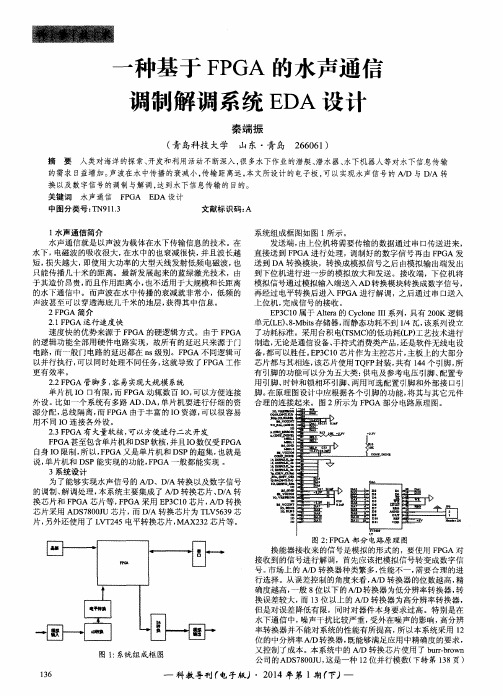

的逻辑功能全部用硬件 电路实现,故所有 的延迟只来源于门 电路 , 而 一 般 门 电路 的延 迟 都 在 n s 级 别 。F P G A 不 同逻 辑 可 以并行执行 , 可 以同时处理不 同任务, 这就导致 了F P G A工作 更有效率 。 2 . 2 F P G A管脚多, 容 易实现 大规模 系统 单片机 I O 口有 限, 而F P G A动辄数百 I O, 可 以方 便 连 接 外设 。比如一个系统有 多路 AD、 D A, 单片机要进行仔细的资 源分配 , 总线隔离, 而F P GA 由于 丰 富 的 1 0 资源 , 可 以很 容 易 用不 同 1 0连接各外设 。 2 - 3 F P G A有大量软核 , 可以方便 进行二 次开发 F P G A甚 至 包含 单 片机 和 DS P软核 , 并且 1 0数 仅 受 F P G A 自身 I O限制 , 所 以, F P G A又是单片机和 DS P的超 集, 也就是 说, 单片机和 DS P能实现的功能, F P GA一般 都能实现 。 3系 统 设 计 为了能够实现水声信号的 A / D、D / A转换 以及数字信号 的调制 、 解 调处理 , 本系统主要集成 了A/ D转换芯 片、 D / A转 换芯片和 F P GA芯片等, F P G A采用 E P 3 C1 0芯片 , A/ D转换 芯 片采 用 ADS 7 8 0 0 J U芯片, 而D / A转 换 芯 片为 T L V5 6 3 9芯 片, 另外还使用 了 L VT 2 4 5电平转换芯片, MA x2 3 2芯片等。

基于FPGA和SD卡的水声信号高速采集与存储系统设计

种模式数据传输速率最快;另~种是SPI模式,引脚

万方数据

210

电

子

器件

第32卷

口RAM交替进行数据的读写操作,一个RAM在

的wren和rden。512 byte的双端口RAM输入总 线配置为8位,采集来的数据data[-7..o]可以直接 写入RAM,输出总线配置为1位,这样在RAM中

进行写操作时,另一个RAM进行读操作。计数器

as

a

controller,SD card

as

as

memory,FPGA

as

high-speed interface between acquisition

and SD card,FAT file system

format of storage.This design has merits of small size,capability of

万方数据

第1期

张洪刚,苑秉成等:基于FPGA和SD卡的水声信号高速采集与存储系统设计

209

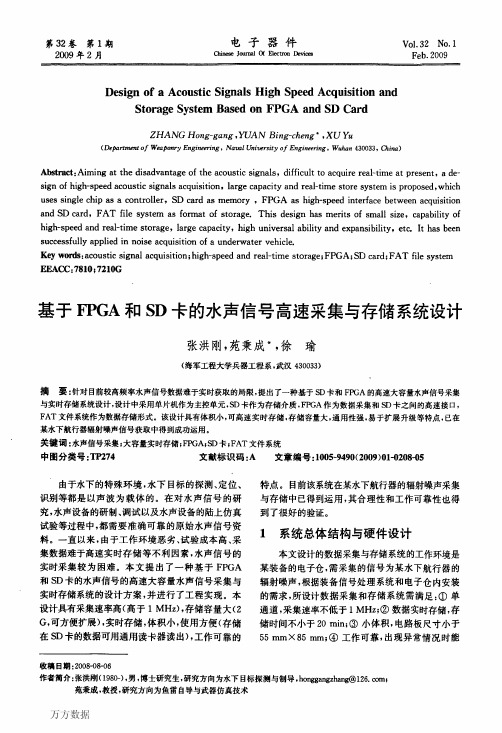

保证采集的有效数据不丢失。 系统的总体结构如图1所示,主要由A/D采集

连接关系如图2中所示,SPI模式也是只用一条数

据线传送数据,由于兼容SPI总线,在系统硬件和软

模块、FPGA接口模块、单片机、门限比较电路以及

第32卷第1期 2009年2月

电子器件

Chinese

v01.32

No.1

Jourmt Of

Electron

Devic8

Feb.2009

Design of

a

Acoustic Signals High Speed Acquisition and

on

Storage System Based

基于FPGA的信号采集与处理系统设计与实现

基于FPGA的信号采集与处理系统设计与实现一、本文概述随着电子技术的快速发展,信号采集与处理技术在众多领域,如通信、医疗、军事和航空航天等,都发挥着至关重要的作用。

现场可编程门阵列(FPGA)作为一种高性能、高灵活性的硬件平台,其在信号采集与处理领域的应用日益广泛。

本文旨在探讨基于FPGA的信号采集与处理系统的设计与实现,包括系统的硬件架构、软件设计、信号采集方法、处理算法以及优化策略等方面。

本文将首先介绍FPGA的基本原理、特性和在信号处理中的优势,然后阐述信号采集与处理系统的总体设计方案。

在硬件设计部分,将详细介绍FPGA的选择、外围电路的设计以及与其他硬件组件的接口设计。

在软件设计部分,将重点讨论信号采集模块、处理算法模块以及控制模块的实现方法。

接着,本文将深入探讨信号采集的关键技术,包括采样率的选择、抗混叠滤波器的设计以及模数转换器的选型等。

对于处理算法部分,将涉及数字信号处理的基础理论,如傅里叶变换、滤波器等,以及它们在FPGA上的实现方法。

还将讨论如何通过优化算法和硬件设计来提高系统的性能和实时性。

本文将通过具体的实验和测试来验证所设计的信号采集与处理系统的性能,并给出结论和展望。

本文旨在为读者提供一个全面、深入的基于FPGA的信号采集与处理系统设计与实现的参考指南,同时也希望为相关领域的研究和实践提供有益的借鉴和启示。

二、FPGA基础知识FPGA,全称为现场可编程门阵列(Field Programmable Gate Array),是一种半定制电路,它结合了通用处理器和专用集成电路(ASIC)的优点。

FPGA内部包含大量的可配置逻辑块(Configurable Logic Blocks, CLBs)、输入输出块(Input/Output Blocks, IOBs)和内部连线(Interconnect),这些资源可以通过编程实现各种不同的逻辑功能。

可配置逻辑块(CLBs):CLBs是FPGA的基本逻辑单元,可以配置为执行各种逻辑操作,如AND、OR、OR等,以及更复杂的组合逻辑和时序逻辑功能。

基于FPGA的音频信号处理系统设计与实现

基于FPGA的音频信号处理系统设计与实现随着科技的发展和音频技术的不断进步,音频信号处理系统被广泛应用于各个领域。

本文将介绍基于FPGA的音频信号处理系统的设计与实现,并探讨其中的原理和关键技术。

一、引言随着数字音频技术的快速发展,音频信号处理系统的需求日益增长。

传统的音频信号处理方法往往通过软件实现,但其实时性和处理能力受到了限制。

而基于FPGA的音频信号处理系统具有高速运算、低延迟和灵活性强等优势,逐渐成为热门研究方向。

二、FPGA的基本原理FPGA(Field Programmable Gate Array)是一种可编程逻辑器件,其内部由大量可编程的逻辑资源和存储器单元组成。

通过在FPGA上配置电路,可以实现各种不同的功能,包括音频信号处理。

三、音频信号处理系统的设计1. 模拟信号输入音频信号一般以模拟信号的形式输入到系统中,需要进行采样和模数转换。

采样率的选择应根据音频信号的特点和需求进行合理确定。

2. 数字信号处理在FPGA上设计并实现各种数字信号处理算法,如滤波、均衡、降噪等。

选择适合的算法和优化算法实现的技术,以提高系统的处理能力和性能。

3. 实时性要求由于音频信号的特性需保证处理系统的实时性。

FPGA的高并行性和硬件级别的实时性特点,使得其能够满足音频信号处理系统的实时性要求。

4. 数据存储与输出经过数字信号处理后的音频信号可以存储在FPGA内部的存储器中或外部的存储器中,也可以通过数字转模拟的方式输出到外部设备中。

四、关键技术与应用1. 快速算法优化为提高音频信号处理系统的处理速度,可以采用快速算法进行优化,如FFT(Fast Fourier Transform)等。

这些优化算法能够在保证处理结果准确性的前提下有效提高系统的运算速度。

2. 并行计算FPGA的并行计算能力是其强大的优势之一,可以将音频信号的处理任务进行拆分,同时进行多路处理,从而提高整个系统的处理能力。

3. 运算精度的选择在音频信号处理系统中,需要根据处理需求选择合适的运算精度。

基于FPGA的水声信号检测系统设计

基于FPGA的水声信号检测系统设计刘毅;程锦房;肖大为;何光进【摘要】An underwater acoustic signal detecting system is designed based on FPGA in which array signal processing and engineering MUSIC algorithm are used. It has some reference value for the designs of some sonar detection system.%结合阵列信号处理技术,应用工程化的MUSIC算法,本文设计了一套基于FPGA的水声信号检测系统,对某些声纳检测系统的设计有一定参考价值。

【期刊名称】《船电技术》【年(卷),期】2012(032)012【总页数】3页(P22-24)【关键词】MUSIC算法;低功耗;FPGA【作者】刘毅;程锦房;肖大为;何光进【作者单位】海军工程大学兵器工程系,武汉430033;海军工程大学兵器工程系,武汉430033;海军工程大学兵器工程系,武汉430033;海军工程大学兵器工程系,武汉430033【正文语种】中文【中图分类】TP2741 引言对于需要在水下长时间工作的声信号检测系统,通常采用电池供电,因而往往要求元器件具有较低功耗,以延长系统的运行时间。

在 FPGA芯片、DSP芯片、单片机中,FPGA芯片具有低功耗和高运算速度的特性,因而更适合用于水下系统。

MUSIC算法是一个可用于波达方向(DOA)估计的经典算法,其中包含一些不规则运算步骤,它们在FPGA中不易实现,鉴于此,本文将在基于FPGA系统中运用实用改进化的MUSIC算法判断水声信号源的方位。

2 FPGA简介现场可编程门阵列(Field-Programmable Gate Array, FPGA)是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物,具有更高的集成度、更强的逻辑实现能力和更好的设计灵活性[1]。

试析基于FPGA的水声信号记录电路设计

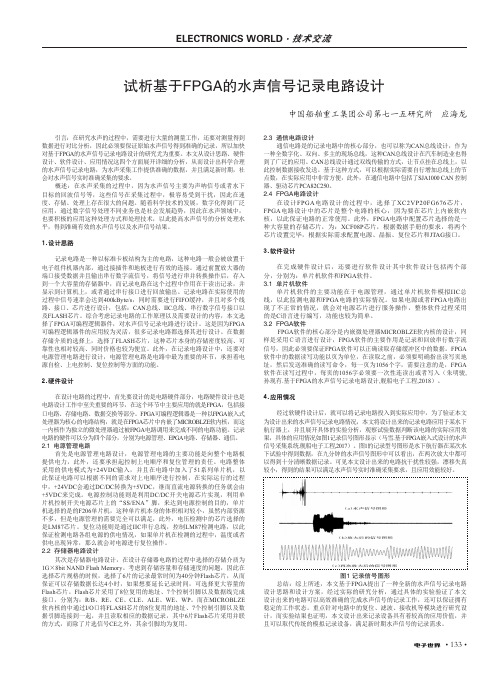

• 133•ELECTRONICS WORLD・技术交流试析基于FPGA的水声信号记录电路设计中国船舶重工集团公司第七一五研究所 应海龙引言:在研究水声的过程中,需要进行大量的测量工作,还要对测量得到数据进行对比分析,因此必须要保证原始水声信号得到准确的记录,所以加快对基于FPGA的水声信号记录电路设计的研究尤为重要。

本文从设计思路、硬件设计、软件设计、应用情况这四个方面展开详细的分析,从而设计出科学合理的水声信号记录电路,为水声采集工作提供准确的数据,并且满足新时期,社会对水声信号实时准确采集的要求。

概述:在水声采集的过程中,因为水声信号主要为声呐信号或者水下目标的回波信号等,这些信号在采集过程中,极容易受到干扰,因此在速度、存储、处理上存在很大的问题。

随着科学技术的发展,数字化得到广泛应用,通过数字信号处理不同业务也是社会发展趋势,因此在水声领域中,也要积极的应用这种处理方式和处理技术,以此提高水声信号的分析处理水平,得到准确有效的水声信号以及水声信号结果。

1.设计思路记录电路是一种以标准卡板结构为主的电路,这种电路一般会被放置于电子组件机器内部,通过接插件和地板进行有效的连接。

通过前置放大器的端口接受数据并且输出串行数字流信号,将信号进行串并转换操作后,存入到一个大容量的存储器中,而记录电路在这个过程中作用在于读出记录,并显示到计算机上,或者通过串行接口进行回放输出。

记录电路在实际使用的过程中信号速率会达到400kByte/s,同时需要进行FIFO缓冲,并且对多个线路、接口、芯片进行设计,包括:CAN总线、IIC总线、串行数字信号接口以及FLASH芯片。

综合考虑记录电路的工作原理以及需要设计的内容,本文选择了FPGA可编程逻辑器件,对水声信号记录电路进行设计。

这是因为FPGA 可编程逻辑器件的应用较为灵活,很多记录电路都选择其进行设计。

在数据存储介质的选择上,选择了FLASH芯片,这种芯片本身的存储密度较高、可靠性也相对较高、同时价格也较为便宜。

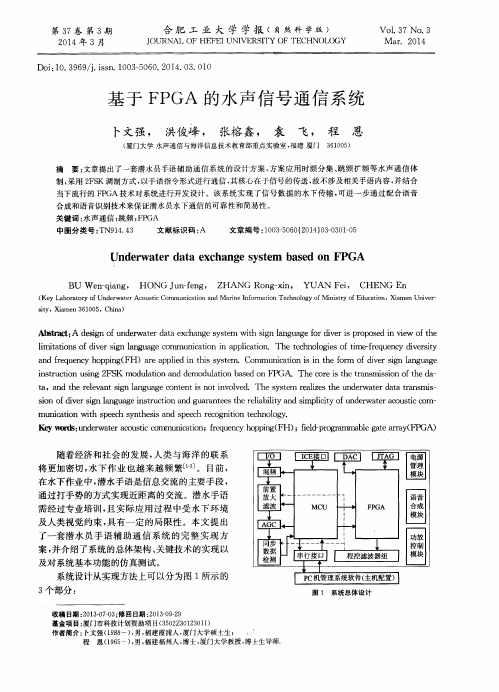

基于FPGA的水声信号通信系统

基于 F P G A 的水声信号通 信 系 统

卜文强 , 洪俊峰 , 张榕 鑫 , 袁 飞 , 程 恩

( 厦 门大学 水声通信与海洋信息技术教育部重点实验室 , 福建 厦 门 3 6 1 0 0 5 )

摘

要: 文章提 出了一套潜水员手语辅 助通 信系统 的设计 方案 , 方案应 用 时频分集 、 跳频 扩频等水 声通 信体

关键词 : 水声通信 ; 跳频 ; F P G A 中图分类号 : T N9 1 4 . 4 3 文献标识码 : A 文章编号 : 1 0 0 3 — 5 0 6 0 ( 2 0 1 4 ) 0 3 — 0 3 0 1 — 0 5

Un d e r wa t e r d a t a e x c h a n g e s y s t e m b a s e d o n FP GA

t a ,a n d t h e r e l e v a n t s i n g l a n g u a g e c o n t e n t i s n o t i n v o l v e d .Th e s y s t e m r e a l i z e s t h e u n d e r wa t e r d a t a t r a n s mi s — s i o n o f iv d e r s i n g l ng a u a g e i n s t r u c t i o n a n d g u a r a n t e e s t h e r e l i a b i l i t y a n d s i mp l i c i t y o f u n d e r wa t e r a c o u s t i c c o m— mu n i at c i o n it w h s p e e c h s y n t h e s i s a n d s p e e c h r e c o g n i t i o n t e c no h l o g y .

基于FPGA的水下多路数据采集存储系统

基于FPGA的水下多路数据采集存储系统喻鹏;肖大为;姬庆【摘要】设计了以FPGA器件SPARTAN-6系列为核心的多通道数据采集存储系统,通过FPGA对扩展AD和存储卡的工作时序控制,实现数据采集存储功能.该系统具有可靠性强,采集速度快,体积小,存储空间大和功耗较低的特点.【期刊名称】《船电技术》【年(卷),期】2016(036)010【总页数】3页(P58-60)【关键词】FPGA;数据采集;数据存储【作者】喻鹏;肖大为;姬庆【作者单位】海军工程大学,武汉430033;海军工程大学,武汉430033;海军工程大学,武汉430033【正文语种】中文【中图分类】TP273随着对海洋开发力度的加大,水下信号采集在军事、民用上需求越来越大。

相比于陆地上,水下数据采集存在着工作环境复杂,数据通讯困难的问题,所以一般均采用先采集存储后取出来进行数据分析的方法。

这对采集可靠性、采集工作时长、存储容量要求较高。

本系统初步设计具有6个采集通道,实现对声信号(声信号和声包络信号)、磁信号(磁信号分x、y、z三路)、水压信号的采集存储。

通过对声、磁、水压信号的提取不仅可以对水下目标的特征进行识别,同时也能够对目标方位进行判别,这对军用及民用探测领域都有一定的使用价值。

本系统工作效率高,能连续工作100 h,存储容量大(32G)、成本低,应用性强。

水下采集的信号首先经过信号调理模块进行处理,然后经过AD采样送入FPGA 中,经过数据处理后存储到存储器中。

与A/D芯片的接口采用FPGA,A/D的串行数据需要经过内部的FIR滤波器进行滤波后串行输出给FPGA,FPGA完成数据处理,存入FIFO(先进先出存储器),当数据存储量达到一定状态时,进行位校验运算,校验完成后将数据写入FLASH。

整体设计如下:FPGA选用的XILINX公司出品的SPARTAN-6系列的XC6SLX9芯片,它拥有144个管脚,接近100个可用管脚,含4个时钟倍频器。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

基于FPGA的水声信号采集与存储系统设计

摘要:为实现对水声信号的多通道同步采集并存储,提出了一种基于FPGA的多通道信号同步采集、高速大容量实时存储的系统设计方案,并完成系统的软硬件设计。

该系统的硬件部分采用模块化设计,通过FPGA丰富的外围接口实现模块间的数据交互,软件部分采用Verilog HDL硬件描述语言进行编程,能够灵活的实现信号的采集及存储。

实际应用表明,该设计具有功耗低,可高速实时存储,存储容量大,通用性强,易于扩展升级等特点。

水声信号采集存储系统是海洋环境调查仪器的重要组成部分。

开展水声环境调查所使用的海洋仪器要求设备通道多、同步性好、采样率高、数据存储容量大。

市场上常见的数据采集器多是采集某些固定种类的信号,动态范围比较小,通道数一般也比较少,有些还要求与主机进行接口等,这些都限制了其在水声信号采集中的应用。

为满足需要,本文设计了适合于水声数据采集存储的较为通用的系统,系统单板具有8个采集通道,多个单板级联可实现多通道同步采集、USB高速存储。

1 总体设计

该系统总体结构如图1所示,上级电路通过级联接口发送采集指令,单片机初始化控制FPGA,控制FPGA首先判断单板是否为级联单板,再初始化相应的FPGA。

采集模块的FPGA 向需要同步采集的通道对应的A/D芯片提供统一的时钟,使得A/D同步的选择相应的通道进行数据的同步采样和转换,其结果传给负责缓存的FPGA,缓存在DDR对应的存储空间,然后由ARM控制存储模块的FPGA从DDR空间读取数据进行本地存储。

2 系统硬件设计

系统硬件主要由控制模块、数据采集模块、缓存模块、存储模块几部分组成,系统硬件结构图如图2所示。

单片机功耗低、接口丰富、可靠性高,被系统用做上电引导芯片;FPGA 器件具有集成度高、内部资源丰富、特别适合处理多路并行数据等明显优于普通微处理器的特点,所以系统采用XILINX公司不同型号的FPGA作为不同模块的主控芯片。

针对系统设计中对采集存储实时性和同步性的要求,存储模块采用FPGA与ARM相结合的设计,采集主控制逻辑用ARM实现,FPGA负责数据的高速传输和存储。

控制模块相当于系统的值班电路,当系统作为从板工作时,只有控制模块和数据采集模块带电,其他模块关闭。

由于FPGA内核电压只有1.2 V,在这种情况下系统工作电流不大于1 A,低功耗的设计保证系统可在无人值守的情况下长时间连续进行采集存储工作。

系统需要多通道数据同时采集存储时,用户通过配置主板的控制模块参数设定8、16或32通道采集,主控FPGA通过级联接口发送统一的采集时钟到系统从板,从而实现系统多通道水声信号的同步采集及存储。

另外,通过单片机接口也可以随时监控系统工作状态,系统具有修复功能,采集存储过程中出现错误时,可根据用户配置自动进行相应的错误处理。

数据采集模块具有8路数据采集存储通道,每通道采用TI公司的24位高精度模数转换器ADS1258,A/D采用15.36 MHz的外部输入时钟。

设计中数字电源、模拟电源、参考电压单独布线,保证8通道信号隔离度几乎为零,降低了系统测量噪声。

模块中FPGA并行控制多路数据转换,包括转换启动、转换同步、转换停止、转换数据输出等。

数据缓存模块采用64M byte的DDR作为缓存,因为DDR在一个时钟周期内进行两次数据传输操作,它能够在时钟的上升沿和下降沿各传输一次数据,具有双倍的数据传输量,DDR 可以在与SDRAM相同的总线频率下达到更高的数据传输率。

缓存模块中的FPGA对DDR的数据写入和存储

模块中的FPGA对数据的读取是通过兵乓传输结构实现的。

当FPGA写满DDR上半区后,向存储模块申请中断,存储模块响应中断后,读出上半区数据到存储模块;同时FPGA向DDR 的下半区写数据,写满下半区后也向存储模块发出中断,通知存储模块读出下半区数据。

通过乒乓传输保证了系统数据采集和数据传输可连续进行。

数据存储模块的作用是将多通道24 bit数据经过缓存模块,按采样的时间顺序,以低字节到高字节的次序,依次将其写入电子硬盘。

系统采用IPD的iPD-USB型300G电子硬盘作为存储器。

由于它没有普通硬盘的旋转介质,因而抗震性极佳,同时工作温度很宽,可工作在-40~+85℃,再加上重量较硬盘轻很多,非常适用于水下声信号采集存储设备。

根据系统要求,采用USB底层芯片配合存储模块实现大容量高速USB存储,速度可达480Mbit/s,比全速USB存储快了40倍。

3 系统软件设计

程序设计采用Verilog HDL硬件描述语言,软件采用模块化设计,提高了程序的可移植性和可维护性。

系统的软件主要分为初始化模块、水声数据采集模块、数据缓存模块、数据存储模块、中断服务程序模块等构成。

初始化程序仅在系统复位及程序开始时执行一次,完成各模块主控芯片及外围电路的初始化;数据采集模块通过模拟量输入端口采集水声信号;

数据缓存模块负责将DDR中缓存的数据依次输出给存储模块;数据存储模块每分钟向电子硬盘中写入一个文件。

软件设计的流程图如图3所示。

4 试验应用

4.1 实验室测试结果

系统的性能测试是保证系统稳定,可靠工作的重要手段。

在实验室测试过程中,主要对系统的整体性能进行考察,其中包括:多通道采集同步误差、数据吞吐量、系统功耗、自噪声等。

测试结果如表1所示。

4. 2 海上试验结果

本系统应用的海洋环境噪声测量潜标在中国某海域进行了海上实验,系统连续工作3个月,性能稳定可靠,并获取了大量完整有效的海洋环境噪声数据。

测量的海洋环境噪声功率谱符合海洋环境噪声的自然分布规律。

实测海洋环境噪声功率谱如图4所示。

5 结论

本系统采用多FPGA相结合的设计,很好的完成了高速多通道数据采集与存储,并且详细介绍了FPGA各模块的设计方法。

本系统设计灵活,能很容易的扩展为多通道数据采集存储系统,也能很容易的修改为与其他的A/D转换芯片接口。

所以本系统可根据不同的应用进行扩展,进一步增强了系统在其他领域应用的灵活性。