MOS晶体管击穿特性研究

功率场效应晶体管(MOSFET)原理3

功率场效应晶体管(MOSFET)原理功率场效应管(Power MOSFET)也叫电力场效应晶体管,是一种单极型的电压控制器件,不但有自关断能力,而且有驱动功率小,开关速度高、无二次击穿、安全工作区宽等特点。

由于其易于驱动和开关频率可高达500kHz,特别适于高频化电力电子装置,如应用于DC/DC变换、开关电源、便携式电子设备、航空航天以及汽车等电子电器设备中。

但因为其电流、热容量小,耐压低,一般只适用于小功率电力电子装置。

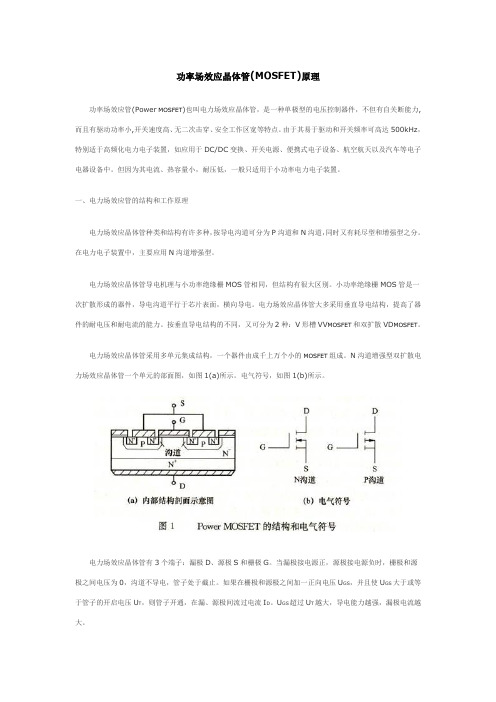

一、电力场效应管的结构和工作原理电力场效应晶体管种类和结构有许多种,按导电沟道可分为P沟道和N沟道,同时又有耗尽型和增强型之分。

在电力电子装置中,主要应用N沟道增强型。

电力场效应晶体管导电机理与小功率绝缘栅MOS管相同,但结构有很大区别。

小功率绝缘栅MOS管是一次扩散形成的器件,导电沟道平行于芯片表面,横向导电。

电力场效应晶体管大多采用垂直导电结构,提高了器件的耐电压和耐电流的能力。

按垂直导电结构的不同,又可分为2种:V形槽VV MOSFET和双扩散VD MOSFET。

电力场效应晶体管采用多单元集成结构,一个器件由成千上万个小的MOSFET组成。

N沟道增强型双扩散电力场效应晶体管一个单元的部面图,如图1(a)所示。

电气符号,如图1(b)所示。

电力场效应晶体管有3个端子:漏极D、源极S和栅极G。

当漏极接电源正,源极接电源负时,栅极和源极之间电压为0,沟道不导电,管子处于截止。

如果在栅极和源极之间加一正向电压U GS,并且使U GS大于或等于管子的开启电压U T,则管子开通,在漏、源极间流过电流I D。

U GS超过U T越大,导电能力越强,漏极电流越大。

二、电力场效应管的静态特性和主要参数Power MOSFET静态特性主要指输出特性和转移特性,与静态特性对应的主要参数有漏极击穿电压、漏极额定电压、漏极额定电流和栅极开启电压等。

{{分页}}1、静态特性(1)输出特性输出特性即是漏极的伏安特性。

功率场效应晶体管MOSFET特性试验研究及仿真 - 副本

3、纯电阻及阻感负载时,MOSFET开关特性的测试研究;

二、基本要求

1、学功率场效应晶体管MOSFET的有关参数的测定方法和工作原理,设计实验步骤,做线路搭接并进行实验研究。

2、实验数据整理、绘制曲线,对实验结果和理论结果进行对比分析。

3、使用MATLAB软件对各主电路进行仿真。

放大原理和主要参数辅以实验来化解和提高学习效率是研究场效应管行之有效的方法。但由于目前MOS场效应管的实验装置普遍存在弊端,即实验装置没有充分考虑到场效应管易损的因素,即实验者误操作、带电连接电路,造成实验中场效应管大量损坏,导致实验不能顺利完成,乃至正常开展。经调查,目前高校开展MOS场效应管测试实验的较少,无法深入甚至放弃。

场效应管是一种电压控制半导体器件,应用非常广泛。目前与我们的日常生活高度相关,如现代电子计算机、超大规模成电路、数码相机、开关电源、控制电路、液晶电视、数码音响、热释电传感器等就是以场效应管为基本器件构成和发展起来的。

MOS场效应管由于特殊的结构和工艺,其栅极与导电沟道没有电接触,即绝缘的,故它的输入电阻很高,可达109Ω以上,工作时几乎栅极不取电流,又栅-源极间电容非常小,极易受外界电磁场或静电的感应而带电,而少量电荷就可在极间电容上形成相当高的电压(U=Q/C),将管子损坏。通俗地说,MOS场效应管比较“娇气”。因此MOS场效应管出厂时各管脚都绞合在一起,或装在金属箔内,使G极与S极呈等电位,防止积累静电荷。管子不用时,全部引线也应短接。在测量时应格外小心,并采取相应的防静电感措施。

1、当需要进入实验室做毕设实验研究时,一定要遵守实验室学生守则。

2、不准在实验室内吸烟,喧哗、打闹等。不准在实验室内吃零食。

3、要爱护设备、仪器、仪表,轻拿轻放。旋钮使用不要用力过猛,防止机械性损坏;不要超量程扭动,以确保仪器、仪表等的完好和安全使用。

MOS晶体管击穿特性研究

微电子器件课程设计MOS晶体管击穿特性研究班级:微电子0901学号:******姓名:***指导老师:****日期:2012.5.20一、目的研究MOSFET漏源极击穿特性,主要包括:1.验证掺杂浓度对MOSFET漏源极雪崩击穿的影响2.验证栅氧化层厚度对MOSFET漏源极雪崩击穿的影响3.介绍源漏穿通穿通二、工作原理当V DS增大到漏源击穿电压BV DS的值时,反向偏置的漏PN结会因雪崩倍增效应而发生击穿,或在漏区与源区之间发生穿通。

这时I D将迅速上升,如图所示。

通过改变衬底掺杂浓度和栅氧化层厚度,可改变穿电压BVDS的值得到不同的输出特性曲线三、仿真过程首先构建NMOS结构源代码如下:go athena# 网格定义(创建非均匀网格)# Non-Uniform Grid(0.6um x 0.8um)line x loc=0.00 spac=0.10line x loc=0.20 spac=0.01line x loc=0.60 spac=0.01#line y loc=0.00 spac=0.008line y loc=0.2 spac=0.01line y loc=0.5 spac=0.05line y loc=0.8 spac=0.15#初始衬底参数:浓度、晶向等(浓度1.0e14/cm2晶向100方向)# Initial Silicon Structure with <100> Orientationinit silicon c.boron=1.0e16 orientation=100 two.d# 栅极氧化及优化(使氧化层厚度约为100A)# Gate Oxidationdiffus time=11 temp=925.727 dryo2 press=0.982979 hcl.pc=3# 提取栅极厚度#extract name="Gateoxide" thickness material="SiO~2" mat.occno=1 x.val=0.3# 阈值电压调整注入(注入9.5e11/cm2的)# Threshold Voltage Adjust implantimplant boron dose=9.5e11 energy=10 crystal# 多晶硅淀积# Conformal Polysilicon Depositiondeposit polysilicon thick=0.20 divisions=10# 多晶硅刻蚀# Poly Definitionetch polysilicon left p1.x=0.35# 多晶硅氧化# Polysilicon Oxidationmethod fermi compressdiffus time=3 temp=900 weto2 press=1.00# 多晶硅参杂# Polysilicon Dopingimplant phosphor dose=3e13 energy=20 crystal# 隔离氧化层淀积# Spacer Oxide depositiondeposit oxide thick=0.12 divisions=10# 侧墙氧化隔离层的形成etch oxide dry thick=0.12# Source/Drain Implant# 源漏注入implant arsenic dose=5e15 energy=50 crystal# 源漏退火method fermidiffus time=1 temp=900 nitro press=1.00# 刻蚀通孔# Open Contact Windowetch oxide left p1.x=0.2# 铝淀积# Aluminum Depositiondeposit aluminum thick=0.03 divisions=2# 刻蚀铝电极# Etch Aluminumetch aluminum right p1.x=0.18#计算结深extract name="nxj" xj material="Silicon" mat.occno=1 x.val=0.2 junc.occno=1 #获得N++源漏极方块电阻extract name="n++ sheet res" sheet.res material="Silicon" mat.occno=1 \x.val=0.05 region.occno=1#测量LDD方块电阻extract name="ldd sheet res" sheet.res material="Silicon" mat.occno=1 \x.val=0.3 region.occno=1#测量长沟倒阈值电压extract name="1dvt" 1dvt ntype qss=1e10 x.val=0.5#结构镜像struct mirror right#定义电极electrode name=source x=0.1#electrode name=drain x=1.1#electrode name=gate x=0.6#electrode name=backside backside#struct outfile=nmos1.str生成结构后,进行仿真源代码如下:go atlas##调用结构文件mesh infile=nmos.str##指定接触面特性contact name=gate n.polysiliconinterf qf=3E10# Set modelsmodels print cvt consrh#用于击穿分析的雪崩碰撞电离模型impact selbmethod newton trap climit=1e-4 #注①## open log filelog outf=mos1.logsolve vdrain=0.025solve vdrain=0.05solve vdrain=0.1solve vdrain=0.5solve vstep=0.25 vfinal=12 name=drain compl=1e-7 cname=drain #注②#save outf=mos1_1.str#extract name="NVbd" x.val from curve(abs(v."drain"),abs(i."drain")) where y.val=1e-9tonyplot mos1.log -set mos1_log.settonyplot mos1_1.str -set mos1_1.setquit四、结果与讨论首先,对衬底掺杂浓度对击穿电压的影响进行了研究,将init silicon c.boron=1.0e16 orientation=100 two.d 语句中的浓度参数进行了调整分别使c.boron=1.0e15 和c.boron=1.0e17经过仿真可得到一组图像:c.boron=1.0e15 c.boron=1.0e16 c.boron=1.0e171e151e161e17而后研究了栅氧厚度对击穿电压的影响,栅氧厚度可通过Optimizer选项修改,通过优化过程,将扩散过程语句diffus time=11 temp=925.727 dryo2 press=0.982979 hcl.pc=3分别改为diffus time=11 temp=985.969 dryo2 press=1.12818 hcl.pc=3 和diffus time=11 temp=865.817 dryo2press=0.944327 hcl.pc=3 得到了氧化层厚度200Å和50Å,并得到击穿特性如图:100Å 200Å 50Å50 Å100Å200 Å五、总结此次验证的是MOSFET漏源极击穿特性,当源极与衬底相连时,漏源电压VDS对漏PN结是反向电压。

MOS管被击穿的原因及解决方案(全)

MOS管被击穿的原因及解决方案(转)而MOS管被击穿的原因及解决方案如下:第一、MOS管本身的输入电阻很高,而栅-源极间电容又非常小,所以极易受外界电磁场或静电的感应而带电,而少量电荷就可在极间电容上形成相当高的电压(U=Q/C),将管子损坏。

虽然MOS输入端有抗静电的保护措施,但仍需小心对待,在存储和运输中最好用金属容器或者导电材料包装,不要放在易产生静电高压的化工材料或化纤织物中。

组装、调试时,工具、仪表、工作台等均应良好接地。

要防止操作人员的静电干扰造成的损坏,如不宜穿尼龙、化纤衣服,手或工具在接触集成块前最好先接一下地。

对器件引线矫直弯曲或人工焊接时,使用的设备必须良好接地。

第二、MOS电路输入端的保护二极管,其导通时电流容限一般为1mA在可能出现过大瞬态输入电流(超过10mA)时,应串接输入保护电阻。

而129#在初期设计时没有加入保护电阻,所以这也是MOS管可能击穿的原因,而通过更换一个内部有保护电阻的MOS管应可防止此种失效的发生。

还有由于保护电路吸收的瞬间能量有限,太大的瞬间信号和过高的静电电压将使保护电路失去作用。

所以焊接时电烙铁必须可靠接地,以防漏电击穿器件输入端,一般使用时,可断电后利用电烙铁的余热进行焊接,并先焊其接地管脚。

附录:静电的基本物理特征为:有吸引或排斥的力量;有电场存在,与大地有电位差;会产生放电电流。

这三种情形会对电子元件造成以下影响:1.元件吸附灰尘,改变线路间的阻抗,影响元件的功能和寿命。

2.因电场或电流破坏元件绝缘层和导体,使元件不能工作(完全破坏)。

3.因瞬间的电场软击穿或电流产生过热,使元件受伤,虽然仍能工作,但是寿命受损。

上述这三种情况中,如果元件完全破坏,必能在生产及品质测试中被察觉而排除,影响较少。

如果元件轻微受损,在正常测试中不易被发现,在这种情形下,常会因经过多次加工,甚至已在使用时,才被发现破坏,不但检查不易,而且损失亦难以预测。

静电对电子元件产生的危害不亚于严重火灾和爆炸事故的损失电子元件及产品在什么情况下会遭受静电破坏呢?可以这么说:电子产品从生产到使用的全过程都遭受静电破坏的威胁。

mos管击穿原理

mos管击穿原理引言:MOS管(Metal-Oxide-Semiconductor Field-Effect Transistor)是一种常见的场效应晶体管,被广泛应用于各种电子设备中。

然而,MOS管在特定条件下可能会遭受击穿现象,从而导致设备故障或损坏。

本文将详细介绍MOS管击穿原理及其影响因素,并探讨如何避免击穿现象的发生。

一、MOS管的基本结构MOS管由金属栅极、氧化物层和半导体基底构成。

金属栅极位于氧化物层之上,而氧化物层又位于半导体基底之上。

这种结构使得MOS管能够通过调节栅极电压来控制电流的流动,从而实现信号放大或开关控制的功能。

二、MOS管的击穿现象MOS管的击穿现象指的是在一定条件下,栅极和基底之间的电压超过一定阈值,使得电流大幅度增加,导致器件失效。

根据击穿的具体表现形式,可以将MOS管的击穿分为以下几种类型:1. 雪崩击穿:雪崩击穿是指当栅极和基底之间的电压超过阈值时,迁移率较高的电子或空穴在电场的作用下,获得足够的能量,与原子碰撞后产生新的电子空穴对。

这些新的电子空穴对继续获得能量并与其他原子碰撞,形成一系列的电子空穴对,导致电流急剧增加。

2. 倒向击穿:倒向击穿是指当栅极和基底之间的电压过大时,使得半导体材料中的载流子被强电场加速,从而导致电流增加。

倒向击穿主要发生在栅极电压为负值时。

3. 隧穿击穿:隧穿击穿是指当栅极和基底之间的电压过大,电场足够强时,电子能够跨越禁带宽度,通过氧化物层隧穿到达基底区域,形成电流增加的现象。

三、影响MOS管击穿的因素MOS管的击穿与多种因素有关,下面将介绍几个主要的影响因素:1. 栅极电压:栅极电压是影响MOS管击穿的关键因素。

当栅极电压超过一定阈值时,击穿现象就会发生。

因此,在设计电路时,需要合理控制栅极电压,以避免击穿的发生。

2. 环境温度:环境温度对MOS管的击穿特性有一定影响。

一般情况下,当环境温度升高时,击穿电压会有所降低。

因此,在高温环境下使用MOS管时,需要注意其耐压能力。

场效应晶体管参数测量的实验报告(共9篇)

场效应晶体管参数测量的实验报告(共9篇)实验2、场效应晶体管参数测量实验二场效应晶体管特性的测量与分析一前言场效应晶体管不同于一般的双极晶体管。

场效应晶体管是一种电压控制器件。

从工作原理看,场效应晶体管与电子管很相似,是通过改变垂直于导电沟道的电场强度去控制沟道的导电能力,因而称为“场效应”晶体管。

场效应晶体管的工作电流是半导体中的多数载流子的漂移流,参与导电的只有一种载流子,故又称“单极型”晶体管。

通常用“FET”表示。

场效应晶体管分为结型场效应管(JFET)和绝缘栅型场效应管(MISFET)两大类。

目前多数绝缘栅型场效应应为金属-氧化物-半导体(MOS)三层结构,缩写为MOSFET。

本实验对结型、MOS型场效应管的直流参数进行检测。

场效应管按导电沟道和工作类型可分为:???耗尽型??n沟????增强型MOSFET???耗尽型?? FET?p沟??增强型?????JFET?n沟?耗尽型???p沟???检测场效应管特性,可采用单项参数测试仪或综合参数测试仪。

同时,场效应管与双极管有许多相似之处,故通常亦采用XJ4810半导体管图示仪检测其直流参数。

本实验目的是通过利用XJ4810半导体管图示仪检测场效应管的直流参数,了解场效应管的工作原理及其与双极晶体管的区别。

二实验原理1. 实验仪器实验仪器为XJ4810图示仪,与测量双极晶体管直流参数相似,但由于所检测的场效应管是电压控制器件,测量中须将输入的基极电流改换为基极电压,这可将基极阶梯选择选用电压档(伏/级);也可选用电流档(毫安/级),但选用电流档必须在测试台的B-E间外接一个电阻,将输入电流转换成输入电压。

测量时将场效应管的管脚与双极管脚一一对应,即G(栅极)? B(基极);S(源极)? E(发射极);D(漏极)? C(集电极)。

值得注意的是,测量MOS管时,若没有外接电阻,必须避免阶梯选择直接采用电流档,以防止损坏管子。

另外,由于场效应管输入阻抗很高,在栅极上感应出来的电荷很难通过输入电阻泄漏掉,电荷积累会造成电位升高。

4HSiC埋沟MOSFET击穿特性模拟研究

西安电子科技大学硕士学位论文4H-SiC埋沟MOSFET击穿特性模拟研究姓名:夏杰申请学位级别:硕士专业:微电子学与固体电子学指导教师:张义门20060101摘要碳化硅材料有着包括禁带宽、击穿电场大、电子饱和漂移速度快等等物理性质方面的优势,这决定了碳化硅材料在高温、高频、高辐射等这些相对极端的环境下发挥重要的作用。

同时,埋沟MOSFET(在SiO2/SiC界面注入一层N型掺杂层)的出现很好地避免了SiC/SiO2界面对载流子输运的影响。

为了更好地发挥碳化硅埋沟MOSFET在功率性能的优势和潜力,必须对器件的电学击穿特性进行较为深入的模拟研究。

本文的主要工作有:研究了4H-SiC埋沟MOSFET的基本结构模型及其参数,其中主要包括迁移率模型及其参数、不完全电离模型和碰撞离化模型,验证了器件的工作机理,讨论了器件的基本特性,验证了埋沟MOSFET相对传统MOSFET的优势;研究了4H-SiC埋沟MOSFET的高温特性。

为接下来讨论4H-SiC埋沟MOSFET的击穿特性奠定了基础。

为正确地模拟4H-SiC埋沟MOSFET的击穿特性,合理地设置了器件的深度和漏区的宽度。

介绍了4H-SiC埋沟MOSFET的基本击穿机理;比较了埋沟和传统MOSFET的击穿特性,埋沟器件的击穿电压大说明了它在高压器件方面具有一定的优势;讨论了4H-SiC埋沟MOSFET的各个结构参数对器件击穿特性的影响,包括埋沟沟道掺杂浓度、沟道深度、衬底掺杂浓度、氧化层厚度、场板等;最后,介绍了环境温度对器件击穿特性的影响等。

结果表明:4H-SiC埋沟MOSFET击穿电压随着栅压、沟道掺杂浓度、埋沟深度、氧化层厚度增大而增大;随着衬底掺杂浓度增大而减小;随着场板的出现而增大;另外,击穿电压随着温度的升高而增大。

这将对4H-SiC埋沟MOSFET在今后研究中起到指导作用。

介绍了4H-SiC埋沟MOSFET研制的最新实验情况。

实验测试表明所有器件的阈值电压都为正,说明器件都是增强型的;器件I-V特性都具有较好的线性区和饱和区;最高的有效迁移率约为90cm2/Vs。

半导体器件物理施敏答案

半导体器件物理施敏答案【篇一:施敏院士北京交通大学讲学】t>——《半导体器件物理》施敏 s.m.sze,男,美国籍,1936年出生。

台湾交通大学电子工程学系毫微米元件实验室教授,美国工程院院士,台湾中研院院士,中国工程院外籍院士,三次获诺贝尔奖提名。

学历:美国史坦福大学电机系博士(1963),美国华盛顿大学电机系硕士(1960),台湾大学电机系学士(1957)。

经历:美国贝尔实验室研究(1963-1989),交通大学电子工程系教授(1990-),交通大学电子与资讯研究中心主任(1990-1996),国科会国家毫微米元件实验室主任(1998-),中山学术奖(1969),ieee j.j.ebers奖(1993),美国国家工程院院士(1995), 中国工程院外籍院士 (1998)。

现崩溃电压与能隙的关系,建立了微电子元件最高电场的指标等。

施敏院士在微电子科学技术方面的著作举世闻名,对半导体元件的发展和人才培养方面作出了重要贡献。

他的三本专著已在我国翻译出版,其中《physics of semiconductor devices》已翻译成六国文字,发行量逾百万册;他的著作广泛用作教科书与参考书。

由于他在微电子器件及在人才培养方面的杰出成就,1991年他得到了ieee 电子器件的最高荣誉奖(ebers奖),称他在电子元件领域做出了基础性及前瞻性贡献。

施敏院士多次来国内讲学,参加我国微电子器件研讨会;他对台湾微电子产业的发展,曾提出过有份量的建议。

主要论著:1. physics of semiconductor devices, 812 pages, wiley interscience, new york, 1969.2. physics of semiconductor devices, 2nd ed., 868 pages, wiley interscience, new york,1981.3. semiconductor devices: physics and technology, 523 pages, wiley, new york, 1985.4. semiconductor devices: physics and technology, 2nd ed., 564 pages, wiley, new york,2002.5. fundamentals of semiconductor fabrication, with g. may,305 pages, wiley, new york,20036. semiconductor devices: pioneering papers, 1003 pages, world scientific, singapore,1991.7. semiconductor sensors, 550 pages, wiley interscience, new york, 1994.8. ulsi technology, with c.y. chang,726 pages, mcgraw hill, new york, 1996.9. modern semiconductor device physics, 555 pages, wiley interscience, new york, 1998. 10. ulsi devices, with c.y. chang, 729 pages, wiley interscience, new york, 2000.课程内容及参考书:施敏教授此次来北京交通大学讲学的主要内容为《physics ofsemiconductor device》中的一、四、六章内容,具体内容如下:chapter 1: physics and properties of semiconductors1.1 introduction 1.2 crystal structure1.3 energy bands and energy gap1.4 carrier concentration at thermal equilibrium 1.5 carrier-transport phenomena1.6 phonon, optical, and thermal properties 1.7 heterojunctions and nanostructures 1.8 basic equations and exampleschapter 4: metal-insulator-semiconductor capacitors4.1 introduction4.2 ideal mis capacitor 4.3 silicon mos capacitorchapter 6: mosfets6.1 introduction6.2 basic device characteristics6.3 nonuniform doping and buried-channel device 6.4 device scaling and short-channel effects 6.5 mosfet structures 6.6 circuit applications6.7 nonvolatile memory devices 6.8 single-electron transistor iedm,iscc, symp. vlsi tech.等学术会议和期刊上的关于器件方面的最新文章教材:? s.m.sze, kwok k.ng《physics of semiconductordevice》,third edition参考书:? 半导体器件物理(第3版)(国外名校最新教材精选)(physics of semiconductordevices) 作者:(美国)(s.m.sze)施敏 (美国)(kwok k.ng)伍国珏译者:耿莉张瑞智施敏老师半导体器件物理课程时间安排半导体器件物理课程为期三周,每周六学时,上课时间和安排见课程表:北京交通大学联系人:李修函手机:138******** 邮件:lixiuhan@案2013~2014学年第一学期院系名称:电子信息工程学院课程名称:微电子器件基础教学时数: 48授课班级: 111092a,111092b主讲教师:徐荣辉三江学院教案编写规范教案是教师在钻研教材、了解学生、设计教学法等前期工作的基础上,经过周密策划而编制的关于课程教学活动的具体实施方案。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

微电子器件课程设计MOS晶体管击穿特性研究班级:微电子0901学号:******姓名:***指导老师:****日期:2012.5.20一、目的研究MOSFET漏源极击穿特性,主要包括:1.验证掺杂浓度对MOSFET漏源极雪崩击穿的影响2.验证栅氧化层厚度对MOSFET漏源极雪崩击穿的影响3.介绍源漏穿通穿通二、工作原理当V DS增大到漏源击穿电压BV DS的值时,反向偏置的漏PN结会因雪崩倍增效应而发生击穿,或在漏区与源区之间发生穿通。

这时I D将迅速上升,如图所示。

通过改变衬底掺杂浓度和栅氧化层厚度,可改变穿电压BVDS的值得到不同的输出特性曲线三、仿真过程首先构建NMOS结构源代码如下:go athena# 网格定义(创建非均匀网格)# Non-Uniform Grid(0.6um x 0.8um)line x loc=0.00 spac=0.10line x loc=0.20 spac=0.01line x loc=0.60 spac=0.01#line y loc=0.00 spac=0.008line y loc=0.2 spac=0.01line y loc=0.5 spac=0.05line y loc=0.8 spac=0.15#初始衬底参数:浓度、晶向等(浓度1.0e14/cm2晶向100方向)# Initial Silicon Structure with <100> Orientationinit silicon c.boron=1.0e16 orientation=100 two.d# 栅极氧化及优化(使氧化层厚度约为100A)# Gate Oxidationdiffus time=11 temp=925.727 dryo2 press=0.982979 hcl.pc=3# 提取栅极厚度#extract name="Gateoxide" thickness material="SiO~2" mat.occno=1 x.val=0.3# 阈值电压调整注入(注入9.5e11/cm2的)# Threshold Voltage Adjust implantimplant boron dose=9.5e11 energy=10 crystal# 多晶硅淀积# Conformal Polysilicon Depositiondeposit polysilicon thick=0.20 divisions=10# 多晶硅刻蚀# Poly Definitionetch polysilicon left p1.x=0.35# 多晶硅氧化# Polysilicon Oxidationmethod fermi compressdiffus time=3 temp=900 weto2 press=1.00# 多晶硅参杂# Polysilicon Dopingimplant phosphor dose=3e13 energy=20 crystal# 隔离氧化层淀积# Spacer Oxide depositiondeposit oxide thick=0.12 divisions=10# 侧墙氧化隔离层的形成etch oxide dry thick=0.12# Source/Drain Implant# 源漏注入implant arsenic dose=5e15 energy=50 crystal# 源漏退火method fermidiffus time=1 temp=900 nitro press=1.00# 刻蚀通孔# Open Contact Windowetch oxide left p1.x=0.2# 铝淀积# Aluminum Depositiondeposit aluminum thick=0.03 divisions=2# 刻蚀铝电极# Etch Aluminumetch aluminum right p1.x=0.18#计算结深extract name="nxj" xj material="Silicon" mat.occno=1 x.val=0.2 junc.occno=1 #获得N++源漏极方块电阻extract name="n++ sheet res" sheet.res material="Silicon" mat.occno=1 \x.val=0.05 region.occno=1#测量LDD方块电阻extract name="ldd sheet res" sheet.res material="Silicon" mat.occno=1 \x.val=0.3 region.occno=1#测量长沟倒阈值电压extract name="1dvt" 1dvt ntype qss=1e10 x.val=0.5#结构镜像struct mirror right#定义电极electrode name=source x=0.1#electrode name=drain x=1.1#electrode name=gate x=0.6#electrode name=backside backside#struct outfile=nmos1.str生成结构后,进行仿真源代码如下:go atlas##调用结构文件mesh infile=nmos.str##指定接触面特性contact name=gate n.polysiliconinterf qf=3E10# Set modelsmodels print cvt consrh#用于击穿分析的雪崩碰撞电离模型impact selbmethod newton trap climit=1e-4 #注①## open log filelog outf=mos1.logsolve vdrain=0.025solve vdrain=0.05solve vdrain=0.1solve vdrain=0.5solve vstep=0.25 vfinal=12 name=drain compl=1e-7 cname=drain #注②#save outf=mos1_1.str#extract name="NVbd" x.val from curve(abs(v."drain"),abs(i."drain")) where y.val=1e-9tonyplot mos1.log -set mos1_log.settonyplot mos1_1.str -set mos1_1.setquit四、结果与讨论首先,对衬底掺杂浓度对击穿电压的影响进行了研究,将init silicon c.boron=1.0e16 orientation=100 two.d 语句中的浓度参数进行了调整分别使c.boron=1.0e15 和c.boron=1.0e17经过仿真可得到一组图像:c.boron=1.0e15 c.boron=1.0e16 c.boron=1.0e171e151e161e17而后研究了栅氧厚度对击穿电压的影响,栅氧厚度可通过Optimizer选项修改,通过优化过程,将扩散过程语句diffus time=11 temp=925.727 dryo2 press=0.982979 hcl.pc=3分别改为diffus time=11 temp=985.969 dryo2 press=1.12818 hcl.pc=3 和diffus time=11 temp=865.817 dryo2press=0.944327 hcl.pc=3 得到了氧化层厚度200Å和50Å,并得到击穿特性如图:100Å 200Å 50Å50 Å100Å200 Å五、总结此次验证的是MOSFET漏源极击穿特性,当源极与衬底相连时,漏源电压VDS对漏PN结是反向电压。

当V DS增加到一定程度时漏PN结就会发生雪崩击穿。

雪崩击穿电压的大小由衬底掺杂浓度和结深决定。

当衬底的电阻率大于1Ω·cm时,BVDS就不再与衬底材料的掺杂浓度有关,而主要右栅极电压的特性、大小和栅氧化层的厚度决定。

源漏穿通如果MOSFET的沟道长度较短而衬底电阻率较高,则当V DS增加某一数值时,虽然漏区与衬底间尚未发生雪崩击穿,但漏PN结的耗尽区却已经扩展到与源区相连接了,这种现象称为漏源穿通。

发生漏源穿通后,如果V DS继续增加,源PN结上会出现正偏,使电子从源区注入沟道。

这些电子将被耗尽层区内的强电场扫入漏区,从而产生较大的漏极电流。

使漏源两区发生穿通的漏源电压称为穿通电压,记为V pT。

沟道长度越短,衬底电阻率越高,穿通电压就越低。

源漏击穿电压是由漏PN结雪崩击穿电压和穿通电压两者中的较小者决定的。

源漏穿通限制了MOSFET的沟道长度不能太短,否则会使BV DS降得太低。

因此在设计MOSFET时必须对漏源穿通现象予以足够的重视。

注①:由于预击穿漏电流非常低,有必要收紧对当前的收敛公差。

参数设置方法climit = 1E-4网格注②:设置漏一个遵守5.0e-7A/um限制(此处使用1e-7,有的使用了1e-10,根据需要设置)。

一旦崩溃点到达,遵守限制击穿模拟停止模拟。

这是一个计算时间的问题。

通常是不值得的CPU花费时间。

因为自己在仿真时使用软件要计算很久,参考资料获得限制方法。