高速高精度DAC关键性能测试方法研究

高性能sigma-deltaADC的设计与研究

西安电子科技大学博士学位论文高性能sigma-delta ADC的设计与研究姓名:***申请学位级别:博士专业:微电子学与固体电子学指导教师:***20100401摘要i摘要高性能的模数转换器是当今微电子模拟领域研究的热点之一。

基于过采样技术和sigma-delta调制机制的模数转换器(Analog to Digital Converter,ADC)广泛使用在数字音频、综合业务数字网(Integrated Services Digital Network,ISDN)、数字电话等系统中。

这种高精度的模数转换器,通过采用过采样技术,增加调制器系统的信噪比,提高其实现的精度;通过使用sigma-delta噪声整形技术,降低了信号带内的量化噪声功率。

sigma-delta ADC由模拟调制器和数字抽取滤波器组成,而模拟调制器的噪声整形性能决定了整个转换器系统的精度。

本文首先对sigma-delta ADC的系统设计进行了深入的研究,采用MATLAB软件进行系统建模和仿真,并由此总结了一套完整的系统设计方法。

根据过采样率、精度和动态性能的要求,得出调制器所需的阶数以及前馈因子、反馈因子和积分器增益因子等参数。

然后再通过MATLAB系统仿真,预测出实际调制器可以达到的性能。

在模拟调制器的设计中,各种非理想因素会极大地影响模拟调制器的性能。

因此,对各种非理想因素进行系统的、量化的分析是必要的。

本文对各种非理想因素,如运放有限直流增益、有限带宽和摆率、输出摆幅限制、开关非线性,时钟抖动、采样电容kT/C噪声等都进行了量化分析,从而为随后的电路设计提供了设计依据。

sigma-delta ADC的结构主要分为单环(Single-Loop)结构和级联结构(Multi-stAge-noise-SHaping,MASH)两种,这两种结构具有各自的优缺点。

针对这两种结构,本文分别设计了一个高阶单环一位结构的sigma-delta ADC和一个级联多位(MASH24b-24b)结构的sigma-delta ADC。

L-DACS1系统关键技术研究与USRP实现

L-DACS1系统关键技术探究与USRP实现专业品质权威编制人:______________审核人:______________审批人:______________编制单位:____________编制时间:____________序言下载提示:该文档是本团队精心编制而成,期望大家下载或复制使用后,能够解决实际问题。

文档全文可编辑,以便您下载后可定制修改,请依据实际需要进行调整和使用,感谢!同时,本团队为大家提供各种类型的经典资料,如办公资料、职场资料、生活资料、进修资料、教室资料、阅读资料、知识资料、党建资料、教育资料、其他资料等等,想进修、参考、使用不同格式和写法的资料,敬请关注!Download tips: This document is carefully compiled by this editor. I hope that after you download it, it can help you solve practical problems. The document can be customized and modified after downloading, please adjust and use it according to actual needs, thank you!And, this store provides various types of classic materials for everyone, such as office materials, workplace materials, lifestyle materials, learning materials, classroom materials, reading materials, knowledge materials, party building materials, educational materials, other materials, etc. If you want to learn about different data formats and writing methods, please pay attention!L-DACS1系统关键技术探究与USRP实现L-DACS1系统关键技术探究与USRP实现随着航空交通的持续进步和航空器数量的快速增加,传统的航空通信技术面临着越来越大的挑战。

高速高分辨率ADC有效位测试方法研究

作为连接模拟世界和数字世界的桥梁,ADC的性能影响整个系统的性能。如何对ADC进行性能测试是目前ADC研究的热门领域之一。表征ADC的性能参数分为静态性能参数和动态性能参数。静态性能参数描述ADC的内在特性,主要关注稳定模拟输入与对应数字输出的关系;动态性能参数描述的是ADC采样和重现时序变化信号的能力。用于定量表示ADC动态性能的常用参数有6个,分别是:SINAD(信纳比)、ENOB(有效位数)、SNR(信噪比)、THD(总谐波失真)、THD+N(总谐波失真加噪声)和SFDR(无杂散动态范围)等。在这些动态性能参数中,ENOB是表征ADC的动态性能的重要参数,ADC自身及外部电路产生的噪声和谐波等都可以在该参数中得到反映。 测试ADC性能参数的方法主要有模拟方法和数字方法两种。模拟方法是将ADC得到的采样数据经DAC转换为模拟信号,再使用传统的方法进行测试,该方法引入了DAC的噪声和谐波,因此会影响ADC性能指标;数字方法主要有直方图法、正弦波拟合法和FFT法等[1],直方图法测试ADC的等效输入噪声等性能参数,正弦波拟合法对ADC的动态性能给出总体描述,FFT方法测试ADC动态性能参数。直方图法和正弦波拟合法引入了信号源的噪声和谐波等外围电路干扰,并且测试的性能参数单一,相比之下,FFT方法可以抑制甚至消除外围电路影响,获得的动态性能参数也较多[2]。本文重点讨论如何采用FFT方法对ADC的ENOB进行测试。 可以看到,相干采样对信号源的频率分辨率和稳定性要求很高。在实际操作时,信号源无法满足条件,需要对采样数据进行加窗函数处理以减少频谱泄漏。 加窗函数时,窗函数的选择非常重要。理想的窗函数是主瓣宽度尽量小、过渡带尽量陡,以使频点能量更加集中。应用较多的窗函数有矩形窗、汉宁窗、哈明窗、布莱克曼窗等。图1给出了相干采样图形和非相干采样图形加窗函数后的功率谱密度。对于相干采样,能量都集中在一个频率点上,平均噪底低;对于非相干采样,出现了频谱泄漏现象,平均噪底被抬高,经过加窗函数处理后,其平均噪底被压低,能量分布得到集中,但是能量依然不如相干采样集中。在测试ADC动态性能参数时,选择一个合适的窗函数很难,不同的窗函数导致测试结果也不一样。

GE推出新型高性能ADC/DAC模块,设计紧凑、灵活且具成本效益

GE推出新型高性能ADC/DAC模块,设计紧凑、灵活且具

成本效益

佚名

【期刊名称】《测控技术》

【年(卷),期】2011(30)8

【摘要】GE智能平台近日宣布推出ICS-1572A ADC/DAC(模拟-数字转换器/数字-模拟转换器)收发器XMC模块。

该模块强化了模拟传感器领域和数字计算领域的联系,可部署在要求严苛的雷达、信号智能、通信和测试及测量应用中。

新型板卡具备250MHz的16位数据采集能力和先进的Xilinx Virtex^TM-6FP-GA处理器,性能卓越、低成本、高效且紧凑、轻巧。

【总页数】1页(P114-114)

【关键词】DAC;ADC;模块;成本效益;性能;GE;紧凑;模拟-数字转换器

【正文语种】中文

【中图分类】TP311.13

【相关文献】

1.GE Fanuc智能平台推出适合严格军事应用的高性能加固型单插槽图形解决方案/美盛科技发表新型嵌入式以太网络供电系统受电端模块 [J],

2.Microchip推出集成兼具成本效益的先进模拟和数字外设之8位PIC单片机全新MCU具有片上12位ADC、8位DAC、运算放大器、高速比较器和超低功耗技术;其16位PWM可实现业界最高级先进控制 [J],

3.GE推出新型高性能ADC/DAC模块 [J],

4.GE推出新型高性能ADC/DAC模块 [J], 廖日昌

5.GE公司推出具有高性能和灵活性的新型测厚仪——DSM Go [J], 侯芳

因版权原因,仅展示原文概要,查看原文内容请购买。

dac测试方法

dac测试方法DAC(Digital-to-Analog Converter,数字到模拟转换器)是一种电子设备,将数字信号转换为模拟信号。

在音频设备中,DAC负责将数字音频信号转换为模拟音频信号,以便于扬声器或耳机等模拟设备进行播放。

进行DAC测试的目的是确保DAC的性能和准确度,以保证音频信号的高质量转换。

以下是一些常见的DAC测试方法:1. 信噪比测试:信噪比是衡量DAC性能的重要指标之一。

测试过程中,将输入一个固定的音频信号,然后测量输出信号中的噪声水平。

较高的信噪比表示DAC能够更准确地转换数字信号并减少噪声。

2. 频率响应测试:频率响应测量评估DAC在不同频率下的输出准确度。

测试中,输入一系列频率的音频信号,然后测量输出的幅度和相位。

通过比较输入和输出信号之间的差异,可以确定DAC在不同频率下的性能。

3. 线性度测试:线性度测试用于评估DAC的线性转换能力。

在测试中,输入一个连续的音频信号,然后测量输出信号的失真水平。

较低的失真表示DAC能够更准确地转换输入信号。

4. 动态范围测试:动态范围测试用于衡量DAC的动态范围,即DAC 能够处理的最大和最小信号的幅度差异。

测试中,输入一个具有不同幅度的音频信号,然后测量输出信号的幅度范围。

较大的动态范围表示DAC能够处理更广泛的信号幅度。

5. 抖动测试:抖动是指由于时钟不稳定性而引起的时序误差。

抖动测试用于评估DAC的抖动性能。

测试中,输入一个稳定的音频信号,并测量输出信号的时序误差。

较低的抖动表示DAC能够更准确地转换输入信号。

以上是一些常见的DAC测试方法,通过对DAC进行全面的测试和评估,可以确保音频设备提供高质量的模拟音频输出。

这些测试方法可以帮助制造商和工程师在开发和生产过程中,确保DAC的性能和准确度达到预期水平。

基于电流舵的高精度低功耗13-bits DAC设计

76电子技术Electronic Technology电子技术与软件工程Electronic Technology & Software Engineering数模转换器(Digital-to-Analog Converter ,简称DAC ),顾名思义,是集成电路领域中连接数字电路和模拟电路的桥梁,亦是数字电路系统与外部模拟信号世界间交换信息的主要渠道。

利用DAC ,可以将离散的数字信号转化为连续的模拟信号,其在现代5G 通信、高速雷达探测、医疗通信系统及物联网等信号处理过程中扮演着不可或缺的角色,重要性不言而喻。

目前,随着集成电路技术的飞速发展,各电子技术应用领域对DAC 的指标性能也提出了更加苛刻的要求,研究和设计低功耗、宽范围、高精度、高速率的数模转换器具有十分重要的实践意义。

传统的DAC 结构有权电阻结构、R-2R 结构、电荷分布结构等;一般地,电压型DAC 多用于低速转换器内,且电阻结构中电阻的数量会随着转换位数的增加而带来版图面积的消耗。

因此,在高速、高精度的应用需求下,设计一款性能优越的电流舵型DAC 将对通信领域起到推动型的作用。

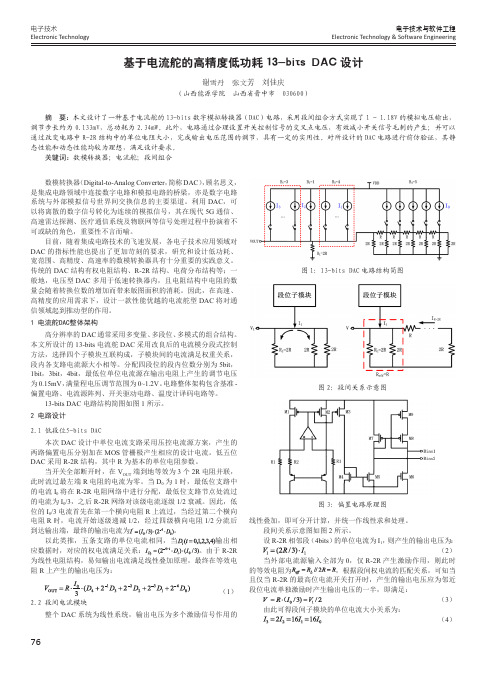

1 电流舵DAC整体架构高分辨率的DAC 通常采用多变量、多段位、多模式的组合结构。

本文所设计的13-bits 电流舵DAC 采用改良后的电流模分段式控制方法,选择四个子模块互联构成,子模块间的电流满足权重关系,段内各支路电流源大小相等。

分配四段位的段内位数分别为5bit ,1bit ,3bit ,4bit ,最低位单位电流源在输出电阻上产生的调节电压为0.15mV ,满量程电压调节范围为0~1.2V 。

电路整体架构包含基准-偏置电路、电流源阵列、开关驱动电路、温度计译码电路等。

13-bits DAC 电路结构简图如图1所示。

2 电路设计2.1 低段位5-bits DAC本次DAC 设计中单位电流支路采用压控电流源方案,产生的两路偏置电压分别加在MOS 管栅极产生相应的设计电流。

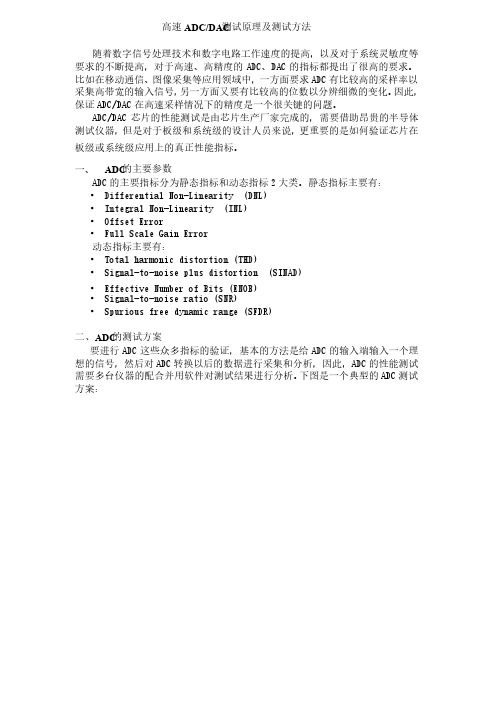

高速ADC、DAC测试原理及测试方法

高速ADC/DAC 测试原理及测试方法随着数字信号处理技术和数字电路工作速度的提高,随着数字信号处理技术和数字电路工作速度的提高,以及对于系统灵敏度等以及对于系统灵敏度等要求的不断提高,对于高速、高精度的ADC ADC、、DAC 的指标都提出了很高的要求。

比如在移动通信、图像采集等应用领域中,一方面要求ADC 有比较高的采样率以采集高带宽的输入信号,另一方面又要有比较高的位数以分辨细微的变化。

因此,保证ADC/DAC 在高速采样情况下的精度是一个很关键的问题。

ADC/DAC 芯片的性能测芯片的性能测试试是由芯片芯片生产厂家完成生产厂家完成生产厂家完成的,的,的,需需要借助昂贵借助昂贵的的半导体测试仪器试仪器,,但是对于是对于板级板级板级和系统和系统和系统级级的设计人员来说设计人员来说,,更重更重要的是如要的是如要的是如何验何验何验证芯片在证芯片在板级或板级或系统系统系统级级应用应用上上的真正真正性能指标。

性能指标。

一、ADC的主要参数ADC 的主要指标分要指标分为静态为静态为静态指标和动指标和动指标和动态态指标2大类大类。

静态静态指标指标指标主主要有要有::•Differential Non-Linearity (DNL)•Integral Non-Linearity (INL)•Offset Error•Full Scale Gain Error动态指标指标主主要有要有::•Total harmonic distortion (THD)•Signal-to-noise plus distortion (SINAD)•Effective Number of Bits (ENOB) •Signal-to-noise ratio (SNR) •Spurious free dynamic range (SFDR)二、ADC 的测试方案要进行ADC 这些众多这些众多指标的指标的指标的验验证,证,基本基本基本的方的方的方法法是给ADC 的输入的输入端端输入一个理想的信号,的信号,然后然后然后对对ADC 转换转换以以后的数的数据进行据进行据进行采集和分采集和分采集和分析析,因此,,因此,ADC ADC 的性能测的性能测试试需要多台仪器多台仪器的的配合并配合并用用软件软件对测对测对测试结果进行试结果进行试结果进行分分析。

经典:ADC与DAC-动态性能测试

食品安全管理制度清单及其操作流程食品安全管理制度清单:一、从业人员健康管理制度1.食品生产经营者应建立并执行从业人员健康管理制度。

2.从事接触直接入口食品工作的食品生产经营人员应每年进行健康检查,取得健康证明后方可上岗工作。

3.患有国务院卫生行政部门规定的有碍食品安全疾病的人员,不得从事接触直接入口食品的工作。

二、食品安全自查制度1.食品生产经营者应建立食品安全自查制度,定期对食品安全状况进行检查评价。

2.生产经营条件发生变化,不再符合食品安全要求的,食品生产经营者应立即采取整改措施。

3.有发生食品安全事故潜在风险的,应立即停止食品生产经营活动,并向所在地县级人民政府食品药品监督管理部门报告。

三、食品原料、食品添加剂、食品相关产品进货查验制度1.食品生产经营者应建立食品原料、食品添加剂、食品相关产品进货查验制度。

2.对采购的食品原料、食品添加剂、食品相关产品的名称、规格、数量、生产批号、保质期、供货者名称及联系方式、进货日期等内容进行登记,建立台帐。

四、食品出厂检验记录制度1.食品生产经营者应建立食品出厂检验记录制度。

2.对出厂的食品的名称、规格、数量、生产批号、保质期、检验日期等内容进行记录。

五、食品添加剂出厂检验记录制度1.食品生产经营者应建立食品添加剂出厂检验记录制度。

2.对出厂的食品添加剂的名称、规格、数量、生产批号、保质期、检验日期等内容进行记录。

六、食品安全追溯体系1.食品生产经营者应建立食品安全追溯体系,保证食品可追溯。

2.对食品的生产、流通、消费等环节进行记录,确保食品来源可查、去向可追。

七、不合格食品处置制度1.食品生产经营者应建立不合格食品处置制度。

2.对检测不合格的食品进行标记、隔离,并及时采取整改、召回等措施。

八、食品安全突发事件应急处置方案1.食品生产经营者应制定食品安全突发事件应急处置方案。

2.在发生食品安全突发事件时,立即启动应急预案,采取控制、处理措施,并及时报告。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

阶跃 响应

的输人为一个正弦波的数字代码 ; 其 输 出是 阶 梯 状 的 正 弦 波 输 出 ,需 要通过一个滤波器进行平滑处理 。 经 滤 波 后 的 输 出 波 形再 在 颁 域 进 行

分 析 ,寻 找 与 基 波 频 率 相 关 的 谐 波

■ 俞 慧 月 邵博 闻 刘芸 易伟 上 海 硅 知 识产 权 交易 中心

随着无 线局 域 网( A 技 术 、 WL N) 移 动 通 信 技 术 和 集 成 电 路 技 术 的 快

速 发 展 ,对 高 速 高 精 度 模 数 转 换 器

( DAC) 的性 能 指 标 提 出 r很 高 的 要

所  ̄( NDP或 SNAD1 S . I :跟s NR的计 算 数 , 可 以 搭 建 如 图 1 示 的 测 试 系

方 法 一 样 , 只是 将谐 波 分 量 也 计 算 统 。测 试 系 统 使 用 数 字 输 入 输 出系

在 噪声 内。4 伞谐 波 失真 (HD :和 . T )

sN 相 似 ,但 它 只包 含 谐 波 分 量 I AD 不 包 含 噪 声 。 在 这 个 比值 计 算 中 ,

需 的 DAC,主 要 关 注 以 下 性 能 指 除 基波 分 量 以及 所 有 谐 波分 量 后 剩 在 系 统 中的 表 现 。 比如 在 视 频 应 用

标 :1 无 杂 波 动态 范 同( F . S DR) :指 下 部 分就 是 噪声 ,S NR是 基 波 分量 中 , 如 果 S DR 小 ,颜 色 的 分 辨 F 偏

在 的问题

不 确 定 的 负 载 ,导 致 不 能 确 定 内置 (cieb f r 解决 驱动 负载不 确定 at uf ) v e来 在 一 定 的时 间 内稳 定 下来 。这 样 系

( 接4 页 ) 下 6

F T图 F

s l

在 对 DAC进 行 测 试 时 , 一 方 ADC采集 时 ,DAC输 m 信号 是 否 已 的问 题 ,可 以 有 效地 保 证 DAC 片 芯

基 波 或 载 波 分 量 与 其 他 非 基 波 和 载 与 所 有 噪 声 分量 之 和 的 比 值 。 S 率 就 会 下 降 ;在 数 字 传 输 系 统 中 , NR

波 的最 大 杂 波频 率 分 量( 以是 谐 波 可 通过 给 D 施 加 一 个 满 量 程 的 正 误 码 率 就 会 提 高 。在 音 频 系统 中 , 可 AC

求 。 而 对 于设 计人 员 来 说 ,如 何 测 试 、 验 证 DAC真 正 的 性 能 指 标 非

常重 要 ,本 文将 专 门 对 高 速 高 精 度

DAC的测试 方法进 行探讨 。

D C A 的主要 参数和 常 用的测 试方法

对 于 视 频 和无 线 通讯 等 应 用 所

图1 :D C测 试 系 统 A

设计 诀 窍

IHc w w N L。 。 T IK H E AN C

高速高精度D C A 关键性能测试 方法研究

本 文介绍 了高速 高精 度D C的测试方 法 ,并针对 测试 中遇到的具体 问题 ,提 出了在测试动态 参数方 A 面 的解 决 办法 ,而 且 以实 际 测试 证 明 d 。2 信 弦 波 数字 代码 冉 分 析其 输 出 波 形 的 T 偏 大 ,则 导致 杂音 的产生 。 B . HD

噪 [( NR :DAC的输 出经过 滤波 滤 频 率 特 性 得 到 。 3 信 号 与 噪 声 谐 波 LS ) .

一

般 来 说 , 为 了 测 试 以 上 参

抓取被测器件的输f信号并量化 , 』 j

由图3 以看 出 ,同样 的DAC 可 驱

激励 ,再使 用 数字 量 化 器( gt e1 方 面要 保 证 信 号 传 递 的质 量 和 完 整 动下 ,不 同 的 负 载 有 着不 同 的稳 定 Dii z r i 性 ,这 对 测 试 电路 板 的设 计 、制 造 时 间 ,负 载 越 大稳 定 时 间越 慢 ,而 并 且 分 别 存不 同频 点 进 行 验 证 ,在 就 提 出 了一 定 的 要 求 ;而 在 高 速 高 在 DAC的 动态 性 能 测 试 中 ,芯 片是

的功 耗 ,使 用测 试 设 备(P ) 被 复现所需的信号。 P MU 对 测 器 件 漏 电流 和参 考 电 压等 参 数 进

行 量测 。 由于使用 ADC 模数 转换 器) ( 采集 DAC 态性 能测试 的解决 方案 动

D C A 的信 号时 ,不 同 的A C 着 不 D 有

图2 :不 同负 载 的 阶 跃 响 应

分 量 。 上 述 参 数 将 直 接 影 响 DAC 图3:在 测试 系统 中加 入 缓 冲 器 。

4 集成 电路应用 2l

设计诀 窍

TECHNI cAL KN。W H 。w

图4:缓 冲 器 电 路

统( I ) 被测 器 件 提 供 数 字 信 号 信号与时钟信号 的时序关 系 ;另一 DSO 为

验 证 过程 中使用 直 流 仪表 ( D ) H VS为 精 度 D C的测 试 中 ,更 重要 的是 要 否能 在 所 需 的 时 间稳 定 下 来 是 测 试 A

被 测 器 件 提 供 电源 并 测量 被 测 器 件 保 证 信 号 采 集 的 正 确 ,能 够 『 确 地 是 否成功 的关 键 。 伟

为 了能 够 正 确 评 价 高 速 高 精 度

同 的输 入 电容 。 所 以 一 般 测 试 过 程 DAC芯 片 的 动 态 参 数 , 在 常 用 的 高 速 高 精 度 DAC测 试 的 关 键 点及 存 中 不 叮避 免 地 在 DAC的输 H 端 带 来 测 试 系 统 中 ,通 过 加 入 有 源 缓 冲器 {