计算机系统结构第四章.ppt

合集下载

计算机系统结构多媒体教程课件_第四章 存储系统

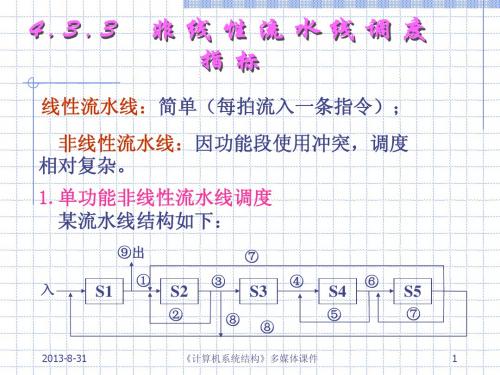

2013-8ቤተ መጻሕፍቲ ባይዱ31 《计算机系统结构》多媒体课件 15

结论:CPU在执行程序时, 所用到的指令和数据的MEM 单元地址分布不会是随机的, 而是相对集中成自然的块或 页面(MEM中较小的连续单元 区)。

2013-8-31

《计算机系统结构》多媒体课件

5

Embedded , desktop, server computers

2013-8-31 《计算机系统结构》多媒体课件 6

1、MEM容量、速度、价 格的矛盾 2、存贮体系层次 3、程序的局部性 4、存贮体系的性能参数

2013-8-31 《计算机系统结构》多媒体课件 7

2013-8-31

《计算机系统结构》多媒体课件

2

introduction

In 1980 microprocessors were often design without caches,while many come with two levels of caches on the chip. Why? !!!!

A A

Tm

2013-8-31

Tm

9

《计算机系统结构》多媒体课件

(3)频宽Bm: * MEM连续访问时,每单位时间内存取的信 息量以bit/s OR Byte/s为单位。 * 单体MEM :Bm =W/TM * 多体并行MEM :Bm =W·m/TM 理想状态下MEM满负荷工作的最大频宽。 * 实际上由于MEM不可能一直处于RD/WR , 所以实际频宽 < 最大频宽。

1、MEM 容量 * Sm=W*L*m * W:MEM 存储体字长(以 bit OR Byte 为单位) L:单个存贮体字数 m:并行工作的MEM 体个 数 * Sm 单位为***bit OR ***B

结论:CPU在执行程序时, 所用到的指令和数据的MEM 单元地址分布不会是随机的, 而是相对集中成自然的块或 页面(MEM中较小的连续单元 区)。

2013-8-31

《计算机系统结构》多媒体课件

5

Embedded , desktop, server computers

2013-8-31 《计算机系统结构》多媒体课件 6

1、MEM容量、速度、价 格的矛盾 2、存贮体系层次 3、程序的局部性 4、存贮体系的性能参数

2013-8-31 《计算机系统结构》多媒体课件 7

2013-8-31

《计算机系统结构》多媒体课件

2

introduction

In 1980 microprocessors were often design without caches,while many come with two levels of caches on the chip. Why? !!!!

A A

Tm

2013-8-31

Tm

9

《计算机系统结构》多媒体课件

(3)频宽Bm: * MEM连续访问时,每单位时间内存取的信 息量以bit/s OR Byte/s为单位。 * 单体MEM :Bm =W/TM * 多体并行MEM :Bm =W·m/TM 理想状态下MEM满负荷工作的最大频宽。 * 实际上由于MEM不可能一直处于RD/WR , 所以实际频宽 < 最大频宽。

1、MEM 容量 * Sm=W*L*m * W:MEM 存储体字长(以 bit OR Byte 为单位) L:单个存贮体字数 m:并行工作的MEM 体个 数 * Sm 单位为***bit OR ***B

计算机组成原理-第4章_指令系统

7. 段寻址方式(Segment Addressing)

方法:E由段寄存器的内容加上段内偏移地址而形成。

应用:微型机采用段寻址方式,20位物理地址为16位 段地址左移四位加上16位偏移量。

分类:① 段内直接寻址; ② 段内间接寻址; ③ 段间直接寻址; ④ 段间间接寻址;

9 堆栈寻址方式

堆栈:是一组能存入和取出数据的暂时存储单元。

*** 指令字长度

概念 指令字长度(一个指令字包含二进制代码的位数) 机器字长:计算机能直接处理的二进制数据的位数。 单字长指令 半字长指令 双字长指令

多字长指令的优缺点

优点提供足够的地址位来解决访问内存任何单元的寻址问题 ; 缺点必须两次或多次访问内存以取出一整条指令,降低了CPU的运 算速度,又占用了更多的存储空间。

*** 指令系统的发展与性能要求

*** 指令系统的发展

指令:即机器指令,要计算机执行某种操作的命令。

指令划分:微指令、机器指令和宏指令。

简单

复杂

指令系统:一台计算机中所有指令的集合;是表征

计算机性能的重要因素。

系列计算机:基本指令系统相同、基本体系结构相同 的一系列计算机。

*** 对指令系统性能的要求

(2)立即数只能作为源操作数,立即寻址主要用来给寄存 器或存储器赋初值。以A~F开头的数字出现在指令中时,前 面要加0。

(3)速度快(操作数直接在指令中,不需要运行总线周期)

(4)立即数作为指令操作码的一部分与操作码一起放在代 码段区域中。

(5)指令的长度(翻译成机器语言后)较长,灵活性较差。

【例】MOV AX, 10H 执行后(AX)=? 其中:这是一条字操作指令,源操作数为立即寻址 方式,立即数为0010H,存放在指令的下两个单元。

《计算机体系结构》课件

ABCD

理解指令集体系结构、处 理器设计、存储系统、输 入输出系统的基本原理和 设计方法。

培养学生对计算机体系结 构领域的兴趣和热情,为 未来的学习和工作打下坚 实的基础。

CHAPTER

02

计算机体系结构概述

计算机体系结构定义

计算机体系结构是指计算机系统的整 体设计和组织结构,包括其硬件和软 件的交互方式。

CHAPTER

06

并行处理与多核处理器

并行处理概述

并行处理

指在同一时刻或同一时间间隔内 完成两个或两个以上工作的能力

。

并行处理的分类

时间并行、空间并行、数据并行和 流水并行。

并行处理的优势

提高计算速度、增强计算能力、提 高资源利用率。

多核处理器

1 2

多核处理器

指在一个处理器上集成多个核心,每个核心可以 独立执行一条指令。

间接寻址

间接寻址是指操作数的有效地址通过寄存器间接给出,计算机先取出 寄存器中的地址,再通过该地址取出操作数进行操作。

CHAPTER

04

存储系统

存储系统概述

存储系统是计算机体系结构中 的重要组成部分,负责存储和 检索数据和指令。

存储系统通常由多个层次的存 储器组成,包括主存储器、外 存储器和高速缓存等。

《计算机体系结构》ppt 课件

CONTENTS

目录

• 引言 • 计算机体系结构概述 • 指令系统 • 存储系统 • 输入输出系统 • 并行处理与多核处理器 • 流水线技术 • 计算机体系结构优化技术

CHAPTER

01

引言

课程简介

计算机体系结构是计算机科学的一门核心课程,主要研究计算机系统的基本组成、组织结构、工作原 理及其设计方法。

西安电子科技大学_计算机组成与体系结构_第4章存储系统_课件PPT

的时间一样。

存取方式 读写功能

随机读写:RAM 顺序(串行)访问:

顺序存取存储器 SAM 直接存取存储器 DAM

12

4.1 存储系统概述 4.1.2 存储器分类:不同的分类标准

存储信息的介质

在计算机中的用途

存放信息的易失(挥发)性

存取方式 读写功能

读写存储器 只读存储器

13

存储信息的介质

在计算机中的用途 存放信息的易失(挥发)性 存取方式 读写功能

易失:RAM 非易失:

ROM 磁盘

……

11

4.1 存储系统概述 4.1.2 存储器分类:不同的分类标准

存储信息的介质 在计算机中的用途 存放信息的易失(挥发)性

存储器的存取时间 与存储单元的物理 地址无关,随机读 写其任一单元所用

无

36

8086系统总线

D0~D7

A1~A13 MEMR MEMW

A0

D8~D15 A1~A13 MEMR MEMW

BHE

&

A19

A18

A17

&

A16 A15 A14

6264与8086系统总线的连接

6264

D0~D7

A0~A12

CS1

OE

WE

CS2

6264

D0~D7

A0~A12

CS1

OE

WE

CS2

74LS138

每次读出/写入的字节数 存取周期

价格

体积、重量、封装方式、工作电压、环境条件

14

4.1 存储系统概述 4.1.2 存储器的性能指标

容量 速度 可靠性

可维修部件的可靠性: 平均故障间隔时间(MTBF)

存取方式 读写功能

随机读写:RAM 顺序(串行)访问:

顺序存取存储器 SAM 直接存取存储器 DAM

12

4.1 存储系统概述 4.1.2 存储器分类:不同的分类标准

存储信息的介质

在计算机中的用途

存放信息的易失(挥发)性

存取方式 读写功能

读写存储器 只读存储器

13

存储信息的介质

在计算机中的用途 存放信息的易失(挥发)性 存取方式 读写功能

易失:RAM 非易失:

ROM 磁盘

……

11

4.1 存储系统概述 4.1.2 存储器分类:不同的分类标准

存储信息的介质 在计算机中的用途 存放信息的易失(挥发)性

存储器的存取时间 与存储单元的物理 地址无关,随机读 写其任一单元所用

无

36

8086系统总线

D0~D7

A1~A13 MEMR MEMW

A0

D8~D15 A1~A13 MEMR MEMW

BHE

&

A19

A18

A17

&

A16 A15 A14

6264与8086系统总线的连接

6264

D0~D7

A0~A12

CS1

OE

WE

CS2

6264

D0~D7

A0~A12

CS1

OE

WE

CS2

74LS138

每次读出/写入的字节数 存取周期

价格

体积、重量、封装方式、工作电压、环境条件

14

4.1 存储系统概述 4.1.2 存储器的性能指标

容量 速度 可靠性

可维修部件的可靠性: 平均故障间隔时间(MTBF)

计算机系统结构多媒体教程课件_第四章 控制方式——流水线2

平均间 隔拍数 4.50 3.67

调度策略

平均间 隔拍数

(3, 4, 3, 7) 4.25 (4, 3, 7) 4.67

3.50

5.00

(4, 7)

(7)

5.00

7.00

(3, 4, 7)

2013-8-31

4.67

12

《计算机系统结构》多媒体课件

最小平均等待时间(minimal average latency---MAL) 可见,最佳调度方案为(3,4),MAL=3 .5。对非C0 开始的调度方案由流水线控制器完成控制的过渡。 简单循环:每种状态只出现一次的等待时间循环 简单循环中由一些是迫切循环。 迫切循环:从各自的初始状态输出的边缘都具有最小 等待时间的循环。这样的循环首先是简单循环,并且 他们的平均等待时间必须比其他简单循环的更小。 从迫切循环中确定MAL • MAL应小于或等于状态图中任一迫切循环的平均等待 时间 • 上限是初始冲突向量的1个数再+1

t S 1 2 3 4 5 6 7 8 9

1

2 3

×

× × × × ×

×

4

5

2013-8-31

×

×

× ×

2

《计算机系统结构》多媒体课件

与时空图区别? 动态流水线可以由一张以上的预约表来表示。 每张预约表表示的是某一功能求值的数据通过 流水线的时空流 预约表一行可以有多个符号,含义是在不同周期 重复使用同一段;一列中多个符号是指在一个 特定的时钟周期内并行使用多个周期。

2

7

4

7

10111101 2 10111111

2013-8-31

《计算机系统结构》多媒体课件

11

(5)找出最佳调度方案 从各个闭合回路中找出平均间隔最小的一个。 本例中调度方案如下:

第4章-计算机系统结构(第五版)李学干

为简单起见,以图4 - 4所示的二级存储体系(M1,M2)为

例来分析。 存储层次的每位价格为

c1 S M1 c2 S M 2 c S M1 S M 2

第4章 存储体系

图 4 - 4 二级存储体系的评价

第4章 存储体系

存储层次的等效访问时间TA= HTA (1 H )TA 。希望 1 2 TA越接近于 T ,即存储层次的访问效率e= TA /TA越接近于1 A 越好。

第4章 存储体系

图 4 - 14 主存页面表

第4章 存储体系

【例 4-1】

设有一道程序,有1~5页,执行时的页地址流(即依次用

到的程序页页号)为 2,3,2,1,5,2,4,5,3,2,5,2 若分配给该道程序的主存有3页,则图4 - 15表示FIFO、 LRU、OPT这3种替换算法对这3页的使用和替换过程。

第4章 存储体系

4.1 基本概念 4.2 虚拟存储器 4.3 高速缓冲存储器 4.4 三级存储体系

4.5 存储系统的保护

4.6 本章小结

第4章 存储体系

4.1 基 本 概 念

4.1.1 存储体系及其分支

前面已经讲过,为了同时满足存储系统的大容量、高速度 和低价格,需要将多种不同工艺的存储器组织在一起。 虚拟存储器是因为主存容量满足不了要求而提出来的。在

第4章 存储体系

2. 页式管理 段式存储中各段装入主存的起点是随意的,段表中的地 址字段很长,必须能表示出主存中任意一个绝对地址,加上 各段长度也是随意的,段长字段也很长,这既增加了辅助硬

件开销,降低了查表速度,也使主存管理麻烦。

例如,主存中已有A、B、C三个程序,其大小和位置如 图4 - 7所示,现有一长度为12 KB的D道程序想要调入。

例来分析。 存储层次的每位价格为

c1 S M1 c2 S M 2 c S M1 S M 2

第4章 存储体系

图 4 - 4 二级存储体系的评价

第4章 存储体系

存储层次的等效访问时间TA= HTA (1 H )TA 。希望 1 2 TA越接近于 T ,即存储层次的访问效率e= TA /TA越接近于1 A 越好。

第4章 存储体系

图 4 - 14 主存页面表

第4章 存储体系

【例 4-1】

设有一道程序,有1~5页,执行时的页地址流(即依次用

到的程序页页号)为 2,3,2,1,5,2,4,5,3,2,5,2 若分配给该道程序的主存有3页,则图4 - 15表示FIFO、 LRU、OPT这3种替换算法对这3页的使用和替换过程。

第4章 存储体系

4.1 基本概念 4.2 虚拟存储器 4.3 高速缓冲存储器 4.4 三级存储体系

4.5 存储系统的保护

4.6 本章小结

第4章 存储体系

4.1 基 本 概 念

4.1.1 存储体系及其分支

前面已经讲过,为了同时满足存储系统的大容量、高速度 和低价格,需要将多种不同工艺的存储器组织在一起。 虚拟存储器是因为主存容量满足不了要求而提出来的。在

第4章 存储体系

2. 页式管理 段式存储中各段装入主存的起点是随意的,段表中的地 址字段很长,必须能表示出主存中任意一个绝对地址,加上 各段长度也是随意的,段长字段也很长,这既增加了辅助硬

件开销,降低了查表速度,也使主存管理麻烦。

例如,主存中已有A、B、C三个程序,其大小和位置如 图4 - 7所示,现有一长度为12 KB的D道程序想要调入。

高级体系结构ppt课件

I1

2

2

3

3

4

4

5

5

H

6 7

G

6 7 J

Ω网的特点(2):

并不是所有的置换在Ω网中一次通过便可 以实现。

Ω网是阻塞网络:出现冲突时,可以采用 几次通过的方法来解决冲突。

Ω网的广播功能: 0018个输出端

第0级

第1级

0

1

2 3

4 5

6 7

第2级 0 1

2 3

4 5

6 7

44开关构成的Ω网:多路洗牌

000

000

001

001

010

010

011

011

100

100

101

101

110

110

111

111

0

12

3

4

56

7

6. PM2I函数(加减2i) 共有2n个互连函数,对N个结点的网络为

PM PM

2i 2i

( (

j j

) )

j 2i j 2i

mod mod

N N

其中,0 j N 1,0 i n 1,n log 2 N

000

000

001

001

010

010

011

011

100

100

101

101

110

110

111

111

0

12

3

4

56

7

Cube2: cube2 (X2 X1X0 ) (X2 X1X0 )

000

000

001

001

010

010

011

计算机组成原理4第四章存储器PPT课件精选全文

4.2

11

4.2

请问: 主机存储容量为4GB,按字节寻址,其地址线 位数应为多少位?数据线位数多少位? 按字寻址(16位为一个字),则地址线和数据线 各是多少根呢?

12

数据在主存中的存放

设存储字长为64位(8个字节),即一个存 取周期最多能够从主存读或写64位数据。

读写的数据有4种不同长度:

字节 半字 单字 双字

34

3. 动态 RAM 和静态 RAM 的比较

主存

DRAM

SRAM

存储原理

电容

触发器

集成度

高

低

芯片引脚

少

多

功耗

小

大

价格

低

高

速度

慢

快

刷新

有

无

4.2

缓存

35

内容回顾: 半导体存储芯片的基本结构 4.2

…… ……

地

译

存

读

数

址

码

储

写

据

线

驱

矩

电

线

动

阵

路

片选线

读/写控制线

地址线(单向) 数据线(双向) 芯片容量

D0

…… D 7

22

(2) 重合法(1K*1位重合法存储器芯片)

0 A4

0,00

…

0,31

0 A3

X 地

X0

32×32

… …

0址

矩阵

A2

译

0码

31,0

…

31,31

A1

器 X 31

0 A0

Y0 Y 地址译码器 Y31 A 9 0A 8 0A 7 0A 6 0A 5 0

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

保持异常行为是指:无论怎么改变指令的 执行顺序,都不能改变程序中异常的发生 情况。

➢ 即原来程序中是怎么发生的,改变执行 顺序后还是怎么发生。

➢ 弱化为:指令执行顺序的改变不能导致 程序中发生新的异常。

4.2 指令的动态调度

内容回顾: 1. 相关

• 相关是指两条指令之间存在某种依赖关系,是程序 固有的一种属性。

4.2 指令的动态调度

一、动态调度的基本思想

考虑下面一段代码: DIV.D F4,F0,F2 SUB.D F10,F4,F6 ADD.D F12,F6,F14

➢ SUB.D指令与DIV.D指令关于F4相关,导致流 水线停顿。

➢ ADD.D指令与流水线中的任何指令都没有关系, 但也因此受阻。

4.2 指令的动态调度

+ 停顿控制冲突

➢ 理想CPI是衡量流水线最高性能的一个指标。 通过减少右边各项,就能减小总的CPI,从 而提高IPC。

➢ IPC:Instructions Per Cycle (每个时钟周期完成的指令条数)

4.1 指令级并行的概念

1. 循环级并行:

使一个循环中的不同循环体并行执行。 开发循环体中存在的并行性是指令级并行研

– 记录和检测指令相关,操作数一旦就绪就 立即执行,把发生RAW冲突的可能性减少 到最小;

– 通过寄存器换名来消除WAR冲突和WAW冲突。

4.2 指令的动态调度

IBM 360/91首先采用了Tomasulo算法。

– IBM 360/91的设计目标是基于整个360系 列的统一指令集和编译器来实现高性能, 而不是设计和利用专用的编译器来提高性 能。

本章研究:如何通过各种可能的技术,获得 更多的指令级并行性。

硬件+软件技术

必须要硬件技术和软件技术互相配合,才 能够最大限度地挖掘出程序中存在的指令 级并行。

4.1 指令级并行的概念

流水线处理机的实际CPI

➢ 理想流水线的CPI加上各类停顿的时钟周期 数:

CPI流水线 = CPI理想 + 停顿结构冲突 + 停顿数据冲突

究的重点之一 最基本的开发循环级并行的技术

– 循环展开(loop unrolling)技术 – 采用向量指令和向量数据表示

2. 相关与流水线冲突

静态指令调度 动态指令调度

4.1 指令级并行的概念

3. 对于正确地执行程序来说,必须保持的最关键 的两个属性是:数据流和异常行为。

数据流:指数据值从其产生者指令到其消 费者指令的实际流动。

– 读操作数(Read Operands,RO):等待 数据冲突消失,然后读操作数。

(out of order execution)

IS

RO

检测结构冲突 检测数据冲突

4.2 指令的动态调度

有的代码在采用乱序执行后可能会发生WAR冲突 和WAW冲突。

例如,考虑下面的的基本流水线中:

ID

检测结构冲突 检测数据冲突

• 一旦一条指令受阻,其后的指令都将停顿。 • 解决办法:

允许乱序执行

4.2 指令的动态调度

为了允许乱序执行,我们将5段流水线的译码 阶段再分为两个阶段:

– 流出(Issue,IS):指令译码,检查是 否存在结构冲突。 (in-order issue)

第四章 指令级并行

4.1 指令级并行的概念 4.2 指令的动态调度 4.3 动态分支预测技术 4.4 多指令流出技术 4.5 循环展开和指令调度

4.1 指令级并行的概念

几乎所有的处理机都利用流水线来使指令重 叠并行执行,以达到提高性能的目的。这种 指令之间存在的潜在并行性称为指令级并行。

(ILP:Instruction-Level Parallelism)

4.2 指令的动态调度

3. 冲突的解决

1)结构冲突:停顿(流水线气泡)

2)数据冲突:

• 定向传送技术

• 定向传送与停顿相结合

• 指令调度(依靠编译器): 前提:在乱序流动的流水线中。 不足:可能会产生新的WAR或WAW冲突。

3)控制冲突: • 预测分支失败

静态调度

• 预测分支成功 都是通过编译器来实现

• 相关包括:名相关,数据相关,控制相关。

2. 冲突( HAZARDS,也称为冒险)

• 冲突是指由于相关的存在,使得指令流中的下一条 指令不能在指定的时钟周期执行。

• 具体一次相关是否会导致实际冲突的发生以及该冲 突会带来多长的停顿,则是流水线的属性。

• 流水线冲突包括:结构冲突,数据冲突,控制冲突。

F4, F0, F2 F10, F4, F6

F6, F8, F14

存在数据相关 存在输出相关

WAR冲突

DIV.D F10, F1, F3

WAW冲突

SUB.D F10, F4, F6

Tomasulo算法可以通过使用寄存器重命名来消除。

4.2 指令的动态调度

二、Tomasulo算法

1.基本思想 核心思想:

需要更多地依赖于硬件。 – IBM 360体系结构只有4个双精度浮点寄存

器,限制了编译器调度的有效性。 – 360/91的访存时间和浮点计算时间都很长。

(也是Tomasulo算法要解决的问题)

4.2 指令的动态调度

寄存器换名可以消除WAR冲突和WAW冲突。

考虑之前的代码: DIV.D F4, F0, F2

从指令部件来

指 令 队 列 load/store 操作

store 缓冲器 数据

地址部件

load 缓冲器

6

5

4

3 2 1

地址

3 2 1

标识

浮点寄存器 FP

浮点操作 操作数总线 操作总线 保 留2 站1 标识

• 延迟转移技术

4.2 指令的动态调度

静态调度

➢ 依靠编译器对代码进行静态调度,以减 少相关和冲突。

➢ 它不是在程序执行的过程中,而是在编 译期间进行代码调度和优化。

➢ 通过把相关的指令拉开距离来减少可能 产生的停顿。

动态调度

➢ 在程序的执行过程中,依靠专门硬件对 代码进行调度,减少数据相关导致的停 顿。

存在反相关F6

SUB.D ADD.D DIV.D

F10, F4, F6

FS6,, F8, F14

FT1,0, F1, F3

存在数据相关F4 存在输出相关F10

消除名相关:引入两个临时寄存器S和T,分别 将第一个F10换成S,将后一个F6换成T。

基于Tomasulo算法的MIPS处理器浮点部件的 基本结构

➢ 即原来程序中是怎么发生的,改变执行 顺序后还是怎么发生。

➢ 弱化为:指令执行顺序的改变不能导致 程序中发生新的异常。

4.2 指令的动态调度

内容回顾: 1. 相关

• 相关是指两条指令之间存在某种依赖关系,是程序 固有的一种属性。

4.2 指令的动态调度

一、动态调度的基本思想

考虑下面一段代码: DIV.D F4,F0,F2 SUB.D F10,F4,F6 ADD.D F12,F6,F14

➢ SUB.D指令与DIV.D指令关于F4相关,导致流 水线停顿。

➢ ADD.D指令与流水线中的任何指令都没有关系, 但也因此受阻。

4.2 指令的动态调度

+ 停顿控制冲突

➢ 理想CPI是衡量流水线最高性能的一个指标。 通过减少右边各项,就能减小总的CPI,从 而提高IPC。

➢ IPC:Instructions Per Cycle (每个时钟周期完成的指令条数)

4.1 指令级并行的概念

1. 循环级并行:

使一个循环中的不同循环体并行执行。 开发循环体中存在的并行性是指令级并行研

– 记录和检测指令相关,操作数一旦就绪就 立即执行,把发生RAW冲突的可能性减少 到最小;

– 通过寄存器换名来消除WAR冲突和WAW冲突。

4.2 指令的动态调度

IBM 360/91首先采用了Tomasulo算法。

– IBM 360/91的设计目标是基于整个360系 列的统一指令集和编译器来实现高性能, 而不是设计和利用专用的编译器来提高性 能。

本章研究:如何通过各种可能的技术,获得 更多的指令级并行性。

硬件+软件技术

必须要硬件技术和软件技术互相配合,才 能够最大限度地挖掘出程序中存在的指令 级并行。

4.1 指令级并行的概念

流水线处理机的实际CPI

➢ 理想流水线的CPI加上各类停顿的时钟周期 数:

CPI流水线 = CPI理想 + 停顿结构冲突 + 停顿数据冲突

究的重点之一 最基本的开发循环级并行的技术

– 循环展开(loop unrolling)技术 – 采用向量指令和向量数据表示

2. 相关与流水线冲突

静态指令调度 动态指令调度

4.1 指令级并行的概念

3. 对于正确地执行程序来说,必须保持的最关键 的两个属性是:数据流和异常行为。

数据流:指数据值从其产生者指令到其消 费者指令的实际流动。

– 读操作数(Read Operands,RO):等待 数据冲突消失,然后读操作数。

(out of order execution)

IS

RO

检测结构冲突 检测数据冲突

4.2 指令的动态调度

有的代码在采用乱序执行后可能会发生WAR冲突 和WAW冲突。

例如,考虑下面的的基本流水线中:

ID

检测结构冲突 检测数据冲突

• 一旦一条指令受阻,其后的指令都将停顿。 • 解决办法:

允许乱序执行

4.2 指令的动态调度

为了允许乱序执行,我们将5段流水线的译码 阶段再分为两个阶段:

– 流出(Issue,IS):指令译码,检查是 否存在结构冲突。 (in-order issue)

第四章 指令级并行

4.1 指令级并行的概念 4.2 指令的动态调度 4.3 动态分支预测技术 4.4 多指令流出技术 4.5 循环展开和指令调度

4.1 指令级并行的概念

几乎所有的处理机都利用流水线来使指令重 叠并行执行,以达到提高性能的目的。这种 指令之间存在的潜在并行性称为指令级并行。

(ILP:Instruction-Level Parallelism)

4.2 指令的动态调度

3. 冲突的解决

1)结构冲突:停顿(流水线气泡)

2)数据冲突:

• 定向传送技术

• 定向传送与停顿相结合

• 指令调度(依靠编译器): 前提:在乱序流动的流水线中。 不足:可能会产生新的WAR或WAW冲突。

3)控制冲突: • 预测分支失败

静态调度

• 预测分支成功 都是通过编译器来实现

• 相关包括:名相关,数据相关,控制相关。

2. 冲突( HAZARDS,也称为冒险)

• 冲突是指由于相关的存在,使得指令流中的下一条 指令不能在指定的时钟周期执行。

• 具体一次相关是否会导致实际冲突的发生以及该冲 突会带来多长的停顿,则是流水线的属性。

• 流水线冲突包括:结构冲突,数据冲突,控制冲突。

F4, F0, F2 F10, F4, F6

F6, F8, F14

存在数据相关 存在输出相关

WAR冲突

DIV.D F10, F1, F3

WAW冲突

SUB.D F10, F4, F6

Tomasulo算法可以通过使用寄存器重命名来消除。

4.2 指令的动态调度

二、Tomasulo算法

1.基本思想 核心思想:

需要更多地依赖于硬件。 – IBM 360体系结构只有4个双精度浮点寄存

器,限制了编译器调度的有效性。 – 360/91的访存时间和浮点计算时间都很长。

(也是Tomasulo算法要解决的问题)

4.2 指令的动态调度

寄存器换名可以消除WAR冲突和WAW冲突。

考虑之前的代码: DIV.D F4, F0, F2

从指令部件来

指 令 队 列 load/store 操作

store 缓冲器 数据

地址部件

load 缓冲器

6

5

4

3 2 1

地址

3 2 1

标识

浮点寄存器 FP

浮点操作 操作数总线 操作总线 保 留2 站1 标识

• 延迟转移技术

4.2 指令的动态调度

静态调度

➢ 依靠编译器对代码进行静态调度,以减 少相关和冲突。

➢ 它不是在程序执行的过程中,而是在编 译期间进行代码调度和优化。

➢ 通过把相关的指令拉开距离来减少可能 产生的停顿。

动态调度

➢ 在程序的执行过程中,依靠专门硬件对 代码进行调度,减少数据相关导致的停 顿。

存在反相关F6

SUB.D ADD.D DIV.D

F10, F4, F6

FS6,, F8, F14

FT1,0, F1, F3

存在数据相关F4 存在输出相关F10

消除名相关:引入两个临时寄存器S和T,分别 将第一个F10换成S,将后一个F6换成T。

基于Tomasulo算法的MIPS处理器浮点部件的 基本结构