任意波形发生器设计

DDS任意波形发生器的设计与实现

DDS任意波形发生器的设计与实现近年来,随着电子技术的飞速进步,任意波形发生器在信号发生、测试、测量等领域扮演着重要的角色。

而Direct Digital Synthesis(DDS)任意波形发生器作为一种数字信号处理技术,由于其高精度、低失真、灵活性强等优点,成为了目前最为常用的任意波形发生器技术之一。

DDS任意波形发生器工作原理基于数字信号处理与相位累加器。

其主要组成部分包括振荡器、相位累加器、数字控制模块和DAC(数模转换器)模块。

其中,相位累加器用于产生一个累加的相位值,该相位值会被数字控制模块处理后再输入DAC模块进行数模转换,并输出到外部电路。

而该外部电路毗连到输出端口,可以控制输出的幅值以及频率,从而生成所需的任意波形。

在过程中,需要思量多个关键因素。

起首,选择合适的振荡器型号以及参考时钟。

振荡器的质量和稳定性直接影响到输出信号的频率稳定性。

而参考时钟的准确性则决定了相位累加器的性能。

其次,在相位累加器的设计中,需要合理选择累加的相位步进值以及相位累加位数。

过大的步进值可能导致相位区分率降低,而过小的步进值会增加累加器的位数,增加系统的复杂度。

另外,数字控制模块的设计需要思量到输入的频率、相位和幅度的变化。

最后,需要合理选择DAC模块以及输出电路,以确保输出信号的质量和稳定性。

在实际实现过程中,可以使用FPGA(Field-Programmable Gate Array)作为主要硬件实现平台,并利用VHDL(VHSIC Hardware Description Language)进行硬件描述,从而构建DDS任意波形发生器。

FPGA的高度灵活性使得其适用于DDS任意波形发生器的实现,并且其可重构的特点使得系统可以依据需要进行扩展和改进。

在软件方面,可以使用C语言编写相应的控制程序,以实现对DDS任意波形发生器的控制和调整。

是一个综合性的工程项目,需要对电路设计、硬件描述语言、数字信号处理等方面有深度的了解和精通。

基于FPGA的任意波形发生器设计

典型的模拟滤波器有巴特沃斯 (Butterworth) 滤波器、切比雪夫 (Chcbyshcv) 滤波器、贝塞尔(Scsscl) 滤波器和椭I 圜(Ellipsc) 滤波器。

这几种低通滤波器都有各自的幅频特性。通带与阻带之间称为过渡带,过渡 带越窄,说明滤波器的选择性越好。巴特沃斯滤波器的响应最为平坦,它的 通带内没有波纹,在靠近零频处,有最平坦通带,趋向阻带时衰减单调增大, 缺点是从通带到阻带的过渡带最宽,对于带外干扰信号的衰减作用最弱,过 渡带不够陡峭。切比雪夫滤波器在通带内衰减在零值和一个土限值之间做等 起伏变化,阻带内衰减单调增大,通带或组带有波动,但过渡带比较陡峭。 贝塞尔滤波器通带内有较好的线性相位持性。椭圆函数滤波器不仅通带内有 起伏,阻带内也有起伏,而且过渡带陡峭。

? 单片机主要完成以下三个方向的任务:

(1) 根据键盘设置的波形和频率,完成波形的选择、编辑,并产生相应的 频率控制字送FPGA 。

(2) 将输出信号的频率送数码管显示。

(3) 与USB 接口芯片实现USB 接口电路并与上位PC 机通信。

主要要完成的工作:

? 1)基于FPGA 的DDS 实现 首先熟悉Quartus II 开发环境,其次对确定FPGA

工艺,无需另行架构,波形稳定度与准确度都比较高,有 理想的波形质量。但是,专用的DDS 芯片的数据表都已 经固化在芯片里,因此对于不同的应用其灵活性相对较, 无法灵活的实现任意波形的输出,同时DDS 芯片加单片 机的设计模式使硬件电路相对复杂。

基于DDS技术选择的实施方案

? 方案二: 基于FPGA 实现DDS 功能,通过单片机实现控制。此方 案的核心在于FPGA 的设计实现逻辑功能,通过对存储器 查表后输出信号,由相连接的数模转换器转换为要求的波 形。单片机作为控制器,易于控制与调试。

dds任意波形发生器设计.

目录1.1 DDS的基本结构 (2)1.2 DDS的工作特点 (4)1.3 DDS的技术指标 (5)1.4实现方案 (7)1.5硬件结构说明 (7)1.6设计过程 (8)1.7频率测量 (18)1.8误差与杂散分析 (19)DDS(Direct Digital Synthesis)的概念首先由美国学者J.Tierncy,C.M.Radar和B.Gold在1971年提出,但限于当时的技术和工艺水平,DDS技术仅仅限于理论研究,而没有应用到实际中去。

近20年来,随着VLSI(Very Large Scale Integration),FPGA(Field Programmable Gates Array)以及DSP(Digital Signal Processing)的发展,这种结构独特的频率合成技术得到了飞速发展。

目前该技术已经被广泛用于接收机本振、信号发生器、通信系统、雷达系统等相关领域中。

1.1 DDS的基本结构DDS(Direct Digital Synthesis)技术设计思想是基于数值计算信号波形的抽样值来实现频率合成的。

它包括数字器件与模拟器件两部分,主要有相位累加器、ROM波形查询表、数模转换器组成。

其基本框图如下。

(1)相位累加器是DDS的核心部分。

一般是由数字全加器和数字寄存器组成,实现相位累加。

如下图所示。

一般DDS的累加器都采用二进制,线性数字信号通过相位累加器实现逐级的累加。

假设累加器字长为N,频率控制字为K,控制时钟频率为f c,系统在同一个时钟下工作,每个时钟周期加法器做一次累加计算。

因为累加器的满偏是2N,所以累加一次,相当于做一次2N模的运算。

得到的和作为相位值。

(2)波形函数存储在ROM中。

根据累加器输出的相位值,作为地址,寻找存储在ROM中的波形函数的幅度量化值,完成相位到幅值的转换,输出相对应的序列。

(3)数模转换器DAC是DDS中的重要部分。

经过查表以后得到的是离散的脉冲信号,通过数模转换器将转换成为连续平滑的信号。

任意波形发生器方案

任意波形发生器的设计方案12电信1 张晓航 1200301108 一,选择课题:电子测量仪器设计——任意波形发生器设计二,设计要求:能产生方波、三角波、正弦波、锯齿波信号。

主要技术指标:(1)输出频率范围100HZ~1KHZ、1~10KHZ(2)输出电压:方波UPP=6V,三角波UPP=6V,正弦波UPP>1V,锯齿波UPP=6V。

三,仪器仪表清单:1.直流稳压电源 1台 2.双踪示波器 2台3.运放741(LM324n)*3 4.二极管 1N4154*2 1N4680*25.电位器50K*2 1K*1 6.电容1μF 47nF *17.电阻 100k 10k 5k 3k 4k 96k若干 8.面包板 1块9.剪刀1把 10.仪器探头线 2根11.电源线若干四,设计考虑因素:信号发生器可以通过多种方法设计产生,但是考虑到如果使用芯片去完成可能所需要的成本比较高,但如果用单片机等则设计太复杂,还需要嵌入相应代码,有点大材小用,综合多方面的因素考虑该方案是可行性比较高,性价比比较高的一种方案,同时,能够让我对于一些专业基础知识有了更深的了解。

元器件可重复利用,符合现在可持续发展的绿色思想。

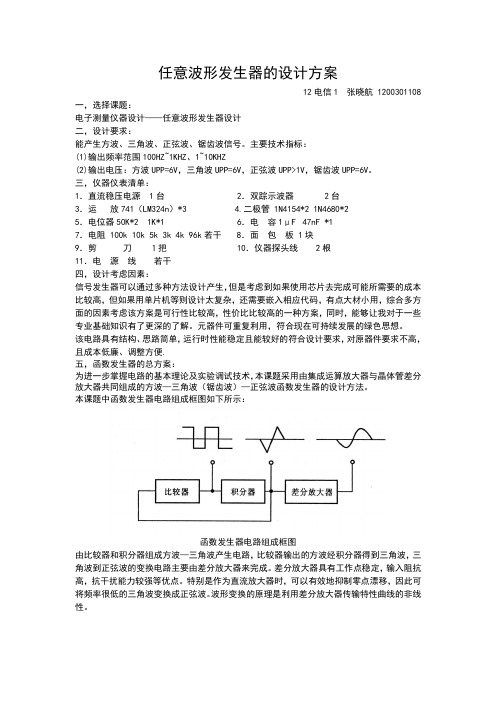

该电路具有结构、思路简单,运行时性能稳定且能较好的符合设计要求,对原器件要求不高,且成本低廉、调整方便.五,函数发生器的总方案:为进一步掌握电路的基本理论及实验调试技术,本课题采用由集成运算放大器与晶体管差分放大器共同组成的方波—三角波(锯齿波)—正弦波函数发生器的设计方法。

本课题中函数发生器电路组成框图如下所示:函数发生器电路组成框图由比较器和积分器组成方波—三角波产生电路,比较器输出的方波经积分器得到三角波,三角波到正弦波的变换电路主要由差分放大器来完成。

差分放大器具有工作点稳定,输入阻抗高,抗干扰能力较强等优点。

特别是作为直流放大器时,可以有效地抑制零点漂移,因此可将频率很低的三角波变换成正弦波。

波形变换的原理是利用差分放大器传输特性曲线的非线性。

任意波形发生器设计

任意波形发生器设计一、设计目标和需求分析在进行任意波形发生器设计之前,首先需要明确设计目标和需求。

根据实际应用需求,我们需要设计一种具有以下特点的任意波形发生器:1.多种波形形状:能够产生包括正弦波、方波、三角波、锯齿波等多种波形形状的输出信号。

2.高精度输出:能够提供稳定、精确的波形输出,满足对波形频率、幅度、相位等参数的要求。

3.宽频率范围:能够在较宽的频率范围内产生波形信号,适应不同应用场景的需求。

4.灵活性和操作便捷:具备灵活的参数调节和操作界面,方便用户配置所需波形信号。

二、电路设计和构成基于以上需求,我们可以采用数字/模拟混合电路来设计任意波形发生器。

整体电路结构包括信号发生器、波形调节电路、滤波器、放大器和输出接口等几大部分。

1.信号发生器:信号发生器是生成基本信号的核心部分。

可以采用数字逻辑电路,通过编程控制产生不同形状的基本波形,例如正弦波、方波、三角波、锯齿波等。

可以使用存储器来存储基本波形的采样点,并通过数字模拟转换器(DAC)将数字信号转换为模拟信号。

2.波形调节电路:波形调节电路用于调整波形的频率、幅度和相位等参数。

通过调整振荡电路中的电阻、电容或电感等元件,实现对基本波形的变换和调节。

可以设计多种电路模块来完成这一任务,例如可变电容二极管电路、可调电阻电路等。

3.滤波器:滤波器用于对产生的波形信号进行滤波处理,除去高频或低频的杂散分量,保留所需频率范围内的信号。

可以采用各种类型的滤波器电路,例如RC滤波器、有源滤波器或数字滤波器等。

4.放大器:放大器用于增强波形信号的幅度,确保输出的信号具备足够的驱动能力,可以驱动接收端电路。

可以采用运放等放大电路,根据需要选择合适的增益。

5.输出接口:输出接口用于将产生的波形信号输出给外部设备。

可以设计多种类型的输出接口,例如模拟输出接口(BNC接口)、数字输出接口(USB接口)等,方便用户接入不同类型的设备。

三、实现方法和关键技术在设计任意波形发生器时,需要考虑以下关键技术和实现方法:1.数字信号处理技术:通过数字信号处理技术,实现对基本波形的生成、存储和输出。

频率可变的任意波形发生器的设计

深圳大学实验报告课程名称:Verilog数字系统设计教程实验工程名称:频率可变任意波形发生器的设计学院:电子科学与技术专业:微电子指导教师:刘春平报告人:潘志钟学号: 2007160051班级: 07级微电1班实验时间:2009-12-8 ~ 2010-1-11实验报告提交时间:2010-1-4教务处制(·····这里可加前言摘要之类的东西····自己想来写···)1设计原理DDS 是一种把数字信号通过数/模转换器转换成模拟信号的合成技术。

直接数字频率合成技术(DDS )是一种以采样定理为基础的全数字化频率合成波形的方法。

DDS 频率合成器主要由频率寄存器、相位寄存器(需要时可加入)、相位累加器、波形存储表(ROM ),DAC 转换器和模拟低通滤波器(LPF )等组成。

在系统时钟(SYSCLK )输入一定的情况下,频率寄存器中的频率控制字决定系统输出频率,而相位累加器的位数决定了系统频率分辨率。

总体设计方案及其原理说明:图 1-1 系统总体设计方案相位累加器由N 位加法器和N 位累加寄存器级联而成。

每当系统时钟SYSCLK 产生一个上升沿,N位加法器将频率寄存器中的频率控制字(FREQDAT A)与上一个系统时钟累加寄存器输出的累加相位数据相加,相加后的结果送累加寄存器。

这样在系统时钟的作用下,不断对频率控制字进行线性相位累加,相位累加器的溢出率就是DDS任意波形发生器的输出频率。

2设计与实现实际上DDS就是通过改变地址增量来达到控制输出频率的目的,而波形存储器(ROM)是以相位为地址,存有一个或多个按相位划分幅值的波形幅度信息。

参考频率f_clk为整个合成器的工作频率,输入的频率字保存在频率寄存器中,经N位相位累加器,累加一次,相位步进增加,经过内部ROM波形表得到相应的幅度值,经过D/A转换和低通滤波器得到合成的波形(数模转换在这里不作要求)。

基于fpga的任意波形发生器的设计与实现

基于fpga的任意波形发生器的设计与实现

一、设计概述

本设计的主要目的是利用FPGA(可编程逻辑器件)来实现一个任意波形发生器,可以产生任意的波形,用于模拟信号的测试和测量。

本设计利用FPGA的自定义功能,根据用户输入的参数,设计一个可以产生任意波形的发生器,并将其实现在一个硬件系统中。

二、系统架构

本系统的架构主要由以下几个部分组成:

(1)输入模块:用户输入的参数由输入模块接收,并将其转换为FPGA可识别的数据格式。

(2)FPGA模块:FPGA模块将用户输入的参数转换为可以产生任意波形的算法,并将其实现在FPGA的芯片上。

(3)输出模块:输出模块将FPGA模块产生的波形输出到外部设备,以便进行测试和测量。

三、设计实现

(1)输入模块:输入模块负责接收用户输入的参数,包括波形类型、频率、相位等,并将其转换为FPGA可识别的数据格式。

(2)FPGA模块:FPGA模块负责将用户输入的参数转换为可以产生任意波形的算法,并将其实现在FPGA的芯片上。

(3)输出模块:输出模块负责将FPGA模块产生的波形输出到外部设备,以便进行测试和测量。

基于FPGA的任意波形发生器的设计和实现范文

0 引言在腐蚀领域和电镀行业,常常需要使用任意波形的电流电压信号进行生产和测试。

任意波形是指频率可变、幅值可变、相位可变的正弦波形和其他波形,如三角波形、锯齿波、特殊波形等。

目前任意波形发生器大多采用直接数字频率合成(DDS)技术,即将波形的数字量信号存储于存储器中,嵌入式主机以一定的速率依次将存储器单元中的波形数据逐个发送给D/A转换器,合成为需要的波形。

随着微处理器日益广泛的应用和大规模集成电路技术的发展,出现了大量能够产生多种波形且性能稳定的任意波形发生器,但大多数方案都是基于串行或并行总线进行数据的传输,这种方案虽然成本较低,但系统的实时性较差,难以满足复杂波形的大数据量的传输要求。

我们设计了一种基于FPGA芯片的任意波形发生器,充分利用了FPGA强大的逻辑功能,实现了利用单片FPGA芯片控制整个系统的方案。

同时选择USB2.0接口芯片CY7C68013,它能较好地与FPGA芯片合作,完成系统预先设计的功能,使总体电路简单,成本低廉,产生的波形信号精度较高。

数字波形数据从上位机通过USB总线直接存储在SRAM数据存储器中,通过FPGA控制,将波形数据读出,送入后向通道进行D/A转换和放大处理后得到所需的模拟信号波形。

与传统的发生器在ROM或FLASH存储波形数据的方法相比,具有更大的灵活性。

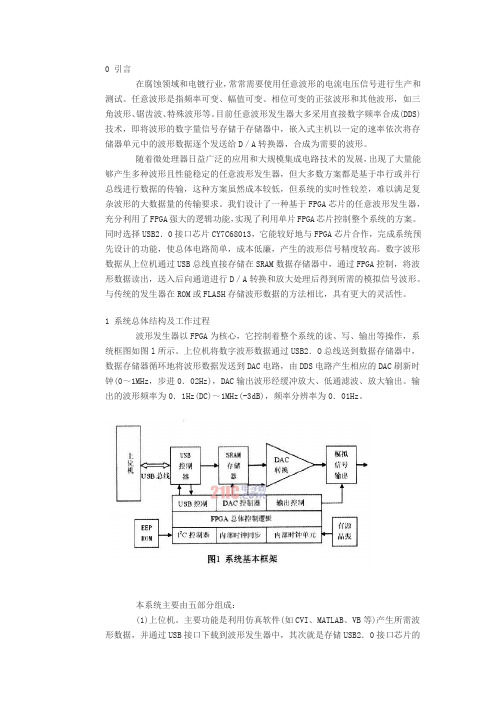

1 系统总体结构及工作过程波形发生器以FPGA为核心,它控制着整个系统的读、写、输出等操作,系统框图如图l所示。

上位机将数字波形数据通过USB2.O总线送到数据存储器中,数据存储器循环地将波形数据发送到DAC电路,由DDS电路产生相应的DAC刷新时钟(0~1MHz,步进0.02Hz),DAC输出波形经缓冲放大、低通滤波、放大输出。

输出的波形频率为0.1Hz(DC)~1MHz(-3dB),频率分辨率为0.01Hz。

本系统主要由五部分组成:(1)上位机。

主要功能是利用仿真软件(如CVI、MATLAB、VB等)产生所需波形数据,并通过USB接口下载到波形发生器中,其次就是存储USB2.0接口芯片的驱动程序。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

任意波形发生器设计-CAL-FENGHAI-(2020YEAR-YICAI)_JINGBIAN学号:毕业设计题目:任意波形发生器设计作者刘慧届别2016院部物理与电子学院专业电子科学与技术指导老师易立华职称副教授完成时间摘要任意波形发生器(Arbitrary Waveform Generator,AWG)作为一种多波型的信号发生器,它不仅可以产生锯齿波、正弦波等常规波形,而且还能表现出载波调制的多样化特点,使波形发生调幅、调相、调频和脉冲调制等。

甚至能利用计算机软件实现波形的编辑,生成用户所需要的任意波形。

任意波形发生器广泛应用于自动控制、电子电路和科学试验领域,是一款给电子测量工作提供符合技术要求的电信号设备。

因此在各个领域都得到迅猛的发展。

本论文设计一款任意波形发生器,该系统由输入模块、FPGA模块、DAC数模转换模块、显示模块4个部分组成。

该设计将虚拟化的仪器技术、串行总线接口技术和直接数字频率合成技术完美地结合在一起,以现场可编程门阵列(FPGA)作为硬件基础,然后再通过逻辑设计、系统软件设计和系统硬件电路设计,实现了一款基于直接数字频率合成技术的低成本、便携式、可扩展的可立即使用的任意波形发生器。

关键词:数字频率合成器;verilog;FPGA;仿真AbstractArbitrary waveform generator (Arbitrary Waveform Generator,AWG) is a multi wave signal generator. It can not only generates a sawtooth wave, sine wave and so on conventional waveform and the diversification of the modulated carrier, so that the waveform occurrence amplitude modulation, phase modulation, frequency modulation and pulse modulation. Can even use computer software to realize the waveform of the editor, the user needs to generate arbitrary waveform. Arbitrary waveform generator is widely used in the field of automatic control, electronic circuit and scientific experiment. It is an electrical signal equipment which meets the technical requirements for electronic paper designs an arbitrary waveform generator, which is composed of 4 parts, input module, FPGA module, DAC module and display module. The design the virtual instrument technology, serial bus interface technology and direct digital frequency synthesis technology perfect combination together, convertible to field programmable gate array (FPGA) as the basis of hardware, and then through the logic design, system software design and the hardware circuit design, and the implementation of a arbitrary waveform generator based on direct digital frequency synthesis technology of low cost, portable, scalable and can be immediately used.Keywords: Digital frequency synthesizer; Verilog; FPGA;Simulation目录摘要................................................................................................. 错误!未定义书签。

Abstract ........................................................... 错误!未定义书签。

错误!未定义书签。

第一章绪论................................................................................. 错误!未定义书签。

引言........................................................................................... 错误!未定义书签。

任意波形发生器国内外发展现状.......................................... 错误!未定义书签。

问题的提出.............................................................................. 错误!未定义书签。

主要研究工作及内容安排...................................................... 错误!未定义书签。

第二章直接数字频率合成器原理及性能分析.............................. 错误!未定义书签。

直接数字频率合成技术的基本原理...................................... 错误!未定义书签。

DDS技术的性能分析.............................................................. 错误!未定义书签。

第三章 FPGA设计流程.................................................................... 错误!未定义书签。

FPGA简介................................................................................ 错误!未定义书签。

FPGA的优点............................................................................ 错误!未定义书签。

FPGA的设计结构.................................................................... 错误!未定义书签。

第四章针对任意波形发生器的系统设计...................................... 错误!未定义书签。

系统设计.................................................................................. 错误!未定义书签。

FPGA的模块划分.................................................................... 错误!未定义书签。

时钟模块.......................................................................... 错误!未定义书签。

D/A转换模块 .................................................................. 错误!未定义书签。

48位寄存器设计 ...................................................................... 错误!未定义书签。

地址发生器模块.............................................................. 错误!未定义书签。

波形数据存储器设计 ............................................................... 错误!未定义书签。

任意波形输出模块.......................................................... 错误!未定义书签。

任意波形发生器的FPGA实现............................................... 错误!未定义书签。

第五章总结与展望.......................................................................... 错误!未定义书签。

参考文献........................................................................................... 错误!未定义书签。

致谢................................................................................................. 错误!未定义书签。

附录................................................................................................. 错误!未定义书签。

第一章绪论引言波形发生器是我们生活中一种十分常见的电子测试仪器,能够为待测电路形成需要的数据信号,不仅具有精度很高、很好的稳定性、操作很简单等众多优点,而且还能对波形、波形的频率、波形的幅值和波形图的状态控制,甚至被用来虚拟出各种各样复杂而繁琐的信号。