倍流同步整流在DCDC变换器中工作原理分析

一种采用倍流同步整流的高效率AC_DC变换器.Stamped

37

8

通信电源技术

20 08 年 1月 25 日第 25 卷第 1 期

Telecom Powe r Technologie s Jan. 25 , 20 08 , Vol. 25 No. 1

图 3 各模态等效电路图

2. 2 实现主开关管 ZVS 的条件 由电路的工作过程分析中可以知道 ,开关管 Q 1实 现 Z VS的条件为 :

开关管 Q2实现 Z V S的条件是 :

I 1 L O2 2 1 2 Lr ( + I ≥ ( Cp1 + Cp2 ) Ucb L in ) 2 n 2

( 4)

很明显 , Q1零压开通的条件比 Q 2零压开通的条件 要苛刻 ,因此 , 相对于 Q2 来说 , Q1 实现零压开通更难一 些

[4]

。 在设计中参数设计应满足 :

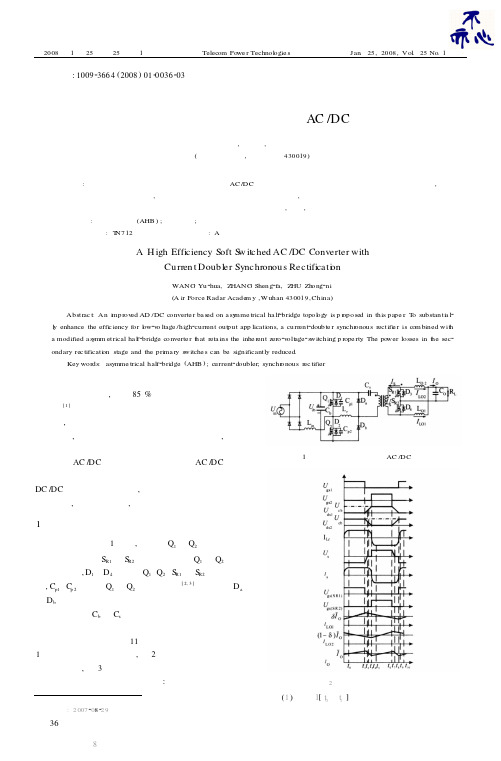

图 1 采用 倍流 同步 整流的 AC /DC 变换器

1 电路拓扑和工作原理

电路拓扑如图 1 所示 , 开关管 Q1 和 Q2交替互补导 通 。同步整流管 SR1和 SR2 分别与开关管 Q1 和 Q2 同步 开通和关闭 , D1 ~D 4分别是 Q1 、 Q2 、 SR1 和 SR2 的体二极 管 , Cp1 、 Cp 2分别是 Q1 和 Q2的寄生电容 [ 2, 3 ] 。二极管 D a 和 D b用来抑制谐振电感与变压器分布电容 之间的震 荡 。假定电容 C b和 Cs足够大以至于电容两端电压近 似于恒定不变 。 电路工作过程分为 11 个模态进行分析 。基于图

汪育华 等 : 一种采用倍流同步整流的 高效率 AC /DC变换器

Telecom Powe r Technologie s Jan. 2 5, 200 8 , Vol. 2 5 No. 1

[课程]全桥DCDC变换器平均电流控制模式控制分析

![[课程]全桥DCDC变换器平均电流控制模式控制分析](https://img.taocdn.com/s3/m/b696a41b854769eae009581b6bd97f192279bf0c.png)

一种大电流输出的全桥DC/DC变换器平均电流控制模式控制分析2009年09月21日作者:王少坤来源:《中国电源博览》编辑:樊晓琳摘要:倍流整流电路能够降低变压器副边的电流,特别适合于大电流输出的应用。

本文分析和研究了平均电流模式控制策略在带有倍流整流电路的大电流输出全桥DC/DC变换器中的应用。

并进行了仿真和实验。

关键词:DC/DC变换器;电流控制;倍流整流Abstract: The two inductor rectifier circuit offers reduced secondary side current rating and is most suitable for high current applications. The paper analysis of average current mode Control on a high current output FB DC/DC Converter with two inductor rectifier circuit. Simulations and experiments ensure the rightness of the method.Key Words: FB DC/DC Converter; Current-mode Control; Compensation Network0 引言相比电压控制模式控制,电流控制模式通过对电感电流的相位补偿,大大改善了电源的动态响应和并联特性。

倍流整流(CDR)能够降低变压器副边的电流,减少其损耗;同时它有两个输出滤波电感,流经每个电感的电流只有负载电流的一半,输出滤波电感的损耗也小,特别适用于现今越来越多的需要大电流输出的场合。

本文对一种带倍流整流电路的全桥DC/DC变换器的平均电流模式控制进行了分析和仿真。

1 两种电流控制模式的优缺点比较电流控制模式有两种类型:峰值电流模式控制(PCMC)和平均电流模式控制(ACMC)。

倍流同步整流在DC-DC变换器中工作原理分析

倍流同步整流在DC/DC变换器中工作原理分析

在低压大电流变换器中倍流同步整流拓扑结构已经被广泛采用。

就其工作原理进行了详细的分析说明,并给出了相应的实验和实验结果。

关键词:倍流整流;同步整流;直流/直流变换器;拓扑

0 引言

随着微处理器和数字信号处理器的不断发展,对芯片的供电电源的要求越

来越高了。

不论是功率密度、效率和动态响应等方面都有了新要求,特别是要求输出电压越来越低,电流却越来越大。

输出电压会从过去的3.3V 降低到

1.1~1.8V 之间,甚至更低[1]。

从电源的角度来看,微处理器和数字信号处理器等都是电源的负载,而且它们都是动态的负载,这就意味着负载电流会在瞬间变化很大,从过去的13A/μs 到将来的30A/μs~50A/μs[2]。

这就要求有能够输出电压低、电流大、动态响应好的变换器拓扑。

而对称半桥加倍流同步整流结构的DC/DC 变换器是最能够满足上面的要求的[3]。

本文对这种拓扑结构的变换器的工作原理作出了详细的分析说明,实验结

果证明了它的合理性。

1 主电路拓扑结构

主电路拓扑如图1 中所示。

由图1 可以看出,输入级的拓扑为半桥电路,

而输出级是倍流整流加同步整流结构。

由于要求电路输出低压大电流,则倍流同步整流结构是最合适的,这是因为:

图1 主电路拓扑

1)变压器副边只需一个绕组,与中间抽头结构相比较,它的副边绕组数只有中间抽头结构的一半,所以损耗在副边的功率相对较小;

2)输出有两个滤波电感,两个滤波电感上的电流相加后得到输出负载电流,。

dcdc整流器的工作原理

dcdc整流器的工作原理DC-DC整流器的工作原理1. 简介DC-DC整流器是一种电力转换器,用于将直流电源的电压转换为不同的直流电压。

它在各种电子设备中广泛应用,如计算机、手机和汽车电子等。

2. 基本原理DC-DC整流器的工作原理基于电感和开关器件的组合。

它主要包括输入滤波、变换、输出滤波和控制部分。

3. 输入滤波在电源输入端,使用电容器对输入信号进行滤波,以消除输入电压中的高频噪声和干扰。

这样可以保证后续步骤的正常运行。

4. 变换在变换环节,使用开关器件和电感进行能量转换。

这个过程主要分四个步骤:打开开关、储能、关断开关和能量释放。

5. 打开开关开关器件切换到导通状态,电容器开始充电并储能。

6. 储能当开关器件导通时,电感中储存的能量逐渐增加。

同时,电容器内的电压也逐渐上升。

7. 关断开关为了改变输出电压,开关器件必须被关闭。

当开关断开,电感上的电流开始流动,并将电感储存的能量传递到电容器。

8. 能量释放当开关器件断开时,电容器释放储存的能量,使其通过输出滤波器并输出至负载。

这样就实现了输入电压向输出电压的转换。

9. 输出滤波输出滤波器对输出电压进行滤波,以去除剩余的高频噪声和干扰,并提供稳定的输出电压给负载。

10. 控制部分DC-DC整流器的控制部分是整个系统的大脑,通过控制开关器件的导通和断开,使其输出电压保持稳定。

常见的控制方法包括脉宽调制(PWM)和电流/电压反馈等。

11. 结论DC-DC整流器的工作原理是基于电感和开关器件的能量转换。

通过合理的设计和控制,可以实现直流电压的转换和稳定输出。

这种电力转换器在现代电子设备中起着重要的作用,为各种应用提供了可靠的电源。

以上是DC-DC整流器的工作原理的简要介绍,希望能帮助你更好地理解这一关键技术。

AC-DC转换器的工作原理

AC/DC转换器的工作原理AC-AlternaTIngcurrent是交流的意思,DC-Directcurrent是直流的意思,AC/DC 变换是将交流变换为直流,AC/DC转换器就是将交流电变为直流电的设备,其功率流向可以是双向的,功率流由电源流向负载的称为“整流”,功率流由负载返回电源的称为“有源逆变”。

一:AC/DC转换器的工作原理-工作原理交流电转换为直流电称为整流,而直流电转换为交流电称为逆变。

逆变要比整流复杂得多。

常用的有两种方法,一种是先通过SPWM方式,调制出正弦波波形(如果方波也可以的话,这步可以省略),然后通过一个H桥切换输出电压极性,这要求H 桥的切换与SPWM电路同步,技术上较复杂但这种方式的效率好像很高,所以不少逆变器都是这种方式。

将直流电源转变为交流电使用的设备就是叫“逆变器”原理基本是将直流电送到用于逆变输出的三极管,利用接在该管子回路上的变压器等元器件对管子形成正反馈而使管子产生“震荡”电流(起振)而变为交流输出,如果需要比较“严格”的电流输出波形,则还要接入有关电子元器件,组成对输出波形进行整形的电路。

一般通过二极管整流电路或电子开关电路,都可将交流电转换为直流电。

AC/DC转换器的工作过程图整流电路,是将工频交流电转换为脉动直流电;滤波电路,将脉动直流中的交流成分滤除,减少交流成分,增加直流成分;稳压电路,采用负反馈技术,对整流后的直流电压进一步进行稳定。

1整流--即把交流调整成直流,换句话就是使交流的正玄波调整到的X轴上方。

但是现在还只是脉冲的。

主要元件是二极管。

整流方式:全波整流(桥式整流,有专门的元件或用4个二极管)、半波整流(x以下的波损失掉,电流不是连续的。

用一个二极管做)。

2滤波--把波形调整成平稳的直流(可用电容)另:根据需要的电压,可以在整流之前做变压。

一般来讲整流电路有如下几种方法:半波整流电路:半波整流就是利用二极管的单向导电性能,使经变压器出来的电压Vo只有半个周期可以到达负载,如下:单相桥式整流电路是最基本的将交流转换为直流的电路,在分析整流电路工作原理时,整流电路中的二极管具有单向导电性。

倍流整流在低压大电流开关电源中的应用

倍流整流在低压大电流开关电源中的应用崔晶【摘要】在隔离型低压大电流输出的DC/DC变换器中,同步整流电路中存在着纹波电流大的问题。

针对此问题,提出了倍流同步整流电路,与传统的整流电路相比,大大减小了纹波电流。

通过实验验证了该方案的有效性和优越性。

%In this paper, the merits and limitations of current -doubler rectifier are analyzed and synthesized. The current-doubler rectifier is compared with the other second-side rectifier. The conclu-sion has been drawn that the current-doubler rectifier is suitable for the low-voltage high-current out-put DC-DC converter.【期刊名称】《工业仪表与自动化装置》【年(卷),期】2015(000)004【总页数】4页(P78-80,84)【关键词】倍流整流电路;DC-DC;拓扑【作者】崔晶【作者单位】西安铁路职业技术学院,西安710014【正文语种】中文【中图分类】TM910 引言随着微处理器和数字信号处理器的不断发展,对芯片供电电源的要求越来越高,不论是功率密度、效率和动态响应等方面都有了新要求,特别是要求输出电压越来越低,电流却越来越大。

这就要求具有输出电压低、电流大、动态响应快的变换器。

同步整流可使变换器损耗减小,但电流纹波大的问题比较难解决。

因此该文提出了倍流同步整流电路,很好地解决了电流纹波大的问题。

1 同步整流方案的选择由于输出为低压大电流,因此副边整流电路的选用尤为重要,在常用的4种副边拓扑结构中,倍流整流电路具有如下特点:1)全波和倍流整流中整流管的导通损耗远比半波整流小。

倍压整流电路的工作原理及电路分析(史上最全)

倍压整流电路的工作原理及电路设计在某些电子设备中,需要高压(几千伏甚至几万伏)、小电流的电源电路。

一般都不采用前面讨论过的几种整流方式,因为那种整流电路的整流变压器的次级电压必须升的很高,圈数势必很多,绕制困难。

这里介绍的倍压整流电路,在较小电流的条件下,能提供高于变压器次级输入的交流电压幅值数倍的直流电压,可以避免使用变压比很高的升压变压器,整流元件的耐压相对也可较低,所以这类整流电路特别适用于需要高电压、小电流的场合。

倍压整流是利用电容的充放电效应工作的整流方式,它的基本电路是二倍压整流电路。

多倍压整流电路是二倍压电路的推广。

1、二倍压整流电路(1)桥式二倍压整流电路图1所示电路是桥式倍压整流电路,图1的(1)和(2)为同一电路的两种不同画法。

在这里,用两个电容器取代了全波桥式整流电路中的两只二极管。

整流管D1、D2在交流电的两个半周分别进行半波整流。

各自对电容C1和C2充电。

由负载RL与C1、C2回路看,两个电容是接成串联的。

负载RL 上的直流电能是由C1、C2共同供给的。

当e2正半周时,D1导通,如果负载电阻RL很大,即流过RL的电流很小的话,整流电流i D1使C1充电到2E2的电压,并基本保持不变,极向如图中所示。

同样,当e2负半周时,经D2对C2也充上2 E2的电压,极向如图中所示。

跨接在两个串联电容两端的负载R L 上的电压UL=UC1+UC2,接近于e2幅值的两倍。

所以称这种电路为二倍压整流电路。

实际上,在正半周C1被充电到幅值2 E2后,D1随即截止,C1将经过RL对C2放电,UC1将有所降低。

在负半周,当C2被充电到幅值2 E2后,D2截止,C2的放电回路是由C1至RL ,UC2也应有所降低。

这样,UC1和UC2的平均值都应略低于2 E2,也即负载电压是不到次级绕组电压幅值的两倍的。

只有在负载RL 很大时,UL≈2 E2。

UC1、UC2及UL的变化规律如图2所示。

这种整流电路中每个整流元件承受的最大反向电压是22 E2,电容器C1、C2上承受的电压为2 E2,这里的电容器同时也起到滤波的作用。

倍压整流电路原理讲解

倍压整流电路原理讲解

倍压整流电路是一种简单有效的电路,它在电源输出端输出一个比输入电压更高的电压,其原理是通过利用开关电路的原理,将低压的输入电压转换为更高的电压。

倍压整流电路的组成由恒定阻抗、正反变换以及调节器组成,其工作原理如下:首先,恒定阻抗电路负责通过放大增加电流,由此产生了放大倍数,然后由正反变换电路将低压输入电压反转为更高的输出电压,其中包括电流变换器、压降变换器和旋转变换器的基础电路结构;最后,调节器将反转的高压输出电压经过调节,以保持输出电压恒定不变。

整流电路通常用于调节电压的大小,调节电压的大小可以达到稳定输出和节省能源的效果。

它也可以用作电源调节、照明调节、电机调节等,对于需要电路设计的应用方面有着重要的作用。

在实际应用中,倍压整流电路有许多优点。

首先,它具有耐用性强、结构简单等特点,使用起来非常方便;其次,它可以实现自动调节和无限调节,使用者可以根据实际需要调整输出电压;最后,倍压整流电路的精度高,可以实现稳定的输出,且节省能源。

倍压整流电路有着重要的应用价值,尤其在电源调节、照明调节、电机调节等方面的应用。

此外,倍压整流电路可以根据实际需要调节电压大小,可以实现输出稳定。

但是,倍压整流电路也有一些局限性,如调节范围有限、损耗大等,这些局限性在实际应用中需要特别注意。

无论是电源调节、照明调节、电机调节还是其他领域的应用,倍

压整流电路都具有重要的意义,有助于提高输出精度和节约能源。

可以看出,倍压整流电路是一种简单有效的电路,具有重要的应用价值,且能够满足不同类型的应用需求。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

倍流同步整流在DC/DC变换器中工作原理分析

[作者:佚名转贴自:未知点击数:13 更新时间:2005-6-16 文章录入:chinlea ]摘要:在低压大电流变换器中倍流同步整流拓扑结构已经被广泛采用。

就其工作原理进行了详细的分析说明,并给出了相应的实验和实验结果。

关键词:倍流整流;同步整流;直流/直流变换器;拓扑

0 引言

随着微处理器和数字信号处理器的不断发展,对芯片的供电电源的要求越来越高了。

不论是功率密度、效率和动态响应等方面都有了新要求,特别是要求输出电压越来越低,电流却越来越大。

输出电压会从过去的3.3V降低到1.1~1.8V之间,甚至更低[1]。

从电源的角度来看,微处理器和数字信号处理器等都是电源的负载,而且它们都是动态的负载,这就意味着负载电流会在瞬间变化很大,从过去的13A /μs到将来的30A/μs~50A/μs[2]。

这就要求有能够输出电压低、电流大、动态响应好的变换器拓扑。

而对称半桥加倍流同步整流结构的DC/DC变换器是最能够满足上面的要求的[3]。

本文对这种拓扑结构的变换器的工作原理作出了详细的分析说明,实验结果证明了它的合理性。

1 主电路拓扑结构

主电路拓扑如图1中所示。

由图1可以看出,输入级的拓扑为半桥电路,而输出级是倍流整流加同步整流结构。

由于要求电路输出低压大电流,则倍流同步整流结构是最合适的,这是因为:

图1 主电路拓扑

1)变压器副边只需一个绕组,与中间抽头结构相比较,它的副边绕组数只有中间抽头结构的一半,所以损耗在副边的功率相对较小;

2)输出有两个滤波电感,两个滤波电感上的电流相加后得到输出负载电流,而这两个电感上的电流纹波有相互抵消的作用,所以,最终得到了很小的输出电流纹波;

3)流过每个滤波电感的平均电流只有输出电流的一半,与中间抽头结构相比较,在输出滤波电感上的损耗明显减小了;

4)较少的大电流连接线(high current inter-connection),在倍流整流拓扑中,它的副边大电流连接线只有2路,而在中间抽头的拓扑中有3路;

5)动态响应很好。

它唯一的缺点就是需要两个输出滤波电感,在体积上相对要大些。

但是,有一种叫集成磁(integrated magnetic)的方法,可以将它的两个输出滤波电感和变压器都集成到同一个磁芯内,这样可以大大地减小变换器的体积。

2 电路基本工作原理

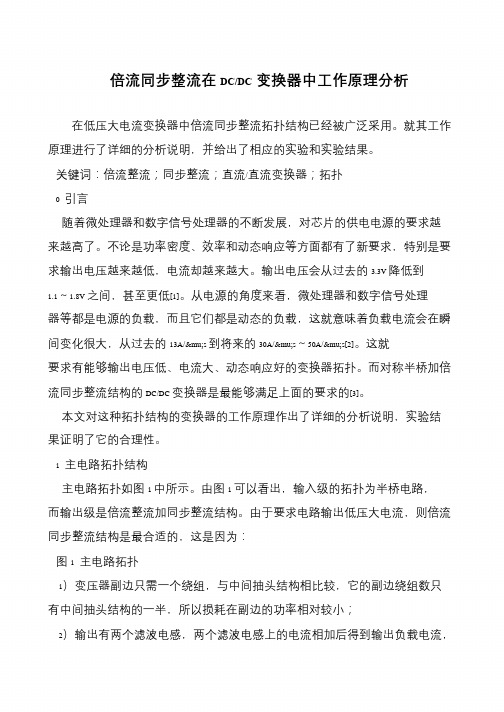

电路在一个周期内可分为4个不同的工作模式,如图2所示,理想的波形图如图3所示。

(a) 模式1[t0-t1]

(b) 模式2[t1-t2]

(c) 模式3[t2-t3]

(d) 模式4[t3-t4]图2 工作模式图

图3 工作波形图

L o1,L o2 2.2μH

C o1500μF/2.5V

磁芯(core) R-42216-EC

匝比(turnratio) 10:1

漏感(L k) 600nH

开关频率(f s) 310kHz

图4所示的是原边两个主管和副边同步管的门极驱动波形。

通道R2表示S1的驱动波形;通道R1表示S2的驱动波形;通道1是同步管S R2的驱动波形;通道2是同步管S R1的驱动波形。

由表1可以看到,变压器漏感L k=600nH。

所以,在电流较小的时候,存储在漏感中的能量不是很大,因而开关管在关断后的漏感和开关管输出结电容间的振荡不是很大,图5所示的是在负载电流I o=5A时的S2漏源极v ds2的波形。

图4 门极驱动波形

图5 v ds2波形(I o=5A)

当变换器以满载I o=25A输出时,变压器原边的振荡就明显地增大。

这是因为,当输出电流增大的时候,反映到原边的电流也会增大,

所以,这个时候存储在变压器漏感中的磁能就会增大,在t off期间内振荡的时间较长,幅值也较大,如图6所示。

在大电流的拓扑中,这种振荡的损耗也是不可忽略的。

图7给出了变换器的效率曲线图,最大值出现在I o=15A时。

图6 v ds2波形(I o=25A)

图7 效率曲线图

4 结语

对适于低压大电流的整流拓扑(倍流整流+同步整流)的工作原理作了详细的说明,并在分析的基础上,给出了相应的实验结果。

证明了这种整流拓扑在低压大电流DC/DC变换器中的合理性。

随着对电源性能要求的提高,这种整流拓扑将会越来越广泛地被采用。

但应该指出的是,变压器的漏感应该尽量地减小,以减少原边振荡。