EDA课后答案(适用于朱正伟《EDA技术及应用》)

《EDA技术》习题(解答)5

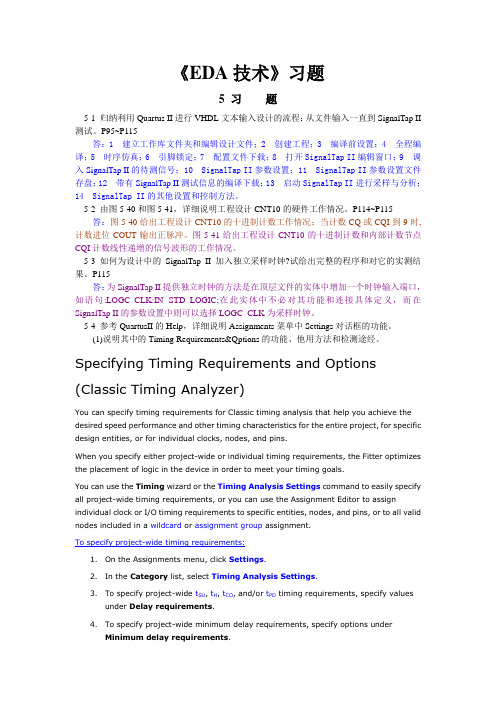

《EDA技术》习题5 习题5-1 归纳利用Quartus II进行VHDL文本输入设计的流程:从文件输入一直到SignalTap II 测试。

P95~P115答:1 建立工作库文件夹和编辑设计文件;2 创建工程;3 编译前设置;4 全程编译;5 时序仿真;6 引脚锁定;7 配置文件下载;8 打开SignalTap II编辑窗口;9 调入SignalTap II的待测信号;10 SignalTap II参数设置;11 SignalTap II参数设置文件存盘;12 带有SignalTap II测试信息的编译下载;13 启动SignalTap II进行采样与分析;14 SignalTap II的其他设置和控制方法。

5-2 由图5-40和图5-41,详细说明工程设计CNT10的硬件工作情况。

P114~P115答:图5-40给出工程设计CNT10的十进制计数工作情况;当计数CQ或CQI到9时,计数进位COUT输出正脉冲。

图5-41给出工程设计CNT10的十进制计数和内部计数节点CQI计数线性递增的信号波形的工作情况。

5-3 如何为设计中的SignalTap II加入独立采样时钟?试给出完整的程序和对它的实测结果。

P115答:为SignalTap II提供独立时钟的方法是在顶层文件的实体中增加一个时钟输入端口,如语句:LOGC_CLK:IN STD_LOGIC;在此实体中不必对其功能和连接具体定义,而在SignalTap II的参数设置中则可以选择LOGC_CLK为采样时钟。

5-4 参考QuartusII的Help,详细说明Assignments菜单中Settings对话框的功能。

(1)说明其中的Timing Requirements&Qptions的功能、他用方法和检测途经。

Specifying Timing Requirements and Options (Classic Timing Analyzer)You can specify timing requirements for Classic timing analysis that help you achieve the desired speed performance and other timing characteristics for the entire project, for specific design entities, or for individual clocks, nodes, and pins.When you specify either project-wide or individual timing requirements, the Fitter optimizes the placement of logic in the device in order to meet your timing goals.You can use the Timing wizard or the Timing Analysis Settings command to easily specify all project-wide timing requirements, or you can use the Assignment Editor to assign individual clock or I/O timing requirements to specific entities, nodes, and pins, or to all valid nodes included in a wildcard or assignment group assignment.To specify project-wide timing requirements:1.On the Assignments menu, click Settings.2.In the Category list, select Timing Analysis Settings.3.To specify project-wide t SU, t H, t CO, and/or t PD timing requirements, specify valuesunder Delay requirements.4.To specify project-wide minimum delay requirements, specify options underMinimum delay requirements.5.Under Clock Settings, select Default required fmax.6.In the Default required fmax box, type the value of the required f MAX and select atime unit from the list.7.If you want to specify options for cutting or reporting certain types of timing pathsglobally, enabling recovery/removal analysis, enabling clock latency, and reporting unconstrained timing paths, follow these steps:8.Click OK.To specify clock settings:1.On the Assignments menu, click Settings.2.In the Category list, select Timing Analysis Settings.3.Under Clock Settings, click Individual Clocks.4.Click New.5.In the New Clock Settings dialog box, type a name for the new clock settings in theClock settings name box.6.To assign the clock settings to a clock signal in the design, type a clock node name inthe Applies to node box, or click Browse... to select a node name using the Node Finder.7.If you want to specify timing requirements for an absolute clock, follow these steps:8.If you have already specified timing requirements for an absolute clock, and you wantto specify timing requirements for a derived clock, follow these steps:9.In the New Clock Settings dialog box, click OK.10.In the Individual Clocks dialog box, click OK.11.In the Settings dialog box, click OK.To specify individual timing requirements:1.On the Assignments menu, click Assignment Editor.2.In the Category bar, select Timing to indicate the category of assignment you wishto make.3.In the spreadsheet, select the To cell and perform one of the following steps:•Type a node name and/or wildcard that identifies the destination node(s) you want to assign.•Double-click the To cell and click Node Finder to use the Node Finder to enter a node name.•Double-click the To cell, click the arrow that appears on the right side of the cell, and click Select Assignment Group to enter an existing assignmentgroup name.4.To specify an assignment source, repeat step 3 to specify the source name in theFrom cell.5.In the spreadsheet, double-click the Assignment Name cell and select the timingassignment you wish to make.6.For assignments that require a value, double-click the Value cell and type or selectthe appropriate assignment value.To specify timing analysis reporting restrictions:1.On the Assignments menu, click Settings.2.In the Category list, double-click Timing Analysis Settings.3.Click Timing Analyzer Reporting.4.To specify the range of timing analysis information reported, specify one or moreoptions in the Timing Analyzer Reporting page.5.Click OK.(2)说明其中的Compilation Process的功能和使用方法。

EDA完整版答案

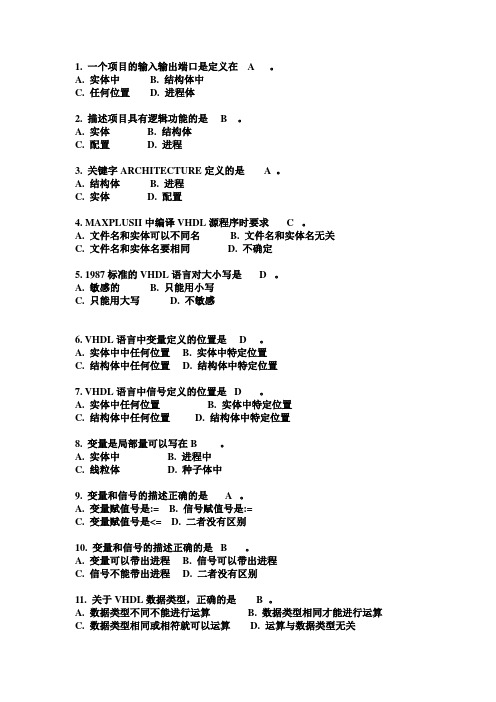

1. 一个项目的输入输出端口是定义在 A 。

A. 实体中B. 结构体中C. 任何位置D. 进程体2. 描述项目具有逻辑功能的是 B 。

A. 实体B. 结构体C. 配置D. 进程3. 关键字ARCHITECTURE定义的是 A 。

A. 结构体B. 进程C. 实体D. 配置4. MAXPLUSII中编译VHDL源程序时要求 C 。

A. 文件名和实体可以不同名B. 文件名和实体名无关C. 文件名和实体名要相同D. 不确定5. 1987标准的VHDL语言对大小写是 D 。

A. 敏感的B. 只能用小写C. 只能用大写D. 不敏感6. VHDL语言中变量定义的位置是 D 。

A. 实体中中任何位置B. 实体中特定位置C. 结构体中任何位置D. 结构体中特定位置7. VHDL语言中信号定义的位置是 D 。

A. 实体中任何位置B. 实体中特定位置C. 结构体中任何位置D. 结构体中特定位置8. 变量是局部量可以写在 B 。

A. 实体中B. 进程中C. 线粒体D. 种子体中9. 变量和信号的描述正确的是 A 。

A. 变量赋值号是:=B. 信号赋值号是:=C. 变量赋值号是<=D. 二者没有区别10. 变量和信号的描述正确的是 B 。

A. 变量可以带出进程B. 信号可以带出进程C. 信号不能带出进程D. 二者没有区别11. 关于VHDL数据类型,正确的是 B 。

A. 数据类型不同不能进行运算B. 数据类型相同才能进行运算C. 数据类型相同或相符就可以运算D. 运算与数据类型无关12. 下面数据中属于实数的是 B 。

A. 4.2B. 3C. …1‟D. “11011”13. 下面数据中属于位矢量的是 D 。

A. 4.2B. 3C. …1‟D. “11011”14. 关于VHDL数据类型,正确的是 B 。

A. 用户不能定义子类型B. 用户可以定义子类型C. 用户可以定义任何类型的数据D. 前面三个答案都是错误的15. 可以不必声明而直接引用的数据类型是 C 。

EDA技术使用教程课后答案第4章

【例4-8】 】 ... IF a1 > b1 THEN q1 <= '1' ; ELSE q1 <= '0' ; END IF; ...

的电路图( 综合) 图4-6 例4-8的电路图(Synplify综合) 的电路图 综合

图4-2 mux21a结构体 结构体

KX

康芯科技

4.1 多路选择器的 多路选择器的VHDL描述 描述

4.1.1 2选1多路选择器的 选 多路选择器的 多路选择器的VHDL描述 描述

【例4-1】 】 ENTITY mux21a IS PORT ( a, b : IN BIT; s : IN BIT; y : OUT BIT ); END ENTITY mux21a; ARCHITECTURE one OF mux21a IS BEGIN y <= a WHEN s = '0' ELSE END ARCHITECTURE one ;

KX

康芯科技

4.2 寄存器描述及其 寄存器描述及其VHDL语言现象 语言现象

4.2.2 VHDL描述的语言现象说明 描述的语言现象说明 2. 设计库和标准程序包

LIBRARY LIBRARY WORK ; STD ;

图4-4 D触发器

USE STD.STANDARD.ALL ; 使用库和程序包的一般定义表式是: 使用库和程序包的一般定义表式是: LIBRARY USE <设计库名>; 设计库名>

< 设计库名>.<程序包名>.ALL ; 设计库名> 程序包名>

eda技术作业参考答案.doc

5-14library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity div is port(clk,RESET: in std_logic;outl,out2:out std_logic);end div;architecture div_16 of div issignal ent: std_logic_vector(3 downto 0);beginprocess(clk)beginif reset=T thencnt<=u OOOO n;elsif (clk'event and clk=T) then cnt<=cnt+T;end if;end process;outl<=T when cnt=15 else 'O';--不等out2<=cnt(3); -正负脉宽相等end div_16;5-11library ieee;use ieee.std_logic_l 164.all;entity s_machine is port(clk:in std_logic;din:in std_logic_vector( 1 downto 0); dout:out std_logic_vector( 1 downto 0));end s_machine;architecture a of s_machine istype state is (s0,sl,s2);signal current_state,next_state:state;beginprocess(din,curret_state) -次态译码器与输出译码器描述begincase current_state iswhen sO =>讦(din = "00") then next_state <= sO; doutv="00'';elsif (din = "01") then next_state <= s2; dout<=,,10,?;elsif (din = TO") then next_state <= s2; dout<=,,lF,;end if;when si =>if (din = “00") then next_state <= si; doutv="00''; elsif(din = "01") then next_state <= sO; doutv=''00"; elsif(din = TO") then next_state <= s2; dout<=,,10,?; end if;when s2 =>讦(din = "00") then next_state <= s2; doutv="00''; elsif(din = "01") then next_state <= si; doutv="00''; elsif(din = TO") then next_state <= sO; doutv=''00"; end if;end case;End process;process(clk) -状态寄存器描述beginif (clk?event and clk== '1') then current_state<=next_state;end if;End process;End a;5-10(1)entity h_sub isport (x, y: in BIT ;diff, sub_out: out bit);end h_sub; Architecture A of h_sub isbegindiff <= x xor y; sub_out <= not X and Y;end A;ENTITY F_SUB ISPORT(X, Y, SUB_IN: IN BIT;DIFF, SUB_OUT: OUT BIT);ENDF_SUB;ARCHITECTURE ART OF F_SUB ISCOMPONENT H_SUBPORT(X, Y: IN BIT;DIFF, SUB_OUT: OUT BIT);END COMPONENT;SIGNAL SI, S2, S3: BIT;BEGINUl: H_SUB PORT MAP (X=>X, Y=>Y, DIFF=>S1, SUB_OUT=>S2);U2 : H_SUB PORT MAP (X=>S1 , Y=>SUB_IN ,DIFF=>DIFF, SUB_OUT=>S3);SUB_OUT<=S2 OR S3;END ARCHITECTURE ART;⑵.entity f^sub isport ( x, y, sub_in: in bit;diff, sub_out: out bit);end f_sub;architecture func of 匚sub isbeginprocess(x, y, sub_in)variable con: bit_vector(l downto 0);variable com: bit_vector(2 downto 0);begincom:= x & y & sub_in;if (com = “000") then con := “00";elsif (com = "Oil") then con := "01";elsif (com 二"100") then con :二"10";elsif (com 二"101") then con := "00";elsif (com = T10") then con := “00";else con := T1";end if;diff <= con(l); sub_out <= con(0);end process;end func;⑶entity subtracter isport ( a, b : in bit_vector(7 dowto 0);sub_in : in bit;diff: out bit_vector(7 dowto 0); sub_out: out bit); end subtracter;architecture stru of subtracter iscomponent H_subport ( x, y, sub_in: in bit; diff, sub_out: out bit);end component; signal sub: bit_vector(8 downto 0); begingO: for I in 0 to 7 generateu_inst: H_subbport map(a(i), b(i),sub(i),diff(i), sub(i+l));end generate;sub(0) <= sub_in;sub_out <=sub(8);end stru;5-8library IEEE:use IEEE. Std _logic_ 1164.all:use IEEE. STD_LOGIC _UNSIGNED.all:entity seq_gen isport(CIK, RESET: in STD_LOGIC:Y0: out STD_LOGIC_vector(9 downto 0)):End seq_gen;Architecture rtl of seq_gen isSignal CNT: STD_LOGIC_VECTOR(3 downto 0);beginprocess(CLK, RESET)begin〜 ifRESET=,l,thenCNT v=''0000";Elsif CLK'event and CLK=T thenIfcnt="1001''thenCNTv=”000";elseCNT<=CNT +T;End if;End if;End process ;With CNT SelectY0<=,,000000000F, when ” 0000”,“0000000010” when " 0001”,“0000000100” when ” 0010”,“0000001000” when ” 0011”,“0000010000” when ” 0100”,^^0000100000^^ when ” 0101”,“0001000000” when ” 0110”,“0010000000” when ” 0111”,4<010*******,? when ” 1000”,T 000000000’' when others ;end rtl;5-7library IEEE;use IEEE.Std _logic_ 1164.all;use IEEE.std_logic_unsigned.al 1; entity counter isport(clk,rst,ml,m0:in std_logic;y:out std_logic_vector (4 downto 0));End counter;Architecture rtl of counter isSignal sei: std_logic_vector (1 downto 0);Signal per,ent: std_logic_vector (4 downto 0);beginsel<=ml&mO;With sei Selectperv=”1001(F when “0(F,"OOOll" when “01",,,0100r, when TO","00101" when others;process(reset,clk)beginif reset=T thencnt<=n00000n;elsif (clk'event and clk=r)thenif ent = pre thencnt<=H00000u;elsecnt<=cnt+T;end if;end if;end process;y<=cnt;end rtl;2-1判断下列标示符是否合法,如果有误指出原因:16#OFA#, 10#12F#, 8#7989#, 8#356#, 2#0101010#, 74HC245,\74HC574\, CLR/RESET, \IN, 4/SCLKX, DI00% 16#OFA#10#12F# 8#7989# 8#356# 2#0101010# 以上不合法,不能以数字开头和存在#符号。

EDA技术习题集及答案

第一章 EDA概述一、填空题1.2000年推出的Pentium 4微处理器芯片的集成度达——万只晶体管。

2.一般把EDA技术的发展分为——、——和——三个阶段。

3.在EDA发展的——阶段,人们只能借助计算机对电路进行模拟、预测,以及辅助进行集成电路版图编辑、印刷电路板(PcB)布局布线等工作。

4.在EDA发展的——阶段,人们可以将计算机作为单点设计工具,并建立各种单元库,开始用计算机将许多单点工具集成在一起使用。

5.EDA设计流程包括——、——、——和——四个步骤。

6.EDA的设计验证包括——、——和——三个过程。

7.EDA的设计输入主要包括——、——和———。

8.文本输入是指采用——进行电路设计的方式。

9.功能仿真是在设计输入完成之后,选择具体器件进行编译之前进行的逻辑功能验证,因此又称为——。

10.时序仿真是在选择了具体器件并完成布局、布线之后进行的时序关系仿真,因此又称为——或——。

11.当前最流行的并成为1EEE标准的硬件描述语言包括————和——。

12.采用PLD进行的数字系统设计,是基于芯片的设计或称之为——的设计。

13.硬件描述语言HDL给PLD和数字系统的设计带来了更新的设计方法和理念,产生了目前最常用的并称之为——的设计法。

14.EDA工具大致可以分为——、——、———、———和——等五个模块。

15.将硬件描述语吉转化为硬件电路的重要工具软件称为——————。

二、单项选择题1.将设计的系统或电路按照EDA开发软件要求的某种形式表示出来,并送入计算机的过程称为( )。

①设计输入②设计输出③仿真④综合2.一般把EDA技术的发展分为( )几个阶段。

①2 ②3 ③4 ④53.AHDL属于( )描述语言。

①普通硬件②行为③高级④低级4.vHDL属于( )描述语言。

①普通硬件②行为③高级④低级5.包括设计编译和检查、逻辑优化和综合、适配和分割、布局和布线,生成编程数据文件等操作的过程称为( )。

EDA课后习题答案

定义为Net型的变量常被综合为硬件电路中的物理连接,其特点是输出的值 紧跟输入值的变化而变化,因此常被用来表示以assign关键词引导的组合电路描 述。

形成结构,即用SRAM来构成逻辑函数发生器。一个N输入LUT可以实现N个

输1-入8 变就量逻的辑任宏何单逻元辑而功言能,,G如ALN中输的入O“LM与C”、、CNP输LD入中“的异LC或、”F等PG。A中的LUT和

LE的含义和结构特点是什么?它们都有何异同点?

答:输出逻辑宏单元(Output Logic Macro Cell,OLMC),此结构使得

综合器就是能够将一种设计表述形式自动向另一种设计表述形式转换的 计算机程序,或协助进行手工转换的程序。它可以将高层次的表述转化为低 层次的表述,可以将行为域转化为结构域,可以将高一级抽象的电路描述 (如算法级)转化为低一级的电路描述(如门级),并可以用某种特定的 “技术”(如CMOS)实现。

精选ppt课件

1-10 标志FPGA/CPLD逻辑资源的逻辑宏单元包含哪些结构? 答: CPLD( MAX7000S)系列中的 逻辑宏单元由3个功能块组成:逻辑阵列、 乘积项选择矩阵和可编程寄存器,它们可以被单独地配置为时序逻辑和组合逻 辑工作方式。其中逻辑阵列实现组合逻辑,可以给每个逻辑宏单元提供5个乘 积项。“乘积项选择矩阵”分配这些乘积项作为到“或门”和“异或门”的主 要逻辑输入,以实现组合逻辑函数;或者把这些乘积项作为宏单元中寄存器的 辅助输入:清零(Clear)、置位(Preset)、时钟(Clock)和时钟使能控制 (Clock Enable)。 FPGA(Cyclone III)器件的可编程资源主要来自逻辑阵列块LAB,而每个LAB都 由多个逻辑宏单元(Logic Element,LE)构成。LE是Cyclone III FPGA器件 的最基本的可编程单元,LE主要由一个4输入的查找表LUT、进位链逻辑、寄 存器链逻辑和一个可编程的寄存器构成。

eda习题与答案

eda习题与答案

EDA习题与答案

探索性数据分析(EDA)是数据科学中的一项重要技能,通过对数据进行可视化和统计分析,可以帮助我们更好地理解数据的特征和规律。

在实际应用中,我们经常会遇到各种EDA习题,下面就让我们一起来看看一些常见的EDA习题及其答案。

1. 习题:对一组学生的考试成绩进行EDA,包括成绩的分布、平均分、及格率等统计指标。

答案:首先,我们可以绘制成绩的直方图,以了解成绩的分布情况。

然后计算平均分和及格率,可以通过描述性统计方法来实现。

最后,我们还可以使用箱线图来展示成绩的离散程度和异常值情况。

2. 习题:分析一组房屋价格数据,探索价格的变化趋势和影响因素。

答案:首先,我们可以绘制价格随时间变化的折线图,以了解价格的趋势。

然后可以使用相关系数分析价格与其他因素(如面积、地段、装修等)的关系。

最后,可以利用散点图和回归分析来探讨价格与各种因素之间的关联性。

3. 习题:分析一组销售数据,探索销售额的季节性变化和产品销售额的贡献比例。

答案:首先,可以使用折线图或柱状图来展示销售额随时间的变化情况,以了解销售额的季节性变化。

然后,可以计算各个产品在总销售额中的贡献比例,以了解产品销售情况的分布。

通过以上习题及其答案的分析,我们可以看到EDA在实际应用中的重要性和灵活性。

通过对数据进行可视化和统计分析,我们可以更好地理解数据的特征和

规律,为后续的数据建模和决策提供有力支持。

因此,掌握好EDA技能对于数据科学从业者来说至关重要。

EDA技术实用教程课后习题答案(20210110132612)

第一章1- 1 EDA技术与ASIC设计与FPGA开发有什么关系?答:利用EDA技术进行电子系统设计得最后目标就是完成专用集成电路ASIC得设计与实现;FPGA与CPLD就是实现这一途径得主流器件。

FPGA与CPLD通常也被称为可编程专用IC,或可编程ASIC o FPGA与CPLD得应用就是EDA技术有机融合软硬件电子设计技术、SoC(片上系统)与ASIC设计,以及对自动设计与自动实现最典型得诠释。

1- 2与软件描述语言相比,VHDL有什么特点? P6答:编译器将软件程序翻译成基于某种特定CPU得机器代码,这种代码仅限于这种CPU而不能移植,并且机器代码不代表硬件结构,更不能改变CPU得硬件结构,只能被动地为其特定得硬件电路结构所利用。

综合器将VHDL程序转化得目标就是底层得电路结构网表文件,这种满足VHDL设计程序功能描述得电路结构,不依赖于任何特定硬件环境;具有相对独立性。

综合器在将VHDL(硬件描述语言)表达得电路功能转化成具体得电路结构网表过程中,具有明显得能动性与创造性,它不就是机械得一一对应式得“翻译”,而就是根据设计库、工艺库以及预先设置得各类约束条件,选择最优得方式完成电路结构得设计。

1- 3什么就是综合?有哪些类型?综合在电子设计自动化中得地位就是什么?什么就是综合?答:在电子设计领域中综合得概念可以表示为:将用行为与功能层次表达得电子系统转换为低层次得便于具体实现得模块组合装配得过程。

有哪些类型?答:(1)从自然语言转换到VHDL语言算法表示,即自然语言综合。

(2)从算法表示转换到寄存器传输级(RegisterTransport Level,RTL),即从行为域到结构域得综合,即行为综合。

(3)从RTL级表示转换到逻辑门(包括触发器)得表示,即逻辑综合。

(4)从逻辑门表示转换到版图表示(ASIC设计),或转换到FPGA得配置网表文件,可称为版图综合或结构综合。

综合在电子设计自动化中得地位就是什么?答:就是核心地位(见图1- 3)。

EDA技术及应用试卷B含答案

《EDA技术与应用》试卷B一、填空题(共10分,每题2分)1、EDA技术的应用范畴包括计算机辅助设计CAD、计算机辅助制造CAM、、等。

2、实体定义中的端口模式用来说明端口上的数据流动方向,端口模式有以下几种IN、OUT、、。

3、可编程逻辑器件按照结构复杂程度的不同,可将PLD大致分为简单可编程逻辑器件、、。

4、信号的赋值采用符号,而变量的赋值符号为。

5、进程语句本身是,但其内部的语句是由构成的。

二、解释程序(第1题5分,第2题5分,第3题10分,共20分)1解释带有下划线的语句2说明该程序逻辑功能3改用WITH-SELECT语句编写下列程序。

LIBRARY ieee;USE ieee.std_logic_1164.ALL;entity xuan2 isport (a :in std_logic_vector(3 downto 0);sel:in std_logic_vector(1 downto 0);d:out std_logic);end xuan2;architecture a of xuan2 isbeginprocess(sel)begincase sel iswhen "00" =>d<=a(0);when "01" =>d<=a(1);when "10" =>d<=a(2);when others =>d<=a(3);end case;end process;end a;三、判断下列程序是否有错误,如有则指出错误所在,并修改程序。

(20分)程序一:ENTITY decoder3_8 ISPORT(a:IN BIT_VECTOR(2 DOWNTO 0);y:OUT BIT_VECTOR(7 DOWNTO 0));END decoder3_8;ARCHITECTURE beh OF decoder3_8 IS BEGINWITH a SELECTy<= “11111110”WHEN “000”;“11111101”WHEN “001” ;“11111011”WHEN “010” ;“11110111”WHEN “011” ;“11101111”WHEN “100” ;“11011111”WHEN “101” ;“10111111”WHEN “110” ;“01111111”WHEN “111”;END beh;程序二:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;Entity behavioral isport(a: in bit;b: in bit;equal: out std_ulogic);end behavioral;Architecture eqcomp4 of behavioral isBeginif a=b thenequal <='1';elseequal <='0';end eqcomp4 ;四、分析下列程序功能,并将程序补充完整。

《EDA技术》复习题-电子版答案2023年修改整理

一、 填空题1、目前国际上较大的PLD器件制造公司有Altera 和Xilinx 公司。

2、当前最流行并成为IEEE标准的硬件描述语言包括VHDL 和V erilog HDL 。

3、高密度可编程逻辑器件HDPLD包括EPLD 、CPLD 和FPGA 。

4、PLD从集成密度上可分为LDPLD 和HDPLD两类,其中HDPLD包括__EPLD_ ____、__ CPLD_____和___FPGA _____三种。

5、EDA设计流程包括设计预备、设计输入、设计处理和器件编程四个步骤。

6、图形文件的扩展名是_.bdf__;QuartusII所建工程的扩展名是_.qpf_;自建元件图形符号文件的扩展名_.bsf__;Verilog HDL所编程序的扩展名为__.v__ 。

7、图形文件的扩展名是 .bdf ;矢量波形文件的扩展名是.vwf ;自建元件图形符号文件的扩展名 .bsf 。

8、可编程逻辑器件的优化过程要紧是对__速度__和___资源___的处理过程即时刻优化和面积优化。

9、EDA设计输入要紧包括__图形输入__、__ 文本输入和__ 波形__输入。

10、设计处理的后来一步是产生可供器件编程使用的数据文件,对CPLD来说是产生熔丝图文件即JEDEC文件,关于FPGA来说是产生位流数据文件Bitstream 。

11、EDA设计输入要紧包括 图形输入 、 文本输入 和 波形输入 。

12、设计优化要紧包括 面积优化 和 速度优化 。

13、Verilog HDL语言的扩展名为 .v 。

14、EDA的中文名称是 电子设计自动化 。

15、EDA仿真分为功能仿真又称前仿真、系统级仿真或行为仿真,用于验证系统的功能;时序仿真又称后仿真、电路级仿真,用于验证系统的时序特性、系统性能。

16、一般把EDA技术的进展分为_ __CAD____、__ CAE_____和___EDA____三个时期。

17、堵塞型赋值符号为= ,非堵塞型赋值符号为<= 。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1 1.1、设计集成计数器74161,设计要求如下: 4-BIT BINARY UP COUNTER WITH SYNCHRONOUS LOAD AND ASYNCHRONOUS CLEAR NOTE INPUTS: CLK LDN CLRN D C B A OUTPUTS:QD QC QB QA RCO *RCO = QD & QC & QB & QA LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_UNSIGNED.ALL; ENTITY CNT4 IS PORT( CLK,LDN,CLRN : IN STD_LOGIC; D,C,B,A : IN STD_LOGIC; CARRY : OUT STD_LOGIC; QD,QC,QB,QA : OUT STD_LOGIC ); END; ARCHITECTURE A OF CNT4 IS SIGNAL DATA_IN: STD_LOGIC_VECTOR(3 DOWNTO 0); BEGIN DATA_IN<=D&C&B&A; PROCESS(DATA_IN,CLK,LDN,CLRN) VARIABLE CNT:STD_LOGIC_VECTOR(3 DOWNTO 0); BEGIN IF CLRN='0' THEN CNT:=(OTHERS=>'0'); ELSIF CLK'EVENT AND CLK='1' THEN IF LDN='0' THEN CNT:=DATA_IN; ELSE CNT:=CNT+1; END IF; END IF; CASE CNT IS WHEN "1111"=> CARRY<='1'; WHEN OTHERS=> CARRY<='0'; END CASE; QA<=CNT(0); QB<=CNT(1); QC<=CNT(2); QD<=CNT(3); END PROCESS; END A;

1.2、设计一个通用双向数据缓冲器,要求缓冲器的输入和输出端口的位数可以由参数决定。 设计要求:N BIT数据输入端口A,B。工作使能端口EN=0时双2

向总线缓冲器选通, DIR=1,则A=B;反之B=A。 LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; ENTITY BIDIR IS GENERIC(N:INTEGER:=8); PORT( A,B : INOUT STD_LOGIC_VECTOR(N-1 DOWNTO 0); EN,DIR : IN STD_LOGIC); END; ARCHITECTURE A OF BIDIR IS BEGIN PROCESS(EN,DIR) BEGIN IF EN='0' THEN A<=(OTHERS=>'Z'); B<=(OTHERS=>'Z'); ELSE IF DIR='1' THEN B<=A; ELSE A<=B; END IF; END IF; END PROCESS; END A;

2.1、用VHDL语言编程实现十进制计数器,要求该计数器具有异步复位、同步预置功能。 LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; ENTITY CNT_10_2 IS PORT( CLK,CLR : IN STD_LOGIC; COUNT : OUT STD_LOGIC ); END; ARCHITECTURE A OF CNT_10_2 IS SIGNAL CNT_10 : INTEGER RANGE 0 TO 10; BEGIN PROCESS(CLK,CLR) BEGIN IF CLR='1' THEN CNT_10<=0; ELSIF CLK'EVENT AND CLK='1' THEN CNT_10<=CNT_10+1; IF CNT_10=9 THEN CNT_10<=0; COUNT<='1'; ELSE 3

COUNT<='0'; END IF; END IF; END PROCESS; END A;

2.2、设计实现一位全减器。 行为描述: F_SUB4 LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY F_SUB4 IS PORT( A,B,CIN : IN STD_LOGIC; DIFF,COUT : OUT STD_LOGIC ); END; ARCHITECTURE A OF F_SUB4 IS BEGIN DIFF<=A XOR B XOR CIN; COUT<=(NOT A AND B) OR (NOT A AND CIN) OR (B AND CIN); END A;

数据流描述F_SUB1 LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY F_SUB1 IS PORT( A,B :IN STD_LOGIC; CIN :IN STD_LOGIC; DIFF,COUT : OUT STD_LOGIC ); END; ARCHITECTURE A OF F_SUB1 IS SIGNAL S :STD_LOGIC_VECTOR(2 DOWNTO 0); BEGIN S<=CIN&A&B; PROCESS(A,B,CIN) BEGIN CASE S IS WHEN "000" => DIFF<='0';COUT<='0'; WHEN "001" => DIFF<='1';COUT<='1'; WHEN "010" => DIFF<='1';COUT<='0'; WHEN "011" => DIFF<='0';COUT<='0'; WHEN "100" => DIFF<='1';COUT<='1'; WHEN "101" => DIFF<='0';COUT<='1'; 4

WHEN "110" => DIFF<='0';COUT<='0'; WHEN "111" => DIFF<='1';COUT<='1'; WHEN OTHERS=> DIFF<='X';COUT<='X'; END CASE; END PROCESS; END A;

数据流描述F_SUB2

LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY F_SUB2 IS PORT( A,B,CIN : IN STD_LOGIC; DIFF,COUT : OUT STD_LOGIC ); END; ARCHITECTURE A OF F_SUB2 IS SIGNAL S :STD_LOGIC_VECTOR(2 DOWNTO 0); SIGNAL C :STD_LOGIC_VECTOR(1 DOWNTO 0); BEGIN S<=CIN&A&B; DIFF<=C(1); COUT<=C(0); C<="00" WHEN S="000" ELSE "11" WHEN S="001" ELSE "10" WHEN S="010" ELSE "00" WHEN S="011" ELSE "11" WHEN S="100" ELSE "01" WHEN S="101" ELSE "00" WHEN S="110" ELSE "11" ; END A;

数据流描述F_SUB3 LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY F_SUB3 IS PORT( A,B,CIN : IN STD_LOGIC; DIFF,COUT : OUT STD_LOGIC ); END; ARCHITECTURE A OF F_SUB3 IS SIGNAL S :STD_LOGIC_VECTOR(2 DOWNTO 0); SIGNAL C :STD_LOGIC_VECTOR(1 DOWNTO 0); 5

BEGIN S<=CIN&A&B; DIFF<=C(1); COUT<=C(0); WITH S SELECT C<="00" WHEN "000", "11" WHEN "001", "10" WHEN "010", "00" WHEN "011", "11" WHEN "100", "01" WHEN "101", "00" WHEN "110", "11" WHEN OTHERS; END A;

3.1、阅读教材P181页,例[5-55]并回答下列问题: (1)、该程序的功能是什么? (2)、请写出该程序所有端口的功能描述。 3.2、试描述一个十进制——BCD码编码器,输出使能为低电平有效。 LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; ENTITY BIN_BCD IS PORT( BIN : IN INTEGER RANGE 0 TO 20; --ENA : IN STD_LOGIC; BCD_OUT : OUT STD_LOGIC_VECTOR(7 DOWNTO 0) ); END; ARCHITECTURE A OF BIN_BCD IS BEGIN BINARY_BCD : BLOCK BEGIN BCD_OUT <= "00000000" WHEN BIN = 0 ELSE "00000001" WHEN BIN = 1 ELSE "00000010" WHEN BIN = 2 ELSE "00000011" WHEN BIN = 3 ELSE "00000100" WHEN BIN = 4 ELSE "00000101" WHEN BIN = 5 ELSE "00000110" WHEN BIN = 6 ELSE "00000111" WHEN BIN = 7 ELSE "00001000" WHEN BIN = 8 ELSE "00001001" WHEN BIN = 9 ELSE "00010000" WHEN BIN = 10 ELSE "00010001" WHEN BIN = 11 ELSE "00010010" WHEN BIN = 12 ELSE "00010011" WHEN BIN = 13 ELSE "00010100" WHEN BIN = 14 ELSE "00010101" WHEN BIN = 15 ELSE