EDA VHDL 第3章 VHDL基础

第3章 VHDL设计初步

当执行到CASE语句时,首先计算表达式的值,然后根据条件句中与之相 同的选择值,执行对应的顺序语句,最后结束CASE语句。表达式可以是一 个整数类型或枚举类型的值,也可以是由这些数据类型的值构成的数组(请注 意,条件句中的“=>”不是操作符,它只相当于“THEN”的作用)。 使用CASE语句需注意以下几点: (1)条件句中的选择值必须在表达式的取值范围内。

STD_LOGIC所定义的9种数据的含义是: ‘U’表示未初始化的; ‘X’表示强未知的; ‘0’表示强 逻辑0; ‘1’表示强逻辑1; ‘Z’表示高阻态; ‘W’ 表示弱未知的; ‘L’表示弱逻辑0; ‘H’表示弱 逻辑1; ‘-’表示忽略。

3.1 组合电路的VHDL描述

3.1.2 2选1多路选择器及其VHDL描述2

3.1 组合电路的VHDL描述

3.1.4 半加器及其VHDL的描述

3.1 组合电路的VHDL描述

3.1.4 半加器及其VHDL的描述

1. CASE语句

CASE语句属于顺序语句,必须放在进程语句中。 CASE语句的一般表式是: CASE <表达式> IS When <选择值或标识符> => <语句1>; ... ; <语句n> ; When <选择值或标识符> => <语句1>; ... ; <语句n> ; ... WHEN OTHERS => <语句>; END CASE ;

VHDL程序结构

综合需要 根据需要选用

库说明 LIBRARY USE 程序包 PACKAGE 实体 ENTITY 结构体 ARCHITECTURE 数据流描述 结构化描述 行为描述 BEHAVIOR DATAFLOW STRUCTURE

第三章 VHDL程序设计1

五、VHDL与其它硬件描述语言的比较

行为级 VHDL: 具有较强的系统级抽象描述能力,适 合行为级和 RTL级的描述。设计者可不必 了解电路细节,所作工作较少,效率高。 但对综合器的要求高,不易控制底层电路 的生成。IEEE标准,支持广泛。 RTL: Register Translate Level

其中,端口模式: in: 输入型,此端口为只读型。 out: 输出型,只能在实体内部对其赋值。 inout:输入输出型,既可读也可赋值。 buffer: 缓冲型,与 out 相似,但可读。

21

out 和 buffer 的区别:

inout 和 buffer 的区别: Inout:是一个双向引脚,它在out引脚上加入一个 22 三态输出和输入缓冲器构成的

configuration 配置名 of 实体名 is

for

选配结构体名

end for ;

end 配置名;

32

例:一个与非门不同实现方式的配置如下:

library ieee; use ieee.std_logic_1164.all; configuration first of nand is for art1; entity nand is end for; port(a: in std_logic; end first; b: in std_logic; c: out std_logic); --configuration second of nand is end entity nand; -for art2 architecture art1 of nand is -end for; begin --end second; c<=not (a and b); end architecture art1; architecture art2 of nand is begin c<=‘1’ when (a=‘0’) and (b=‘0’) else ‘1’ when (a=‘0’) and (b=‘1’) else ‘1’ when (a=‘1’) and (b=‘0’) else ‘0’ when (a=‘1’) and (b=‘1’) else ‘0’; 33 end architecture art2;

EDA习题集

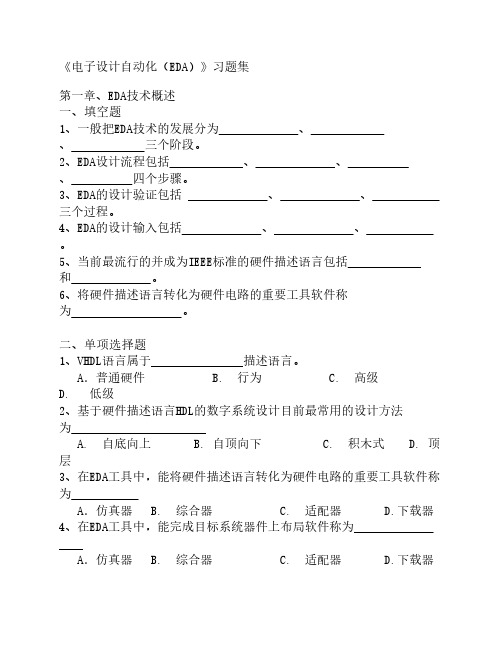

《电子设计自动化(EDA)》习题集第一章、EDA技术概述一、填空题1、一般把EDA技术的发展分为 、、 三个阶段。

2、EDA设计流程包括 、 、、 四个步骤。

3、EDA的设计验证包括 、 、 三个过程。

4、EDA的设计输入包括 、 、 。

5、当前最流行的并成为IEEE标准的硬件描述语言包括和 。

6、将硬件描述语言转化为硬件电路的重要工具软件称为 。

二、单项选择题1、VHDL语言属于 描述语言。

A.普通硬件 B. 行为 C. 高级D. 低级2、基于硬件描述语言HDL的数字系统设计目前最常用的设计方法为A. 自底向上B. 自顶向下C. 积木式D. 顶层3、在EDA工具中,能将硬件描述语言转化为硬件电路的重要工具软件称为A.仿真器 B. 综合器 C. 适配器 D.下载器4、在EDA工具中,能完成目标系统器件上布局软件称为A.仿真器 B. 综合器 C. 适配器 D.下载器 第2章、大规模可编程逻辑器件 一、填空题1、集成度是集成电路一项重要的指标,可编程逻辑器件按集成密度可分为 和 两类。

2、可编程逻辑器件的编程方式可分为 和 两类。

3、基于EPROM、E2PROM和快闪存储器件的可编程器件,在系统断电后编程信息 。

4、基于SRAM结构的可编程器件,在系统断电后编程信息 。

5、CPLD器件中至少包括 、 、 三种结构。

6、FPGA的三种可编程电路分别是 、、 三种结构。

7、根据逻辑功能块的大小不同,可将FPGA分为和 两类;据FPGA内部连线结构的不同,可将FPGA分为 和 两类;据FPGA采用的开关元件不同,可将FPGA分为 和 两类.8、目前常见的可编程逻辑器件的编程和配置工艺包括基于 、基于 和基于 三种编程工艺。

二、 单项选择题1、在下列可编程逻辑器件中,不属于高密度可编程逻辑器件的是A. EPLDB. CPLDC. FPGAD. PAL2、在下列可编程逻辑器件中,属于易失性器件的是A. EPLDB. CPLDC. FPGAD. PAL3、在自顶向下的设计过程中,描述器件总功能的模块一般称为A.底层设计 B. 顶层设计 C. 完整设计 D. 全面设计4、边界扫描测试技术主要解决 的测试问题A.印制电路板 B. 数字系统 C. 芯片 D. 微处理器 三、 简答题1、CPLD和FPGA有什么差异?在实际应用中各有什么特点?第3章、VHDL编程基础一、填空题1、VHDL设计实体的基本结构由 、、 、 和 等部分组成。

EDA技术实用教程(潘松第5版)第3章-VHDL设计初步

库—STD库

VHDL定义了两个标准程序包,即STANDARD和 TEXTIO(文件输入/输出)程序包,它们都收入在 STD库中,可随时调用。由于STD库符合VHDL语言 标准,在应用中不必用打开库语句。即

LIBRARY

STD;

STD.STANDARD.ALL

是不必要的。

库— WORK库

WORK库是用户的VHDL设计的现行工作库,用 于存放用户设计和定义的一些设计单元和程序包。 WORK库自动满足VHDL语言标准,在实际调用中, 也不必显示预先说明,即不必在VHDL程序中明确 打开并指定。 基于VHDL所要求的WORK库的基本概念,利用 VHDL进行设计时,不允许在根目录下进行,而是 必须为此设定一个文件夹,用于保存所有此项目 的设计文件,VHDL综合器将此文件默认为WORK库。 还要注意的是,工作库并不是这个文件夹的名字, 而是一个逻辑名。综合器将指示器指向该文件夹 的路径。

库的用法

例:

LIBRARY

USE

IEEE;

IEEE.STD_LOGIC_1164.STD_ULOGIC;

USE

IEEE. STD_LOGIC_1164.RISING _EDGE;

表示向当前设计实体开放了IEEE. STD_LOGIC_1164程序包中的RISING_EDGE函数, 但由于此函数要用到IEEE. STD_ULOGIC,所以在 其前面加了一条USE语句,开放同一程序包中的这 一数据类型。

设计实体

结构体 (Architecture) (P62)

结构体用于描述设计实体的内部结构和实

体端口间的逻辑关系,在电路上相当于器件的内

部电路结构。结构体由信号声明部分和功能描述

语句部分组成。信号声明部分用于结构体内部使

EDA课件第三章

tmp2:=d1 AND (NOT sel); tmp3:=tmp1 OR tmp2; tmp<=tmp3;

q<=tmp AFTER m; END PROCESS cale;

END ARCHITECTURE connect;

(2) 端口方向

端口方向用来定义外部引脚的信号方向是输入还 是输出。

凡是用“IN”进行方向说明的端口,其信号自端口 输入到构造体,而构造体内部的信号不能从该端口输 出。相反,凡是用“OUT”进行方向说明的端口,其信 号将从构造体内经端口输出,而不能通过该端口向构 造体输入信号。

实体说明

一个模块中仅有一 个设计实体。

实体 提供设计模块的接口信息,是VHDL设计电 路的最基本部分。

实体说明具有如下的结构:

ENTITY 实体名 IS

实体说明以“ENTITTY 实体名

[类属参数说明];

IS”开始至“END ENTITTY实体 名”结束。这里大写字母表示

实体说明的框架。实际上,对

此例中的外部引脚

ARCHITECTURE connect OF mux IS SIGNAL tmp:BIT; BEGIN

cale:PROCESS(d0,d1,sel) IS VARIABLE tmp1,tmp2,tmp3:BIT;

BEGIN tmp1:=d0 AND sel;

为d0,d1,sel,q 。

库(Library)是经编译后的数据的集合,它存放包集合 定义、实体定义、构造体定义和配置定义。

设计中的子程序和 公用数据类型的集合。

程序包

IEEE标准的标准程序包 设计者自身设计的程序包

包和库具有这样的关系:多个过程和函数汇集在一起构成包 集合,而几个包汇集在一起就形成一个库。

第3章 VHDL基础

3.2 时序电路描述

图3-5 例3-7的电路图 的电路图

3.2 时序电路描述

【例3-8】 】 ... IF a1 > b1 THEN q1 <= '1' ; ELSE q1 <= '0' ; END IF; ...

图3-6 例3-8的电路图 的电路图

3.2.3 时序电路的不同表述

3.2 时序电路描述

y <= d OR

e

3.1 VHDL 基本语法

组合电路描述 3.1.1 组合电路描述

【例3-3】 】 ENTITY mux21a IS PORT ( a, b, s: IN BIT; y : OUT BIT ); END ENTITY mux21a; ARCHITECTURE one OF mux21a IS BEGIN PROCESS (a,b,s) BEGIN IF s = '0' THEN y <= a ; END IF; END PROCESS; END ARCHITECTURE one ;

or_gate, Or_gate, Qr_Gate, OR_GATE. 不合法的: 不合法的: 2illegal_name, _illegal_name, illegal#name, Illegal_name_

3.1.2 扩展标识符

扩展标识符(Extended Identifier)是VHDL’93版扩展的 扩展标识符 是 版扩展的 书写规则和识别都有新规定,扩展标识符具有以下特性: 书写规则和识别都有新规定,扩展标识符具有以下特性: (1)扩展标识符用反斜杠来界定。 扩展标识符用反斜杠来界定。 扩展标识符用反斜杠来界定 例如: 是合法的。 例如:\invalid\,\controller_decode\是合法的。 , 是合法的 (2)允许包含图形符号、空格符,但没有格式的作用。 允许包含图形符号、 允许包含图形符号 空格符,但没有格式的作用。 例如: 是合法的。 例如:\$5000&T\,\mode A and B\是合法的。 & , 是合法的 (3) 2个反斜杠之问的字可以和保留字相同。 个反斜杠之问的字可以和保留字相同。 个反斜杠之问的字可以和保留字相同

最新整理版_EDA技术与VHDL第三章课后习题答案_第3版_潘松_黄继业

第3章 VHDL基础3-1:画出与下例实体描述对应的原理图符号元件:ENTITY buf3s IS -- 实体1:三态缓冲器PORT (input : IN STD_LOGIC ; -- 输入端enable : IN STD_LOGIC ; -- 使能端output : OUT STD_LOGIC ) ; -- 输出端END buf3x ;ENTITY mux21 IS --实体2: 2 选1 多路选择器PORT (in0, in1, sel : IN STD_LOGIC;output : OUT STD_LOGIC);3-1.答案3-2. 图3-30 所示的是4 选1 多路选择器,试分别用IF_THEN 语句和CASE 语句的表达方式写出此电路的VHDL 程序。

选择控制的信号s1 和s0 的数据类型为STD_LOGIC_VECTOR;当s1='0',s0='0';s1='0',s0='1';s1='1',s0='0'和s1='1',s0='1'分别执行y<=a、y<=b、y<=c、y<=d。

3-2.答案LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY MUX41 ISPORT(s:IN STD_LOGIC_VECTOR(1 DOWNTO 0); --输入选择信号a,b,c,d:IN STD_LOGIC; --输入信号y:OUT STD_LOGIC);--输出端END ENTITY;ARCHITECTURE ART OF MUX41 ISBEGINPROCESS(s)BEGINIF (S="00") THEN y<=a;ELSIF (S="01") TH EN y<=b;ELSIF (S="10") TH EN y<=c;ELSIF (S="11") TH EN y<=d;ELSE y<=NULL;END IF;EDN PROCESS;END ART;LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY MUX41 ISPORT(s:IN STD_LOGIC_VECTOR(1 DOWNTO 0); --输入选择信号a,b,c,d:IN STD_LOGIC; --输入信号y:OUT STD_LOGIC);--输出端END MUX41;ARCHITECTURE ART OF MUX41 ISBEGINPROCESS(s)BEGINCASE s ISWHEN “00” => y<=a;WHEN “01” => y<=b;WHEN “10” => y<=c;WHEN “11” => y<=d;WHEN OTHERS =>NULL;END CASE;END PROCESS;END ART;3-3. 图3-31 所示的是双 2 选 1 多路选择器构成的电路MUXK,对于其中MUX21A,当s='0'和'1'时,分别有y<='a'和y<='b'。

EDA技术与VHDL程序设计基础教程

二、EDA技术的发展历程和未来展望

现代EDA技术是20世纪90年代初从计算机辅助设计、辅助制造和辅 助测试等工程概念发展而来的。它的成熟主要经历了三个阶段,即:

计算机辅助设计(CAD,Computer Aided Design) 计算机辅助工程设计(CAED,Computer Aided Engineering Design) 电子设计自动化(EDA,Electronic System DesignAutomation)。

11 111 111 11111111 11

&

≥1

&

≥1

&

≥1

&

≥1

1

三、 CPLD的基本结构和工作原理

1.输出逻辑宏单元 2.控制电路

3.全局布线区

属于ispLSI中的一种专用内部 互联结构。起作用是将GLB的 输出信号或I/O单元的输入信 号与GLB的输入端连接

EDA技术主要有四个方面: 1、可编程逻辑器件,即应用EDA技术完成电子系统设计的载体; 2、硬件描述语言(VHDL 或者 Verilog)。它用来描述系统的结构和功

能,是EDA的主要表达手段; 3、配套的软件工具。它用来完成电子系统的智能化设计; 4、实验开发系统。在整个EDA设计电子系统的过程中,实验开发系统是 实现可编程器件下载和验证的工具,

第2章

重点内容:

CPLD结构和工作原理 FPGA结构和工作原理 FPGA配置方式 CPLD/FPGA应用选型

一、可编程逻辑器件概述

可编程逻辑器件 PROM、PLA和PAL的原理和特性

PROM

基于二极管和三极管 的一次可编程PROM单 字线

元

二极管

上拉电阻

2选1选择器的VHDL设计课件

3.1 多路①可以使用26个英文字母,数字0-9以及下划线“_”,且 只能以英文字母开头;

②不区分大小写;最长不超过64个字符;

③必须是单一下划线,且下划线前后都必须有英文字母 或数字;

6、端口定义语句port和端口模式 端口模式

IN 输入端口,定义的通道为单向只读模 OUT 式输出端口,定义的通道为单向输出模 INOUT 式 定义的通道确定为输入输出双向端口 BUFFER 缓冲端口,其功能与INOUT类似

3、界符 标点符号“;”表示VHDL中语句的结束;

3.1 多路选择器的VHDL描述

4、实体和结构体

实体和结构体是VHDL程序的两个基本组成部分;其中 实体主要用于定义电路或系统的外部端口;结构体用于定义 内部逻辑功能或电路结构。

ENTITY e_name IS PORT ( p_name : port_m

-- 注意,赋值条件的数据类型必须是boolean

3.1 多路选择器的VHDL描述

思考 ❖还有没有其它方法实现二选一? ❖n选一的多路选择器怎么设计?

3.1 多路选择器的VHDL描述

9、赋值符号<=

信号赋值符号“<=”,表示将符号右端的值赋值给左端的 信号; 10、关系运算符=

等号“=”没有赋值的含义,也不是相等的意思,而是 关系运算符,只是一种数据比较符号,其结果只有两种情况, 要么为真true,条件成立;要么为假false,条件不成立。 表达式 WHEN 赋值条件 ELSE

END ARCHITECTURE one ;

3.1 多路选择器的VHDL描述

3.1 多路选择器的VHDL描述

entity 实体

architecture 结构体

实体 mux21a1

EDA课件3

用VHDL语言设计的电路无论规模大小,都要使 用一个完整的VHDL程序结构,这个完整的程序结构 称为设计实体或实体。

设计实体是指能被VHDL语言综合器所接受,并 能作为独立的设计单元,以元件的形式存在的VHDL 语言程序。 所谓的元件,既可以被高层次的系统调用,成 为系统的一部分,也可以作为一个电路的功能模块, 独立存在和运行。

fallw: TIME :=1ns ); --定义fallw为下降沿

--定义A、B和Y为逻辑位

B: IN

STD_LOGIC;

STD_LOGIC );

16

第3章 VHDL程序的基本结构

3.1.2 VHDL语言的结构体

结构体是设计实体的核心,它具体指明了设计 实体的行为、元件及内部连接关系。

结构体所承担的任务 : ① 定义结构体内部所使用的各项元素;

3

第3章 VHDL程序的基本结构

1. VHDL设计实体的结构 一个完整的VHDL设计实体(设计文件),通常

包括:

■ 库(Library)和程序包(Package)

■ 实体说明(Entity)

■ 结构体(Architecture)

■ 配置(Configuration)

4

第3章 VHDL程序的基本结构

结构体:用来描述电路内部结构和逻辑功能。并以 标识符ARCHITECTURE开头,以END结尾。

8

第3章 VHDL程序的基本结构

3. 1.1 VHDL语言的实体说明

实体说明是VHDL程序设计中最基本的组成部分, 实体说明语句的格式如下: 主要用来描述设计实体的外部接口信号,定义设计 实体说明语句 ENTITY 实体名 IS 单元的输入、输出端口,是设计实体对外的一个通 类属说明语句 [GENERIC(类属表);] 信界面,但它不描述设计的具体功能。 端口说明语句 [PORT(端口表);] 结束语句 END [ENTITY] 实体名;

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

KX

康芯科技

3.3 全加器的VHDL描述

3.3.1 半加器描述

【例3-17】 LIBRARY IEEE ; --或门逻辑描述 USE IEEE.STD_LOGIC_1164.ALL; ENTITY or2a IS PORT (a, b :IN STD_LOGIC; c : OUT STD_LOGIC ); END ENTITY or2a; ARCHITECTURE one OF or2a IS BEGIN c <= a OR b ; END ARCHITECTURE one ;KXFra bibliotek康芯科技

3.2 时序电路描述

图3-5 例3-7的电路图

KX

康芯科技

3.2 时序电路描述

【例3-8】 ... IF a1 > b1 THEN q1 <= '1' ; ELSE q1 <= '0' ; END IF; ...

图3-6 例3-8的电路图

KX

康芯科技

3.2 时序电路描述

3.2.3 时序电路的不同表述

KX

康芯科技

3.3 全加器的VHDL描述

【例3-16】 LIBRARY IEEE; --半加器描述(2):真值表描述方法 USE IEEE.STD_LOGIC_1164.ALL; ENTITY h_adder IS PORT (a, b : IN STD_LOGIC; co, so : OUT STD_LOGIC); END ENTITY h_adder; ARCHITECTURE fh1 OF h_adder is SIGNAL abc : STD_LOGIC_VECTOR(1 DOWNTO 0) ; --定义标准逻辑位矢量数据类型 BEGIN abc <= a & b ; --a相并b,即a与b并置操作 PROCESS(abc) BEGIN CASE abc IS --类似于真值表的CASE语句 WHEN "00" => so<='0'; co<='0' ; WHEN "01" => so<='1'; co<='0' ; WHEN "10" => so<='1'; co<='0' ; WHEN "11" => so<='0'; co<='1' ; WHEN OTHERS => NULL ; END CASE; END PROCESS; END ARCHITECTURE fh1 ;

KX

康芯科技

3.2 时序电路描述

【例3-11】 LIBRARY IEEE ; USE IEEE.STD_LOGIC_1164.ALL ; ENTITY DFF3 IS PORT (CLK,D : IN STD_LOGIC ; Q : OUT STD_LOGIC ); END ; ARCHITECTURE bhv OF DFF3 IS SIGNAL Q1 : STD_LOGIC; BEGIN PROCESS (CLK) BEGIN IF rising_edge(CLK) -- 必须打开STD_LOGIC_1164程序包 THEN Q1 <= D ; END IF; END PROCESS ; Q <= Q1 ; --在此,赋值语句可以放在进程外,作为并行赋值语句 END ;

KX

康芯科技

3.2 时序电路描述

3.2.2 时序描述VHDL规则

1. 标准逻辑位数据类型 STD_LOGIC

BIT数据类型定义:

TYPE BIT IS('0','1'); --只有两种取值

STD_LOGIC数据类型定义:

TYPE STD_LOGIC IS ('U','X','0','1','Z','W','L','H','-'); --有9种取值

3.3.1 半加器描述

u1 h_adder ain bin cin A B co so

d

h_adder A co so u2 f

a b

or2a

c

cout

ain bin

f_adder

cout sum

e

B

u3

sum

cin

图3-9

全加器f_adder电路图及其实体模块

I113康芯科技 KX

3.3 全加器的VHDL描述

【例3-9】 ... PROCESS (CLK) BEGIN IF CLK'EVENT AND (CLK='1') AND (CLK'LAST_VALUE='0') THEN Q <= D ; --确保CLK的变化是一次上升沿的跳变 END IF; END PROCESS ; 【例3-10】 ... PROCESS (CLK) BEGIN IF CLK='1' AND CLK'LAST_VALUE='0' --同例3-9 THEN Q <= D ; END IF; END PROCESS ;

y <= d OR

e

KX

康芯科技

3.1 VHDL 基本语法

3.1.1 组合电路描述

【例3-3】 ENTITY mux21a IS PORT ( a, b, s: IN BIT; y : OUT BIT ); END ENTITY mux21a; ARCHITECTURE one OF mux21a IS BEGIN PROCESS (a,b,s) BEGIN IF s = '0' THEN y <= a ; END IF; END PROCESS; END ARCHITECTURE one ;

ELSE

y <= b ;

KX

康芯科技

3.1 VHDL 基本语法

3.1.1 组合电路描述

图3-3 mux21a功能时序波形

KX

康芯科技

3.1 VHDL 基本语法

3.1.2 VHDL结构 1. 实体表达

【例3-4】

ENTITY e_name IS port_m data_type; PORT ( p_name : ... p_namei : port_mi END ENTITY e_name; data_type );

KX

康芯科技

3.2 时序电路描述

2. 设计库和标准程序包

LIBRARY LIBRARY

WORK ; STD ;

USE STD.STANDARD.ALL ;

LIBRARY <设计库名>;

USE

< 设计库名>.<程序包名>.ALL ;

LIBRARY USE IEEE ;

IEEE.STD_LOGIC_1164.ALL ;

KX

康芯科技

3.1 VHDL 基本语法

9. 条件语句 10. WHEN_ELSE条件信号赋值语句

赋值目标 <= 表达式 WHEN 赋值条件 ELSE 表达式 WHEN 赋值条件 ELSE ...

表达式 ;

z

<=

a WHEN p1 = '1' ELSE

b WHEN p2 = '1' ELSE

c ;

KX

KX

康芯科技

3.2 时序电路描述

3.2.3 实现时序电路的不同表述 【例3-12】 ... PROCESS BEGIN wait until CLK = '1' ; Q <= D ; END PROCESS;

--利用wait语句

KX

康芯科技

3.2 时序电路描述

【例3-13】 ... PROCESS (CLK) BEGIN IF CLK = '1' THEN Q <= D ; --利用进程的启动特性产生对CLK的边沿检测 END IF; END PROCESS

3.3.1 半加器描述

co a b and2 so not xnor2

a 0 0 1 1

b 0 1 0 1

so 0 1 1 0

co 0 0 0 1

图3-10 半加器h_adder电路图及其真值表

KX

康芯科技

3.3 全加器的VHDL描述

3.3.1 半加器描述

【例3-15】 LIBRARY IEEE; --半加器描述(1):布尔方程描述方法 USE IEEE.STD_LOGIC_1164.ALL; ENTITY h_adder IS PORT (a, b : IN STD_LOGIC; co, so : OUT STD_LOGIC); END ENTITY h_adder; ARCHITECTURE fh1 OF h_adder is BEGIN so <= NOT(a XOR (NOT b)) ; co <= a AND b ; END ARCHITECTURE fh1;

KX

康芯科技

3.1 VHDL 基本语法

7. 赋值符号和数据比较符号

IF a THEN ... -- 注意,a的数据类型必须是 boolean IF (s1='0')AND(s2='1')OR(c<b+1) THEN ..

8. 逻辑操作符 AND(与)、OR(或)、NAND(与非)、NOR(或非)、 XOR(异或)、XNOR(同或)和NOT(取反) BIT、BOOLEAN、STD_LOGIC