数字控制振荡器(NCO)的FPGA实现

应用于数字锁相环的NCO设计

应用于数字锁相环的NCO设计保玲;佘世刚;周毅;金玉琳【摘要】本文鉴于数字锁相环在实际应用中对信号频率的准确度和稳定度有较为严格的要求,设计一种应用于数字锁相环的数控振荡器(NCO,Number Controlled Oscillator)。

基于直接数字频率合成(DDS)技术,介绍NCO工作原理,基于FPGA实现NCO,关键是相位累加器与波形存储器两个模块的设计,并利用QUARTUS对设计结果进行编译仿真。

对NCO杂散信号进行频谱分析,并提出解决方法。

该设计有效抑制杂散,修改灵活,便于调试,在数字锁相环设计中可有广泛应用。

%Based on the high standard for veracity and stability of signal frequency applied in digital PLL,a kind of NCO(Number Controlled Oscillator) is designed applied in digital PLL.Based on DDS(Direct Digital Frequency Synthesizers),the basic principle of NCO is introduced,NCO is realized based on FPGA.The key point is how to design phase accumulator and ROM,the design result is complied and simulated with applied software tool QUARTUS.The frequency spectrum of NCO is analyzed,and the resolve measure is given.This design can control spurious,modify conveniently,it has widely application in design of digital PLL.【期刊名称】《电子设计工程》【年(卷),期】2011(019)014【总页数】3页(P160-162)【关键词】NCO;DDS;杂散;FPGA【作者】保玲;佘世刚;周毅;金玉琳【作者单位】兰州空间技术物理研究所,甘肃兰州730000;兰州空间技术物理研究所,甘肃兰州730000;兰州空间技术物理研究所,甘肃兰州730000;兰州空间技术物理研究所,甘肃兰州730000【正文语种】中文【中图分类】TN802数字锁相环已在数字通信、无线电电子学及电力系统自动化等领域得到广泛应用。

数字Costas环在FPGA中的实现

数字Costas环在FPGA中的实现摘要:Costas环是一种闭环自动调整系统,常用于抑制载波的相位调制系统中提取参考载波信号。

文中介绍了Costas环的基本原理, 提出了一种用CIC滤波器代替环路滤波器的方法,并根据该原理用matlab的simulink工具箱对costas环进行了建模和仿真,最后在Quartus Ⅱ+ ModelSim环境中用Verilog语言实现了该算法,并下载到软件无线电硬件电路中验证了该算法的正确性.仿真和实验结果表明,该Costas环路具有十分优良的性能。

关键词:Costas环;VCO压控振荡器;CIC滤波器中图分类号:文献标识码:文章编号:Implementation of Digital Costas Loop on FPGA PlatformFENG Xiao-yu,YAN Wen-fei,LIU Bi-gangAbstract:Costas loop is a closed self-adjusting system, usually used to extract reference carrier in suppressed carrier phasemodulated systems.In this paper, The basic principle is introduced,Presents a CIC filter to replace the loop filter ,and base on this principle,the Costas loop is modeled and simulated by the simulink toolbox of matlab,Finally, in Quartus Ⅱ+ ModelSim environment, using Verilog language to implement the algorithm, and downloaded to the software radio hardware circuits to validate the correctness of the algorithm.Simulation and experimental results show that high performance can be achieved using this kind of all-digita Costas loop.Key words:Costas loop;VCO;CIC filter引言在利用相干解调的数字通信系统中,载波同步是正确解调的前提,也是实际通信中的一项关键技术[1-2],没有载波同步就不可能正确的恢复出数字信号。

基于FPGA的可变速率PSK数字解调器实现

收稿日期:2015-06-05修回日期:2015-07-23作者简介:毛小群(1981-),女,湖南邵阳人,研究生,讲师。

研究方向:电子技术、自动化控制,信号处理。

摘要:针对QPSK 变速率调制数字系统,提出了一种新的基于现场可编程门阵列(FPGA )实现方法,该系统可以支持4.88Kb/s 到2Mb/s 和更高的连续比特速率。

设计采用混合乘法器、数控振荡器(NCO )和积分-梳状滤波器(CIC ),并给出了系统中载波和信号恢复电路的设计结构,且可以移植到任何FPGA 器件。

提出的设计在Xilinx Vir-tex-5FPGA 平台进行了硬件测试。

硬件实现结果显示,采用本方法实现的解调器,表现出优越的使用效率。

关键词:变速率,调制器,比特速率,现场可编程门阵列中图分类号:TN761文献标识码:A基于FPGA 的可变速率PSK 数字解调器实现毛小群(重庆电子工程职业学院,重庆401331)FPGA Implementation of Variable Rate PSK Digital DemodulatorMAO Xiao-qun(Chongqing College of Electronic Engineering ,Chongqing 401331,China )Abstract :In order to achieve QPSK variable rate modulation digital system ,a novel based onfield programmable gate array (FPGA )implementation method is proposed.The system can support 4.88Kb/s to 2Mb/s and higher continuous bit rate.Design with the mixed multiplier ,numericallycontrolled oscillator (NCO )and integral comb filter (CIC ),and the structure of carrier recovery circuitand signal of the system is described.This system can be ported to any FPGA device.The proposeddesign of the hardware tests in the Xilinx Virtex -5FPGA platform.The test results show that the proposed demodulator show superior ability in efficiency.Key words :variable rate ,modulator ,bit rate ,field programmable gate array (FPGA )0引言随着全球范围内个人通信需求的不断增长,卫星通信的使用规模也不断增大。

数字控制振荡器

背景知识:在实际的通信系统中,携带数字信息的信号通常是由某种类型的载波调制方式发送的,传送信号的带宽限制在以载波为中心的一个频段上,如双边带调制,或在邻近载波的频段上,如单边带调制。

无论何种调制方式,在发送端均需要一个高频载波将信息调制上去,以减小信号衰落,相干解调时在接收端也需要一个与发送端同频同相的高频载波将信息从高频上解调下来。

为了产生这个高频载波,在数字电路中是采用数控振荡器(NCO),也称为直接数字频率合成器〔DDS),它的输出频率和相位可以受人为控制,从而满足各种需要。

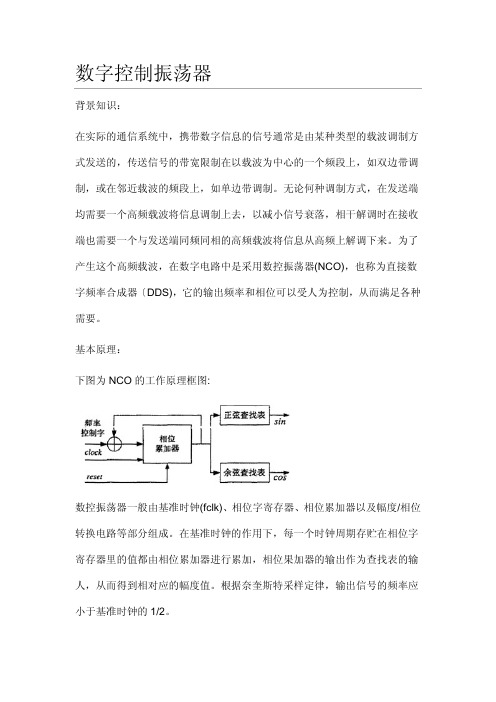

基本原理:下图为NCO的工作原理框图:数控振荡器一般由基准时钟(fclk)、相位字寄存器、相位累加器以及幅度/相位转换电路等部分组成。

在基准时钟的作用下,每一个时钟周期存贮在相位字寄存器里的值都由相位累加器进行累加,相位果加器的输出作为查找表的输人,从而得到相对应的幅度值。

根据奈奎斯特采样定律,输出信号的频率应小于基准时钟的1/2。

相位累加器输出(△Ф)的数值和系统的频率(fclk)决定了输出频率(fout),它门的关系如下:N是相位寄存器的位数,N值的大小决定了频率分辨率(fres ),有在这里假设,fclk=128MHz, N=32,可以计算出NCO的频率分辨率fres=0.0298Hz相位累加器是决定NCO电路性能的一个关键部分。

我们可以采用了Altera 的加法器宏功能模块形成一个32bit的累加器,它以流水线处理方式进行工作。

相位/幅度转换电路是NCO电路中的另一个关键部分,在设计中面临的主要问题就是资源的开销。

一般电路采用ROM结构,相位累加器的输出是一种数字式锯齿波,通过取它的若干位作为ROM的地址输人,而后通过查表和运算,ROM就能输出所需波形的量化数据。

在APEX器件中,ROM由EAB实现,ROM表的尺寸随着地址位数或数据位数的增加成指数递增关系,因此在满足信号性能的前提条件下,如何减少资源的开销就是一个重要的问题。

fpga 频率变换 实现方法

fpga 频率变换实现方法

FPGA(现场可编程门阵列)是一种可以进行并行处理的集成电路,其频率

变换可以通过以下几种方法实现:

1. 时钟分频器:FPGA内部通常包含一些内置的时钟分频器,可以将输入的时钟信号进行分频,从而得到不同频率的输出信号。

在FPGA开发工具中,可以通过配置时钟分频器的参数来改变分频比,从而实现频率变换。

2. 时钟生成器:FPGA内部还可以生成一些高精度的时钟信号,这些时钟信号可以通过配置时钟生成器的参数来改变其频率。

在FPGA开发工具中,可以使用内建的时钟生成器来生成所需的时钟信号。

3. 数字控制振荡器(Digital Controlled Oscillator,DCO):DCO是一种数字控制的振荡器,可以通过改变控制字来改变其振荡频率。

在FPGA开发工具中,可以通过配置DCO的参数来改变其振荡频率,从而实现频率变换。

4. 查找表(LUT):FPGA内部还可以使用查找表来实现频率变换。

查找表可以根据输入的地址选择相应的输出值,从而实现不同的频率变换。

在FPGA开发工具中,可以通过配置查找表的参数来改变输出值,从而实现频率变换。

5. 硬件描述语言:在FPGA开发过程中,可以使用硬件描述语言(如Verilog或VHDL)来实现频率变换的逻辑电路。

通过编写相应的代码,可

以实现不同的频率变换功能。

在FPGA开发工具中,将代码进行编译和综合后生成相应的配置文件,然后将配置文件下载到FPGA中即可实现频率变换。

以上是FPGA实现频率变换的几种常见方法,具体实现方式可以根据实际需求和开发环境进行选择。

基于FPGA的高速数字下变频系统设计

基于FPGA的高速数字下变频系统设计摘要:基于FPGA设计了一高速数字下变频系统,在设计中利用并行NCO和多相滤波相结合的方法有效的降低了数据的速率,以适合数字信号处理器件的工作频率。

为了进一步提高系统的整体运行速度,在设计中大量的使用了FPGA中的硬核资源DSP48。

Xilinx ISE14.4分析报告显示,电路工作速度可达360MHz。

最后给出了在Matlab和ModelSim中仿真的结果,验证了各个模块以及整个系统的正确性。

数字下变频(Digital Down Conversion,DDC)是软件无线电系统的关键模块之一,其可将高频数据流信号变成易于后端数字信号处理器(Digital Signal Processor,DSP)设备实时处理的低频数据流信号。

在数字下变频实现中,随着信号采样率的不断提高,数据率也会相应的提高,但是实际应用中随着数据速率的不断提高,数据处理器件(如FPGA)的处理速度会无法满足要求而不能正常工作,从而带来了数字信号处理的瓶颈问题。

本设计就是以多路并行NCO技术为基础,研究了如何在FPGA中用多路并行采样数据的方式来解决数据处理器件无法提供高速率的匹配信号的问题,并给出了高速DDC实现的架构和仿真结果。

1 数字下变频基本原理数字下变频主要由频谱搬移和抽取两部分组成,如图1所示,其中频谱搬移包含数控振荡器(Numerically Controlled Oscillators,NCO)、乘法器和低通滤波器(LPF,Low Pass Filter);抽取包含抽取滤波器(LPF2)和D倍的抽取,LPF2是为了限制信号的频谱,以免抽取后发生混叠。

模拟信号经过A/D转换后分成两路信号,一路信号和NCO输出的正弦信号相乘(同相分量),一路和NCO输出的余弦信号相乘(正交分量),之后经过低通滤波器(LPF1)将高频分量滤除,然后信号经过抽取滤波以降低速率,最终输出的两路信号就可以送往后续的数字信号处理器中做进一步的处理。

FPGA_ASIC-数字差分BPSK扩频接收机的设计与FPGA实现

数字差分BPSK扩频接收机的设计与FPGA实现摘要:本文提出了一种全数字差分BPSK扩频接收机的实现方案,通过Simulink仿真验证了该方案具有较低的误码率。

然后利用Verilog硬件描述语言编程,通过了综合和仿真验证,最后在Xilinx公司FPGA上实现了整个系统。

该系统经过优化设计,具有易于硬件实现,占用芯片资源少等优点,对实际工程有一定的指导意义。

关键字:FPGA,扩频,同步,数字差分,BPSK,接收机,可编程逻辑1引言随着软件无线电技术的发展,传统的基于复杂模拟硬件的接收设备逐渐向数字IC 产品过渡,而FPGA作为ASIC产品原型设计的可编程逻辑器件,以其丰富的逻辑资源和可重新配置的优势,成为人们前期研究与开发的重要手段。

因此,在可编程逻辑器件上实现数字扩频接收机关键技术进行研究,具有重要的应用价值。

本文给出了一种数字差分BPSK直接序列扩频接收机的方案,并通过simulink进行了仿真,同时本文深入探讨了方案中的关键技术在FPGA中的实现结构,在保证系统稳定性,和不影响系统性能的前提下降低硬件复杂度的问题上提出了FPGA实现方案,并最终在Xilinx XC2V500 FPGA上实现了整个系统,对工程实践有一定的指导意义。

2. 数字差分BPSK扩频接收机的结构与实现数字BPSK扩频接收机原理图见图1,系统主要可以分为三个部分:解调电路、PN 码捕获电路和PN码跟踪电路。

图1 数字差分BPSK扩频接收机原理图通过Simulink仿真该系统,同时结合Xilinx公司FPGA特点,对硬件电路实现进行探讨,在保证系统性能的前提下,减小硬件实现复杂度。

下面将具体介绍电路各部分原理与硬件实现。

2.1 数字解调BPSK信号的解调通常采用相干解调的方式,已经证明跟踪低信噪比的抑制载波信号的最佳装置是Costas环及平方环[1],并且这两种结构是等效的,在数字域中通常采用Costas环实现载波同步。

Costas环电路结构见图1解调电路,电路各部分实现如下。

基于NCO IP core的Chirp函数实现设计

基于NCO IP core的Chirp函数实现设计作者:董亮,汪敏,高亦菲,高冠男来源:《现代电子技术》2009年第20期摘要:首先分析Chirp函数在频域上的一般特性,并且分析Altrea 公司提供的数控振荡器知识产权核(NCO IP core)的输入/输出特性,通过MegaCore环境确定其输入控制字,通过外围逻辑电路实时向NCO IP core调入控制频率控制字以达到改变输出频率的目的,并通过在示波器上观测FPGA的运行情况,验证了该设计具有很好的输出效果。

关键词:NCO IP core;FPGA;Chirp函数;MegaCore中图分类号:TP311文献标识码:A文章编号:1004-373X(2009)20-020-03Design and Implementation of Chirp Function Based on NCO IP coreDONG Liang1,2,WANG Min2,GAO Yifei2,GAO Guannan2(1.Graduate School of Chinese Academy of Science,Beijing,100049,China;2.Yunnan Observatory,Chinese Academy of Science,Kunming,650011,China)Abstract:This design analyses the character of Chirp function in the time and frequency domain zone.And after analyzing the input/output feature of the NCO IP core.The different output frequency by writing different controlling words which can be determined from the MegaCore environment.The FPGA′s running situation by oscillograph to inspect and verify feature of the de sign is detected.The conclusion that this design can get the Chirp′s function perfectly.Keywords:NCO IP core;FPGA;Chirp function;MegaCore0 引言IP就是知识产权核或者知识产权模块的意思。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

数字控制振荡器(NCO)的FPGA实现

NCO(N umerically Controlled Oscillator)是用于产生一个理想的、数字可控的正弦或余弦波的数字控制式振荡器,其实现方法有实时计算法和查表法等多种。

实时计算法的正弦波样本以实时计算产生,该方法因其计算需要耗费很多时间,因而只能产生较低频率的正弦波,而且存在计算精度与计算时间的矛盾。

由于在需要产生高速的正交信号时,实时计算法将无法实现。

因此,在实际应用中一般采用最有效、最简单的查表法,即事先根据各个NCO正弦波的相位计算好相位的正弦值,并按相位作为地址信息存储该相位的正弦值数据。

1 NCO的基本原理

在通过相位累加产生地址信息时,通常需要输出当前时刻的相位值所对应的正弦值,即以参考频率源对相位进行等可控间隔采样。

众所周知,理想的正弦波信号S(t)可以表示成:。