最新《集成电路设计原理》试卷及答案

超大规模集成电路设计导论考试题及答案

1、MOS集成电路的加工包括哪些基本工艺?各有哪些方法和工序?答:(1)热氧化工艺:包括干氧化法和湿氧化法;(2)扩散工艺:包括扩散法和离子注入法;(3)淀积工艺:化学淀积方法:1 外延生长法;2 热CVD法;3 等离子CVD 法;物理淀积方法:1 溅射法;2 真空蒸发法(4)光刻工艺:工序包括:1 涂光刻胶;2 预烘干;3 掩膜对准;4 曝光;5 显影;6 后烘干;7 腐蚀;8 去胶。

2、简述光刻工艺过程及作用。

答:(1)涂光刻胶:为了增加光刻胶和硅片之间的粘附性,防止显影时光刻胶的脱落,以及防止湿法腐蚀产生侧向腐蚀;(2)预烘干:以便除去光刻胶中的溶剂;(3)掩膜对准:以保证掩模板上的图形与硅片上已加工的各层图形套准;(4)曝光:使光刻胶获得与掩模图形相同的感光图片;(5)显影:将曝光后的硅片浸泡在显影液中,使正光刻胶的曝光部分和负光刻胶的未曝光部分被溶解掉;(6)后烘干:使残留在光刻胶中的有机溶剂完全挥发掉,提高光刻胶和硅片的粘接性及光刻胶的耐腐蚀性;(7)腐蚀:以复制在光刻胶上图形作为掩膜,对下层材料进行腐蚀,将图形复制到下层材料中;(8)去胶:除去光刻胶。

3、说明MOS晶体管的工作原理答:MOS晶体管有四种工作状态:(1)截止状态:即源漏之间不加电压时,沟道各电场强度相等,沟道厚度均匀,S、D之间没有电流I ds=0;(2)线性工作状态:漏源之间加电压Vds时,漏端接正,源端接负,沟道厚度不再均匀,在D端电位升为V d,栅漏极电位差为Vgs-Vtn,电场强度变弱,反型层变薄,并在沟道上产生由D到S的电场E ds,使得多数载流子由S端流向D端形成电流I ds,它与V ds变化呈线性关系:I ds=βn[(V gs-V tn)-V ds/2]V ds(3)饱和工作状态:Vs继续增大到V gs-V tn时,D端栅极与衬底不足以形成反型层,出现沟道夹断,电子运动到夹断点V gs-V ds=V tn时,便进入耗尽区,在漂移作用下,电子被漏极高电位吸引过去,便形成饱和电流,沟道夹断后,(V gs-V tn)不变,I ds 也不变,即MOS工作进入饱和状态,I ds=V gs-V tn/R c(4)击穿状态:当Vds增加到一定极限时,由于电压过高,晶体管D端得PN结发生雪崩击穿,电流急剧增加,晶体管不能正常工作。

集成电路试卷

集成电路考试一、填空题(10×3)1、集成电路的出现电子设备向着__微小型化 、_智能化和低功耗 、__高速度___发展,加快了人类进入信息化时代的步伐。

2、集成度大约是每 18_____月翻一番的增长规律,这就是著名的摩尔定律。

3、根据参与导电的载流子可以把MOS 晶体管分成两类:一类是_____n 沟道_____ MOS 晶体管,另一类是___p 沟道_____MOS 晶体管。

4、现代先进双极晶体管的三个基本特征是___自对准工艺_______、_多晶硅发射极技术__________和 ____深槽隔离_______。

5、MOS 晶体管的阈值电压公式V T = 2BM FB F OXQ V C ϕ-+。

6、MOS 晶体管交流小信号模型中,跨导g m = _D GSI V ∂∂____________,有栅跨导g mb = ____D BSI V ∂∂_________。

7、与MOS 工艺兼容的电阻包括___扩散电阻_____、____多晶硅电阻____、____n 阱或p 阱电阻___。

8、集成电路的设计方法主要包括三部分内容:__设计抽象_____、___设计流程_____、__设计方法_______。

9、集成电路的设计方法包括 __PLD 设计方法______、__半定制设计方法____、___定制设计方法_____。

10、在集成电路的加工过程中,图形的加工是通过____光刻______和___刻蚀_________工艺完成的。

二、选择题(5×4)11、MOS 集成电路都选择<100>晶向的晶片,下列不是选取<100>晶向硅的原因是(A )A 、晶界面密度高B 、缺陷少C 、迁移率高D 、有利于器件提高性能12、RTL 电路的主要问题是( B )A 、速度慢B 、噪声容限低C 、功耗低D 、电路的关门电平高13、从瞬态特征看,下列哪种反相器的性能最差( D )A、耗尽型负载B、电阻负载C、非饱和增强负载D、饱和增强负载14、下列哪项不是BTCMOS电路相对于CMOS电路拥有的优点( A)A、结构简单,所用器件少B、没有静态功耗C、噪声容限低D、输入阻抗高15、减少动态功耗最有效的措施是(A )A、降低电源电压B、减少负载电容C、减少寄生电容D、防止电荷分享三、判断题(10×2)16、SOICMOS可以喝体硅CMOS一样采用LOCOS隔离工艺,但是不需要场区注入。

1+X集成电路理论考试题及答案

1+X集成电路理论考试题及答案一、单选题(共39题,每题1分,共39分)1.封装工艺的电镀工序中,完成前期的清洗后,下一步操作是()。

A、高温退火B、电镀C、装料D、后期清洗正确答案:B2.湿度卡的作用是( )。

A、去潮湿物质中的水分B、可以防止静电C、起到防水的作用D、显示密封空间的湿度状况正确答案:D答案解析:湿度卡是用来显示密封空间湿度状况的卡片。

3.“对刀”操作时,点击显示屏上主菜单的()按钮,使承载盘真空从关闭状态转为开启状态。

A、θ角度调整B、开始C、Work SetD、Manual Align正确答案:C答案解析:点击显示屏上主菜单的“Work Set”(设置)按钮,使承载盘真空从关闭状态转为开启状态。

点击显示屏上的“Manual Align”(手动对位)按钮,界面跳转到“切割道调整界面”。

点击“4.利用平移式分选机进行芯片分选时,吸嘴从()上吸取芯片,然后对芯片进行分选。

A、入料梭B、收料盘C、出料梭D、待测料盘正确答案:C5.如果遇到需要加温的晶圆,对晶圆的加温是在扎针调试( )。

A、之前B、之后C、过程中D、都可以正确答案:A答案解析:根据热胀冷缩的原理,需要加温的晶圆要在加温结束后再进行扎针调试。

若先进行扎针调试再加温可能会扎透铝层。

6.下列对芯片检测描述正确的是()。

A、集成电路测试是确保产品良率和成本控制的重要环节B、所有芯片的测试、分选和包装的类型相同C、测试完成后直接进入市场D、测试机分为数字测试机和模拟测试机正确答案:A7.口罩和发罩()。

A、需要定期清洗B、不得重复使用C、一周必须更换一次D、每天下班时放入消毒柜,下次对应取用正确答案:B答案解析:口罩和发罩不得重复使用,每天需穿戴全新的口罩和发罩。

8.待测芯片的封装形式决定了测试、分选和包装的不同类型,而不同的性能指标又需要对应的测试方案进行配套完成测试,测试完成后,经()即可进入市场。

A、运行测试后包装B、人工目检C、机器检测、人工目检D、人工目检、包装正确答案:D9.下列语句的含义是()。

《模拟集成电路设计原理》期末考试试卷及答案

《软件工程基础训练》实训报告在倒入酒的方法中,首先判断当前酒量是否已经达到酒杯的容量。

如果是,则提示酒杯已满;如果不是,则将倒入的酒量加到当前酒量上。

实现一个方法,用于从酒杯中倒出酒。

该方法接受一个参数,表示要倒出的酒量。

在倒出酒的方法中,首先判断当前酒量是否大于等于要倒出的酒量。

如果是,则将当前酒量减去要倒出的酒量;如果不是,则提示酒量不足。

实现一个方法,用于获取当前酒量。

在获取酒量的方法中,直接返回当前酒量的值。

2.1.3程序流程图图 12.1.4设计代码package wmx;import java.io.BufferedReader;import java.io.IOException;import java.io.InputStreamReader;import java.util.StringTokenizer;public class Main1 {}}}}2.1.5代码运行截图图 22.2第二阶段2.2.1需求分析明确问题定义:首先需要明确问题的背景和涉及的实体,例如旅行者、手电筒、桥等。

同时,需要确定问题的目标,即如何让所有人尽快过桥。

确定约束条件:根据问题的描述,我们知道有一些约束条件,例如每个人过桥的速度不同,手电筒不能扔掉,只能两个人同时过桥等。

这些约束条件将影响解决方案的设计。

分析时间需求:由于目标是尽快让所有人过桥,因此需要分析每个人过桥所需的时间。

这将影响如何分配手电筒和如何安排过桥的顺序。

制定策略:基于上述分析,需要制定一个有效的策略来最大化过桥的速度。

这可能涉及到如何分配手电筒,如何安排过桥的顺序,以及如何返回等。

评估和优化:最后,需要对所制定的策略进行评估和优化。

这可能涉及到对策略的模拟、测试和比较,以便找到最优的解决方案。

2.2.2设计思路这是一个经典的过桥问题,通常称为“蒙提霍尔问题”。

在这个问题中,目标是让所有人尽快过桥。

根据题目的条件,每个人单独过桥的时间是已知的,但是两个人一起过桥的时间是较慢的那个人所需的时间。

模拟集成电路设计原理_试题库1

《模拟集成电路设计原理》试卷(答题卷)(1)一、填空题(共30分,每空格1分)1. MOSFET 是一个四端器件,现在大多数的CMOS 工艺中,P 管做在_____中,并且,在大多数电路中,P 管的衬底与______(高或低)电平相连接,这样连接的原因是使得_________________________________________________。

2. 对增强型NMOS 来说,让其处于饱和时的条件为_______________________________,增强型PMOS 处于饱和时的条件为__________________________________________。

3. 在两级运放中,通常是用第一级运放实现_____________,用第二级运放实现_____________。

4. 实际工艺中,本征阈值电压并不适用于电路设计,因此在器件制造过程中,通常通过向沟道区注入__________来调整阈值电压,其实质是改变氧化层(栅氧)界面附近衬底的_______________。

5. 阈值电压为发生强反型时的栅压,对增强型NMOS 管来说,发生强反型时的条件为__________________________________________________。

6. 折叠式共源共栅运放与套筒式共源共栅结构相比,输出电压摆幅_______,但这个优点是以较大的________、较低的_______________、较低的_____________和较高的____________为代价得到的。

7. 对于一个负反馈系统来说,有前馈网络A 和反馈网络β,那么这个系统的开环增益为_______,闭环增益为________________,环路增益为____________。

8. 对于一个单极点系统来说,单位增益带宽为80MHz ,若现在带宽变为16MHz ,则环路增益为_________,闭环增益为_______。

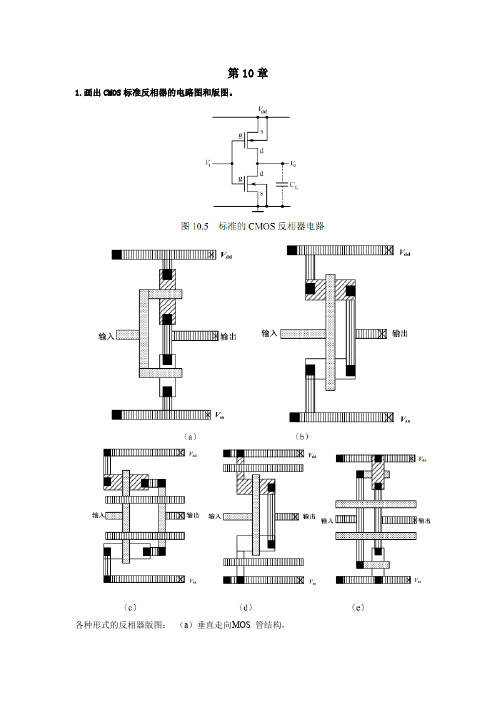

《集成电路设计(第2版)》习题答案10-12章

图10.40 反相器链驱动结构 4.列出CMOS存储器的分类和各自的特点。 分类: 半导体存储器按数据存取方式的不同可分为随机存储器 (RAM) 和只读存储器 (ROM) . 基 于单个数据存储单元的工作原理,RAM 主要分为两大类:动态存储器(DRAM)和静态存储器 (SRAM)。 而在ROM中根据数据存储(写入数据)方式的不同, 可分为掩膜ROM 和可编ROM(PROM)。 可编程ROM 又可进一步分为熔丝型ROM、 可擦除PROM(EPROM)、 电可擦除PROM(EEPROM)和闪存 (Flash),下图概括了存储器的分类。

1+X集成电路理论考试题(附参考答案)

1+X集成电路理论考试题(附参考答案)一、单选题(共39题,每题1分,共39分)1.在外观检查中发现料管破损,应( )。

A、继续使用B、及时更换C、对破损部位进行修补D、视情况而定正确答案:B答案解析:料管破损时要进行料管更换,否则会丢失芯片。

2.转塔式芯片检测前需要进行参数设置,其中设置动作延时的时间是为了( )。

A、确保所有环节的测试能够完整进行B、配合并行测试的速率C、防止卷盘上编带两端在操作过程中出现封口分离的情况D、准备对应的测试卡正确答案:A答案解析:转塔式分选机设备在芯片检测前需要进行参数设置,其中设置动作延时的时间是为了确保所有环节的测试能够完整进行。

3.重力式外观检查是在( )环节之前进行的。

A、编带B、测试C、分选D、真空包装正确答案:D答案解析:重力式分选机设备芯片检测工艺流程:上料→测试→分选→编带(SOP)→外观检查→真空包装。

4.晶圆烘烤时,温度一般设置在( )℃。

A、110B、120C、130D、140正确答案:B答案解析:晶圆烘烤时,温度一般设置在120℃。

5.用比色法进行氧化层厚度的检测时,看到的色彩是()色彩。

A、反射B、干涉C、衍射D、二氧化硅膜本身的正确答案:B答案解析:硅片表面生成的二氧化硅本身是无色透明的膜,当有白光照射时,二氧化硅表面与硅-二氧化硅界面的反射光相干涉生成干涉色彩。

不同的氧化层厚度的干涉色彩不同,因此可以利用干涉色彩来估计氧化层的厚度。

6.湿法刻蚀中,()的腐蚀液是以氢氟酸为基础的水溶液。

A、硅B、铝C、二氧化硅D、砷化镓正确答案:C答案解析:二氧化硅腐蚀液是以氢氟酸为基础的水溶液。

7.通常情况下,一个内盒中装入的DIP管装芯片( )颗。

A、3000B、1000C、5000D、2000正确答案:D答案解析:一般情况下,一个内盒中装入的DIP管装芯片2000颗。

8.8英寸晶圆的直径为( )mm。

A、125B、150C、200D、300正确答案:C答案解析:5英寸晶圆直径是125mm,6英寸晶圆直径是150mm,8英寸晶圆直径是200mm,12英寸晶圆直径是300mm。

集成电路试题库

半导体集成电路典型试题绪论1、什么叫半导体集成电路?【答案:】通过一系列的加工工艺,将晶体管,二极管等有源器件和电阻,电容等无源元件,按一定电路互连。

集成在一块半导体基片上。

封装在一个外壳内,执行特定的电路或系统功能。

2、按照半导体集成电路的集成度来分,分为哪些类型,请同时写出它们对应的英文缩写【答案:】小规模集成电路(SSI),中规模集成电路(MSI),大规模集成电路(VSI),超大规模集成电路(VLSI),特大规模集成电路(ULSI),巨大规模集成电路(GSI)3、按照器件类型分,半导体集成电路分为哪几类?【答案:】双极型(BJT)集成电路,单极型(MOS)集成电路,Bi-CMOS型集成电路。

4、按电路功能或信号类型分,半导体集成电路分为哪几类?【答案:】数字集成电路,模拟集成电路,数模混合集成电路。

5、什么是特征尺寸?它对集成电路工艺有何影响?【答案:】集成电路中半导体器件的最小尺寸如MOSFET的最小沟道长度。

是衡量集成电路加工和设计水平的重要标志。

它的减小使得芯片集成度的直接提高。

6、名词解释:集成度、wafer size、die size、摩尔定律?【答案:】7、分析下面的电路,指出它完成的逻辑功能,说明它和一般动态组合逻辑电路的不同,分析它的工作原理。

【答案:】该电路可以完成NAND逻辑。

与一般动态组合逻辑电路相比,它增加了一个MOS管M kp,它可以解决一般动态组合逻辑电路存在的电荷分配的问题。

对于一般的动态组合逻辑电路,在评估阶段,A=“H” B=“L”, 电荷被OUT处和A处的电荷分配,整体的阈值下降,可能导致OUT的输出错误。

该电路增加了一个MOS管M kp,在预充电阶段,M kp导通,对C点充电到V dd。

在评估阶段,M kp截至,不影响电路的正常输出。

8、延迟时间【答案:】时钟沿与输出端之间的延迟第1章集成电路的基本制造工艺1、四层三结的结构的双极型晶体管中隐埋层的作用【答案:】减小集电极串联电阻,减小寄生PNP管的影响2、在制作晶体管的时候,衬底材料电阻率的选取对器件有何影响【答案:】电阻率过大将增大集电极串联电阻,扩大饱和压降,若过小耐压低,结电容增大,且外延时下推大3、简单叙述一下pn结隔离的NPN晶体管的光刻步骤【答案:】第一次光刻:N+隐埋层扩散孔光刻第二次光刻:P隔离扩散孔光刻第三次光刻:P型基区扩散孔光刻第四次光刻:N+发射区扩散孔光刻第五次光刻:引线孔光刻第六次光刻:反刻铝4、简述硅栅p阱CMOS的光刻步骤【答案:】P阱光刻,光刻有源区,光刻多晶硅,P+区光刻,N+区光刻,光刻接触孔,光刻铝线5、以p阱CMOS工艺为基础的BiCMOS的有哪些不足【答案:】NPN晶体管电流增益小,集电极串联电阻大,NPN管的C极只能接固定电位6、以N阱CMOS工艺为基础的BiCMOS的有哪些优缺点?并请提出改进方法【答案:】首先NPN具有较薄的基区,提高了其性能:N阱使得NPN管C极与衬底断开,可根据电路需要接任意电位。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

电科《集成电路原理》期末考试试卷一、填空题1.(1分) 年,第一次观测到了具有放大作用的晶体管。

2.(2分)摩尔定律是指 。

3.集成电路按工作原理来分可分为 、 、 。

4.(4分)光刻的工艺过程有底膜处理、涂胶、前烘、 、 、 、 和去胶。

5.(4分)MOSFET可以分为 、 、 、 四种基本类型。

6.(3分)影响MOSFET 阈值电压的因素有: 、 以及 。

7.(2分)在CMOS 反相器中,V in ,V out 分别作为PMOS 和NMOS 的 和 ; 作为PMOS 的源极和体端, 作为NMOS 的源极和体端。

8.(2分)CMOS 逻辑电路的功耗可以分为 和 。

9.(3分)下图的传输门阵列中5DD V V =,各管的阈值电压1T V V =,电路中各节点的初始电压为0,如果不考虑衬偏效应,则各输出节点的输出电压Y 1= V ,Y 2= V ,Y 3= V 。

DD 13210.(6分)写出下列电路输出信号的逻辑表达式:Y 1= ;Y 2= ;Y 3= 。

AB Y 1AB23二、画图题:(共12分)=+的电路图,要求使用的1.(6分)画出由静态CMOS电路实现逻辑关系Y ABD CDMOS管最少。

2.(6分)用动态电路级联实现逻辑功能Y ABC=,画出其相应的电路图。

三、简答题:(每小题5分,共20分)1.简单说明n阱CMOS的制作工艺流程,n阱的作用是什么?2.场区氧化的作用是什么,采用LOCOS工艺有什么缺点,更好的隔离方法是什么?3.简述静态CMOS 电路的优点。

4.简述动态电路的优点和存在的问题。

四、分析设计题:(共38分1.(12分)考虑标准0.13m μ CMOS 工艺下NMOS 管,宽长比为W/L=0.26/0.13m m μμ,栅氧厚度为2.6ox t nm =,室温下电子迁移率2220/n cm V s μ=,阈值电压T V =0.3V,计算 1.0GS V =V 、0.3DS V =V 和0.9V 时D I 的大小。

已知:148.8510/o F cm ε-=⨯, 3.9ox ε=。

2.(12分)如图所示,M1和M2两管串联,且B G T A V V V V <-<,请问: 1) 若都是NMOS ,它们各工作在什么状态? 2) 若都是PMOS ,它们各工作在什么状态?3) 证明两管串联的等效导电因子是eff K =1212/()K K K K +。

3.(14分)设计一个CMOS 反相器,要求在驱动10fF 外部负载电容的情况下,输出上升时间和下降时间都不能大于40ps ,并要求最大噪声容限不小于0.55V 。

针对0.13m μ工艺,已知:0.30TN V V =,0.28TP V V =-,2220/n cm V s μ=,276/p cm V s μ=,2.6ox t nm =,148.8510/o F cm ε-=⨯,3.9ox ε=, 1.2DD V V =,ln14.33=2.66,ln14=2.64。

《集成电路原理》期末考试试卷 参考答案一、填空题:(共30分)1.(1分)1947 2.(2分)集成电路中的晶体管数目(也就是集成度)大约每18个月翻一番 3.(3分)数字集成电路,模拟集成电路,数模混合集成电路 4.(4分)曝光,显影,坚膜,刻蚀 5.(4分)增强型NMOS ,耗尽型NMOS ,增强型PMOS ,耗尽型PMOS 6.(3分)栅电极材料,栅氧化层的质量和厚度,衬底掺杂浓度 7.(2分)栅极,漏极,VDD ,GND 8.(2分)动态功耗,静态功耗 9.(3分)4,3,2 10.(6分)()A B C D ++,AB AB +,AB C +二、画图题:(共12分)1.(6分) 2.(6分)Y3三、简答题:(每小题5分,共20分)1.答:n 阱CMOS 的制作工艺流程:1.准备硅片材料;2.形成n 阱;3.场区隔离;4.形成多晶硅栅;5.源漏区n+/p+注入;6.形成接触孔;7.形成金属互连;8.形成钝化层。

n 阱的作用:作为PMOS 管的衬底,把PMOS 管做在n 阱里。

2.答:场区氧化的作用:隔离MOS 晶体管。

LOCOS 工艺的缺点:会形成鸟嘴,使有源区面积比版图设计的小。

更好的隔离方法:浅槽隔离技术。

3.答:1.是一无比电路,具有最大的逻辑摆幅;2.在低电平状态不存在直流导通电流;3.静态功耗低;4.直流噪声容限大;5.采用对称设计获得最佳性能。

4.答:动态电路的优点:1.减少了MOS 管数目,有利于减小面积;2.减小了电容,有利于提高速度;3.保持了无比电路的特点。

动态电路存在的问题:1.靠电荷存储效应保存信息,影响电路的可靠性;2.存在电荷分享、级联、电荷泄漏等问题;3.需要时钟信号控制,增加设计复杂性。

四、分析设计题:(共38分)1.(12分)解:计算MOSFET 导电因子β:142073.98.85100.26()()220584.1()2.6100.13ox n ox n ox W W C A V L t L εεβμμμ---⨯⨯===⨯⨯=⨯ 4分 当 1.0GS V =V(>T V =0.3V)、0.3DS V =V(<0.7GS T V V V -=)时,NMOS 管处于线性区,线性区电流为:21[()]96.3765()2D GS T DS DS I V V V V A βμ=--= 4分当 1.0GS V =V(>T V =0.3V)、0.9DS V =V(>0.7GS T V V V -=)时,NMOS 管处于饱和区,饱和区电流为:2()143.1045()2D GS T I V V A βμ=-= 4分2.(12分)解:1) 设中间节点为C 。

分析知当电压满足V B < V G - V T < V A 时,在电路达到稳态之后,M1和M2都导通。

于是对M1而言,有GS V 0T V ->,即 Vc < V G -V T 。

又V G - V T < V A ,即GS V DS T V V >-,故M1工作于饱和区。

而对M2而言,有GS V T DS V V ->,故M2工作于线性区。

3分 2) 依据NMOSFET 和PMOSFET 的电压反转对称性知,若两管都是PMOSFET ,则M1工作于线性区,M2工作于饱和区。

3分3) 取一例证明。

以此题中的NMOSFET 和给定的偏压为例,两个NMOS 管等效为一个NMOS 管后,依V B < V G - V T < V A 知该等效管应工作于饱和区。

故对M1、M2和等效管Meff 有:21122222()[()()]()D G T C D G T B G T C Deff eff G T B I K V V V I K V V V V V V I K V V V ⎧=--⎪=-----⎨⎪=--⎩则有1212DeffD D effI I I K K K +=由1D I =2D I =Deff I 知: 12111eff K K K += 即K eff = K 1 K 2 / (K 1 + K 2) 6分3.(14分)解:先考虑瞬态特性要求:由()20.1 1.9212(1)0.1(1)0.280.2331.2ln TPPDDPPPPLP DDr r C r K V V V t αααααττ----=-=+===⎧⎡⎤⎪⎣⎦⎪⎪⎨⎪⎪⎪⎩()20.1 1.9212(1)0.1(1)0.30.251.2ln TNNDDNNNNLN DDf f C f K VV V t αααααττ----=-=+===⎧⎡⎤⎪⎣⎦⎪⎪⎨⎪⎪⎪⎩(4分)得424.0810/PKA V-=⨯,424.2210/NKA V-=⨯ (2分)而0OXOX11()()2211()()22OXPPPPPOXOXNNnNnOXWWK C LL tWWK C LL tεεμμεεμμ====⎧⎪⎪⎨⎪⎪⎩(2分)代入相关参数可得()8.09() 2.89PNW LW L==⎧⎪⎨⎪⎩,即{1.0520.376PNm mWWμμ== (2分)考察噪声容限:由it0.607V V == (2分)得:{0.6070.550.5930.55NLMitNLMDDitVV V VVV V V V==>=-=> (2分)所以所设计的CMOS 反相器符合题意要求,即{1.0520.376PNm mWWμμ==。