一位全加器电路版图设计

(免费)用两片74ls138译码器设计一个全加器(word文档良心出品)

用两片74LS138译码器设计一个全加器模电课题实践设计者:洪建峰班级:10电本班学号:201092170102指导老师:崔有明用两片74LS138译码器设计一个全加器作者:洪建峰 201092170102 摘要:两个二进制数之间的算术运算无论是加、减、乘、除,目前在数学计算机中都是化作若干步加法运算进行的。

因此,加法器是构成算术运算器的基本单元。

在将两个多位二进制数相加时,除了最低位以外,每一位都应该考虑来自低位的进位,即将两个对应位的加数和来自低位的进位3个数相加。

这种运算称为全加,所用的电路称为全加器。

本课题是用两片74LS138设计一个全加器。

在考虑到74LS138译码器为3 线-8 线译码器,共有54/74S138和54/74LS138 两种线路结构型式,其74LS138工作原理为:当一个选通端(G1)为高电平,另两个选通端(/(G2A)和/(G2B))为低电平时,可将地址端(A、B、C)的二进制编码在一个对应的输出端以低电平译出。

根据以上特性,设计制作出一个全加器。

关键词:二进制数算术运算;算术运算器;74LS138;全加器。

1设计流程1.1提出方案该次课题从查找资料到方案的制定过程中,分析出四套方案:1.1. 1方案一、将两片74LS138译码器使能端接通,A1B 1作为一个两位二进制数,C1作为低进位,A2B2作为另一个两位二进制数。

通过A1B1C1A2B2输入信号,通过16个输出端与或门的连接,得到了S1S2,以及高进位C0。

1. 1. .2方案二、将两片74LS138连成4/16线译码器,通过参考4/16线连成一个全加器的方法将它连成一个全加器。

1. 1. 3方案三、将74LS138(1)单独连成一个一位二进制全加器。

输出的S0连74LS138(2)的A2作为进入数据,进位信号C0连C2作为第二级上的进位信号,因此,最后的和为S=A1+B1+C1+B2。

1. 1. 4方案四、将两片74LS138通过一系列的与门的输出级联成多位加法器。

实验五1位全加器的文本输入(波形仿真应用)

实验五 1位全加器的文本输入(波形仿真用)1.实验目的通过此实验让学生逐步了解、熟悉和掌握FPGA开发软件Quartus II的使用方法及VHDL 的编程方法。

学习电路的仿真方法。

2.实验内容本实验的内容是建立一个1位全加器。

在实验箱上的按键KEY1~KEY3分别为A、B 和Cin,并通过LED1~LED3指示相应的状态。

输出Sum和Cout通过LED7和LED8指示。

3.实验原理1位全加器的真值表如下所示。

表1位全加器逻辑功能真值表4.实验步骤(1) 启动Quartus II,建立一个空白工程,然后命名为full_add.qpf。

(2) 新建full_add.vhd源程序文件,编写代码。

然后进行综合编译。

若在编译过程中发现错误,则找出并更正错误,直到编译成功为止。

也可采用原理图文件的输入方式,建立半加器,然后在组成1位全加器。

原理图如下所示半加器设计1位全加器设计(3) 波形仿真步骤如下:① 在Quartus II 主界面中选择File → New 命名,打开新建文件对话框,从中选择V ector Waveform File ,如下图所示。

单击OK 建立一个空的波形编辑窗口。

选择File →Saveas 改名为full_add.vwf。

此时会看到窗口内出现如下图所示。

图 新建文件对话框 图 新建波形文件界面② 在上图所示的Name 选项卡内双击鼠标左键,弹出如图 所示的对话框。

在该对话框中单击Node Finder 按钮,弹出如图 所示的对话框。

图 添加节点对话框③ 按照下图所示进行选择和设置,先按下“list ”按钮,再按下“>>”按钮添加所有节点,最后按下“ok ”按钮。

图添加节点④波形编辑器默认的仿真结束时间为1us,根据仿真需要可以设置仿真文件的结束时间。

选择Edit→ End Time命令可以更改。

这里采用默认值不需更改。

图添加完节点的波形图⑤编辑输入节点的波形。

编辑时将使用到波形编辑工具栏中的各种工具。

CMOS反相器

B

18

N阱形成的主要步骤是:

1、外延层;2、原氧化生长;3、第一层掩膜(N阱注 入);4、N阱注入(高能);5、退火,如下图。外延层 与衬底有完全相同的晶格结构,只是纯度更高晶格缺陷更 少。氧化层的主要 作用是:1、保护表面的外延层免受沾 污;2、阻止在注入过程中对硅片过度损伤;3、作为氧化 屏蔽层,有助于控制注入过程中杂质的注入深度。光刻胶 图形覆盖了硅片上的特定区域,将起保护起来免于离子注 入。离子注入机离化杂质原子,使其加速获得高能,选出 最恰当的元素注入,并聚焦离子成为极窄的一束,最后扫 描使硅片不受光刻胶保护的区域得到均匀掺杂。杂质离子 穿透硅的晶格结构,对其共价原子结构造成损伤,这种损 伤在以后的扩散以及退火步骤中得到修复。

源/漏(S/D)注入工艺

为了完成倒掺杂技术,用中等剂量的掺杂稍稍超过LDD的结

深,但是比最初的双阱掺杂的结深浅,上一步形成的侧墙阻止

了注入杂质侵入狭窄的沟道。N+S/D注入的主要步骤是:1、第

七层掩膜(N+S/D注入);2、 N+S/D注入(中等能量)P+S/D

注入的步骤:1、第八层( P+S/D 注入);2、 P+S/D(中等能

B

SUM

≥1

COUT

B

13

---用RTL描述的一位半加器

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY HADDER IS

PORT (A,B:IN STD_LOGIC;

SO,CO:OUT STD_LOGIC);

END ENTITY HADDER;

ARCHITECTURE FH1 OF HADDER IS

CMOS全加器的版图分析

Vss)转折连接,C线二段

不能直接连接,在Vss附近用金属连接。③来自整个电路分为4行,第版图

2和第3行组成进位电路的

前级,第1行和第4行组成

求和电路的前级。

④ 进位与求和的输出反

相器采用较大的宽长比。

版图把abc多晶分成二段且排成二列a线在上面靠近vdd转折连接b线在下面靠近vss转折连接c线二段不能直接连接在vss附附近用金属连接

CMOS全加器的 版图分析

CMOS全加器

特点:

① 几个输入信号被几乎

所有的器件公用.

② 版图把A、B、C多晶

分成二段且排成二列,A

线在上面(靠近Vdd)转折

连接,B线在下面(靠近

半加器&全加器

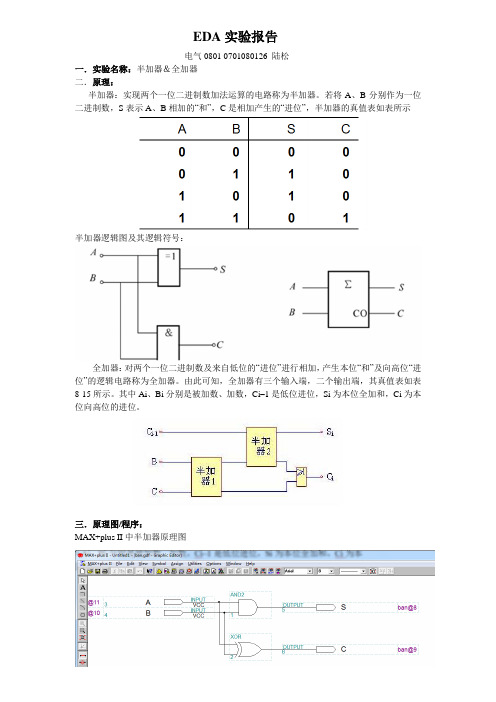

EDA实验报告电气0801 0701080126 陆松一.实验名称:半加器&全加器二.原理:半加器:实现两个一位二进制数加法运算的电路称为半加器。

若将A、B分别作为一位二进制数,S表示A、B相加的“和”,C是相加产生的“进位”,半加器的真值表如表所示半加器逻辑图及其逻辑符号:全加器:对两个一位二进制数及来自低位的“进位”进行相加,产生本位“和”及向高位“进位”的逻辑电路称为全加器。

由此可知,全加器有三个输入端,二个输出端,其真值表如表8-15所示。

其中Ai、Bi分别是被加数、加数,Ci–1是低位进位,Si为本位全加和,Ci为本位向高位的进位。

三.原理图/程序:MAX+plus II中半加器原理图VHDL程序:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY HALF_ADDER ISPORT(A,B:IN STD_LOGIC;S,CO:OUT STD_LOGIC);END HALF_ADDER;ARCHITECTURE HALF_ADDER OF HALF_ADDER IS COMPONENT HALF_ADDERPORT(A,B:IN STD_LOGIC;S,CO:OUT STD_LOGIC);END COMPONENT;BEGINS<='0' WHEN A='0' AND B='0' ELSE'1'WHEN A='0' AND B='1' ELSE'1' WHEN A='1' AND B='0' ELSE'0' WHEN A='1' AND B='1';CO<='0' WHEN A='0' AND B='0' ELSE'0' WHEN A='0' AND B='1' ELSE'0' WHEN A='1' AND B='0' ELSE'1' WHEN A='1' AND B='1';END HALF_ADDER;MAX+plus II中全加器原理图VHDL程序:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY FULL_SUBER ISPORT(A,B,CIN:IN STD_LOGIC;CO,S:OUT STD_LOGIC);END FULL_SUBER;ARCHITECTURE FULL OF FULL_SUBER IS COMPONENT HALF_SUBERPORT(A,B:IN STD_LOGIC;S,CO:OUT STD_LOGIC);END COMPONENT;SIGNAL S1,S2,S3:STD_LOGIC;BEGINU0:HALF_SUBER PORT MAP(A,B,S2,S1);U1:HALF_SUBER PORT MAP(S2,CIN,S,S3);CO<=S1 OR S3;END FULL;四.实验步骤:步骤1:为本项工程设计建立文件夹,文件夹不能为中文名。

北大集成电路版图设计课件_第9章集成电路版图设计实例

22

9.5静电保护电路设计实例

到电路

1.MOS管型静电保护

NMOS GND

P管与N管距离 要远,防闩锁

PAD

VCC

PMOS

23

9.5静电保护电路设计实例

2. 二极管型静电保护

到电路 衬底和 N+构成 的二极管

GND

二极管 标识层

PAD

VCC N阱中的 P+和N+ 构成的二 极管

24

9.5静电保护电路设计实例

8

1:8比例PNP管对称设计

43

9.7带隙基准源版图实例

寄生PNP双极型晶体管版图设计

虚拟管 虚拟管

1

虚拟管

虚拟管

4

1:4比例PNP管对称设计

44

9.7带隙基准源版图实例

寄生PNP双极型晶体管版图设计

1:4比例PNP管对称设计 1:8比例PNP晶体管版图

45

9.7带隙基准源版图实例

对称电阻版图设计

26

9.5静电保护电路设计实例

电源静电保护

栅电容

泄放管

GND

VCC

27

9.5静电保护电路设计实例

二级保护

VCC 二级保护 PAD 限流电阻 二级限流电阻

28

9.5静电保护电路设计实例

二级保护

至内部电路 VCC GND

二级限流电阻

一级保护

29

9.6运算放大器版图设计实例

原理图

VCC Q8 Q3 Q6

垂直走向MOS管结构 水平走向MOS管结构

6

9.2 数字版图设计实例

1.反相器-并联反相器的版图

直接并联

共用漏区

7

一位全加器工作原理

一位全加器工作原理

一位全加器的工作原理是:全加器是用门电路实现两个二进制数相加并求出和的组合线路,称为一位全加器。

一位全加器可以处理低位进位,并输出本位加法进位。

多个一位全加器进行级联可以得到多位全加器。

全加器有两个输入和两个输出:输入是加数A、加数B和进位输入Cin;输出是和数Sum和进位输出Cout。

其中,和数Sum是A和B 相加的结果,进位输出Cout表示向高位的进位。

一位全加器的逻辑表达式为:Sum=A⊕B⊕Cin;Cout=(A∧B)∨(B ∧Cin)∨(A∧Cin),其中⊕表示异或运算,∧表示与运算,∨表示或运算。

一位全加器可以用两个一位半加器和一个或门连接而成。

而一个一位半加器可由基本门电路组成。

半加器只能实现和数的运算,对于1+1=10的进位运算,需要用到全加器。

全加器在设计时需要考虑到电路的功能、性能和可靠性等方面。

在实际应用中,全加器被广泛用于计算机和其他数字系统中,是实现数字电路的重要基础之一。

一位全加器简单设计原理

一位全加器简单设计原理

全加器是数字电路中常用的基本逻辑门之一,它能够实现三个二进制数字的加法运算,即两个数字和来自上一个加器的进位。

这篇文章介绍了一种简单的全加器设计原理,以及实现该设计所需的材料和步骤。

首先,我们需要以下材料:

1. 三个双极性晶体管

2. 两个电阻

3. 一个电源

接下来,我们需要按照以下步骤进行操作:

1. 将三个晶体管连接成一个三角形形状,其中两个晶体管的基极与集电极相连,另一个晶体管的发射极与另一个晶体管的集电极相连。

2. 将两个电阻连接在晶体管三角形的两个角上,以便提供电源和输入信号。

3. 将电源连接到电路中,确保正确极性和电压。

4. 输入两个二进制数字和一个进位信号到电路中,观察输出结果。

通过这种简单的设计原理,我们可以实现一个高效、低成本的全加器电路。

这种设计不仅适用于基本数字电路,还可以用于更复杂的计算机系统中,为数字处理提供更快速和准确的结果。

- 1 -。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

精选文档,希望能帮到您 可编辑修改 目 录 1 绪 论 ..................................................................................................................................... 1

1.1 设计背景 ................................................................................................................. 1

1.2 设计目标 ................................................................................................................. 1

2一位全加器电路原理图编辑 ............................................................................ 2

2.1 一位全加器电路结构 ............................................................................. 2

2.2 一位全加器电路仿真分析波形 .......................................................... 3

2.3 一位全加器电路的版图绘制 ............................................................... 4

2.4一位全加器版图电路仿真并分析波形 ............................................... 4

2.5 LVS检查匹配.............................................................................................. 6

总 结 ........................................................................................................................................... 7

参考文献 ................................................................................................................................. 8

附录一:电路原理图网表 ......................................................... 9 附录二:版图网表 .................................................................... 11 精选文档,希望能帮到您

可编辑修改 1 绪 论 1.1 设计背景 Tanner集成电路设计软件是由Tanner Research 公司开发的基于Windows平台的用于集成电路设计的工具软件。早期的集成电路版图编辑器L-Edit在国内已具有很高的知名度。Tanner EDA Tools 也是在L-Edit的基础上建立起来的。整个设计工具总体上可以归纳为电路设计级和版图设计级两大部分,即以S-Edit为核心的集成电路设计、模拟、验证模块和以L-Edit为核心的集成电路版图编辑与自动布图布线模块。Tanner软件包括S-Edit,T-Spice, L-Edit与LVS[1]。 L-Edit Pro是Tanner EDA软件公司所出品的一个IC设计和验证的高性能软件系统模块,具有高效率,交互式等特点,强大而且完善的功能包括从IC设计到输出,以及最后的加工服务,完全可以媲美百万美元级的IC设计软件。L-Edit Pro包含IC设计编辑器(Layout Editor)、自动布线系统(Standard Cell Place & Route)、线上设计规则检查器(DRC)、组件特性提取器(Device Extractor)、设计布局与电路netlist的比较器(LVS)、CMOS Library、Marco Library,这些模块组成了一个完整的IC设计与验证解决方案。L-Edit Pro丰富完善的功能为每个IC设计者和生产商提供了快速、易用、精确的设计系统。

1.2 设计目标 1.用tanner软件中的原理图编辑器S-Edit编辑一位全加器电路原理图 2.用tanner软件中的TSpice对一位全加器的电路进行仿真并分析波形 3.用tanner软件中的版图编辑器L-Edit进行一位全加器电路的版图绘制,并进行DRC验证 4.用tanner软件中的TSpice对一位全加器的版图进行仿真并分析波形 5.用tanner软件的layout-Edit中的lvs功能对一位全加器进行LVS检验观察原理图与版图的匹配程度精选文档,希望能帮到您 可编辑修改 2一位全加器电路原理图编辑

2.1 一位全加器电路结构 一位全加器电路是数据运算和数字信号处理中应用最广泛的组合模块之一。全加器电路由传统的CMOS电路构成,整个电路分为4行,P管与N管各两行。由于进位电路的器件数少,用第2和第3行组成进位电路的前级,第1行和第4行组成求和电路的前级。由于第2、3行的器件比1、4少,其有源区水平方向的长度比第1、4行短,可以让多晶C从第1行延伸到第4行而不跨越第2.3行的有源区,避免了形成寄生MOS管的可能。PMOS管的衬底连接系统最高电位,NMOS管的衬底连接系统的最低电位[2]。电路原理图如图2.1所示:

图2.1 一位全加器电路原理图 精选文档,希望能帮到您

可编辑修改 2.2 一位全加器电路仿真分析波形 给一位全加器电路网表输入高电平电源电压VDD和低电平GND,添加库,加入激励,再进行瞬态分析[3], .include F:\13\tanner\TSpice70\models\ml2_125.md vvdd VDD GND 5 va A GND PULSE (0 5 0 5n 5n 50n 100n) vb B GND PULSE (0 5 0 5n 5n 60n 120n) vc C GND PULSE (0 5 0 5n 5n 70n 140n) .tran/op 10n 400n method=bdf .print tran v(A) v(B) v(C) v(SUM) v(CO) 对一位全加器电路进行TSpice进行仿真,分析输出波形与自己设计电路的逻辑功能是否一致。波形图如下图2.2所示:

图2.2一位全加器电路原理图输入输出仿真波形精选文档,希望能帮到您

可编辑修改 2.3 一位全加器电路的版图绘制 用L-Edit版图绘制软件对一位全加器电路进行版图绘制,同时进行DRC检查,对于进位和求和的输出反相器都采用了比较大的宽长比,进位从左面输出,求和从右面输出,整个版图的宽度和长度显得比较适中。一位全加器版图如图2.3所示:

图2.3 一位全加器电路版图及DRC验证结果 2.4一位全加器版图电路仿真并分析波形 给一位全加器版图网表输入高电平电源电压VDD和低电平GND,添加库,加入激励,再进行瞬态分析, .include F:\13\tanner\TSpice70\models\ml2_125.md vvdd VDD GND 5 va A GND PULSE (0 5 0 5n 5n 50n 100n)精选文档,希望能帮到您 可编辑修改 vb B GND PULSE (0 5 0 5n 5n 60n 120n) vc C GND PULSE (0 5 0 5n 5n 70n 140n) .tran/op 10n 400n method=bdf .print tran v(A) v(B) v(C) v(SUM) v(CO) 对一位全加器版图进行TSpice进行仿真,分析输出波形与自己设计电路的逻辑功能是否一致。波形图如下图2.4所示:

图2.4一位全加器版图输入输出仿真波形精选文档,希望能帮到您

可编辑修改 2.5 LVS检查匹配 用layout-Edit中的lvs对一位全加器进行LVS检查验证,首先添加输入输出文件,选择要查看的输出,分析输出结果检查一位全加器电路原理图与版图的匹配程度;输出结果如下图2.5所示:

图2.5 一位全加器LVS检查匹配图 由上图的Circuits are equal.可得电路原理图和版图完全匹配。 精选文档,希望能帮到您 可编辑修改 总 结

本次版图课程设计使用tanner软件绘出一位全加器的电路原理图,版图并进行仿真与匹配检查。在绘制电路原理图过程中,由于改错了EXPORT netlist的路径,所以在导出网表的时候出现问题,把原来的库文件给覆盖了,最后复制新的库文件才把问题解决了。 在绘制版图的时候要注意交叠的距离,间距,因为所要画的管子多所以尽量要节省面积,所以尽量用最小宽度来画。最后还要进行DRC检查。 在导出网表的时候一定要先Replace Setup,如果不进行这一步那么后面不能导出网表,在lvs匹配检查的时候一定要把库文件加入电路原理图,否则在匹配的时候就会出现警告,并且在匹配检查的时候一定要把激励屏蔽。在TSpice仿真时候要把激励加入,要仿真的时序加上,最后要分析仿真出来的波形与自己设计的电路逻辑是不是一致。 在本次的课设中在出错和改错的过程中,激起我对版图设计较强的兴趣,在实际运用中结合理论知识才能更好的融会贯通,更好的掌握和理解知识。所以经过这次课程设计,让我对版图这门学科的理论知识和实际应用的软件使用方面有更深的认识,增强自己的综合能力。同时要感谢张老师和同学的无私帮助,让我顺利的完成本次的设计。