接口技术-基于MPC860 PCMCIA的双以太网接口驱动设计

基于MPC860 PCMCIA的双以太网接口驱动设计

(华中科技大学)郝东,杜旭

摘要:MPC860芯片因其强大的通信处理能力和多种协议的支持而被广泛应用于通信领域。但其内部模块仅支持一个10/100M自适应以太网口,限制了应用。本文提出了一种基于其PCMCIA接口扩展的双100M以太网接口的方案,分析了相关驱动程序设计的关键问题。

关键词:嵌入式系统,MPC860,PCMCIA, Linux设备驱动

中图分类号:TP302.1 文献标识码: A 国家十五科技攻关计划:2001BA205A08-09

The Driver Design Of Dual Ethernet Ports Based On

MPC860 PCMCIA Interface

HAO Dong,DU Xu

Abstract: Due to the strong ability of communication processing and support to many protocols, MPC860 is widely used in communication area. But it can only provide one 10/100M

adaptable Ethernet interface directly by its internal modules, which limits its application.

This paper gives out a solution based on the PCMCIA interface of MPC860 and analyzes key problems of the related driver design.

Key words:Embedded System,MPC860,PCMCIA,Linux Device Driver

1.引言

MPC860是互联网络和数据通信及控制领域使用较多、性能相当优越的嵌入式微处理器,其内部集成的CPM (Communication Processor Module) 能完成UART、HDLC、Ethernet 等多种协议的通信控制和处理。然而当应用系统需要两个以上的10M/100M自适应以太网口时, 仅靠片内的通信控制模块便不能满足需求,这是因为:MPC860内部仅有FEC(Fast Ethernet Controller)能实现一个10/100M自适应以太网口,而SCC(Serial Communication Controller)仅支持10M以太网。为了达到应用要求,可以通过MPC860的双PCMCIA接口扩展出两个10/100M自适应以太网口。本文基于这种双PCMCIA扩展以太网口的硬件结构分析了相关驱动程序设计中的关键问题。

2.电路分析和设计

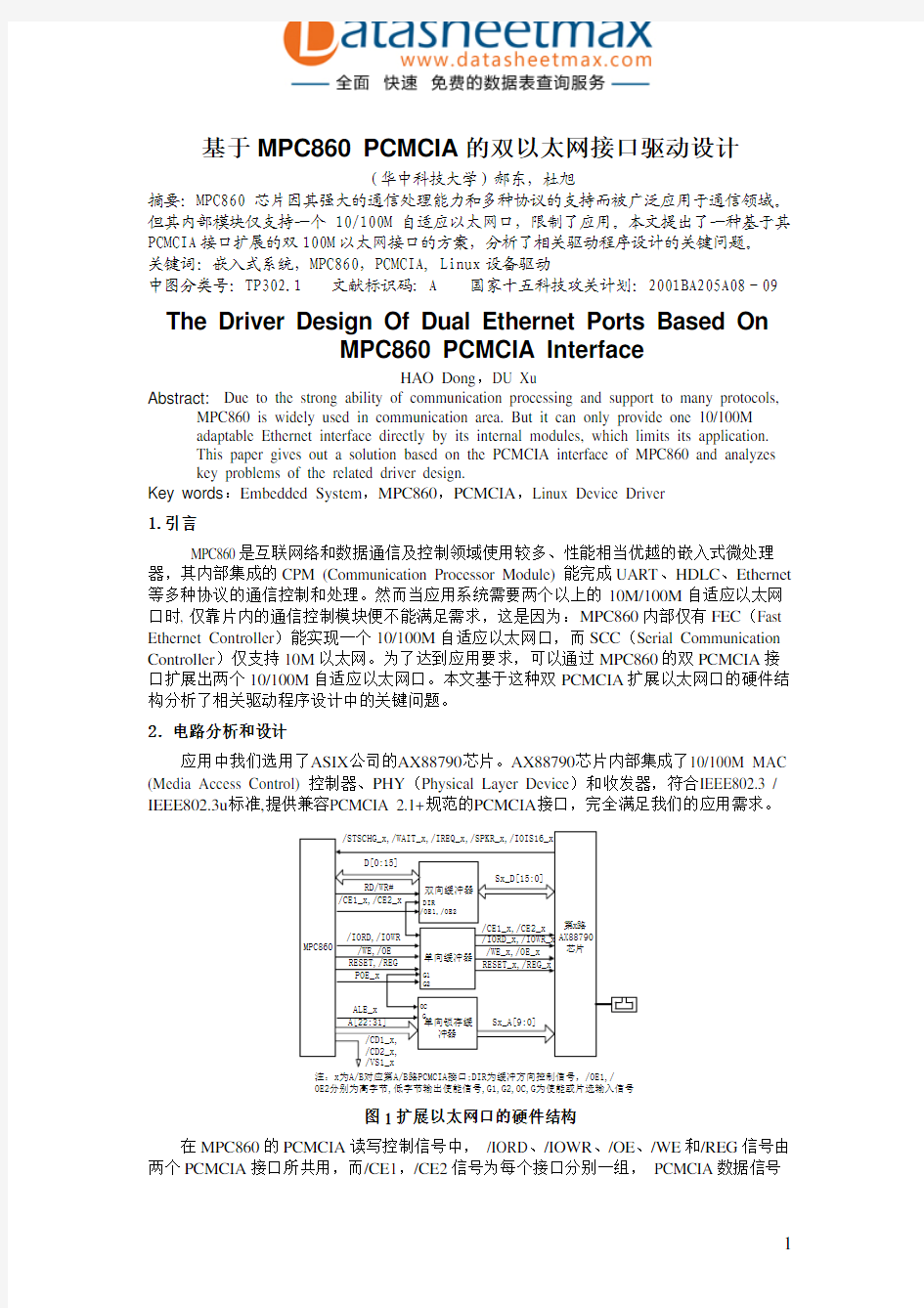

应用中我们选用了ASIX公司的AX88790芯片。AX88790芯片内部集成了10/100M MAC (Media Access Control) 控制器、PHY(Physical Layer Device)和收发器,符合IEEE802.3 / IEEE802.3u标准,提供兼容PCMCIA 2.1+规范的PCMCIA接口,完全满足我们的应用需求。

注:x为A/B对应第A/B路PCMCIA接口;DIR为缓冲方向控制信号,/OE1,/

OE2分别为高字节,低字节输出使能信号,G1,G2,OC,G为使能或片选输入信号

图 1 扩展以太网口的硬件结构

在MPC860的PCMCIA读写控制信号中, /IORD、/IOWR、/OE、/WE和/REG信号由两个PCMCIA接口所共用,而/CE1,/CE2信号为每个接口分别一组, PCMCIA数据信号

和地址信号则均由CPU数据线和地址线提供。另外,MPC860又为每个接口独立读写添加了两个使能信号:地址锁存使能信号/ALE和缓冲输出使能信号/POE。当CPU读写的物理地址落在映射到某个PCMCIA接口的地址区间时,所属PCMCIA接口(A/B)便输出该物理地址到CPU地址线,控制公用的 /IORD、/IOWR、/OE、/WE和/REG信号,并通过仅有效对应接口的/POE(A/B),/ALE(A/B),/CE1(A/B),/CE2(A/B)将两个接口隔离,从而完成两个接口的独立访问。据此我们设计出如图 1的电路结构。

适配器的PCMCIA状态输入信号/CD1, /CD2,/VS1,/VS2是每接口各一组,用于对应接口的PC卡的检测和识别。由于我们的应用目的是通过PCMCIA接口扩展两个10/100M以太网口,并非设计PCMCIA插槽,故将/CD1, /CD2信号长期置于有效状态。另外为了表示AX88790的电源键值为3.3V,我们有效/VS1,而/VS2不连接(No Connection)。其它状态输入信号则上拉至3.3V置于无效状态(见图 1)。

3. 驱动程序设计

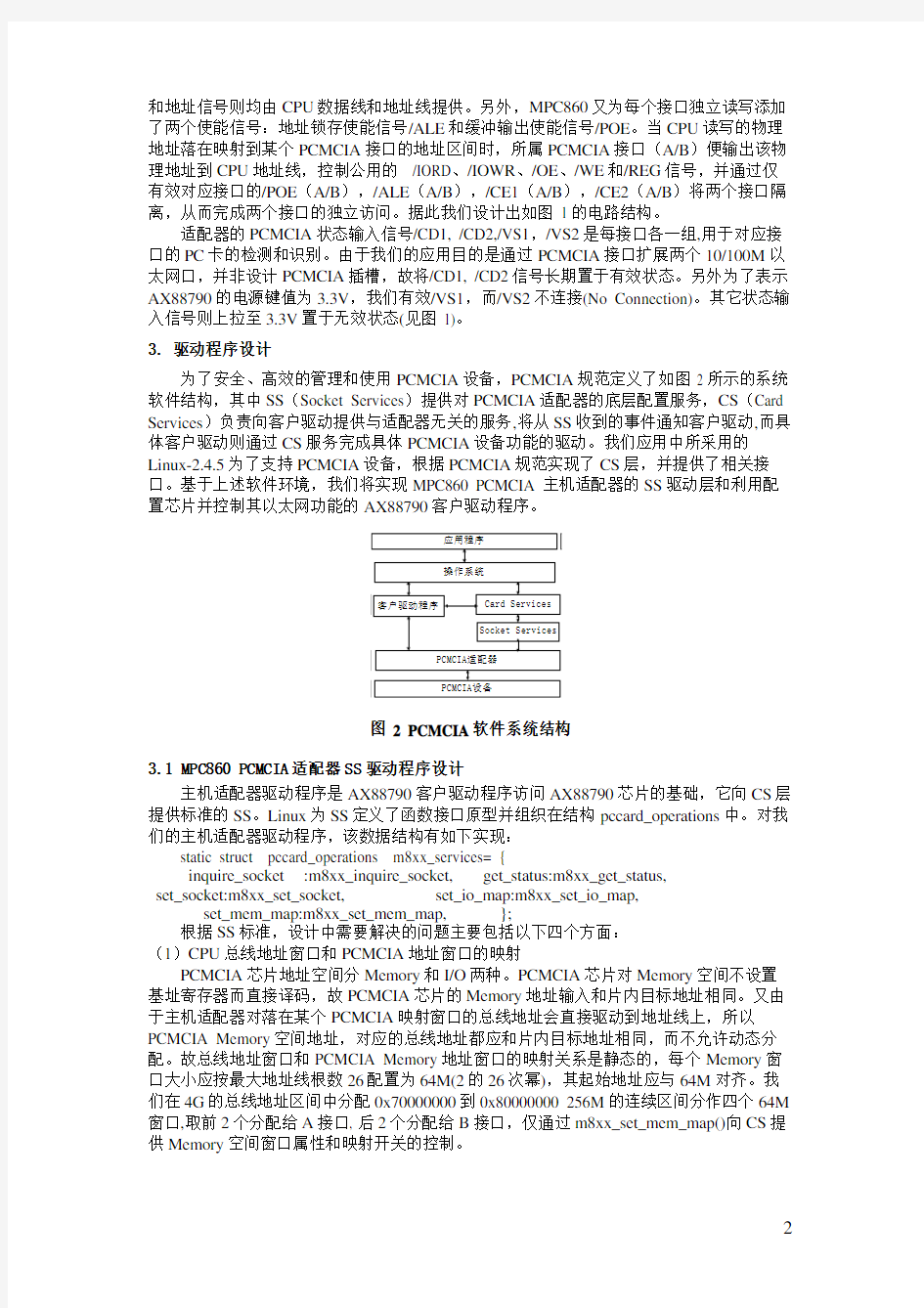

为了安全、高效的管理和使用PCMCIA设备,PCMCIA规范定义了如图 2所示的系统软件结构,其中SS(Socket Services)提供对PCMCIA适配器的底层配置服务,CS(Card Services)负责向客户驱动提供与适配器无关的服务,将从SS收到的事件通知客户驱动,而具体客户驱动则通过CS服务完成具体PCMCIA设备功能的驱动。我们应用中所采用的Linux-2.4.5为了支持PCMCIA设备,根据PCMCIA规范实现了CS层,并提供了相关接口。基于上述软件环境,我们将实现MPC860 PCMCIA 主机适配器的SS驱动层和利用配置芯片并控制其以太网功能的AX88790客户驱动程序。

图 2 PCMCIA软件系统结构

3.1 MPC860 PCMCIA适配器SS驱动程序设计

主机适配器驱动程序是AX88790客户驱动程序访问AX88790芯片的基础,它向CS层提供标准的SS。Linux为SS定义了函数接口原型并组织在结构pccard_operations中。对我们的主机适配器驱动程序,该数据结构有如下实现:

static struct pccard_operations m8xx_services= {

:m8xx_inquire_socket, get_status:m8xx_get_status, inquire_socket

set_socket:m8xx_set_socket,

set_io_map:m8xx_set_io_map,

};

set_mem_map:m8xx_set_mem_map,

根据SS标准,设计中需要解决的问题主要包括以下四个方面:

(1)CPU总线地址窗口和PCMCIA地址窗口的映射

PCMCIA芯片地址空间分Memory和I/O两种。PCMCIA芯片对Memory空间不设置基址寄存器而直接译码,故PCMCIA芯片的Memory地址输入和片内目标地址相同。又由于主机适配器对落在某个PCMCIA映射窗口的总线地址会直接驱动到地址线上,所以PCMCIA Memory空间地址,对应的总线地址都应和片内目标地址相同,而不允许动态分配。故总线地址窗口和PCMCIA Memory地址窗口的映射关系是静态的,每个Memory窗口大小应按最大地址线根数26配置为64M(2的26次幂),其起始地址应与64M对齐。我们在4G的总线地址区间中分配0x70000000到0x80000000 256M的连续区间分作四个64M 窗口,取前2个分配给A接口, 后2个分配给B接口,仅通过m8xx_set_mem_map()向CS提供Memory空间窗口属性和映射开关的控制。

因为PCMCIA芯片I/O基址寄存器的存在,用于映射到I/O空间的系统地址可以由CS 动态分配,只要保证大小在规范限定的64K以内即可。m8xx_set_io_map()向CS提供I/O

空间映射服务。

(2)PCMCIA接口信号的控制和管理

我们通过设置PGCR寄存器控制PCMCIA接口信号,完成CS对接口的控制命令。PGCR寄存器的相应位控制RESET信号和/POE信号的电平状态。例如:

if(state->flags & SS_RESET)

M8XX_PGCRX(_slot_) |= M8XX_PGCRX_CXRESET; //有效_slot_号socket RESET信号else

M8XX_PGCRX(_slot_) &= ~M8XX_PGCRX_CXRESET; //有效_slot_号socket RESET信号是根据命令SS_RESET对RESET的电平设置。

为接口/IREQ信号产生的中断请求分配中断号时,我们考虑到共享中断会引入中断延时而降低驱动性能,因此专门分配7和9使每个接口独占一个中断向量。相应设置PGCR 的IREQLVL后,主机适配器在接口的/IREQ有效时便向处理器核心提交相应的中断请求。

在m8xx_services结构中,m8xx_set_socket()提供接口信号的控制和管理服务。

(3)接口状态的查询和对状态变化的响应

我们通过读取PIPR寄存器查询状态输入信号,并将状态信息提供给CS。

在主机适配器的PCMCIA状态输入信号中,我们固定了/CD1, /CD2,/VS1,/VS2信号的连接,其状态将不会改变。AX88790没有实现PRR (Pin Replace Register) ,因而也无需管理/STSCHG信号的变化。可见基于我们的电路结构不会产生状态信号的改变,更无需处理。在m8xx_services结构中,m8xx_get_status()提供接口状态的查询服务和对状态变化的响应。(4)主机适配器接口特性查询

结合上面的讨论,我们对CS的特性查询返回下面的信息结构:

static socket_cap_t capabilitiesX= { //X 代表A或B插槽

features: SS_CAP_PCCARD|SS_CAP_MEM_ALIGN|SS_CAP_STATIC_MAP,//静态存储映射

irq_mask:0xffff, //可支持1至16的中断号,但若pci_irq 非0则仅支持pci_irq map_size: 0x1000, //存储窗口最小映射单位为4K字节

pci_irq: A接口为9,B接口为7 //分配A接口9号中断,B接口7号中断 } 模块加载时,我们通过register_ss_entry()将m8xx_services向CS注册,接着CS通过函数指针调用m8xx_inquire_socket()查询并获得capabilitiesX接口特性信息,从而建立起CS和PCMCIA主机适配器驱动程序间的桥梁,使CS能正确高效的通过SS配置管理主机控制器。

3.2 AX88790客户驱动程序设计

该驱动程序的设计需要解决下面两个问题:

(1)对AX88790的PCMCIA接口的配置

对AX88790的PCMCIA接口的配置是访问AX88790的I/O寄存器从而驱动其以太网功能的前提,因此在初始化函数中需要最先完成。

首先,基于两片AX88790各与一个PCMCIA接口连接的硬件结构,对每个芯片的控制应各作一个客户驱动并与对应的接口驱动绑定。我们通过CS的BindDevice服务完成。

然后,通过CS的RegisterClient服务注册AX88790客户驱动。在该服务中,CS先通过m8xx_services.set_socket服务有效绑定接口的RESET信号总清AX88790芯片,接着注册事件响应函数axnet_event (),然后通过m8xx_services. get_status服务查询相应接口状态,根据电路连接,查询到的状态为SS_DETECT,于是CS通过回调函数axnet_event ()向AX88790客户驱动发送PC卡插入事件。axnet_event ()对该事件的响应处理便是完成对应AX88790所在PCMCIA接口的配置。通常,客户驱动程序要完成对PC卡的配置应先读取并分析CIS(Card Information Structure)的Tuple项得到它的配置信息,然后根据这些信息为它分配系统资源。在我们的应用中,AX88790芯片是系统中的一个固定部分,而不是作为PC卡使用,因此对它的配置可以直接根据其芯片手册完成,但应注意避免两片AX88790

在系统资源使用上产生冲突。设计时,我们分析解决了下面的问题:

a) AX88790有4个PCMCIA功能配置寄存器,处于属性存储区间 0x3C0~0x3CD。根据主机适配器驱动提供的静态映射特性,该属性存储区间分别被芯片所在的接口映射到系

统地址区间0x700003C0~0x700003CD和0x780003C0~0x780003CD,其读写访问也由对应接口信号控制而不会冲突。AX88790则仅对低10位地址0x3C0~0x3CD译码,这样就保证了对PCMCIA功能配置寄存器的正确访问。

b) AX88790有一个32字节I/O区间作为MAC的寄存器组,片上地址为0x0~0x1F。为了避免两路AX88790产生地址冲突,我们需要利用AX88790芯片的PCMCIA I/O基址配置寄存器。我们指定A路芯片I/O基址为0x300,B路芯片I/O基址为0x380并调用CS的RequestIO服务,得到CPU地址区间:A路0x300~0x31F和B路0x380 ~0x39F。将0x300 (A路)或0x380 (B路)设置到对应的PCMCIA I/O基址配置寄存器中并建立CPU地址区间到PCMCIA I/O区间的映射,就避免了地址冲突和译码混乱。

c)由于AX88790有中断请求线并需要CPU提供中断服务,所以还要通过CS的RequestIRQ服务申请中断号,CS根据与该AX88790客户绑定接口的特性信息capabilitiesX 如下分配中断号:A接口产生9号中断,B 接口的产生7号中断。

至此就申请到了所有无冲突的系统资源。最后由CS的RequestConfiguration服务根据申请到的系统资源配置接口硬件:先由m8xx_set_mem_map()建立属性区间映射,激活其以太网功能,再由m8xx_set_io_map()建立I/O区间映射, 最后由m8xx_set_socket()完成中断向量的设置。自此就可以访问AX88790芯片的MAC寄存器从而驱动其以太网功能了。(2)对AX88790的10/100M以太网功能的驱动

AX88790的MAC寄存器组与NE2000兼容,我们的分析和设计主要有以下三方面:

a) 初始化。AX88790内部的SRAM为32K字节并划分为256字节的页,后16K(页号

0x40至0x80)用作数据缓冲区。我们将0x40开始的12个页用作发送缓冲区,后52个页用作接收缓冲区,并据此初始化接收和发送页号寄存器,启动收发。

b) 以太网数据发送。驱动程序的性能与数据发送部分的代码息息相关,因此应注意数据发送算法的效率。驱动AX88790发送一个数据报需进行两步操作:1) 将要发送的数据通过MAC数据端口寄存器顺序写入AX88790 SRAM中的发送缓存区;2) 向MAC命令寄存器写发送命令触发AX88790的硬件发送。但是当AX88790发送忙时,来自CPU的发送任务必须等待其空闲。因此当来自CPU的新发送任务出现在AX88790正处于硬件发送忙时,我们先完成费时的第一步,而等到AX88790空闲时仅需执行第二步,这样便提高了效率。因此发送缓冲区应至少容纳2个具有最大长度(1518字节,6个256字节的页)的以太网报文,实践证明2个是足够的,这就是在AX88790内部的SRAM中用12个页做发送缓冲区的原因。

c)以太网数据接收。AX88790从物理线路上收完每个报文便产生中断请求,使CPU进入中断服务程序从而完成以太网数据的接收处理。

4. 结束语

本设计已在我们的系统中运用。当系统满负荷运行时,两个网口在 10M/100M模式下均能正常稳定的工作,网络收发没有丢包,说明硬件设计正确完备,驱动程序性能优良。

参考文献

[1] ASIX Electronics Corporation.AX88790 data sheet[M/CD].2000.

[2] PCMCIA/JEIDA. PC Card Standard Release 8[M/CD]. 2001.

[3] 毛德操,胡希明.Linux内核源代码情景分析 (下)[M]. 杭州:浙江大学出版社,2001.

作者简介:郝东,1979年出生,男,汉族,湖北武汉人,硕士研究生,华中科技大学电信系通信与信息系统专业,主要研究方向:嵌入式系统,高性能网络设计,

E-Mail: hddhhddh@https://www.360docs.net/doc/0114757008.html,;杜旭,1970年出生,男,汉族,湖北钟祥人,副教授,华中科技大学电信系,主要研究方向:高速宽带IP网络及应用。通讯地址:(430074 湖北武汉华中科技大学主校区东12舍117室)郝东

Authors’ introduction: Hao Dong, born in 1979, male, Han, graduate student, Dept. of Electronics & Information, Huazhong University Of Science And Technology, major in Communication and Information System, research interests include embedded system and high performance network design, E-mail:hddhhddh@https://www.360docs.net/doc/0114757008.html,. Du Xu, born in 1970, male, Han, associate professor, Dept. of Electronics & Information, Huazhong University Of Science And Technology, research interests include high speed and broadband IP network.

以太网EMC接口电路设计与PCB设计说明

以太网EMC接口电路设计及PCB设计 我们现今使用的网络接口均为以太网接口,目前大部分处理器都支持以太网口。目前以太网按照速率主要包括10M、10/100M、1000M三种接口,10M应用已经很少,基本为10/100M所代替。目前我司产品的以太网接口类型主要采用双绞线的RJ45接口,且基本应用于工控领域,因工控领域的特殊性,所以我们对以太网的器件选型以及PCB设计相当考究。从硬件的角度看,以太网接口电路主要由MAC(Media Access Controlleroler)控制和物理层接口(Physical Layer,PHY)两大部分构成。大部分处理器内部包含了以太网MAC控制,但并不提供物理层接口,故需外接一片物理芯片以提供以太网的接入通道。面对如此复杂的接口电路,相信各位硬件工程师们都想知道该硬件电路如何在PCB上实现。 下图1以太网的典型应用。我们的PCB设计基本是按照这个框图来布局布线,下面我们就以这个框图详解以太网有关的布局布线要点。 图1 以太网典型应用 1.图2网口变压器没有集成在网口连接器里的参考电路PCB布局、布线图,下面就以图2介绍以太网电路的布局、布线需注意的要点。 图2 变压器没有集成在网口连接器的电路PCB布局、布线参考 a)RJ45和变压器之间的距离尽可能的短,晶振远离接口、PCB边缘和其他的高频设备、走线或磁性元件周围,PHY层芯片和变压器之间的距离尽可能短,但有时为了

顾全整体布局,这一点可能比较难满足,但他们之间的距离最大约10~12cm,器件布局的原则是通常按照信号流向放置,切不可绕来绕去; b)PHY层芯片的电源滤波按照要芯片要求设计,通常每个电源端都需放置一个退耦电容,他们可以为信号提供一个低阻抗通路,减小电源和地平面间的谐振,为了让电容起到去耦和旁路的作用,故要保证退耦和旁路电容由电容、走线、过孔、焊盘组成的环路面积尽量小,保证引线电感尽量小; c)网口变压器PHY层芯片侧中心抽头对地的滤波电容要尽量靠近变压器管脚,保证引线最短,分布电感最小; d)网口变压器接口侧的共模电阻和高压电容靠近中心抽头放置,走线短而粗(≥15mil); e)变压器的两边需要割地:即RJ45连接座和变压器的次级线圈用单独的隔离地,隔离区域100mil以上,且在这个隔离区域下没有电源和地层存在。这样做分割处理,就是为了达到初、次级的隔离,控制源端的干扰通过参考平面耦合到次级; f)指示灯的电源线和驱动信号线相邻走线,尽量减小环路面积。指示灯和差分线要进行必要的隔离,两者要保证足够的距离,如有空间可用GND隔开; g)用于连接GND和PGND的电阻及电容需放置地分割区域。 2.以太网的信号线是以差分对(Rx±、Tx±)的形式存在,差分线具有很强共模抑制能力,抗干扰能力强,但是如果布线不当,将会带来严重的信号完整性问题。下面我们来一一介绍差分线的处理要点: a)优先绘制Rx±、Tx±差分对,尽量保持差分对平行、等长、短距,避免过孔、交叉。由于管脚分布、过孔、以及走线空间等因素存在使得差分线长易不匹配,时序会发生偏移,还会引入共模干扰,降低信号质量。所以,相应的要对差分对不匹配的情况作出补偿,使其线长匹配,长度差通常控制在5mil以内,补偿原则是哪里出现长度差补偿哪里; b)当速度要求高时需对Rx±、Tx±差分对进行阻抗控制,通常阻抗控制在100Ω±10%; c)差分信号终端电阻(49.9Ω,有的PHY层芯片可能没有)必须靠近PHY层芯片的Rx±、Tx±管脚放置,这样能更好的消除通信电缆中的信号反射,此电阻有些接电源,有些通过电容接地,这是由PHY芯片决定的; d)差分线对上的滤波电容必须对称放置,否则差模可能转成共模,带来共模噪声,且其走线时不能有stub ,这样才能对高频噪声有良好的抑制能力。

经典中的经典 以太网电接口采用UTP设计的EMC设计指导书

?以太网电接口采用UTP设计的EMC设计指导书 一、UTP(非屏蔽网线)的介绍 非屏蔽网线由两根具有绝缘保护层的铜导线组成,两根绝缘铜导线按照一定密度绞在一起,每一根导线在传输中辐射的电波会与另外一根的抵消,这样可降低信号的干扰程度。 用来衡量UTP的主要指标有: 1、衰减:就是沿链路的信号损失度量。 2、近端串扰:测量一条UTP链路对另一条的影响。 3、直流电阻。 4、衰减串扰比(ACR)。 5、电缆特性。 二、10/100/1000BASE-T以太网电接口原理图设计 10/100/1000BASE-T以太网口电路按照连接器的种类网口电路可以分为:网口变压器集成在连接器里的网口电路和网口变压器不集成在连接器里的网口电路。 1、网口变压器未集成在连接器里的网口电路原理图 网口电路主要包括PHY芯片,网口变压器,网口连接器三部分,图中左侧的八个49.9Ω的电阻是差分线上的终端匹配电阻,其阻值的大小由差分线的特性阻抗决定,当变压器内的线圈匝数发生变化时,其阻值也跟随变化,保证两者的阻抗匹配。由电容组成的差模、共模滤波器可以增强EMC性能。在线圈的中心抽头处接的电容可以有效的改善电路的抗EMC性能,合理的选择电容值可以使电路的EMC做到最优。电路的右侧四个75Ω的电阻是电路的共模阻抗。 2、网口变压器集成在连接器里的网口电路原理图

网口电路主要包括PHY芯片,网口连接器两部分,网口变压器部分集成在接口内部,同样左侧的49.9Ω的电阻阻值也是由变压器的匝数及差分线的特性阻抗决定的。中间的电容组成共模、差模滤波器,滤除共模及差模噪声。75Ω的共模电阻也集成在网口连接器的内部。 3、网口指示灯电路原理图 带指示灯的以太网口电路原理图与不带指示灯灯的大致相同,只是多出指示灯的驱动电路。 注意点: 1)、两个匹配电阻是否需要根据PHY层芯片决定,如有的PHY层芯片内部集成匹配电阻就不需要。匹配电阻是接地还是接电源也是由PHY芯片决定,一般接电源。 2)、芯片侧中间抽头需要通过磁珠串接电源,并且注意每一路接一个磁珠,并通过电容0.01-0.1uf接数字地。 3)、点灯部分电路,link和ACT灯走线要加磁珠处理,同时供电电源也要加磁珠处理。但所有显示驱动灯的电源可以共用一个磁珠。 4)、变压器与连接器部分的匹配电阻75欧姆和50欧姆精度可以放低到5%。

计算机接口技术课程设计

上海应用技术学院课程设计任务书 课程名称计算机接口技术课程设计课程代码B704006 设计题目电子时钟程序设计题目序号 设计时间2011年6月13日——2011年6月24日 系(院)计算机科学与信息 工程 专业 计算机科学与技 术 班级 一、课程设计任务(条件)、具体技术参数(指标) 本课程设计是《计算机接口技术》课程的后继教学环节,通过对一个较大型的、综合性设计及程序进行阅读理解,并在此基础上设计新的功能, 加深学生对本课程专业知识和理论知识的认识和理解,提升学生应用本课程知识体系,构建计算机应用系统,进行应用系统硬件、软件开发的能力。 根据所给的连线.txt、Clock.asm应用程序框架, 在此基础上设计新的功能。 基本任务: 认真阅读文件“连线.tx”、“Clock.asm”源程序,理解设计意图、各芯片的的作用以及程序中每条指令的作用。 实现报时功能:用户设置报时时刻,电子时钟走到该时刻报时。 实现秒表功能:用户可以对单个事件计时。 扩展任务: 实现多个报时功能:用户设置多个报时时刻,电子时钟每走到对应时刻报时。 实现多个秒表功能:用户可以同时对多个事件计时。 其他任务: 自行设计新的功能。 二、对课程设计成果的要求(包括课程设计说明书、图纸、图表、实物等软硬件要求) (1)分析原连线.txt、Clock.asm程序结构: 写出各接口芯片端口地址、控制字、工作方式;绘制接口芯片间连接图;绘制主要模块的流程图。 (2)对新设计的功能:写出详细的功能描述、操作说明;写出设计说明、绘制流程图。 (3)设计总结:对设计中所存在的问题和不足进行分析和总结,提出解决的方法、措施、建议和对这次设计实践的认识、收获和提高。 (4)撰写电子时钟使用说明书,作为报告附录Ⅰ。 (5)电子时钟源程序(修改/增加的指令请使用大写字母,以示区别)作为报告附录Ⅱ(打印版和电子版)。 严禁抄袭,发现雷同,双方扣分 三、课程设计工作进度计划: 第1天:教师布置任务,讲解本课程设计思路、模块。学生细读原始源程序。 第2天:写出各芯片端口地址、控制字、工作方式,绘制芯片间的连线图、主要程序流程图。 第3~4天:设计报时功能及调试程序。 第5~6天:设计秒表功能及调试程序。 第7~8天:设计扩展功能、其他功能及调试程序。 第9~10天:完成设计,提交报告,接受教师考评。 四、主要参考资料 [1] 杨文显主编.现代微型计算机与接口教程,清华大学出版社,2007 [2] 冯博琴,吴宁等.微型计算机原理与接口技术,清华大学出版社,2002 [3] [美]Kip R.Irvine. 电子工业出版社,2004 指导教师(签名):蒯锐教研室主任(签名):杨晶鑫 2011年6月13日2011年6月13日

SPI接口设计与实现

SPI接口设计与实现 SPI(SerialPeripheralInterface)总线是一种同步串行外设接口,它 可以使MCU与各种外围设备以串行方式进行通信以交换信息。SPI总线应用广泛,已经成为很多器件的标准配置,可以直接和各个厂家生产的 多种标准外围器件直接接口。其它常用的串行接口还有I2C、UART这 两种接口,这三种接口互有优缺点。与I2C接口相比,SPI接口速度更快、协议更简单、并且是全双工的,但连线也相对多一些。与UART接口相比,SPI更灵活,因为其使用主设备的时钟进行同步,所以两个比特之间 的时间间隔可以是任意的。在点对点的通信中,SPI接口不需要进行寻 址操作,且为全双工通信,显得简单高效。 1SPI总线工作原理 SPI总线一般以主/从模式工作,通常有一个主设备和一个或多个从设备,数据传输由主机控制,典型SPI结构框图如图1所示。SPI总线包含四条信号线,分别是sclk、miso、mosi和cs,其中,sclk为数据传输时钟,由主机产生;miso是从机输出,主机输入数据线;mosi是主机输出, 从机输入数据线;cs是从设备片选信号,由主机控制,当连接多个从设备时,通过该信号选择不同的从设备。SPI总线是按字节发送数据的,主机和从机内部都包含一个8位串行移位寄存器,在时钟信号控制下,寄存 器内的数据由高到低输出至各自的数据线,8个时钟后,两个寄存器内的数据就被交换了。如果只进行写操作,主机只需忽略接收到的字节;反之,若主机要读取从机的一个字节,就必须发送一个空字节来引发从机 的传输。当主机发送一个连续的数据流时,可以进行多字节传输,在这 种传输方式下,从机的片选端必须在整个传输过程中保持低电平。 根据串行同步时钟极性和相位不同,SPI有四种工作方式。时钟极性(CPOL)为0时,同步时钟的空闲状态为低电平,为1时,同步时钟的空闲 状态为高电平。时钟相位(CPHA)为0时,在同步时钟的第一个跳变沿采 样数据,为1时,在同步时钟的第二个跳变沿采样数据。因为主设备时

接口设计规范

目录 1接口类型 (2) 1.1人机接口 (2) 1.2软件-硬件接口 (2) 1.3软件接口 (2) 1.4通信接口 (2) 2接口设计规范 (2) 2.1基本内容 (2) 2.2规格说明 (3) 2.2.1人机接口 (3) 2.2.2软件-硬件接口 (3) 2.2.3软件接口 (3) 2.2.4通信接口 (3) 3接口设计文档提纲 (3)

1接口类型 1.1人机接口 人机接口是指计算机系统为完成人与机器之间互相传送信息而提供的功能的接口,包括硬件及程序。 1.2软件-硬件接口 软件-硬件接口是指软件系统中软件与硬件之间的接口。例如软件与接口设备之间的接口。 1.3软件接口 软件接口是软件系统中程序之间的接口。包括软件系统与其他系统或子系统之间的接口、程序模块之间的接口、程序单元之间的接口等。 1.4通信接口 通信接口是指处理机和标准通信子系统之间的接口。包括为实现数据通信用来完成接口功能的部件、装置及有关软件。 2接口设计规范 2.1基本内容 1、接口的名称标识 2、接口在该软件系统中的地位和作用 3、接口在该软件系统中与其他程序模块和接口之间的关系 4、接口的功能定义 5、接口的规格和技术要求,包括它们各自适用的标准、协议或约定 6、各个接口的数据特性 7、各个接口的资源要求,包括硬件支持、存储资源分配等 8、接口程序的数据处理要求

9、接口的特殊设计要求 10、接口对程序编制的要求 2.2规格说明 2.2.1人机接口 准确地说明人机接口的设计条件、设计特征、编程要求等技术内容。包括人机交互环境、人机接口部件、信息传输方式及传输特性、信息格式、数据处理、存储资源分配和程序编制要求等。 2.2.2软件-硬件接口 逐个描述每一个软件-硬件间接口的设计特性。包括接口硬件说明、接口功能说明、接口信息说明、接口处理方法、接口控制方式、接口时间特性、存储资源分配和程序编制要求等。 2.2.3软件接口 逐个说明本软件系统与其他软件系统间接口的设计特征。包括接口功能说明、接口约定、数据特性、数据处理方法、接口程序运行控制、接口时间特性、存储资源分配和程序编制要求等。 2.2.4通信接口 逐个描述各个通信接口的设计特性。包括硬件描述、接口功能说明、通信协议、报文处理、存储资源分配、程序接口设计和程序编制要求等。 3接口设计文档提纲 1概述........................................................................................................................................................... 错误!未定义书签。 1.1编写目的......................................................................................................................................... 错误!未定义书签。 1.2参考资料......................................................................................................................................... 错误!未定义书签。 1.3术语和缩写词................................................................................................................................ 错误!未定义书签。2软件系统综述......................................................................................................................................... 错误!未定义书签。3接口设计.................................................................................................................................................. 错误!未定义书签。 3.1接口框图......................................................................................................................................... 错误!未定义书签。 3.2接口一览表.................................................................................................................................... 错误!未定义书签。 3.3人机接口......................................................................................................................................... 错误!未定义书签。 3.4软件-硬件接口 .............................................................................................................................. 错误!未定义书签。

以太网接口PCB设计经验分享

以太网口PCB布线经验分享 目前大部分32 位处理器都支持以太网口。从硬件的角度看,以太网接口电路主要由 MAC 控制器和物理层接口(Physical Layer ,PHY )两大部分构成,目前常见的以太网接口 芯片,如LXT971 、RTL8019 、RTL8201、RTL8039、CS8900、DM9008 等,其内部结构也 主要包含这两部分。 一般32 位处理器内部实际上已包含了以太网MAC 控制,但并未提供物理层接口,因此,需外接一片物理层芯片以提供以太网的接入通道。 常用的单口10M/100Mbps 高速以太网物理层接口器件主要有RTL8201、LXT971 等,均提供MII 接口和传统7 线制网络接口,可方便的与CPU 接口。以太网物理层接口器件主 要功能一般包括:物理编码子层、物理媒体附件、双绞线物理媒体子层、10BASE-TX 编码/ 解码器和双绞线媒体访问单元等。 下面以RTL8201 为例,详细描述以太网接口的有关布局布线问题。 一、布局 CPU M A RTL8201 TX ± 变 压 RJ45 网口 器 C RX± 1、RJ45和变压器之间的距离应当尽可能的缩短. 2、RTL8201的复位信号Rtset 信号(RTL8201 pin 28 )应当尽可能靠近RTL8021,并且,如果可能的话应当远离TX+/-,RX+/-, 和时钟信号。 3、RTL8201的晶体不应该放置在靠近I/O 端口、电路板边缘和其他的高频设备、走线或磁性 元件周围. 4、RTL8201和变压器之间的距离也应该尽可能的短。为了实际操作的方便,这一点经常被放弃。但是,保持Tx±, Rx±信号走线的对称性是非常重要的,而且RTL8201和变压器之间的距离需要保持在一个合理的范围内,最大约10~12cm。 5、Tx+ and Tx- (Rx+ and Rx-) 信号走线长度差应当保持在2cm之内。 二、布线 1、走线的长度不应当超过该信号的最高次谐波( 大约10th) 波长的1/20 。例如:25M的时钟走线不应该超过30cm,125M信号走线不应该超过12cm (Tx ±, Rx ±) 。 2、电源信号的走线( 退耦电容走线, 电源线, 地线) 应该保持短而宽。退耦电容上的过孔直径 最好稍大一点。 3、每一个电容都应当有一个独立的过孔到地。 4、退耦电容应当放在靠近IC的正端(电源),走线要短。每一个RTL8201 模拟电源端都需要退耦电容(pin 32, 36, 48). 每一个RTL8201 数字电源最好也配一个退耦电容。 5、Tx±, Rx ±布线应当注意以下几点: (1)Tx+, Tx- 应当尽可能的等长,Rx+, Rx- s 应当尽可能的等长; (2) Tx±和Rx±走线之间的距离满足下图: (3) Rx±最好不要有过孔, Rx ±布线在元件侧等。

微型计算机原理及接口技术课程设计

微型计算机原理及接口技 术课程设计 学院:信息工程学院 专业:电子信息工程 班级:xxxx班 学号: 6109080203 姓名:XX 指导教师:张坤

第一部分 课程设计任务书 课题名称微型计算机原理及接口技术课程设计——数据采集系统设计 学院(部) 信息工程学院 专业电子信息工程专业 班级610908班 6月11日至6月18日共一周 2010年6月18日

一、设计内容(论文阐述的问题) 设计一个数据采集系统 基本要求:要求具有8路模拟输入 输入信号为0——500mV 采用数码管8位,显示十进制结果 输入量与显示误差<1% 发挥部分:1、速度上实现高精度采集 2、提高系统精度 3、设计抗干扰性 二、设计完成后提交的文件和图表 1. 计算说明书部分: 数据采集是指将压力、流量、温度、位移等模拟量转换成数字量后,再由计算机进行存储、处理、显示、或打印的过程,相应的系统就称为数据采集系统。 数据采集的任务,就是采集传感器输出的模拟信号并转换成计算机能识别的数字信号,然后送入计算机进行相应的计算和处理,取得所需的数据。同时,将计算机得到的数据进行显示或打印,以便实现对某些物理量的监控。 数据采集性能的好坏,主要取决于他的精度和速度。在保证精度的条件下,应有尽可能高的采样速度。 数据采集系统应具有功能: (1)数据采集 计算机按照选定的采样周期,对输入到系统的模拟信号进行采样,称为数据采集。 (2)模拟信号处理 模拟信号是指随时间连续变化的信号,模拟信号处理是指模拟信号经过采样和A/D转换输入计算机后,要进行数据的正确性判断、标度变换、线性化等处理。 (3)数字信号处理 数字信号处理是指数字信号输入计算机后,需要进行码制的转换处理,如

以太网通信接口电路设计规范

目录 1目的 (3) 2范围 (3) 3定义 (3) 3.1以太网名词范围定义 (3) 3.2缩略语和英文名词解释 (3) 4引用标准和参考资料 (4) 5以太网物理层电路设计规范 (4) 5.1:10M物理层芯片特点 (4) 5.1.1:10M物理层芯片的分层模型 (4) 5.1.2:10M物理层芯片的接口 (5) 5.1.3:10M物理层芯片的发展 (6) 5.2:100M物理层芯片特点 (6) 5.2.1:100M物理层芯片和10M物理层芯片的不同 (6) 5.2.2:100M物理层芯片的分层模型 (6) 5.2.3:100M物理层数据的发送和接收过程 (8) 5.2.4:100M物理层芯片的寄存器分析 (8) 5.2.5:100M物理层芯片的自协商技术 (10) 5.2.5.1:自商技术概述 (10) 5.2.5.2:自协商技术的功能规范 (11) 5.2.5.3:自协商技术中的信息编码 (11) 5.2.5.4:自协商功能的寄存器控制 (14) 5.2.6:100M物理层芯片的接口信号管脚 (15) 5.3:典型物理层器件分析 (16) 5.4:多口物理层器件分析 (16) 5.4.1:多口物理层器件的介绍 (16) 5.4.2:典型多口物理层器件分析。 (17) 6以太网MAC层接口电路设计规范 (17) 6.1:单口MAC层芯片简介 (17) 6.2:以太网MAC层的技术标准 (18) 6.3:单口MAC层芯片的模块和接口 (19) 6.4:单口MAC层芯片的使用范例 (20) 71000M以太网(单口)接口电路设计规范 (21) 8以太网交换芯片电路设计规范 (21) 8.1:以太网交换芯片的特点 (21) 8.1.1:以太网交换芯片的发展过程 (21) 8.1.2:以太网交换芯片的特性 (22) 8.2:以太网交换芯片的接口 (22) 8.3:MII接口分析 (23) 8.3.1:MII发送数据信号接口 (24) 8.3.2:MII接收数据信号接口 (25) 8.3.3:PHY侧状态指示信号接口 (25) 8.3.4:MII的管理信号MDIO接口 (25) 8.4:以太网交换芯片电路设计要点 (27) 8.5:以太网交换芯片典型电路 (27) 8.5.1:以太网交换芯片典型电路一 (28)

微机原理与接口技术电子表设计

… 微机原理与接口技术 课程设计报告 、 设计名称:电子表设计 专业:计算机原理与接口技术 班级: 姓名: 学号: 指导教师: |

2014年 11 月 27 日

目录 摘要 (2) 一、设计目的及要求 (3) 设计任务 (3) 设计功能 (3) 课程设计方式及基本要求 (3) 实验方式 (3) * 基本要求 (3) 设计所用元件 (4) 二、设计题目及思想 (4) 设计原理 (4) 主要模块 (5) 芯片初始化 (7) 程序流程图 (9) 硬件接线图 (11) | 三、调试结果 (13) 四、课程设计总结 (16) 遇到问题及解决方案 (16) 课程设计心得体会 (16) 参考文献 附录 `

摘要 汇编语言是计算机能够提供给用户使用的最快而又最有效的语言,也是能够利用计算机所有硬件特性并能直接控制硬件的唯一语言。因而,对程序的空间和时间的要求很高的场合,汇编语言的应用是必不可少的。至于很多需要直接控制硬件的应用场合,则更是非用汇编语言不可了。随着科学技术迅速发展,理工科大学生不仅需要掌握计算机方面的基本理论知识,而且还需要掌握基本的实验技能及一定的科学研究能力。 通过课程设计,使学生巩固和加深微型计算机原理理论知识,通过实践进一步加强学生独立分析问题和解决问题的能力、综合设计及创新能力的培养,同时注意培养学生实事求是、严肃认真的科学作风和良好的实验习惯,为今后工作打下良好的基础。鉴于汇编语言的广泛用途及其在当代计算机界的重要作用,本人利用学的知识,在同学门的帮助下,花费大量时间,完成了关于电子表的系统设计。这个系统是应用于电脑中的小应用程序,可是显示电脑中的时间。很多地方都会有个时钟显示,其中大多是应用了类似这样的方法。 关键词:汇编语言微机原理接口技术时钟显示

接口与接口设计原则

接口与接口设计原则 一.11种设计原则 1.单一职责原则 - Single Responsibility Principle(SRP) 就一个类而言,应该仅有一个引起它变化的原因。职责即为“变化的原因”。 2.开放-封闭原则 - Open Close Principle(OCP) 软件实体(类、模块、函数等)应该是可以扩展的,但是不可修改。对于扩展是开放的,对于更改是封闭的. 关键是抽象.将一个功能的通用部分和实现细节部分清晰的分离开来。开发人员应该仅仅对程序中呈现出频繁变化的那些部分作出抽象. 拒绝不成熟的抽象和抽象本身一样重要 ) 3.里氏替换原则 - Liskov Substitution Principle(LSP) 子类型(subclass)必须能够替换掉它们的基类型(superclass)。 4.依赖倒置原则(IoCP) 或依赖注入原则 - Dependence Inversion Principle(DIP)

抽象不应该依赖于细节。细节应该依赖于抽象。Hollywood原则: "Don't call us, we'll call you". 程序中所有的依赖关系都应该终止于抽象类和接口。针对接口而非实现编程。任何变量都不应该持有一个指向具体类的指针或引用。任何类都不应该从具体类派生。任何方法都不应该覆写他的任何基类中的已经实现了的方法。 5.接口隔离原则(ISP) 不应该强迫客户依赖于它们不用的方法。接口属于客户,不属于它所在的类层次结构。多个面向特定用户的接口胜于一个通用接口。 6.重用发布等价原则(REP) 重用的粒度就是发布的粒度。 7.共同封闭原则(CCP) 包(类库、DLL)中的所有类对于同一类性质的变化应该是共同封闭的。一个变化若对一个包产生影响,则将对该包中的所有类产生影响,而对于其他的包不造成任何影响。 8.共同重用原则(CRP) 一个包(类库、DLL)中的所有类应该是共同重用的。 如果重用了包(类库、DLL)中的一个类,

计算机控制与接口技术课程设计

一.设计题目任务及要求 1. 设计题目:水温控制系统的设计 2. 设计要求: 设计一个水温控控制系统,对象的传递函数:G (s )= e 1 s 10020 -50s ,炉子为电炉结构,单相交流2220V 供电。温度设定值:室温~100℃,可以根据要求任意调节。要求: (1) 画出电路原理图,包括:给定值、反馈、显示的电路以及主电路; (2) 阐述电路的工作原理; (3) 采用对象为大滞后的算法,求出U (k ); (4) 画出闭环数字控制的程序框图。 二.设计任务分析 1.系统设计: 该系统由AT89C51单片机系统、PID 控制算法、温度检测、键盘输入、温度显示、加热丝功率控制等等组成。 Ⅰ.典型的反馈式温度控制系统通常由下图(a )所示的几部分组成,其中调节器由微型机来完成。 图(a ) 温度控制系统组成框图 Ⅱ.给定信号如何给计算机 温度给定值可以通过计算机键盘输入(键盘与单片机连接),也可以通过数学表达式由程序自动设定,还可以用拨码盘,一般拨码盘常用于过程控制的控制柜(化工企业)。 为了便于讨论,本设计假定由人工键盘输入温度给定值。

Ⅲ.温度的监测与调节 理想的情况是采用A/D转换器作为输入通道,当精度要求不高时,可以半导体热敏电阻测量温度,和通过单稳态触发器输出的脉冲宽度来实现温度检测和输入。用热敏电阻也是一种常用的方式。热敏电阻作为半导体的效果往往决定于环境和计算机应用程序配合的结果。 可以采用温度范围为0~120℃的热敏电阻来构成所需要的电路,不用热电偶的原因是:因为热电偶在低温段线性差,它只是在高温段准确。 2.控制方案 本系统中把晶闸管电阻炉温度变送器统一称为被控对象。电阻炉系统是个自衡系统,可以近似为一个一阶惯性环节和一个延迟环节,传递函数可以表示为: 在检测的基础上,我们采用数字PID调节规律,把炉内温度控制的设定值与实测值进行比较,是静态误差最小。 理论分析和实践证明电阻炉是一个具有自平衡能力的对象,可以用一个一阶惯性环节和一个延迟环节来近似描述,考虑到零阶保持器,系统的简化动态结构图如图(b)

RJ45以太网接口EMC防雷设计方案

以太网接口EMC设计方案 一、接口概述 RJ45以太网接口是目前应用最广泛的通讯设备接口,以太网口的电磁兼容性能关系到通讯设备的稳定运行。 二、接口电路原理图的EMC设计 百兆以太网接口2KV防雷滤波设计 图1 百兆以太网接口2KV防雷滤波设计 接口电路设计概述: 本方案从EMC原理上,进行了相关的抑制干扰和抗敏感度的设计;从设计层次解决EMC问题;同时此电路兼容了百兆以太网接口防雷设计。 本防雷电路设计可通过IEC61000-4-5或GB17626.5标准,共模2KV,差摸1KV的非屏蔽平衡信号的接口防雷测试。 电路EMC设计说明: (1) 电路滤波设计要点: 为了抑制RJ45接口通过电缆带出的共模干扰,建议设计过程中将常规网络变压器改为接口带有共模抑制作用的网络变压器,此种变压器示意图如下。

图2 带有共模抑制作用的网络变压器 RJ45接口的NC空余针脚一定要采用BOB-smith电路设计,以达到信号阻抗匹配,抑制对外干扰的作用,经过测试,BOB-smith电路能有10个dB左右的抑制干扰的效果。 网络变压器虽然带有隔离作用,但是由于变压器初次级线圈之间存在着几个pF的分布电容;为了提升变压器的隔离作用,建议在变压器的次级电路上增加对地滤波电容,如电路图上C4-C7,此电容取值5Pf~10pF。 在变压器驱动电源电路上,增加LC型滤波,抑制电源系统带来的干扰,如电路图上L1、C1、C2、C3,L1采用磁珠,典型值为600Ω/100MHz,电容取值0.01μF~0.1μF。 百兆以太网的设计中,如果在不影响通讯质量的情况,适当减低网络驱动电压电平,对于EMC干扰抑制会有一定的帮助;也可以在变压器次级的发送端和接收端差分线上串加10Ω的电阻来抑制干扰。 (2) 电路防雷设计要点: 为了达到IEC61000-4-5或GB17626.5标准,共模2KV,差摸1KV的防雷测试要求,成本最低的设计方案就是变压器初级中心抽头通过防雷器件接地,电路图上的D1可以选择成本较低的半导体放电管,但是要注意“防护器件标称电压要求大于等于6V;防护器件峰值电流要求大于等于50A;防护器件峰值功率要求大于等于300 W。注意选择半导体放电管,要注意器件“断态电压、维持电流”均要大于电路工作电压和工作电流。 根据测试标准要求,对于非屏蔽的平衡信号,不要求强制性进行差模测试,所以对于差模1KV以内的防护要求,可以通过变压器自身绕阻来防护能量冲击,不需要增加差模防护器件。 接口电路设计备注: 如果设备为金属外壳,同时单板可以独立的划分出接口地,那么金属外壳与接口地直接电气连接,且单板地与接口地通过1000pF电容相连。

系统对接接口设计

1.社会服务系统对接接口设计 系统能提供兼容不同技术架构的数据接口,保证系统与省级各联合审批职能部门及其他电子政务系统进行数据交换。 1.1.数据交换接口 数据交换平台基于Java技术和标准数据库接口(JDBC、ODBC等),为不同的数据库系统、应用系统、专用中间件系统提供接入组件,通过对接口协议需求进行抽象,使用TongIntegrator框架,就可以和特定系统的交互。另外提供组件定制接口,可以方便、快速地添加具有新的功能的组件。数据交换平台提供了大量的扩展接口,方便用户进行功能扩展。 1.1.1.提供企业级需求的标准接口 数据压缩,减少带宽瓶颈;数据加密,提高系统安全性;异常处理,创建和维持了一个“消息异常处理器”的接口,它可以保存因为某种原因不能处理的消息,这些“异常”消息还可以被送回重新加以处理。 1.1. 2.提供可扩展的告警方式接口 平台默认实现了邮件告警方式,只需要配置相应的邮件信息,当有警告产生时,会自动发送告警邮件给邮件接收者。同时平台还提供了可扩展的告警方式接口,可根据项目需要扩展不同的告警方式,如短信告警等。 1.1.3.提供第三方的压缩和加密算法接口 提供数据压缩和加密功能,产品本身带有一套数据压缩、加密算法,同时也为第三方的压缩和加密算法提供了接口,用户可以方便的将自己指定的压缩和加密算法嵌入到系统中。 1.1.4.系统特点 易于维护 通过使应用松耦合或分离,使系统环境中的接口更容易维护。同时通过数据交换平台对外提供统一接口,屏蔽了单个系统内部的改变,可以很容易替换过时的应用。 可扩展 数据交换平台提供了大量的扩展接口,方便用户进行功能扩展。

嵌入式系统的以太网接口设计

龙源期刊网 https://www.360docs.net/doc/0114757008.html, 嵌入式系统的以太网接口设计 作者:于申申 来源:《硅谷》2011年第17期 摘要:随着网络和嵌入式系统的发展,嵌入式系统与网络的结合已经成为最新的研究方向。使用处理器S3C44B0X和以太网接口芯片RTL8019AS,设计一种通用的嵌入式系统以太网接口设计与实现方案。这种设计结构简单,实现方便,具有很好的实用价值。 关键词: S3C44BOX; RTL8019AS; uCLinux操作系统 中图分类号:TP368 文献标识码:A 文章编号:1671-7597(2011)0910067-01 目前,随着计算机技术、通信技术的飞速发展,以太网以它的普遍性及低廉的接口价格,已经作为一种最通用的网络,广泛应用于生产和生活中。使得我们在计算机进行网络互连的同时,许多领域的嵌入式设备如工业控制、数据采集、数控机床和智能仪表等也有接入网络的需求。伴随着信息家电出现,嵌入式设备的网络化必将拥有更广阔的发展前途。在这个过程里,首先要解决的是嵌入式设备如何实现网络互连。 本文基于常用的嵌人式处理器S3C44B0X和以太网驱动器RTL8019AS以及μClinux系统设计了一款嵌人式以太网接口。该方案和其它设计比较具有高性能、低功耗、软硬件易扩展特点,是当前及今后工业以太网控制器的理想选择方案。本设计的特点是,既可仅用于嵌人式以太网驱动设备,方便简单,又可进行扩展其他模块,必要时可以移植操作系统,应用于其他复杂领域。 1 芯片简介 1.1 S3C44B0X芯片概述 系统的CPU采用S3C44B0X,它是Samsung公司推出的16/32位RISC处理器,采用了ARM7TDMI内核,0.25um工艺的CMOS标准宏单元和存储编译器。S3C44B0X还采用了一种新的总线结构,即SAMBA-II(三星ARM嵌入式微处理器总线结构)。S3C44B0X[1]通过提供全面的、通用的片上外设,大大减少了系统电路中外围元器件配置,从而最小化系统的成本,它为一般应用提供了高性价比和高性能的微处理器解决方案。 由于S3C44B0X微处理器集成了丰富的外设,非常适合控制管理。而μClinux系统又可对多种硬件资源进行控制,加之S3C44B0X对μClinux操作系统的完美支持,故采用了三星公司S3C44B0X芯片作为微处理器。

C语言中数据库接口的设计与实现

Computer Science and Application 计算机科学与应用, 2019, 9(8), 1554-1560 Published Online August 2019 in Hans. https://www.360docs.net/doc/0114757008.html,/journal/csa https://https://www.360docs.net/doc/0114757008.html,/10.12677/csa.2019.98174 Design and Implementation of Database Interface in C Language Ping Wang Fuzhou University of International Studies and Trade, Fuzhou Fujian Received: July 28th, 2019; accepted: August 12th, 2019; published: August 19th, 2019 Abstract After explaining the characteristics of C language and the importance of database technology, this paper introduces the Union and extensiveness of the two technologies in the application of equipment process control. It focuses on the detailed analysis of the database interface technology encountered in the system development, and shows its application field from one side through an example. Keywords C Language, Database, Interface Technology, Development and Application C语言中数据库接口的设计与实现 王平 福州外语外贸学院,福建福州 收稿日期:2019年7月28日;录用日期:2019年8月12日;发布日期:2019年8月19日 摘要 本文在阐述C语言的特点以及数据库技术的重要性之后,简述了二者在设备过程控制应用中的结合性和广泛性,着重就系统开发中碰到的数据库的接口技术进行详细解析,并通过一个示例从一个侧面展示了其应用领域。 关键词 C语言,数据库,接口技术,开发应用

单片机与接口技术项目设计

单片机与接口技术课程设计项目 项目要求:每个小组2-3人,每个题目最多限两个小组选。 验收内容包括: 1、面包板现场显示结果;项目要求全部完成为30分 2、软件仿真结果。要求全部完成为30分 3、焊接板显示结果;要求全部完成为40分 项目扩展:可以自己设计题目。 一、基于单片机的交通灯显示系统(一) 设计内容: 1、东西方向、南北方向均有红、黄、绿三种信号灯; 2、带紧急制动按钮,按钮按下,所有方向亮红灯;再次按下,恢复正常显示; 3、夜间模式按钮按下,所有方向显示黄灯闪烁; 4、实时提醒绿灯亮的剩余时间。 二、基于单片机的交通灯显示系统(二) 设计内容: 1、东西干道和南北干道的通行分左行、右行、直行,其中左行、右行固定15秒;直行固定30秒。 2、信号灯分绿灯、红灯、黄灯,每次绿灯换红灯时,黄灯亮3秒钟。 3、东西干道和南北干道交替控制,每次干道绿灯交替时,有3秒钟所有干道的交通灯都是黄灯闪烁3秒钟,提示已经进入路口的车辆迅速通过。 三、基于单片机的交通灯显示系统(三) 设计内容:自行设计路口车辆的通行模式,比如通过探测车辆有无改变当前亮灯模式的交通灯显示系统。 四、简易电子琴设计 设计内容: 1、用按键或键盘代表琴键,至少能弹出8个音符,分别是:音符 1,2,3,4,5,6,7

2、键按下的时间长短表征节拍的长短; 3、用蜂鸣器发出声音; 4、点阵或数码管或灯实时动态显示音符高低(自由显示) 五、音乐玩具设计(如音乐娃娃) 设计内容: 1、用按键或键盘代表娃娃的不同部位,按不同部位分别播放不同的音乐,或发出不同的声响,如哭声笑声; 2、用2个LED灯代表2只眼睛,不同的音乐和声音2只眼睛配合不同的闪动效果(自由设计) 六、电风扇模拟控制系统设计 设计内容: 1、3个独立按键分别控制“自然风”、“睡眠风”、“常风”,(三者的区别是直流电机的停歇时间不同),并在数显管上显示出区别; 2、每种类型风可以根据按下独立按键次数分为4个档的风力调节。 3、设计风扇的过热保护,用继电器实现。即当风扇运行一段时间后,暂停10秒。 4、其他创新内容(如报警提示) 七、洗衣机模拟控制系统设计 设计内容: 1、2个独立按键分别选择“漂洗1次”或“漂洗2次”两种洗衣模式; 2、两种漂洗模式电机转动要求不同(两者的区别可用直流电机的停歇时间不同表示) 3、进水和排水用继电器动作来表示; 4、洗衣完成后报警提示。 八、微波炉控制设计 设计要求: 设置开始键,功率设置键(设置功率,可以分为大、中、小三档,初始为中档,由LED显示),定时键(设置时间)以及复位键。

微机接口技术课程设计(DOC)

河北科技大学 课程设计报告 学生姓名:学号: 专业班级:电子信息工程班 课程名称:微机接口技术课程设计学年学期:2014—2015学年第二学期指导教师:王震洲 2 01 5 年7 月

课程设计成绩评定表

目录 一、课程设计目的及意义 (1) 二、课程设计任务及要求 (1) 三、设计内容与步骤 (1) 四、硬件电路设计 (2) 五、程序设计 (7) 六、数字频率示波器调试 (11) 七、课程设计总结及体会 (13) 附录:、接口实验卡电路原理图 (14)

一、课程设计目的及意义 数字存储示波器是常用的电子测量仪器之一,其中采用的转换、转换及数据处理技术与《微机接口技术》课程内容联系紧密。通过本设计,学生可掌握、转换电路的设计和调试方法,培养学生分析解决实际问题的能力。 二、课程设计任务及设计要求 本设计通过简单的转换接口电路,配合汇编语言程序设计,实现最基本的信号波形采集与存储,并通过简单的转换接口电路,将存储的数据还原为信号波形,在普通示波器的屏幕上显示出来。 被测信号产生电路参见“、接口实验扩展卡电路原理图”。当按下S1时,电容C5完全放电,转换器输入电压为零;抬起S1时,电容C5开始充电,转换器输入电压按过渡过程开始上升,最终达到+5V。图中时间常数约为10,整个充电过程需要3~5倍的时间常数时间。设计要求使用转换器捕捉电容C5充电的完整过程,并将采样数据存储起来。然后依次将采样数据通过转换器循环输出,产生一定频率的重复波形,送到普通示波器显示。 基本要求:使用一个转换器通道,将信号波形施加到示波器的Y轴,X轴扫描信号由示波器产生并调节,实现充电过程的波形稳定显示。 发挥部分:将示波器调整在方式,采样数据的转换器输出接到Y轴输入端,增加一个转换器通道,产生频率可变的X轴扫描信号,接到示波器X轴外部输入端,使充电过程的波形稳定显示。 三、设计内容与步骤 1、数字存储示波器原理分析 由于单片机实验系统已经提供了相关信号线,使用0809、0832和相关外围电路元件,组成了最基本的转换和转换电路。可由0809负责采集电容C5充电时的信号,并将其转换为数字信号,并存储。0832将存储的数字信号,转换为模拟的电压值,再将其设置为循环输出,产生一定频率的重复波形,送到普通示波器显示。