Verilog代码覆盖率检查

Verilog代码覆盖率检查

?对于复杂的设计来说,Verilog代码覆盖率检查是检查验证工作是否完全的重要方法,代码覆盖率(codecoverge)可以指示Verilog代码描述的功能有多少在仿真过程中被验证过了,代码覆盖率分析包括以下分析内容。

?

?

?

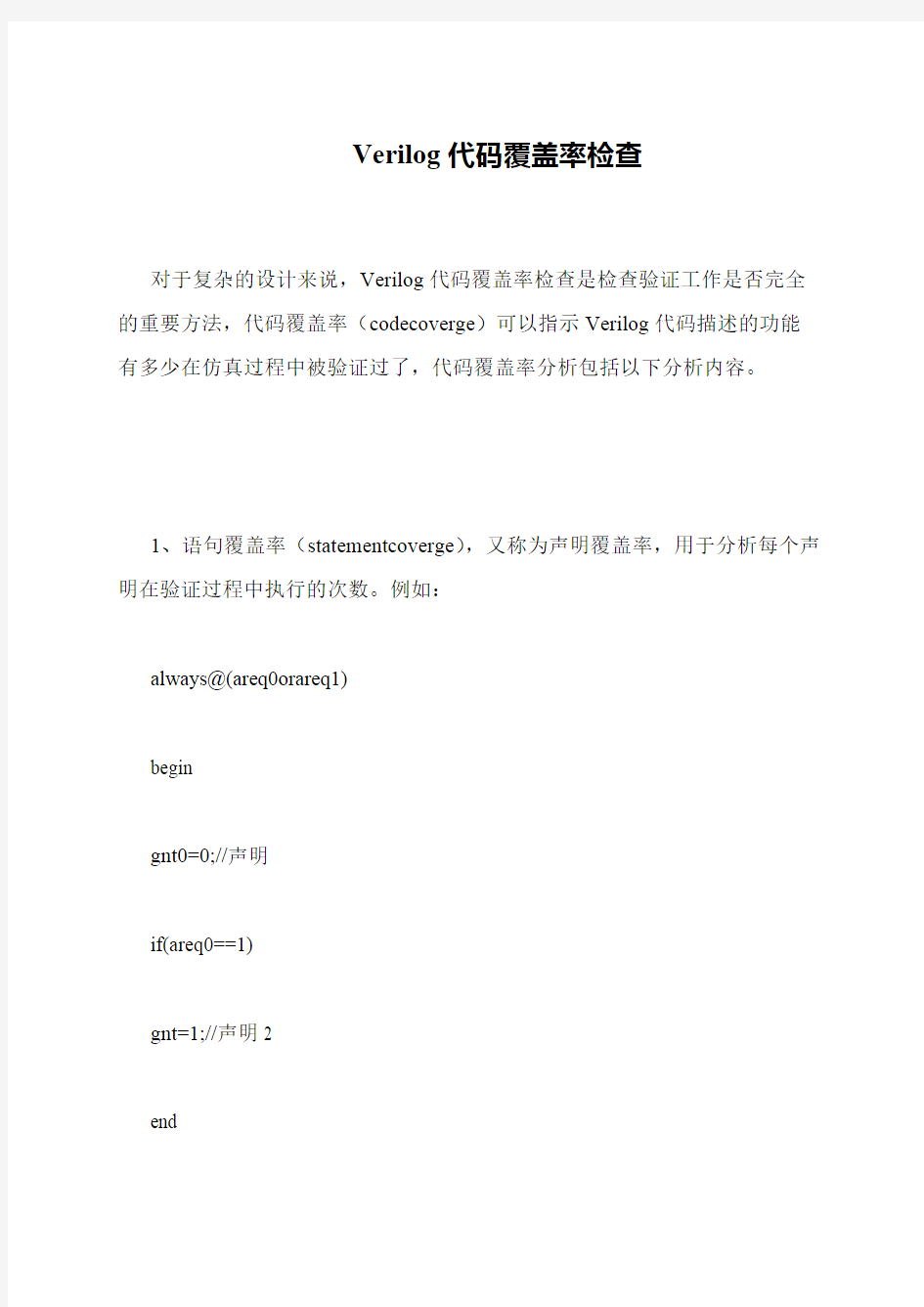

?1、语句覆盖率(statementcoverge),又称为声明覆盖率,用于分析每个声明在验证过程中执行的次数。例如:

?

?always@(areq0orareq1)

?

?begin

?

?gnt0=0;//声明

?

?if(areq0==1)

?

?gnt=1;//声明2

?

?end

?

Director 疑难解答

Director 疑难解答 01. 如何制作一个放映机(projector)可以在不同分辨率下播放? [A] 加入下列语句: on prepareMovie (the stage).rect = (the desktopRectList)[1] (the stage).drawRect = (the desktopRectList)[1] end 注意,这个语句是通过放大或缩小舞台来达到效果的,所以会有变形。 02. 如何导入photoshop的图层? [A] Director7.0以后的版本你可以通过Medialab公司的Photocaster Xtra来实现。 03. 在程序中如何导入图片而不失去图片周围的白色部份? [A] 通过指定图片的trim whitespace属性可以实现: m = new(#bitmap) m.trimWhiteSpace = 0 m.filename = the moviePath & ‘‘file.bmp‘‘ m.media = m.media 04. 如何得到全局变量列表? [A] 在messages的窗口中,你可以输入showGlobals来显示所有的全局变量。以下的代码也可以显示所有的全局变量: repeat with x = 1 to (the globals).count put (the globals).getPropAt(x) & ‘‘= ‘‘& (the globals)[x] end repeat 05. 如何播放mpeg文件? [A] 有一系列的方法,不能说哪一种更好,并且在pc机和mac机上是不一样的,下面是四种常见的方法: 1. 用一个xtra。这种方法用起来简单,且也有好的产品支持,但大多不能跨平台使用。当然,这是需要购买的。 2. 使用ActiveX控件。这只能在pc机上用,相对xtra而言会有更多的限制,但它是免费的,且与标准playback能够很好的集成。

Verilog编码风格

Verilog编码风格 嵌入式开发2010-05-03 15:28:13 阅读14 评论0 字号:大中小订阅 这是以前公司的对fpga代码编写的要求 良好代码编写风格的通则概括如下: (1)对所有的信号名、变量名和端口名都用小写,这样做是为了和业界的习惯保持一致;对常量名和用户定义的类型用大写; (2)使用有意义的信号名、端口名、函数名和参数名; (3)信号名长度不要太长; (4)对于时钟信号使用clk 作为信号名,如果设计中存在多个时钟,使用clk 作为时钟信号的前缀; (5)对来自同一驱动源的信号在不同的子模块中采用相同的名字,这要求在芯片总体设计时就定义好顶层子模块间连线的名字,端口和连接端口的信号尽可能采用相同的名字; (6)对于低电平有效的信号,应该以一个下划线跟一个小写字母b 或n 表示。注意在同一个设计中要使用同一个小写字母表示低电平有效; (7)对于复位信号使用rst 作为信号名,如果复位信号是低电平有效,建议使用rst_n; (8)当描述多比特总线时,使用一致的定义顺序,对于verilog 建议采用bus_signal[x:0]的表示; (9)尽量遵循业界已经习惯的一些约定。如*_r 表示寄存器输出,*_a 表示异步信号,*_pn 表示多周期路径第n 个周期使用的信号,*_nxt 表示锁存前的信号,*_z 表示三态信号等; (10)在源文件、批处理文件的开始应该包含一个文件头、文件头一般包含的内容如下例所示:文件名,作者,模块的实现功能概述和关键特性描述,文件创建和修改的记录,包括修改时间,修改的内容等; (11)使用适当的注释来解释所有的always 进程、函数、端口定义、信号含义、变量含义或信号组、变量组的意义等。注释应该放在它所注释的代码附近,要求简明扼要,只要足够说明设计意图即可,避免过于复杂; (12)每一行语句独立成行。尽管VHDL 和Verilog 都允许一行可以写多个语句,当时每个语句独立成行可以增加可读性和可维护性。同时保持每行小于或等于72 个字符,这样做都是为了提高代码得可读性; (13)建议采用缩进提高续行和嵌套语句得可读性。缩进一般采用两个空格,如西安交通大学SOC 设计中心 2 如果空格太多则在深层嵌套时限制行长。同时缩进避免使用TAB 键,这样可以避免不同机器TAB 键得设置不同限制代码得可移植能力; (14)在RTL 源码的设计中任何元素包括端口、信号、变量、函数、任务、模块等的命名都不能取Verilog 和VHDL 语言的关键字; (15)在进行模块的端口申明时,每行只申明一个端口,并建议采用以下顺序:

Director MX 2004使用问答

Director MX 2004使用问答 Q: 为什么用MX2004打包后会显示标题栏? A:把display template中的titlebat options里的选项都取消就可以了。 Q:如何在DR中打开word文件 A:1,在d内打开须使用activex 2,在d外打开调用word程序打开即可 Q:怎样实现让用户选择不同的背景音乐? A:on mouseUp me,7v@ fileobj=new(xtra "fileio")~M+Hhf fileobj.setFilterMask("all file, *.*,mp3,*.mp3,wave, *.wav")i filename=displayOpen(fileobj)^|kHUb if filename="" or filename=void then exitU9 closefile(fileobj) jhI sound playFile 2, string(filename) end Q:请问怎么给mpg视频加遮照? A:1,利用open widndow 做视频遮照 2,用MPEG advance xtra 插件,在属性窗口中把playback opitions 下的DTS取消了,就可以了,然后就在视频之上的通道里放你遮的图片即可 Q:怎么检测本机是否连接到intel网上? A:WinSocket Xtra Ad可以实现,说明: WinSocket Xtra 是一套Sprite Xtra,一共有三个,分别为 TCPServer.X32,TCPClient.X32和UDPSocket.X32。TCPServer.X32是服务器端xtra,TCPClient.X32是客户端xtra,采用Tcp/ip协议。互相配套用于网络信息传递,可以构建类似聊天室,多人连线游戏。UDPSocket.X32采用UDP 协议。独立用于网络信息传递,也可以构建类似聊天室,多人连线游戏。 Q:flash动画导到dr后声音和动画不同步怎么解决? A:使用线索点,最好调好以后把它锁定。 Q:如何检测用户是否安装quicktime,若无就提示安装? A:on exitframe me if quicktimeversion()<5.0 then open the moviepath@"quicktime\fullinstallercn.exe“ halt() else go "start" end if end Q:为什么发布成exe文件后视频不能正常播放? A:1.打包后Xtras文件夹是否在打包文件夹下,是否包含播放视频所需插件 2.视频是否为mpg,如使用DirectMediaXtras,mpg文件是否与exe在同级目录下 Q:如何实现点击打开本地文件夹? A:gotoNetPage("c:\") 不过路径中不要有中文! Q:如何将dr里的flash导出? A:ExportSWF.x32插件。说明: object = xtra("ExportSWF").new()

Director实例剖析

Director实例剖析:Director的常用Lingo命令和句柄 常用lingo 利用控制director电影的重要方面就是利用控制各个方面的属性,下面列出常用的精灵属性、字段属性、造型成员属性,以及其他的一些常用的命令和句柄。 1.常用精灵属性 blend 语法:the blend of sprite whichsprite 用途:此属性决定了精灵的混合百分比 举例:set the blend of sprite 3 to 40 bottom 语法:the bottom of sprite whichsprite 用途:此属性决定了精灵矩形边框的下部边缘的坐标值,这个属性可以用来测试但是不能直接修改 举例:set lowest =put the botiom ofsprite (i +l) castlibnum 语法:the castlibnum of sprite whichsprite 用途:此属性决定了精灵所使用的造型成员的cast表的编号,可以被测试和修改。如果更改此属性但是不修改castnum属性,director会使用原来的造型成员编号在新的cast表中为精灵寻找造型成员 举例:set the castlibnum of sprite 3 to the number ofcastlib“newcast” constrainh 语法:constrainh(whichsprite,va1ue) 用途:此函数首先计算表达式va1ue的值,然后和精灵的左右矩形边缘坐标进行比较。如果表达式在精灵左右矩形边缘之间,就返回这个表达式;如果这个表达式小于精灵矩形边缘的左边的坐标值,就返回精灵矩形左边边缘的坐标值;如果表达式大于精灵矩形边缘右边的坐标值,就返回精灵矩形右边边缘的坐标值 举例:put constrainh(1,20) --30 put constrainh(1,60) --60 put constrainh(1,100) constrainv 语法:constrainv(whichsprite,va1ue) 用途:和constrainh类似,但是是和精灵矩形边枢的上下边缘进行比较。 举例:set the locv of sprite l to constrainv(3,the mousev) constraint 语法:the constraint of sprite whichsprite

VERILOG语言编写规范

VERILOG语言编写规范 1 目的 本规范的目的是提高书写代码的可读性可修改性可重用性,优化代码综合和仿真结果,指导设计工程师使用VerilogHDL规范代码和优化电路,规范化公司的ASIC设计输入从而做到 1. 逻辑功能正确 2.可快速仿真 3. 综合结果最优如果是hardware model) 4. 可读性较好。 2 范围 本规范涉及Verilog HDL编码风格,编码中应注意的问题, Testbench的编码等。 本规范适用于Verilog model的任何一级( RTL behavioral, gate_level),也适用于出于仿真,综合或二者结合的目的而设计的模块。 3 定义 Verilog HDL : Verilog 硬件描述语言 FSM :有限状态机 伪路径:静态时序分析( STA)认为是时序失败,而设计者认为是正确的路径 4 引用标准和参考资料 下列标准包含的条文通过在本标准中引用而构成本标准的条文在标准出版时所示版本 均为有效所有标准都会被修订使用本标准的各方应探讨使用下列标准最新版本的可能性 Actel HDLCoding Style Guider Sun Microsystems Revision 1.0 VerilogStyle and Coding Guidelines 5 规范内容 5.1 Verilog 编码风格

本章节中提到的Verilog编码规则和建议适应于 Verilog model的任何一级( RTL behavioral,gate_level) 也适用于出于仿真,综合或二者结合的目的而设计的模块。 5.1.1 命名规范 选择有意义的信号和变量名,对设计是十分重要的。命名包含信号或变量诸如出处,有效状态等基本含义下面给出一些命名的规则。 1. 用有意义而有效的名字 有效的命名有时并不是要求将功能描述出来如 For ( I = 0; I < 1024; I = I + 1 ) Mem[I]<= #1 32’b0; For 语句中的循环指针I 就没必要用loop_index作为指针名。 2. 用连贯的缩写 长的名字对书写和记忆会带来不便,甚至带来错误采用缩写时应注意同一信号在模块中的一致性。缩写的例子如下: Addr address Pntr pointer Clk clock Rst reset 3. 用名字前加小写n表示低电平有效高电平有效的信号不得以下划线表示短暂 的引擎信号建议采用高有效 如 nRst, nTrdy, nIrdy nIdsel. 4. 大小写原则 名字一般首字符大写,其余小写(但parameter, integer 定义的数值名可全部用大写),两个词之间要用下划线连接(或第二个单词首字母大写) 如 :Packet_addr, Data_in, Mem_wr , Mem_ce_ Or: PacketAddr, DataIn, MemWr , MemCe 5.全局信号名字中应包含信号来源的一些信息 如: D_addr[7:2] 这里的 D 指明了地址是解码模块(Decoder module)中的地址.

VERYLOG编码规范

Verilog编码规范! 一. 强调Verilog代码编写风格的必要性。 强调Verilog代码编写规范,经常是一个不太受欢迎的话题,但却是非常有必要的。 每个代码编写者都有自己的编写习惯,而且都喜欢按照自己的习惯去编写代码。与自己编写风格相近的代码,阅读起来容易接受和理解。相反和自己编写风格差别较大的代码,阅读和接受起来就困难一些。 曾有编程大师总结说,一个优秀的程序员,能维护的代码长度大约在1万行数量级。代码的整洁程度,很大程度上影响着代码的维护难度。 遵循代码编写规范书写的代码,很容易阅读、理解、维护、修改、跟踪调试、整理文档。相反代码编写风格随意的代码,通常晦涩、凌乱,会给开发者本人的调试、修改工作带来困难,也会给合作者带来很大麻烦。 (实际上英文Coding Style有另一层涵义,更偏重的是,某一个电路,用那一种形式的语言描述,才能将电路描述得更准确,综合以后产生的电路更合理。本文更偏重的是,编写Verilog代码时的书写习惯。) 二. 强调编写规范的宗旨。 缩小篇幅 提高整洁度 便于跟踪、分析、调试 增强可读性,帮助阅读者理解 便于整理文档 便于交流合作 三. 变量及信号命名规范。 1. 系统级信号的命名。 系统级信号指复位信号,置位信号,时钟信号等需要输送到各个模块的全局信号;系统信号以字符串Sys开头。 2. 低电平有效的信号后一律加下划线和字母n。如:SysRst_n;FifoFull_n; 3. 经过锁存器锁存后的信号,后加下划线和字母r,与锁存前的信号区别。如CpuRamRd信号,经锁存后应命名为CpuRamRd_r。 低电平有效的信号经过锁存器锁存后,其命名应在_n后加r。如CpuRamRd_n信号,经锁存后应命名为CpuRamRd_nr 多级锁存的信号,可多加r以标明。如CpuRamRd信号,经两级触发器锁存后,应命名为CpuRamRd_rr。 4. 模块的命名。 在系统设计阶段应该为每个模块进行命名。命名的方法是,将模块英文名称的各个单词首字母组合起来,形成3到5个字符的缩写。若模块的英文名只有一个单词,可取该单词的前3个字母。各模块的命名以3个字母为宜。例如: Arithmatic Logical Unit模块,命名为ALU。 Data Memory Interface模块,命名为DMI。

ChartDirector常见用法(示例代码)

ChartDirector 常见用法(示例代码) 最近在尝试在ChartDirector 里进行坐标的设置,想在这里写写最近最近的学习成果。 下面是我的代码实例,里面就是实现如何在ChartDirector 里进行坐标的设置,代码如下: 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 public void createChart(ChartViewer viewer, int index) { // 这是两组数据,X 和Y 会一一对应生成;多在多纵轴图中使用,横坐标点会自动调整。 double[] dataY0 = { 4.5, 5}; Date[] dataX0 = { new GregorianCalendar(1999, 1, 1).getTime(), new GregorianCalendar(2000, 8, 6).getTime() }; double[] dataY1 = {7, 6.5, 6, 5, 6.5, 7, 6, 5.5, 5,9,8,7,8}; Date[] dataX1 = {new GregorianCalendar(1999, 1, 1).getTime(), new GregorianCalendar(1999, 6, 1).getTime(), new GregorianCalendar(1999, 11, 1).getTime(), new GregorianCalendar(1999, 11, 15).getTime(), new GregorianCalendar(1999, 12, 9).getTime(), new GregorianCalendar(2000, 2, 3).getTime(), new GregorianCalendar(2000, 7, 13).getTime(), new GregorianCalendar(2001, 4, 5).getTime(), new GregorianCalendar(2001, 8, 16).getTime(), new GregorianCalendar(2001, 10, 16).getTime(),new GregorianCalendar(2001, 12, 16).getTime(),new GregorianCalendar(2002, 2, 16).getTime(),new GregorianCalendar(2002, 4, 16).getTime()}; //这是单独的横坐标数据,横坐标会根据数据进行调整,Y 轴会按照顺利一一对应。 Date[] dataX2 = { new GregorianCalendar(1999, 1, 1).getTime(), new

Verilog状态机的写法

Verilog状态机的写法-转 1 引言 Verilog HDL作为当今国际主流的HDL语言,在芯片的前端设计中有着广泛的应用。它的语法丰富,成功地应用于设计的各个阶段:建模、仿真、验证和综合等。可综合是指综合工具能将Verilog HDL代码转换成标准的门级结构网表,因此代码的描述必须符合一定的规则。大部分数字系统都可以分为控制单元和数据单元两个部分,控制单元的主体是一个状态机,它接收外部信号以及数据单元产生的状态信息,产生控制信号,因而状态机性能的好坏对系统性能有很大的影响。 有许多可综合状态机的Verilog代码描述风格,不同代码描述风格经综合后得到电路的物理实现在速度和面积上有很大差别。优秀的代码描述应当易于修改、易于编写和理解,有助于仿真和调试,并能生成高效的综合结果。 2 有限状态机 有限状态机(Finite State Machine,FSM)在数字系统设计中应用十分广泛。根据状态机的输出是否与输入有关,可将状态机分为两大类:摩尔(Moore)型状态机和米莉 (Mealy)型状态机。Moore型状态机的输出仅与现态有关;Mealy型状态机的输出不仅与现态有关,而且和输入也有关。图1是有限状态机的一般结构图,它主要包括三个部分,其中组合逻辑部分包括状态译码器和输出译码器,状态译码器确定状态机的下一个状态,输出译码器确定状态机的输出,状态寄存器属于时序逻辑部分,用来存储状态机的内部状态。 图1 状态机的结构框图 2.1 好的状态机标准 好的状态机的标准很多,最重要的几个方面如下: 第一,状态机要安全,是指FSM不会进入死循环,特别是不会进入非预知的状态,而且由于某些扰动进入非设计状态,也能很快的恢复到正常的状态循环中来。这里面有两层含义。其一要求该FSM的综合实现结果无毛刺等异常扰动,其

Verilog的135个经典设计实例

【例3.1】4位全加器 module adder4(cout,sum,ina,inb,cin); output[3:0] sum; output cout; input[3:0] ina,inb; input cin; assign {cout,sum}=ina+inb+cin; endmodule 【例3.2】4位计数器 module count4(out,reset,clk); output[3:0] out; input reset,clk; reg[3:0] out; always @(posedge clk) begin if (reset) out<=0; //同步复位 else out<=out+1; //计数 end endmodule 【例3.3】4位全加器的仿真程序 `timescale 1ns/1ns `include "adder4.v" module adder_tp; //测试模块的名字 reg[3:0] a,b; //测试输入信号定义为reg型 reg cin; wire[3:0] sum; //测试输出信号定义为wire型 wire cout; integer i,j; adder4 adder(sum,cout,a,b,cin); //调用测试对象 always #5 cin=~cin; //设定cin的取值 initial begin a=0;b=0;cin=0; for(i=1;i<16;i=i+1) #10 a=i; //设定a的取值 end - 1 -

initial begin for(j=1;j<16;j=j+1) #10 b=j; //设定b的取值 end initial//定义结果显示格式 begin $monitor($time,,,"%d + %d + %b={%b,%d}",a,b,cin,cout,sum); #160 $finish; end endmodule 【例3.4】4位计数器的仿真程序 `timescale 1ns/1ns `include "count4.v" module coun4_tp; reg clk,reset; //测试输入信号定义为reg型 wire[3:0] out; //测试输出信号定义为wire型 parameter DELY=100; count4 mycount(out,reset,clk); //调用测试对象 always #(DELY/2) clk = ~clk; //产生时钟波形 initial begin//激励信号定义 clk =0; reset=0; #DELY reset=1; #DELY reset=0; #(DELY*20) $finish; end //定义结果显示格式 initial $monitor($time,,,"clk=%d reset=%d out=%d", clk, reset,out); endmodule 【例3.5】“与-或-非”门电路 module AOI(A,B,C,D,F); //模块名为AOI(端口列表A,B,C,D,F) input A,B,C,D; //模块的输入端口为A,B,C,D output F; //模块的输出端口为F - 2 -

VHDL+Verilog良好的代码编写风格

VHDL+Verilog良好的代码编写风格(二十五条) 田Sir 发表于: 2010-4-28 13:56 来源: 湖北师范学院电工电子实验教学示范中心良好代码编写风格可以满足信、达、雅的要求。在满足功能和性能目标的前提下,增强代码的可读性、可移植性,首要的工作是在项目开发之前为整个设计团队建立一个命名约定和缩略语清单,以文档的形式记录下来,并要求每位设计人员在代码编写过程中都要严格遵守。良好代码编写风格的通则概括如下:(1)对所有的信号名、变量名和端口名都用小写,这样做是为了和业界的习惯保持一致;对常量名和用户定义的类型用大写; (2)使用有意义的信号名、端口名、函数名和参数名; (3)信号名长度不要太长; (4)对于时钟信号使用clk 作为信号名,如果设计中存在多个时钟,使用clk 作为时钟信号的前缀;(5)对来自同一驱动源的信号在不同的子模块中采用相同的名字,这要求在芯片总体设计时就定义好顶层子模块间连线的名字,端口和连接端口的信号尽可能采用相同的名字; (6)对于低电平有效的信号,应该以一个下划线跟一个小写字母b 或n 表示。注意在同一个设计中要使用同一个小写字母表示低电平有效; (7)对于复位信号使用rst 作为信号名,如果复位信号是低电平有效,建议使用rst_n; (8)当描述多比特总线时,使用一致的定义顺序,对于verilog 建议采用bus_signal[x:0]的表示; (9)尽量遵循业界已经习惯的一些约定。如*_r 表示寄存器输出,*_a 表示异步信号,*_pn 表示多周期路径第n 个周期使用的信号,*_nxt 表示锁存前的信号,*_z 表示三态信号等; (10)在源文件、批处理文件的开始应该包含一个文件头、文件头一般包含的内容如下例所示:文件名,作者,模块的实现功能概述和关键特性描述,文件创建和修改的记录,包括修改时间,修改的内容等;(11)使用适当的注释来解释所有的always 进程、函数、端口定义、信号含义、变量含义或信号组、变量组的意义等。注释应该放在它所注释的代码附近,要求简明扼要,只要足够说明设计意图即可,避免过于复杂; (12)每一行语句独立成行。尽管VHDL 和Verilog 都允许一行可以写多个语句,当时每个语句独立成行可以增加可读性和可维护性。同时保持每行小于或等于72 个字符,这样做都是为了提高代码得可读性;(13)建议采用缩进提高续行和嵌套语句得可读性。缩进一般采用两个空格,如西安交通大学SOC 设计中心2 如果空格太多则在深层嵌套时限制行长。同时缩进避免使用TAB 键,这样可以避免不同机器TAB 键得设置不同限制代码得可移植能力; (14)在RTL 源码的设计中任何元素包括端口、信号、变量、函数、任务、模块等的命名都不能取Verilog 和VHDL 语言的关键字; (15)在进行模块的端口申明时,每行只申明一个端口,并建议采用以下顺序:输入信号的clk、rst、enables other control signals、data and address signals。然后再申明输出信号的clk、rst、enalbes other control signals、data signals; (16)在例化模块时,使用名字相关的显式映射而不要采用位置相关的映射,这样可以提高代码的可读性和方便debug 连线错误; (17)如果同一段代码需要重复多次,尽可能使用函数,如果有可能,可以将函数通用化,以使得它可以复用。注意,内部函数的定义一般要添加注释,这样可以提高代码的可读性; (18)尽可能使用循环语句和寄存器组来提高源代码的可读性,这样可以有效地减少代码行数; (19)对一些重要的always 语句块定义一个有意义的标号,这样有助于调试。注意标号名不要与信号名、变量名重复; (20)代码编写时的数据类型只使用IEEE 定义的标准类型,在VHDL 语言中,设计者可以定义新的类型和子类型,但是所有这些都必须基于IEEE 的标准; (21)在设计中不要直接使用数字,作为例外,可以使用0 和1。建议采用参数定义代替直接的数字。同

director 快捷键

1、F i l e菜单快捷键 命令快捷键 New Movie(新影片)Ctrl+N NewCast(新演员表)Ctrl+Alt+N Open(打开)Ctrl+O Close(关闭)Ctrl+F4 Save(保存)Ctrl+S Import(输入)Ctrl+R Export(输出)Ctrl+Shift+R Preview inBrowser(在浏览器中预览)F12 Page Setup(页面设置)Ctrl+Shift+P Print(打印)Ctrl+P General Preferences(基本参数设置)Ctrl+U Exit/Quit(退出)Alt+F4 2、Edit菜单快捷键 命令快捷键 Undo(撤消)Ctrl+Z Repeat(重复)Ctrl+Y Cut(剪切)Ctrl+X 命令快捷键 Copy(拷贝)Ctrl+C Paste(粘贴)Ctrl+V Clear(清除)Backspace Duplicate(复制)Ctrl+D Select All(全选)Ctrl+A Find Text(查找文本)Ctrl+F Find Handler(查找处理程序)Ctrl+Shift+; Find Cast Member(查找演员)Ctrl+; Find Selection(查找选区)Ctrl+H Find Again(再查找)Ctrl+Alt+F Replace Again(再替换)Ctrl+Alt+E Edit Sprite Frames(编辑角色的帧)Ctrl+Alt+] Edit Entire Sprite(编辑整个角色)Ctrl+Alt+[ Exchange Cast Members(交换演员)Ctrl+E Launch External Editor(运行外部编辑器)Ctrl+,(逗号) 3、View菜单快捷键 命令快捷键 Next Marker(下一个标志)Ctrl+右箭头键 Previous Marker(前一个标志)Ctrl+左箭头键 Zoom In(变焦放大)Ctrl++ Zoom Out(变焦缩小)Ctrl+-(连字符) Show Grid(显示网格)Ctrl+Shift+Alt+G Snap to Grid(吸附于网格)Ctrl+Alt+G Show Rulers(显示标尺)Ctrl+Shift+Alt+R

用verilog语言编写交通灯程序

交通灯 一、实验目的 写一个交通灯,要求: ①有东西南北四个方向,两组交通灯轮流交替变换,其中,红灯时间为30 个时间单位,绿灯时间为25个时间单位,黄灯时间为5个时间单位。最后用modelsim软件进行仿真。 ②要求设计是一个可综合设计。 二、实验原理 根据实验要求的逻辑功能描述,可以分析得出原理图如下: 根据实验要求画出控制器的状态转移图如下:

三、代码 1、源代码 (1)控制器模块 module traffic_lights(clk,rst,count,ew,sn); input clk,rst; input[5:0] count; output[2:0] ew,sn; reg[2:0] ew,sn; reg[3:0] state; parameter Idle=3'b000,s1=3'b001,s2=3'b010,s3=3'b011,s4=3'b100; always @(posedge clk) if(!rst) begin state<=Idle; end else casex(state) Idle: if(rst) begin state<=s1; end s1: if(count=='d25) begin state<=s2; end s2: if(count=='d30) begin state<=s3;

end s3: if(count=='d55) begin state<=s4; end s4: if(count=='d60) begin state<=s1; end endcase always @(posedge clk) begin if(!rst) begin ew<=3'b100; sn<=3'b100; end else casex(state) Idle: if(rst) begin ew<=3'b100; sn<=3'b001; end s1: if(count=='d25) begin ew<=3'b100; sn<=3'b010; end

个人总结Verilog代码编写的25条经验

个人总结Verilog代码编写的25条经验 1、对所有的信号名、变量名和端口名都用小写,这样做是为了和业界的习惯保持一致;对常量名和用户定义的类型用大写; 2、使用有意义的信号名、端口名、函数名和参数名; 3、信号名长度不要太长; 4、对于时钟信号使用clk 作为信号名,如果设计中存在多个时钟,使用clk 作为时钟信号的前缀; 5、对来自同一驱动源的信号在不同的子模块中采用相同的名字,这要求在芯片总体设计时就定义好顶层子模块间连线的名字,端口和连接端口的信号尽可能采用相同的名字; 6、对于低电平有效的信号,应该以一个下划线跟一个小写字母b 或n 表示。注意在同一个设计中要使用同一个小写字母表示低电平有效; 7、对于复位信号使用rst 作为信号名,如果复位信号是低电平有效,建议使用rst_n; 8、当描述多比特总线时,使用一致的定义顺序,对于verilog 建议采用bus_signal[x:0]的表示; 9、尽量遵循业界已经习惯的一些约定。如*_r 表示寄存器输出,*_a 表示异步信号,*_pn 表示多周期路径第n 个周期使用的信号,*_nxt 表示锁存前的信号,*_z 表示三态信号等; 10、在源文件、批处理文件的开始应该包含一个文件头、文件头一般包含的内容如下例所示:文件名,作者,模块的实现功能概述和关键特性描述,文件创建和修改的记录,包括修改时间,修改的内容等; 11、使用适当的注释来解释所有的always 进程、函数、端口定义、信号含义、变量含义或信号组、变量组的意义等。注释应该放在它所注释的代码附近,要求简明扼要,只要足够说明设计意图即可,避免过于复杂; 12、每一行语句独立成行。尽管VHDL 和Verilog 都允许一行可以写多个语句,当时每个语句独立成行可以增加可读性和可维护性。同时保持每行小于或等于72 个字符,这样做都是为了提高代码得可读性; 13、建议采用缩进提高续行和嵌套语句得可读性。缩进一般采用两个空格,如西安交通大学SOC 设计中心2 如果空格太多则在深层嵌套时限制行长。同时缩进避免使用TAB 键,这样可以避免不同机器TAB 键得设置不同限制代码得可移植能力; 14、在RTL 源码的设计中任何元素包括端口、信号、变量、函数、任务、模块等的命名都不能取Verilog 和VHDL 语言的关键字; 15、在进行模块的端口申明时,每行只申明一个端口,并建议采用以下顺序: 输入信号的clk、rst、enables other control signals、data and address signals。然后再申明输出信号的clk、rst、enalbes other control signals、data signals; 16、在例化模块时,使用名字相关的显式映射而不要采用位置相关的映射,这样可以提高代码的可读性和方便debug 连线错误; 17、如果同一段代码需要重复多次,尽可能使用函数,如果有可能,可以将函数通用化,以使得它可以复用。注意,内部函数的定义一般要添加注释,这样可以提高代码的可读性;

verilog语言代码设计规范

verilog语言代码设计规范2011年12月

目录 一、规范适用范围 ------------------------------------------------------------------------ 4 1.1项目适用范围------------------------------------------------------------------------------------- 4 1.2人员适用范围------------------------------------------------------------------------------------- 4 1.3编码设计的成果形式 --------------------------------------------------------------------------- 4 二、代码书写规范 ------------------------------------------------------------------------ 5 2.1模块说明书写规范------------------------------------------------------------------------------- 5 2.1模块注释书写规范------------------------------------------------------------------------------- 5 2.3变量名称书写规范------------------------------------------------------------------------------- 6 2.4代码结构书写规范------------------------------------------------------------------------------- 7 三、使用verilog语言的语法范围----------------------------------------------------- 8 3.1设计RTL代码的语法范围 -------------------------------------------------------------------- 8 3.2设计仿真代码的语法范围 -------------------------------------------------------------------- 10 四、使用verilog语言的结构范围---------------------------------------------------- 11 4.1系统设计文件的形式与使用方法----------------------------------------------------------- 11 4.2模块结构划分的标准 -------------------------------------------------------------------------- 12 4.3组合逻辑的代码风格 ------------------------------------------------------------------------ 13 4.4时序逻辑的代码风格 -------------------------------------------------------------------------- 21 4.5仿真代码的代码风格 -------------------------------------------------------------------------- 27 五、使用受限范围内的语法或结构要进行的申请过程-------------------------- 32 5.1受限的语法与结构------------------------------------------------------------------------------ 32 5.2批准使用的程序--------------------------------------------------------------------------------- 32

verilog数字钟代码全新

module digclk(clk,en,rst,dula,wela,s1,s2,s3,led,flag1,start1,flag2,start2,aled,s6,s4,s5); //s1调时s2调分s3调秒wela位码dula段码en使能clk时钟,flag1是跑表标志(拨上去就是显示跑表),置一为跑表功能,start1为跑表开始停止 //flag2为闹钟标志(拨上去就是设置闹钟时间)start2为闹钟开关aled闹钟提示灯input clk,rst,en,s1,s2,s3,flag1,start1,flag2,start2,s6,s4,s5; output [2:0] wela; output [7:0] dula; output led; output aled; reg led; reg aled; reg [7:0] cnt,dula; reg [2:0] wela; reg[7:0] hourh,hourl,minh,minl,sech,secl; reg[7:0] phourh,phourl,pminh,pminl,psech,psecl; reg[7:0] ahourh,ahourl,aminh,aminl,asech,asecl; reg[3:0] a; //a用于数码管显示的临时变量 (* synthesis, keep *) reg clk1; always @(posedge clk1) begin if(start2) begin if(hourh==ahourh&&hourl==ahourl&&minh==aminh&&minl==aminl&&sech==asech&&secl ==asecl) aled=1'b1; else aled=1'b0; end end always @(posedge clk1) //闹钟功能 begin if(flag2) begin if(!s4) //调节小时 begin /*if(ahourl==9)begin ahourl<=0;ahourh<=ahourh+1;end if(ahourh==2&&ahourl==3)begin ahourh<=0;ahourl<=0; end else ahourl<=ahourl+1;*/ ahourl<=ahourl+1; if(ahourl==3&&ahourh==2)begin ahourl<=0;ahourh<=0;end if(ahourl==9) begin ahourl<=0;ahourh<=ahourh+1;end;

外企常用英文简写

外企日常工作中常用的英语术语和缩写语 办公室职员(Office Clerk)加入公司的整个过程为例,引出在跨国公司(MNC-Multi-National Company) 工作中,日常人们喜欢经常使用的术语(Terminology)和缩写语(Abbreviation)。 [找工作Job Searching]我立志大学毕业后加入一家跨国公司。我制作了精美的个人简历(Resume, cv)。我参加了校园招聘(Campus Recruitment)。我关注报纸招聘广告(Recruiting Ads)。我也经常浏览招聘网站(Recruiting Website)。我还参加人才招聘会(Job Fair)。 [参加面试Be invited for Interview] 我选择了几家中意的公司,投出了简历。终于接到了人力资源部(Human Resources Department)邀请面试的通知。经过几轮面试(Interview)和笔试(Written Test)我终于接到了XXXX公司的聘用书(Offer Letter)。这是一家独资/合资企业(Wholly Foreign-Owned Company/Joint-Venture)。 [录用条件Employment Terms] 我隶属XX部门(Department)。我的职位(Position)是XXXX。我的工作职责(Job Responsibilities)是XXXX。我的直接上司(Direct Supervisor)是XXX。我的起点工资(Starting Salary)是XXXX。我的入职日期(Join-Date)是XXXX。我的试用期(Probation)是3个月。首期劳动合同(Labor Contract/Employment Contract)的期限(Term)是3年。 [第一天上班First day of join] 我乘坐公司班车(Shuttle Bus/Commuting Bus)来到公司。先来到人力资源部报到(Register)。我填了一系列的表格(Forms)。我领到了工卡(Badge Card)、餐卡(Meal Card)、员工手册(Employee Manual)、培训手册(Training Handbook)、保险手册(Insurance Handbook)、安全环境健康(EHS-Environment, Health and Safety)手册。公司培训主管(Training Supervisor)为我做了入职培训(Orientation)。我了解了公司的安全须知(Safety Precautions)和紧急疏散通道(Emergency Evacuation Route)。 [部门Department] 我随后来到我的部门,见到了我的部门经理(Department Manager)和同事(Colleagues)。我来到我的办公桌(Desk)前,看到办公用品(Stationery)和台式计算机(DeskTop)已经摆在桌上。经理说以后还会配备笔记本电脑(Notebook/LapTop)。 [午餐Lunch] 中午在公司餐厅(Cafeteria)吃饭,是免费的午餐(Free Lunch)。饭后跟大家一起外出散步。 [第一次会议First meeting] 下午部门开会(Have a Meeting),讨论目前面临的困难和问题(Difficulty & Issues),经理要求大家通过脑力激荡(Brain-Storming),找出问题的根源(Root Cause),并提出解决方案(Solutions)。 [各种类型会议Various meetings] 公司有多种会议。部门经理的管理层会议(Staff Meeting)。讨论项目进展的项目会议(Project Meeting)。讨论预算的预算会议(Budgeting Meeting)。与美国总部的电话会议(Teleconference Call)。还可以利用视频会议系统(Video Conference)或网络会议(Net-Meeting)系统开会。有各种周会(Weekly Meeting)、月例会(Monthly Meeting)、季度会议(Quarterly Meeting)和年度会议(Annual Meeting)。 [各种计划Various plans] 要制定各种计划(Plans)。有长期计划(Long-term Plan)、中期计