两级开环比较器的设计.doc

初级比较器设计

一.前言

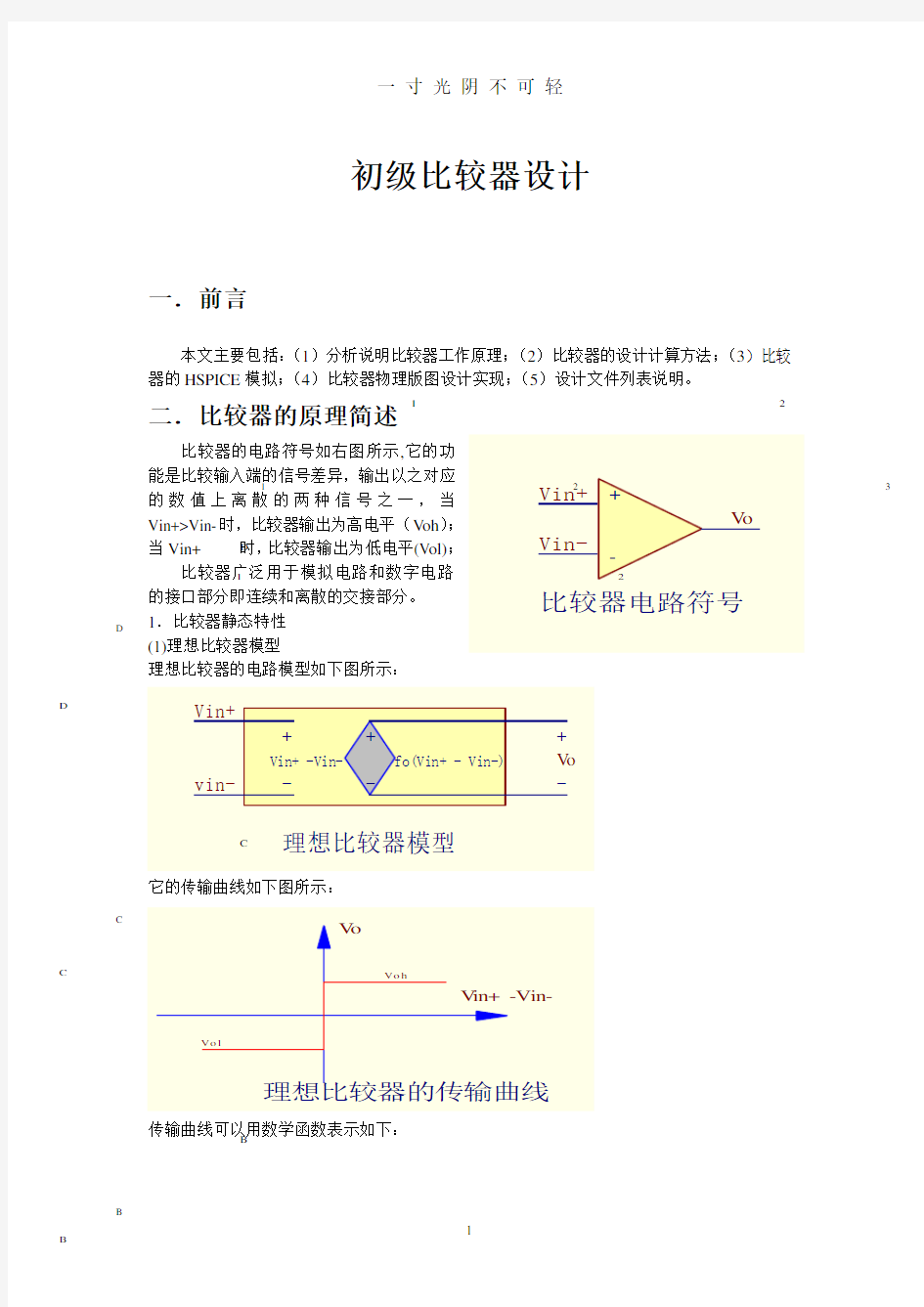

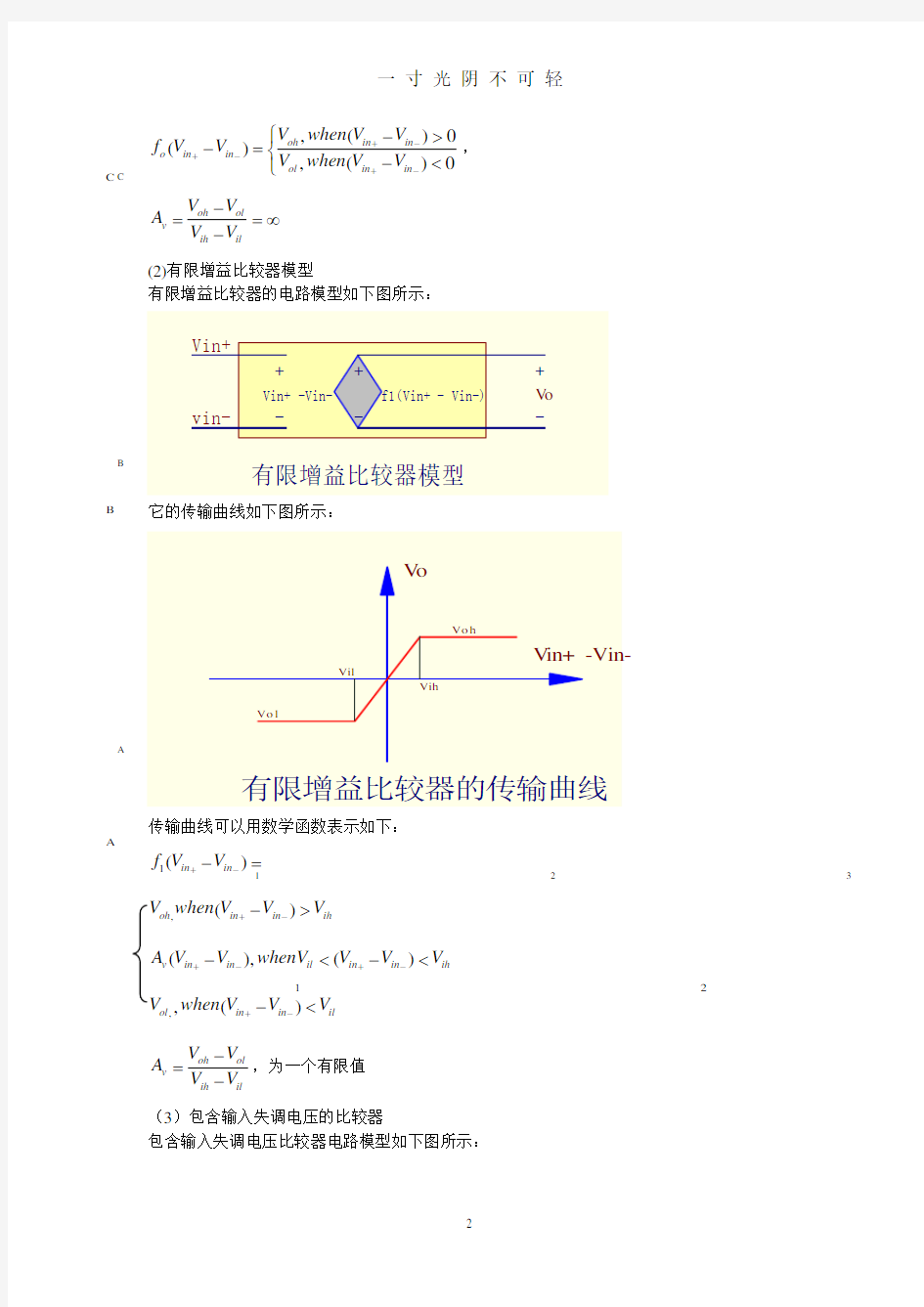

本文主要包括:(1)分析说明比较器工作原理;(2)比较器的设计计算方法;(3)比较

,ol in in il +-oh ol

v ih il

V V A V V -=

-,为一个有限值

(3)包含输入失调电压的比较器

包含输入失调电压比较器电路模型如下图所示:

Vin+

vin-

fo(Vin+' - Vin-')

+

-

Vin+'-Vin-'

+

-

+

-

V o 包含输入失调电压比较器模型

+-Vin+'

vin-'

因此,在摆率响应的情况下,增大对电容的充/放电电流可以减小比较器的时延。

66()[1oh DD DS DD DD G MIN TP V V V V V V V ?=-=--- 显然,

114114511445()(1)out m gs m m gs n n m gs m n n V g V g g V r r g V g r r ?=+=+

12

in

gs V V =

----------------------------------------------------------------

6节点对地电阻676//7ds r rds rds =

6节点对地电容Cn6,

6节点和5节点间的电容Cc(针对比较器电路,采用开环模式,通常使Cc 最小化,以得到

最大的带宽和较快的响应)。

根据基尔霍夫电压环路(KVL )和电流节点(KCL )定理,可以得到该小信号等效电路的方程组并解得:

1624676224567624675656()(1/)

()()1[(')][()]

out m m ds ds c m v in ds n c ds n ds ds n n c n n V s g g r r sC g A s V s s r C M C r C s r r C C C C C -=

=++++++

M ’为密勒因子, (3)估算时延

为了计算的方便,()v A s 可以采用节点时间常数近似方法估算,它的另一种表示方式如下:

12

(0)

()(1)(1)v v A A s s s p p =

++

其中:低频增益16

1246672467(0)(//)(//)()()

m m v m ds ds m ds ds ds ds ds ds g g A g r r g r r g g g g ==

++,

2411ds ds g g p C +=-

,67

22

ds ds g g p C +=-,1C 为第一级输出极点5的电容,2C 为为第二级输

出节点6的电容。

假设输入激励信号为Vin,那么在S 域的电路响应为:

V o(s)= ()v A s Vin(s),对它进行拉普拉斯逆变换可以得到时域的响应为:

/1/2

211212

()(0)[1]()t t o v in p e p e V t A V t p p p p ττ--=+---,其中2416721(//),2(//)ds ds ds ds r r C r r C ττ==,

根据这个时域响应可以估算比较器的线性响应传输时延,为了计算方便,对该式进行级数展开得 :

2221

()(0)[1(1...)(1...)]1212n n o n v in n n t m t m V t A V t mt m m ≈--+++-++--,其中,

211,1

n p p t

m t t p τ=

== 再进一步简化得:

2(0)()2

n v in

o n mt A V V t ≈

令()()/2o n oh ol V t V V =+,解得:

pn t =

==

1pn tp t τ?==

,(21min

,in p Vin

m k p V =

=),这就是估算线性线性响应传输时延的关系式。 附带说明一下如何选择摆率受限或线性响应受限来估算比较器的传输时延:

为了比较线性响应受限和摆率受限,我们对/1/2

211212

()(0)[1]()

t t o v in p e p e V t A V t p p p p ττ--=+---进行归1化处理得:

()'21(0)11()1,1,111

o n n n v in

V t t mt o n n A V p m t

V t e e m t tp m m p τ--=

=-

+=≠==--其中:, 对上式进行两次求导并令其等于0可以得到归一化响应的最大斜率为:

ln ln '

11

max

()[]1

m m

m o n m m n

dV t m e e dt m ----=--------------(3.1-1) 而两级开环比较器的输出摆率为:

7

2

I SR C -=

-------------(3.1-2) 2

66767

2

2

()

DD G MIN TP V V V I I I SR C C β+----=

=------------(3.1-3)

比较(3.1-1)、(3.1-2)和(3.1-3),当min in in V V >且摆率比(3.1-1)小时,则应采用摆率来估算比较器电路的时延。需要特别强调的是:如果是线性响应受限则极点的位置十分重要,如果是摆率受限则对电容的充放电的能力变得更为重要。 (4)设计常用公式: 为设计方便,现将常用的设计公式及步骤总结如下:

①276212N P p C p p I I λλ==

==

+ ②

6677

22

667722,'()'()P SD SAT N DS SAT W I W I L K V L K V ==,67,SD SAT dd oh DS SAT ol ss V V V V V V =-=- ③1

157

2

2C C I I C =假设一个的值,计算 ④

3542'()

W I W L L K V V ==-,3SG dd icm TN V V V V +

=-+

⑤2467166,v ds ds ds ds m m m g g g =

=

2

112125min

,(0)m oh ol v N in g V V W W A L L K I V -=== ⑥124624gd gd gs bd bd C C C C C C =++++

22123221234412344123()2()()2()

AD W L L L PD W L L L AD W L L L PD W L L L =++=+++=++=+++

计算出C1,如果计算出的C1大于在第三步中假设的C1,则必须加大C1且重复3~6的步骤,直道计算出来的C1小于假设的C1为止。 ⑦55512552,

'()DS SAT icm GS ss N DS SAT W I V V V V L K V -

=--=,如果5DS SAT

V 小于100mV 则增大1

1

W L 2.两级开环比较器的摆率响应设计

(1)设计中用到的分析方法 设计中的分析法方法法和“1”部分讲解的类同,重点要理解电路的小信号等效电路,并利用根据基尔霍夫电压环路(KVL )和电流节点(KCL )定理来求解,并进行设计计算。 (2)时延的估算

在大多数的情况下,两级开环比较器会被驱动到摆率受限,此时,传输时延由下式计算:

i i i i

i i

dv v

i C C dt t ?==?,其中:Ci 为第i 级的对地电容,由该式可以得到第i 级的传输时延为:i i i i

i V t t C I ?=?=,总的传输时延为i

i i i

V tp C I ?=∑。 (2)设计常用公式

为设计方便,现将常用的设计公式及步骤总结如下: ①2762

()

out oh ol dv C V V I I C dt tp

-=== ②

6677

22

667722,'()'()P SD SAT N DS SAT W I W I L K V L K V ==,67,SD SAT dd oh DS SAT ol ss V V V V V V =-=- ③假设一个C1值并在以后检查 ④1151

()

o oh ol dv C V V I C dt tp

-=≈ ⑤

3542'()

W I W L L K V V ==-,3SG dd icm TN V V V V +

=-+

⑥2467166,v ds ds ds ds m m m g g g =

=

2

112125min

,(0)m oh ol v N in g V V W W A L L K I V -=== ⑦124624gd gd gs bd bd C C C C C C =++++

22123221234412344123()2()()2()

AD W L L L PD W L L L AD W L L L PD W L L L =++=+++=++=+++

计算出C1,如果计算出的C1大于在第三步中假设的C1,则必须加大C1且重复3~6的步骤,直道计算出来的C1小于假设的C1为止。 ⑧55512552,

'()DS SAT icm GS ss N DS SAT W I V V V V L K V -

=--=,如果5DS SAT

V 小于100mV 则增大1

1

W L

79179111112121111()()1''111111m m m m o o o o o g g R g g R R C V V V V V sR C sR C s s τττ++=

-=-++++

8102810222221212222()()2

''112121

m m m m o o o o o g g R g g R R C V V V V V sR C sR C s s τττ++=

-=-++++

其中:11221,2R C R C ττ==

假设MOS 管采用对称设计使他们的跨导相等,令:79810m m m m m g g g g g ====,

12,R R R ==12,12C C C τττ====,2121,''o o o i o o V V V V V V ?=-?=-,则可以解得:

12'(12)

'1112i

i

m o m m V V g R V V s s g R s g R

ττττττ??-??=

=

=+-++-,其中:'12m g R τ

τ=-

求上式的拉普拉斯逆变换的时域响应为:

(12)/2///'()'m m L t g R g Rt t t o i i i i v t V e V e e V e V ττττ---?=?=?≈?=?,即:

/()L t o i v t e V τ?=?

其中:0.342L m C g R

τ

τ=

=

= 要求锁存器级的传输时延,可以令:/()()/2L

t o i oh ol v t e V V V τ?=?=-,解得传输时延为:

ln(

)2oh ol

L i

V V tp V τ-=?,显然要改善传输时延应该从L τ和i V ?两方面着手解决。特别是选择

以上设计计算的电路参数,只是个估算值,一般都要调整,这时我们可以利用HSPICE

来模拟,一方面,可以检验电路的功能是否正确,另一方面,由模拟的结果反过来调整电路的参数。直到得到满意的性能指标为止。

1.实际采用的两级开环比较器的电路原理图及相关说明(附带文件:)

vin1 in1 gnd pulse(2.4v 2.6v 0n 0n 0n 100n 200n ) vin2 in2 gnd dc 2.5

.tran 1n 400n

.probe

.end

3.HSPICE 的模拟结果(附带文件:com_hspice_wave.bmp )

红色曲线:in2端输入信号 黄色曲线:in1端输入信号 橙色曲线:out2端输出信号

由此波形图可以看出:上升时延大约为:60ns,下降时延大约为40ns,总的时延平均为50ns. 虽然,性能不是很理想,但功能是基本实现了;可以进一步优化。 4.参数确定

最终确定的参数为: PMOS :

1234525252512.512.5(

),(),(),(),()2.5 2.5 2.5 2.5 2.5W uM W uM W uM W uM W uM

L uM L uM L uM L uM L uM =====

NMOS :

123404080(

),(),()2.5 2.5 2.5W uM W uM W uM

L uM L uM L uM

===

Ibias=30uA

五.比较器的物理版图设计

1.编辑比较器的原理图(附带文件为com_sch.png ) 利用IC 工具软件可以编辑比较器的原理图如下:

tpr tpf

2.据编辑比较器的版图(附带文件:com_layout.png和com.gds)

(1)总的比较器版图几何结构如下图所示

左上:MP4和MP5

右上:MP1、MP2 和MP3

左下:MN1和MN2

右下:MN3

(2)总体布局规划

一方面,从电路的电气可靠性考虑,把输入差分放大管MP4和MP5和输出的MN3布局成对角线方位,可以减少输出对输入的干扰;另一方面,从电路的几何面积考虑,把MP1、

MP2 和MP3分别拆成两条长为12.5um的栅,把MN1和MN2分别拆成两条长为20um的栅,把MN3拆成4条长为20um的栅,并按上图布局可以使整个版图紧凑面积最小。(3)MOS晶体管的匹配

由于MP4和MP5的宽长比不是很大,没有拆分,所以把他们平行并排对称布图匹配;MP1、MP2 和MP3分别拆成两条长为12.5um的栅,并把MP1排在中间,MP2 和MP3分别排在它的两侧;MN1和MN2分别拆成两条长为20um的栅,并按共质心方式布图匹配。

(4)大尺寸MOS晶体管的处理

MN3的宽长比高达80/2.5,把它拆分成4条长为20um的栅,单管版图几乎正方形。

(5)在DRC检查

由于事先较为详细的理解了中微晶圆电子有限公司”的《0.5uM SPTM COMS PROCESS DESIGN RULES》内容,布图过程程中,尽可能根据它来取相应部分的尺寸,因此布图过程中没有太多的DRC错误。但是这里必须提到一个失误,由于疏忽,误以为contact到poly 栅的间距大于0.7,并且以此为准先画源和漏区金属时都没有打contact,等到最后打contact 并做DRC检查时,此问题暴露了,最后由于时间太紧,只好修改的divaDRC.rule文件,强行把这约束改为0.7,结果DRC检查没有错误。可是,如果流片这是万万不可的,因为工艺决定了DRC的约束,这里讲述的这种做法也是不允许的,只是时间太紧了(版图我画到凌晨4:38)才如此操作,不过正确的方法因该是:把contact到poly栅的间距调大到0.8。通过这问题,我也吸取教训:不可以最后打contact否则易出错;还是得认真。

3.整体DRC检查及其结果(附带文件:drcout.sum)

DRC最后检查结果如drcout.sum文件所述如下图所示:

DRC错误列表空,可见没有DRC错误。

4.LVS检查及其结果(附带文件:lvsout.lvs)

LVS检查结果如lvsout.lvs文件所述,如下图所示:

由此可见LVS检查通过。

5.该版图设计的不足:

(1)MN2管的两个栅之间打了一个contact,不利于和MN1管匹配。如下图所示:

Contact

(2)用poly来连接多晶硅栅如下图所示,最好用金属以减小寄生电阻。

poly

(3)三个偏置管由于栅条有限难以匹配

6.最后输出版图文件(附带文件:com.gds)六.文件列表说明

所有的文件在report+gds文件夹中

(1)HSPICE网表文件:com_hspice_netlist.sp

(2)HSPICE输出波形图:com_hspice_wave.bmp

(3)IC51编辑的原理图(屏幕硬拷贝):com_sch.png

(4)IC51编辑的版图(屏幕硬拷贝):com_layout.png

(5)DRC检查结果文件:drcout.sum

(6) LVS检查结果文件:lvsout.lvs

(7)GDSII版图文件:com.gds