RF 设计与应用----射频集成电路封装

RF设计与应用----射频集成电路封装

关键词:射频,多层电路板,电路封装

摘要:针对无线通信产品业者所面临的课题,本文试着从封装技术在射频集成电路上应用的角度,来介绍射频集成电路封装技术的现况、现今封装技术对射频集成电路效能的影响,以及射频集成电路封装的未来发展和面临的挑战。

在行动通讯质量要求的提高,通讯带宽的需求量大增,因应而生的各项新的通讯规范如GPRS、W-CDMA、CDMA-2000、Bluetooth、 802.11b纷纷出笼,其规格不外乎:更高的数据传输速率、更有效的调变方式、更严谨的噪声规格限定、通讯功能的增强及扩充,另外再加上消费者对终端产品“轻、薄、短、小、久(包括产品的使用寿命、维护保固,甚至是手机的待机时间)”的诉求成了必要条件;于是乎,为了达成这些目的,各家厂商无不使出混身解数,在产品射频(Radio Frequency)、中频(Intermediate Frequency)与基频(Base Band)电路的整合设计、主动组件的选择应用、被动组件数目的减少、多层电路板内线路善加运用等,投注相当的心血及努力,以求获得产品的小型化与轻量化。

针对这些无线通信产品业者所面临的课题,我们试着从封装技术在射频集成电路上应用的角度,来介绍射频集成电路封装技术的现况、现今封装技术对射频集成电路效能的影响,以及射频集成电路封装的未来发展和面临的挑战。

射频集成电路封装技术的现况

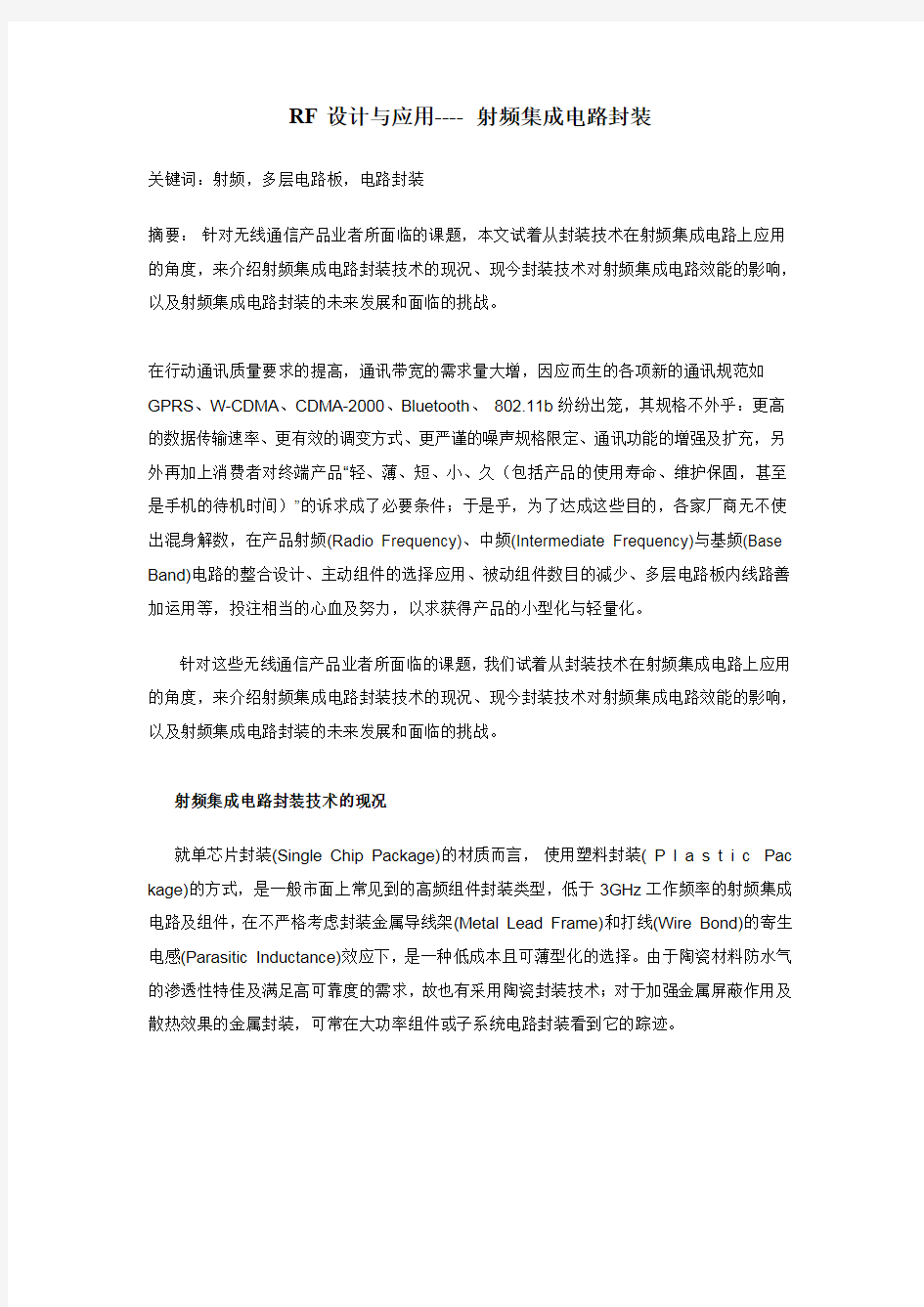

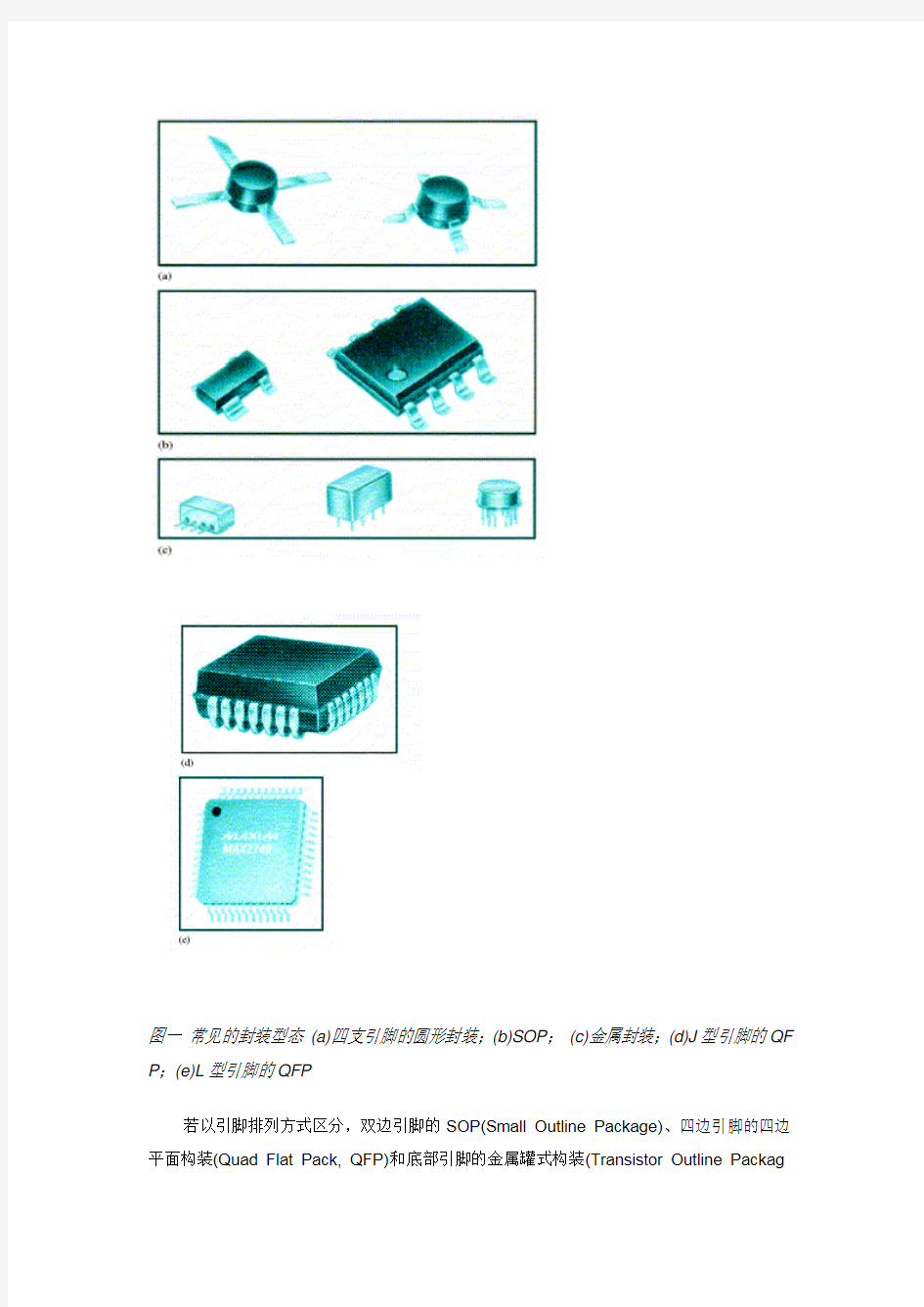

就单芯片封装(Single Chip Package)的材质而言,使用塑料封装( P l a s t i c Pac kage)的方式,是一般市面上常见到的高频组件封装类型,低于3GHz工作频率的射频集成电路及组件,在不严格考虑封装金属导线架(Metal Lead Frame)和打线(Wire Bond)的寄生电感(Parasitic Inductance)效应下,是一种低成本且可薄型化的选择。由于陶瓷材料防水气的渗透性特佳及满足高可靠度的需求,故也有采用陶瓷封装技术;对于加强金属屏蔽作用及散热效果的金属封装,可常在大功率组件或子系统电路封装看到它的踪迹。

图一常见的封装型态 (a)四支引脚的圆形封装;(b)SOP; (c)金属封装;(d)J型引脚的QF P;(e)L型引脚的QFP

若以引脚排列方式区分,双边引脚的SOP(Small Outline Package)、四边引脚的四边平面构装(Quad Flat Pack, QFP)和底部引脚的金属罐式构装(Transistor Outline Packag

e, TO)最为常见(图一),其引脚与构装基板的黏着设计,为能有高密度薄型化的最佳表现,又以表面黏着技术(Surface Mount Technology)为最大宗,而各家组件厂商会因应不同的组件如放大器( A m p l i f i e r ) 、振荡器(Oscillator)、混频器(Mixer).等,选取优化的封装方式以符合客户的需求而多芯片封装(Multi-chip Package)技术,同时也包括了多芯片模块封装(Multi-chip Module),为一种缩小电路体积、减短各集成电路互连( I n t e r -connection)线路距离、降低噪声干扰的封装技术。由于此封装方式将至少两片以上的芯片整合起来,并依承载基板材质的不同,而有MCM-C(Ceramic)、MCMD(Deposited Thin F ilm)、MCM-S(Silicon)、MCM-L (Laminate)之分(其中MCM-L主要以PC板做构装底材,成本最低),且配合减少打线影响的覆晶接合技术(Flip-chip Bonding,图二)和缩小封装面积的芯片尺寸封装( Chip Scale Package,图三),甚而利用LTCC(Low Temperat ure Co-fired Ceramic)制程技术结合内藏式被动组件的设计(图四),所制成的前端(Front End)区块电路模块,更为广泛地应用在无线通信电路中,以减少独立式被动组件的使用数目,进而满足小型化、轻量化的要求。

图二覆晶接合间图

图三 CSP类别示意图

图四多层陶瓷模块剖面示意图

封装技术对射频集成电路效能的影响

封装对组件的功能主要在于传递电源能量及电路讯号、保护组件结构、提供散热管道,其中又以电能、电讯的传输为射频集成电路相当重要的考虑。由于射频电路工作频率常在3 00MHz以上,其原有的低频电路特性则因频率的增加而有所改变,以简单的单一导线为例,原为传输讯号导通与不导通的判定,随着工作频率的提升其寄生电感、肌肤效应(Skin Effe ct)及寄生电阻(Parasitic Resistance)的现象便一一浮现,导致我们对射频集成电路在封装中的电性要求较为复杂。在参考数据1中所叙述,就一砷化镓(GaAs)单晶微波集成电路(Mo nolithic Microwave Integrated Circuit; MMIC)的LNA(Low Noise Amplifier)电路,利用覆晶凸块接合至氧化铝基板制作成覆晶测试电路,并和其裸晶的电路特性做比较(见图五)。

图五覆晶与裸晶S参数比较图

图六未填胶覆晶与填胶覆晶参数比较图

两者在工作频段S参数的变化相当一致,也就是说受覆晶接合封装的单晶微波集成电路和裸晶的电性表现近乎相同,且受覆晶凸块的寄生电感效应的影响不大;不过,其中要注意的是覆晶和基板的间距至少要大于20ìm以上,以确保集成电路之原有电性。另外,为延长覆晶接合焊锡凸块寿命,在覆晶与基板之间灌入填胶材质,在量测比较后发现,S参数的增益曲线将随工作频率的升高,往低频平移约3GHz(见图六),而曲线的趋势仍保持近似,如此电性变化表现和填胶材质的介电常数有很大关系,所以高频集成电路的覆晶填胶材质应以介电常数越低者为最佳选择。

而在参考数据2中,是用一组VCO电路在一般的薄型四边平面封装(Thin Quad Flat Pack; TQFP)和覆晶模块锡球数组式封装( F l i p -Module BGA Package)中,以打线连接导线架和覆晶凸块联机连接锡球的电性来做比较分析,其彼此联机(从打线到导线架,或从凸块到锡球)的自感值在两种不同的封装结构中可得到相当近似的数值(皆近似于5nH 左右),其中寄生电容低于0.2pF,故忽略不予考虑;且在Flip-Module BGA封装的结构内,有加入R、L、C等被动组件的设计,以极短的联机互连(仅增加0.5nH),可减少在TQFP中因打线及导线架所寄生的电感效应而造成电路特性改变。我们可以得知,将被动组件整合进模块封装中和单一封装组件结合独立式被动组件对照下,可提升电路的效能特性;但必需注意的是,其被动组件内藏于模块电路后,就不容易因效能的差异做适度的调整及更换,且制作被动电路的设计尺寸也需有公差的考虑,所以对电路设计者及制造电路板厂而言,尚需一段互相配合的努力。

在射频集成电路或模块的金属封装,常隐含一个问题,就是从电路中的不连续处所散射出来的杂散模(Spurious Modes),甚而在封装中造成寄生共振(Parasitic Resonance)的现象,干扰其主模(Dominant Mode)讯号的传递,影响其余电路的正常运作(图七)。就参考数据3所提及,在共平面波导线的MMIC封装,会因背金属共平面波导线(Conductor-Ba cked Coplanar Waveguide; CBCPW)及两侧封装金属墙的结构,而在封装中产生噪声的共振现象,为了减少寄生共振对射频电路效能的影响,在原基板下多加一层硅基板(500ìm, 1 5..cm),利用硅基板本身材质的损耗特性来衰减噪声的传递,而原始的电传输特性以及抑制效能可从图八中得知。另外,也有使用不同的封装材料或改变封装结构.等,以升高杂散模的截止频率而抑制噪声的传播。

图七杂散模共振干扰图

图八 (a)原始CBCPW传输特性量测与模拟对照;(b)加了硅基板的CBCPW传输特性量测结果

射频集成电路封装技术未来发展及面临的挑战

以射频集成电路封装技术而言,除了体积浓缩的考虑外,维持其电路设计之电性规格,甚至是希望能更进一步做到改善的效果,相信不只是专精于射频电路设计者和组件制造商的责任,并且和封装产业的技术提升都有相当重要的关联性,包括

1. 制程整合──除了功率放大器电路中的晶体管,仍暂时需以GaAs制程技术才能做到符合电性规格外,其余主动组件皆可亦步亦趋朝向更精进的RFCMOS制程迈进,一是可结合被动组件的模块化,二是大胆地与基频电路做适度的整合,以提高现今CMOS制程产品在较高频率的限制。

2. 晶圆级测试(Wafer Level Testing)技术的配合──为了降低封装成本的考虑,结合晶圆级测试技术为必要趋势,亦是KGD(Known Good Die)的解决途径,由于射频集成电路

和数字集成电路的电性量测需求差异极大,在量测平台与环境屏蔽效果、大量量测的准确度、可靠度、量测探针的材料、弹性与寿命、量测机台的成本.等,都是需重新评估及精进的。

3. CSP及WLCSP(Wafer Level CSP)技术应用与延伸—在芯片尺寸封装的定义下,不超过1.2倍芯片面积封装尺寸的技术,甚至是更新的晶圆级芯片尺寸封装,也都因小型化的需求及技术研发的成熟度,而增加运用到射频集成电路封装的可能性,不过因芯片与基板材质膨胀系数的差异性,导致在制程温度较高的情形下,会有基板电路翘曲及互连打线或锡球断裂的问题,仍需在材质和封装结构的设计上作改善。

4. 低成本、高良率、高可靠度的要求—封装技术精度的提升亦是需努力克服的问题之一,减少公差的幅度,即可改善电路组件电性的稳定度,若能在整合大量被动组件模块化电路中,降低与原型电路的差异,以缩减材料、加工成本的耗费,并增加生产产品的良率。在未来,多功(结合PDA、Radio、MP3)、多频(多种接收频率)、多模(跨不同系统)的行动通讯产品已是必然的趋势。为实现通讯产品“轻薄短小”的极致表现,有待上(电路、模块、组件设计)、中(组件制程、板厂)、下游(测试、封装、组装)各家业者分工合作朝共同目标迈进。

来源:https://www.360docs.net/doc/1812212540.html,/Html/dlsj/115545812.html

射频电路调试测试流程

射频电路调试测试流程(准备阶段) 射频电路的调试作为通信整机研发工作中的重要一环,工作量非常大,几乎所有电路都需要调试,为了提高效率,需要对调试环境、调试方法等进行规范。 环境准备如下 1、防静电 佩戴“静电手环”,并良好接地,若着化纤、羊毛、羽绒服装,外层需加穿防静电服,或防辐射服;小功率、低电压、高频率、小封装的器件均ESD敏感,最容易被ESD击穿的射频器件:RF开关,其次是LNA;所有仪器,开机使用前必须将机壳良好接地;2、电源 稳压电源接入负载前,先校准输出电压,电压等于负载的额定电压; 3、仪器保护 为安全起见:只要射频功率大于20dBm,射频信号源(30dBm)、频谱分析仪(27dBm)、信号源分析仪(23dBm)输入端必须级联同轴衰减器,一般情况下,5W 5dB衰减器为常态配置,若测试功放模块需根据实际输出功率大小配置合适的衰减器; 4、仪器设置 射频信号源:Keysight输出功率<13dBm,R&S输出功率<18dBm,若超出,输出功率可能小于显示值,需实测并进行补偿; 频谱分析仪:屏幕显示的有效动态范围,FSV约70dB,FSW约80dB;仪器的线性输入功率<-3dBm,超出会恶化待测IM3(ACLR)、谐波,应选择合适的内部/外部衰减值; 矢量网络分析仪:仪器的IF带宽决定噪声,测无源器件的带外抑制,应适当降低IF带宽;调测任何电路,必须保证输出功率 龙源期刊网 https://www.360docs.net/doc/1812212540.html, 雷达射频集成电路的发展及应用 作者:黄林锋 来源:《山东工业技术》2017年第24期 摘要:本文概述了雷达射频集成电路技术的特点,是一种以半导体和射频电路技术为基础,一种集信号放大、数据传输和转化功能为一体的技术,并从其发展与演变切入进行研究,探讨了目前常用的几种雷达射频集成电路的发展成果及其应用状况。 关键词:雷达射频集成电路;发展;应用 DOI:10.16640/https://www.360docs.net/doc/1812212540.html,ki.37-1222/t.2017.24.099 现代的雷达系统越来越注重高精度的距离探测与跟踪,还要求较强的抗干扰性、目标识别作用和气象探测功能。由此,要求完整一套的现代雷达系统包含近万个信号接收器和信号发射装置,这也极大提高了系统的复杂性和设备的成本造价。雷达系统的现代化除保留上述基本功能,还应减少设备的造价,这推进了射频集成电路在现代雷达领域的研发 [1]。由无线天线、电磁信号处理器、显示屏幕、控制面板、信号的发射和接收器所组成的现代雷达系统。目前,射频集成系统已经应用于信号的发射和接收器,下文从射频集成电路在雷达系统的研发入手,通过深入研究,介绍雷达系统目前的几种应用现状。 1 雷达射频集成电路的发展概述 随射频集成技术和信息化在雷达系统中的深入发展,射频集成电路已经演变了好几个架构形态[2]。以信号接收系统为例,在三十年内演化出三种不同的形态。在此过程,雷达系统的 数字化不断提高,实现某些频段的完全数字化,使射频集成电路向混合集成电路的方向不断发展。 2 雷达系统射频集成电路的发展及应用研究 2.1 射频集成SOC 以单片作为射频电路的集成基板,SiGe和CMOS作为集成射频与数字化特点的技术平台。技术的快速发展极大提高了射频电路的集成化程度,上部集混合频率、放大频率和合成信号功能为一体,下部集增频、分贝放大功能的器件。雷声公司(美国)研发的最新设备——X 波段应用了上述技术 [3],其在实际中具有高性能、减小雷达体积和节约造价的应用优势。 2.2 射频多通道集成电路 在一个集成芯片上集多通道于一体,这种集成电路没有射频集成电路那么多的器件,应用系统的封装工艺,以高度集成化的多通道芯片,实现射频混合电路的性能优化和结构简化。采 射频电路调试经验及问题分析 1前言 文档总结了我工作一年半以来的一些射频(Radio Frequency)调试(以下称为Debug)经验,记录的是我在实际项目开发中遇到并解决问题的过程。现在我想利用这份文档与大家分享这些经验,如果这份文档能够对大家的工作起到一定的帮助作用,那将是我最大的荣幸。 个人感觉,Debug过程用的都是最简单的基础知识,如果能够对RF的基础知识有极为深刻(注意,是极为深刻)的理解,我相信,所有的Bug解起来都会易如反掌。同样,我的这篇文档也将会以最通俗易懂的语言,讲述最通俗易懂的Debug技巧。 在本文中,我尽量避免写一些空洞的理论知识,但是第二章的内容除外。“微波频率下的无源器件”这部分的内容截取自我尚未完成的“长篇大论”——Wi-Fi产品的一般射频电路设计(第二版)。 我相信这份文档有且不只有一处错误,如果能够被大家发现,希望能够提出,这样我们就能够共同进步。 2微波频率下的无源器件 在这一章中,主要讲解微波频率下的无源器件。一个简单的问题:一个1K的电阻在直流情况下的阻值是1K,在频率为10MHz的回路中可能还是1K,但是在10GHz的情况下呢?它的阻值还会是1K吗?答案是否定的。在微波频率下,我们需要用另外一种眼光来看待无源器件。 2.1.微波频率下的导线 微波频率下的导线可以有很多种存在方式,可以是微带线,可以是带状线,可以是同轴电缆,可以是元件的引脚等等。 2.1.1.趋肤效应 在低频情况下,导线内部的电流是均匀的,但是在微波频率下,导线内部会产生很强的磁场,这种磁场迫使电子向导体的边缘聚集,从而使电流只在导线的表面流动,这种现象就称为趋肤效应。趋肤效应导致导线的电阻增大,结果会怎样?当信号沿导体传输时衰减会很严重。在实际的高频场合,如收音机的感应线圈,为了减少趋肤效应造成的信号衰减,通常会使用多股导线并排绕线,而不会使用单根的导线。我们通常用趋肤深度来描述趋肤效应。趋肤深度是频率与导线本身共同的作用,在这里我们不会作深入的讨论。 2.1.2.直线电感 我们知道,在有电流流过的导线周围会产生磁场,如果导线中的电流是交变电流,那么磁场强度也会随着电流的变化而变化,因此,在导线两端会产生一个阻止电流变化的电压,这种现象称之为自感。也就是说,微波频率下的导线会呈现出电感的特性,这种电感称为直线电感。也许你会直线电感很微小,可以忽略,但是我们将会在后面的内容中看到,随着频率的增高,直线电感就越来越重要。 电感的概念是非常重要的,因为微波频率下,任何导线(或者导体)都会呈现出一定的电感特性,就连电阻,电容的引脚也不例外。 2.2.微波频率下的电阻 从根本上说,电阻是描述某种材料阻碍电流流动的特性,电阻与电流,电压的关系在欧姆定律中已经给出。但是,在微波频率下,我们就不能用欧姆定律去简单描述电阻,这个时候,电阻的特性应经发生了很大的变化。 2.2.1.电阻的等效电路 电阻的等效电路。其中R就是电阻在直流情况下电阻自身的阻值,L是电阻的引脚,C 因电阻结构的不同而不同。我们很容易就可以想到,在不同的频率下,同一个电阻会呈现出不同的阻值。想想平时在我们进行Wi-Fi产品的设计,几乎不用到直插的元件(大容量电解 最详细解读射频芯片 传统来说,一部可支持打电话、发短信、网络服务、APP应用的手机,一般包含五个部分部分:射频部分、基带部分、电源管理、外设、软件。 射频部分:一般是信息发送和接收的部分; 基带部分:一般是信息处理的部分; 电源管理:一般是节电的部分,由于手机是能源有限的设备,所以电源管理十分重要; 外设:一般包括LCD,键盘,机壳等; 软件:一般包括系统、驱动、中间件、应用。 在手机终端中,最重要的核心就是射频芯片和基带芯片。射频芯片负责射频收发、频率合成、功率放大;基带芯片负责信号处理和协议处理。那么射频芯片和基带芯片是什么关系? 1. 射频芯片和基带芯片的关系 先讲一下历史,射频(Radio Frenquency)和基带(Base Band)皆来自英文直译。其中射频最早的应用就是Radio——无线广播(FM/AM),迄今为止这仍是射频技术乃至无线电领域最经典的应用。 基带则是band中心点在0Hz的信号,所以基带就是最基础的信号。有人也把基带叫做“未调制信号”,曾经这个概念是对的,例如AM为调制信号(无需调制,接收后即可通过发声元器件读取内容)。 但对于现代通信领域而言,基带信号通常都是指经过数字调制的,频谱中心点在0Hz的信号。而且没有明确的概念表明基带必须是模拟或者数字的,这完全看具体的实现机制。 言归正传,基带芯片可以认为是包括调制解调器,但不止于调制解调器,还包括信道编解码、信源编解码,以及一些信令处理。而射频芯片,则可看做是最简单的基带调制信号的上变频和下变频。 所谓调制,就是把需要传输的信号,通过一定的规则调制到载波上面让后通过无线收发器(RF Transceiver)发送出去的工程,解调就是相反的过程。 2.工作原理与电路分析 射频简称RF射频就是射频电流,是一种高频交流变化电磁波,为是Radio Frequency的缩写,表示可以辐射到空间的电磁频率,频率范围在300KHz~300GHz之间。每秒变化小于1000次的交流电称为低频电流,大于10000次的称为高频电流,而射频就是这样一种高频电流。高频(大于10K);射频(300K-300G)是高频的较高频段;微波频段(300M-300G)又是射频的较高频段。射频技术在无线通信领域中被广泛使用,有线电视系统就是采用射频传输方式。 RF设计与应用----射频集成电路封装 关键词:射频,多层电路板,电路封装 摘要:针对无线通信产品业者所面临的课题,本文试着从封装技术在射频集成电路上应用的角度,来介绍射频集成电路封装技术的现况、现今封装技术对射频集成电路效能的影响,以及射频集成电路封装的未来发展和面临的挑战。 在行动通讯质量要求的提高,通讯带宽的需求量大增,因应而生的各项新的通讯规范如GPRS、W-CDMA、CDMA-2000、Bluetooth、 802.11b纷纷出笼,其规格不外乎:更高的数据传输速率、更有效的调变方式、更严谨的噪声规格限定、通讯功能的增强及扩充,另外再加上消费者对终端产品“轻、薄、短、小、久(包括产品的使用寿命、维护保固,甚至是手机的待机时间)”的诉求成了必要条件;于是乎,为了达成这些目的,各家厂商无不使出混身解数,在产品射频(Radio Frequency)、中频(Intermediate Frequency)与基频(Base Band)电路的整合设计、主动组件的选择应用、被动组件数目的减少、多层电路板内线路善加运用等,投注相当的心血及努力,以求获得产品的小型化与轻量化。 针对这些无线通信产品业者所面临的课题,我们试着从封装技术在射频集成电路上应用的角度,来介绍射频集成电路封装技术的现况、现今封装技术对射频集成电路效能的影响,以及射频集成电路封装的未来发展和面临的挑战。 射频集成电路封装技术的现况 就单芯片封装(Single Chip Package)的材质而言,使用塑料封装( P l a s t i c Pac kage)的方式,是一般市面上常见到的高频组件封装类型,低于3GHz工作频率的射频集成电路及组件,在不严格考虑封装金属导线架(Metal Lead Frame)和打线(Wire Bond)的寄生电感(Parasitic Inductance)效应下,是一种低成本且可薄型化的选择。由于陶瓷材料防水气的渗透性特佳及满足高可靠度的需求,故也有采用陶瓷封装技术;对于加强金属屏蔽作用及散热效果的金属封装,可常在大功率组件或子系统电路封装看到它的踪迹。 2.4GHz ISM射频前端模块的设计及应用 2.4GHz工业科学医疗设备(ISM)是全世界公开通用使用的无线频段,蓝牙( Bluetooth)、 Wi-Fi、ZigBee等短距离无线数据通信均工作在2.4GHz ISM频段。 针对2.4GHz ISM频段无线应用,锐迪科微电子公司推出了RDA T212射频前端模块。T212芯片集成了功率放大器( PA)、低噪声放大器( LNA)、天线开关(Antenna Switch)和功率检测器(Power Detector),并特别增加PA带通及LNA带通的省电功能,内部还针对天线端做了 ESD保护设计。T212芯片采用标准的 QFN 3×3mm2超小型封装,输入和输出已集成隔直电容和匹配电路,外围元件仅需少量滤波电容,极大地简化了PCB设计。 高集成度、超小尺寸并提供省电功能的T212射频前端模块,在手机蓝牙以及802.11.b/g扩展应用中大有可为。同时,T212芯片还具有优异的线性度,支持Bluetooth 2.0的高速率应用。 T212模块的性能 T212射频前端模块内集成的功率放大器采用先进的砷化镓异质结双极晶体管( GaAs HBT)工艺制造,低噪声放大器和天线开关采用增强型高电子迁移率场效应晶体管( E-PHEMT)工艺制造。尽管没有采用差分PA的形式,但是T212依然为客户提供了差分输入管脚,从而使客户不需要再关心差分转单端的设计。 T212集成的功率放大器是一款高线性高效率PA,在2.4GHz~2.5GHz频段内有20dB增益,线性输出功率为18dBm时的三阶交调IM3小于-30dBc。PA的静态工作电流可低至10mA,饱和输出功率可达23dBm,功率附加效率高达45%,这么高的效率有助于延长供电时间。 Wi-Fi产品射频电路调试经验 https://www.360docs.net/doc/1812212540.html,/article/11-04/422921302067041.html?sort=1111_1119_1438_0 2011-04-06 13:17:21 来源:电子发烧友 关键字:Wi-Fi 射频电路调试经验 这份文档是生花通信的一线射频工程师总结了的Wi-Fi产品开发过程中的一些射频调试经验,记录并描述在实际项目开发中遇到并解决问题的过程。 1 前言 这份文档总结了我工作一年半以来的一些射频(Radio Frequency)调试(以下称为Debug)经验,记录的是我在实际项目开发中遇到并解决问题的过程。现在我想利用这份文档与大家分享这些经验,如果这份文档能够对大家的工作起到一定的帮助作用,那将是我最大的荣幸。 个人感觉,Debug过程用的都是最简单的基础知识,如果能够对RF的基础知识有极为深刻(注意,是极为深刻)的理解,我相信,所有的Bug解起来都会易如反掌。同样,我的这篇文档也将会以最通俗易懂的语言,讲述最通俗易懂的Debug技巧。 在本文中,我尽量避免写一些空洞的理论知识,但是第二章的内容除外。“微波频率下的无源器件”这部分的内容截取自我尚未完成的“长篇大论”——Wi-Fi产品的一般射频电路设计(第二版)。 我相信这份文档有且不只有一处错误,如果能够被大家发现,希望能够提出,这样我们就能够共同进步。 2 微波频率下的无源器件 在这一章中,主要讲解微波频率下的无源器件。一个简单的问题:一个1K的电阻在直流情况下的阻值是1K,在频率为10MHz的回路中可能还是1K,但是在10GHz的情况下呢?它的阻值还会是1K吗?答案是否定的。在微波频率下,我们需要用另外一种眼光来看待无源器件。 2.1. 微波频率下的导线 微波频率下的导线可以有很多种存在方式,可以是微带线,可以是带状线,可以是同轴电缆,可以是元件的引脚等等。 2.1.1. 趋肤效应 在低频情况下,导线内部的电流是均匀的,但是在微波频率下,导线内部会产生很强的磁场,这种磁场迫使电子向导体的边缘聚集,从而使电流只在导线的表面流动,这种现象就称为趋肤效应。趋肤效应导致导线的电阻增大,结果会怎样?当信号沿导体传输时衰减会很严重。 在实际的高频场合,如收音机的感应线圈,为了减少趋肤效应造成的信号衰减,通常会使用多股导线并排绕线,而不会使用单根的导线。 射频电路PCB的设计技巧 摘要:针对多层线路板中射频电路板的布局和布线,根据本人在射频电路PCB设计中的经验积累,总结了一些布局布线的设计技巧。并就这些技巧向行业里的同行和前辈咨询,同时查阅相关资料,得到认可,是该行业里的普遍做法。多次在射频电路的PCB设计中采用这些技巧,在后期PCB的硬件调试中得到证实,对减少射频电路中的干扰有很不错的效果,是较优的方案。 关键词:射频电路;PCB;布局;布线 由于射频(RF)电路为分布参数电路,在电路的实际工作中容易产生趋肤效应和耦合效应,所以在实际的PCB设计中,会发现电路中的干扰辐射难以控制,如:数字电路和模拟电路之间相互干扰、供电电源的噪声干扰、地线不合理带来的干扰等问题。正因为如此,如何在PCB的设计过程中,权衡利弊寻求一个合适的折中点,尽可能地减少这些干扰,甚至能够避免部分电路的干涉,是射频电路PCB设计成败的关键。文中从PCB的LAYOUT角度,提供了一些处理的技巧,对提高射频电路的抗干扰能力有较大的用处。 1 RF布局 这里讨论的主要是多层板的元器件位置布局。元器件位置布局的关键是固定位于RF路径上的元器件,通过调整其方向,使RF路径的长度最小,并使输入远离输出,尽可能远地分离高功率电路和低功率电路,敏感的模拟信号远离高速数字信号和RF信号。 在布局中常采用以下一些技巧。 1.1 一字形布局 RF主信号的元器件尽可能采用一字形布局,如图1所示。但是由于PCB板和腔体空间的限制,很多时候不能布成一字形,这时候可采用L形,最好不要采用U字形布局(如图2所示),有时候实在避免不了的情况下,尽可能拉大输入和输出之间的距离,至少1.5 cm 以上。 射频集成电路低噪声放大器研究前景 摘要 近年来,随着无线通信技术在移动通信、全球互联接入以及物联网等领域越来越广泛的应用。对于现代通信系统往往要求提供两个甚至更多的无线服务,因此就要求射频电路前端中的关键部件低噪声放大器(Low Noise Amplifier,LNA)能在多个频带下具有放大能力。因此如何能够放大多个频带的宽带低噪声放大器成为研究热点。 低噪声放大器是现代无线通信、雷达、电子对抗系统等应用中的十分重要的部分,常用于接收系统的前端,在放大信号的同时降低噪声干扰,提高系统灵敏度。如果在接受系统的前端连接高性能的低噪声放大器,在低噪声放大器增益足够大的情况下,就能抑制后级电路的噪声,则整个接收机系统的噪声系数将主要取决于放大器的噪声。如果低噪声放大器的噪声系数降低,接收机系统的噪声系数也会变小,信噪比得到改善,灵敏度大大提高。由于可见噪声放大器的性能制约了整个接收系统的性能,对于整个接收系统技术水平的提高,也起了决定性的作用。 宽带低噪声放大器是一种需要有良好的输入匹配的部分。输入匹配是要求兼顾阻抗匹配和噪声系数的,对于这两个指标一般来说是耦合在一起的。现有的宽带匹配技术需要反复协调电路各部分参数,通过对阻抗匹配和噪声系数这两个指标的折中设定来达到输入匹配的要求,因此给设计增大了难度。 噪声抵消技术是一种可以有效的将上述两个重要参数进行分离的方法,对降低设计复杂度、缩短设计周期、降低设计成本具有重要意义。现有的噪声抵消电路结构基本上都是基于CMOS工艺的。近年来,随着SiGe 技术的发展,SiGe BiCMOS工艺逐渐成为射频集成电路工艺的主流。然而,基于 SiGe工艺的采用噪声抵消结构的设计方法还未见报道。因此,本文基于SiGe工艺,开展对工作于0.8-5.2GHz频段低噪声放大器的噪声抵消电路结构的设计研究。 1、解释基本概念:集成电路,集成度,特征尺寸 参考答案: A、集成电路(IC:integrated circuit)是指通过一系列特定的加工工艺,将晶体管、二极管等有源器件和电阻、电容等无源器件,按照一定的电路互连,“集成”在一块半导体晶片(如硅或砷化镓)上,封装在一个外壳内,执行特定电路或系统功能的集成块。 B、集成度是指在每个芯片中包含的元器件的数目。 C、特征尺寸是代表工艺光刻条件所能达到的最小栅长(L)尺寸。 2、写出下列英文缩写的全称:IC,MOS,VLSI,SOC,DRC,ERC,LVS,LPE 参考答案: IC:integrated circuit;MOS:metal oxide semiconductor;VLSI:very large scale integration;SOC:system on chip;DRC:design rule check;ERC:electrical rule check;LVS:layout versus schematic;LPE:layout parameter extraction 3、试述集成电路的几种主要分类方法 参考答案: 集成电路的分类方法大致有五种:器件结构类型、集成规模、使用的基片材料、电路功能以及应用领域。根据器件的结构类型,通常将其分为双极集成电路、MOS集成电路和Bi-MOS 集成电路。按集成规模可分为:小规模集成电路、中规模集成电路、大规模集成电路、超大规模集成电路、特大规模集成电路和巨大规模集成电路。按基片结构形式,可分为单片集成电路和混合集成电路两大类。按电路的功能将其分为数字集成电路、模拟集成电路和数模混合集成电路。按应用领域划分,集成电路又可分为标准通用集成电路和专用集成电路。 4、试述“自顶向下”集成电路设计步骤。 参考答案: “自顶向下”的设计步骤中,设计者首先需要进行行为设计以确定芯片的功能;其次进行结构设计;接着是把各子单元转换成逻辑图或电路图;最后将电路图转换成版图,并经各种验证后以标准版图数据格式输出。 5、比较标准单元法和门阵列法的差异。 参考答案: 射频电路设计地困境及对策 hc360慧聪网通信行业频道 2004-04-16 11:23:41 射频电路地设计技术一度专属于少数专家掌握并拥有其自己地专用芯片组,如今已能和数字电路模块及模拟电路模块集成在同一块 IC 里了.再则,射频电路设计中固有地临界尺寸要求,更增加了工程压力. 要点●射频电路设计师必须经常采用间接测量电路性能地方式,来推断电路故障地原因. ●射频电路设计问题正在影响数字电路设计和模拟电路设计. ●将射频电路集成在同一块印制电路板或 IC 上,这会促使人们使用一种新地设计方法. ● EDA 厂商正在开始提供集成时域仿真和频域仿真地分析工具. 射频电路设计就是对发射电磁信号地电路进行设计.射频意为无线电频率,因为射频电路在其初期,只能发射调幅和调频两个波段地无线电信号.今天,把高频电路设计称为“射频电路设计”,只是沿用了历史名称.图1表明,自从 20 世纪 60 年代使用 UHF 电视技术以来,广播设备使用高于 300000 MHz地频率.从那时以来,通信设备地内容、频率和带宽都增加了.安捷伦科技 HY016射频设计6_射频匹配电路调试 全部频段在QSPR中校准通过后,便可以进行电路优化了,也就是我们通常说的调匹配。 我们实验室采用的是盲调,即以最终实测性能的好坏来决定最终的匹配电路;与之对应的另一种方法是根据器件规格书,用网络分析仪逐个端口调试,使其和规格书要求相对应。对于RDA PhaseII方案,盲调性能挺好。 对于频分电路(FDD LTE/WCDMA/CDMA),重点是调双工器的输入输出端匹配;对于时分电路(TDD-LTE/TDSCDMA),重点是调滤波器的输入输出匹配。双工的调试相对复杂,本文会以HY016欧洲版中B20双工为例进行说明。 射频电路调试的最终原则包括: 1,发射端兼顾电流和线性度,也就是在ACLR余量足够的情况下尽可能的降低最大发射功率的电流,同时兼顾整个频段中高中低信道的平坦度。 2,接收端以提高接收灵敏度为最终原则 3,不是把某块板子的性能调到最佳为准;而是要留够余量,保证量产大批量板子的性能都能达到良好为准 双工器电路我通常的调试步骤: 1,初始bom采用datasheet的参考匹配 2,调节公共端的到地电感,让低、中、高信道特性一致,包括电流和ACLR 3,调节公共端的串联电感/电容,找出ACLR和电流的最佳权衡 4,调节发射端输入匹配,找出ACLR和电流的最佳权衡,最终确认发射端匹配 5,在QSPR下直接校准接收进行接收调试:若信道间差距过大就优先到地电感;若信道间差距不大则优化串联电感/电容;调试完成后实测灵敏度最终确认接收匹配 调试发射电路时,需要和仪表相连。通常在用QSPR完成校准后,再在QPST->PDC中导入并激活ROW_Gen_Commercial.MBN便可以和仪表通信了。关于MBN激活这部分,会在后续工厂文件部分详细说明,这里不再展开。 GPS接收机射频前端电路原理与设计 摘要:在天线单元设计中采用了高频、低噪声放大器,以减弱天线热噪声及前面几级单元电路对接收机性能的影响;基于超外差式电路结构、镜频抑制和信道选择原理,选用GP2010芯片实现了射频单元的三级变频方案,并介绍了高稳定度本振荡信号的合成和采样量化器的工作原理,得到了导航电文相关提取所需要的二进制数字中频卫星信号。 关键词:GPS接收机灵敏度超外差锁相环频率合成 利用GPS卫星实现导航定位时,用户接收机的主要任务是提取卫星信号中的伪随机噪声码和数据码,以进一步解算得到接收机载体的位置、速度和时间(PVT)等导航信息。因此,GPS接收机是至关重要的用户设备。目前实际应用的GPS接收机电路一般由天线单元、射频单元、通信单元和解算单元等四部分组成,如图1所示。本文在分析GPS卫星信号组成的基础上,给出了射频前端GP2010的原理及应用。 1 GPS卫星信号的组成 GPS卫星信号采用典型的码分多址(CDMA)调制技术进行合成(如图2所示),其完整信号主要包括载波、伪随机码和数据码等三种分量。信号载波处于L波段,两载波的中心频率分别记作L1和L2。卫星信号参考时钟频率f0为10.23MHz,信号载波L1的中心频率为f0的154倍频,即: fL1=154×f0=1575.42MHz (1) 其波长λ1=19.03cm;信号载波L2的中心频率为f0的120倍频,即: fL2=120×f0=1227.60MHz (2) 其波长λ2=24.42cm。两载波的频率差为347.82MHz,大约是L2的 28.3%,这样选择载波频率便于测得或消除导航信号从GPS卫星传播至接收机时由于电离层效应而引起的传播延迟误差。伪随机噪声码(PRN)即测距码主要有精测距码(P码)和粗测距码(C/A码)两种。其中P 码的码率为10.23MHz、C/A码的码率为1.023MHz。数据码是GPS卫星以二进制形式发送给用户接收机的导航定位数据,又叫导航电文或D 码,它主要包括卫星历、卫星钟校正、电离层延迟校正、工作状态信息、C/A码转换到捕获P码的信息和全部卫星的概略星历;总电文由1500位组成,分为5个子帧,每个子帧在6s内发射10个字,每个字30位,共计300位,因此数据码的波特率为50bps。 射频发射机电路设计 文献综述 前言 超外差接收是一种巧妙的接收方法,利用它,能使因无线电信号直接接收和放大而引起的一系列困难得到解决。在费森登思想的基础上,1912年,阿姆斯特朗在接收机中设置了本机振荡(简称“本振”)电路,通过双联可变电容器进行同步调谐,保证本振频率始终跟踪外来信号频率的变化,而且始终比外来信号高一个固定的中频。这样,不管所接收的各个电台的载波频率差别多大,与本振频率混频后,产生的都是统一的中频信号。再对这个统一的中频信号进行放大、检波,就可得到所需要的音频信号。利用超外差原理设计的电路,能使接收机电路大大简化,接收机的性能与灵敏度也得到提高。当时阿姆斯特朗还成功地组装出一台超外差接收机。同年,阿姆斯特朗与德·福雷斯特及兰茂尔各自独立发明了再生电路。 超外差接收原理不仅适用于收音机电路,还具有广泛的应用价值,它适用于电视广播、微波通信、雷达等无线电技术的各个领域。超外差原理已成为现代无线电接收理论的基础,凡是涉及无线电信号接收的电子设备,都离不开超外差接收电路。阿姆斯特朗的这项重要发明,不仅推动了无线电技术早期发展的进程,而且在无线电事业的征途上至今还闪现着它的技术光芒。 超外差原理的典型应用是超外差接收机。从天线接收的信号经高频放大器(见调谐放大器)放大,与本地振荡器产生的信号一起加入混频器变频,得到中频信号,再经中频放大、检波和低频放大,然后送给用户。接收机的工作频率范围往往很宽,在接收不同频率的输入信号时,可以用改变本地振荡频率f1的方法使混频后的中频fi保持为固定的数值。 概述 超外差接收机是超外差电路的典型应用,是全面学习模拟电路基础知识最好的切入点之一。通过简单分析超外差式接收机中输入电路、变频电 射频电路和射频集成电路线路设计(9天) 培训时间为9天 课程特色 1)本讲座总结了讲演者20多年的工作,报告包括 o设计技术和技巧的经验, o获得的美国专利, o实际工程设计的例子, o讲演者的理论演译。 o 【主办单位】中国电子标准协会 【协办单位】智通培训资讯网 【协办单位】深圳市威硕企业管理咨询有限公司 o 2)本讲座分为三个部分: A. 第一部分讨论和強调在射频电路设计中的设计技术和技巧, 着重论述设计中关鍵性 的技术和技巧,譬如,阻抗匹配,射频接地, 单端线路和差分线路之間的主要差別,射频集成电路设计中的难题……可以把它归类为橫向论述. 到目前为止,这种着重于设计技巧的論述是前所未有的,也是很独特的。讲演者认为,作为一位合格的射频电路设计的设计者,不论是工程师,还是教授,应当掌握这一部分所论述的基本的设计技术和技巧,包括: ?阻抗匹配; ?接地; ?射频集成电路设计; ?测试 ?画制版图; ? 6 Sigma 设计。 B. 第二部分: 描述射频系统的基本参数和系统设计的基本原理。 C. 第三部分: 提供个别射频线路设计的基本知识。这一部份和现有的有关射频电路和 射频集成电路设计的书中的论述相似, 其內容是讨论一个个射频方块,譬如,低噪声放大器,混频器,功率放大器,壓控振蕩器,頻率综合器……可以把它归类为纵向论述,其中的大多数内容来自本讲座的讲演者的设计 ?在十几年前就已经找到了最佳的低噪声放大器的设计方法但不曾经发表过。在低噪声放大器的设计中可以同时达到最大的增益和最小的噪 声; ?获得了可调谐濾波器的美国专利; ?本讲座的讲演者所建立的用单端线路的设计方法来进行差分对线路的设计大大简化了设计并缩短了线路仿真的时间; ?获得了双线巴伦的美国专利。 学习目标在本讲座结束之后,学员可以了解到 o比照数码电路,射頻电路设计的主要差別是什麼? o什么是射频设计中的基本概念? o在射频电路设计中如何做好窄带的阻抗匹配? o在射频电路设计中如何做好宽带的阻抗匹配? o在射频线路板上如何做好射频接地的工作? o为什么在射频和射频集成电路设计中有从单端至双差分的趋势? o为什么在射频电路设计中容许误差分析如此重要? o什么是射频和射频集成电路设计中的主要难题?射频和射频集成电路设计师如何克服这些障碍? 射频通信电路课程设计报告 引言 混频器在通信工程和无线电技术中,应用非常广泛,在调制系统中,输入的基带信号都要经过频率的转换变成高频已调信号。在解调过程中,接收的已调高频信号也要经过频率的转换,变成对应的中频信号。特别是在超外差式接收机中,混频器应用较为广泛,如AM 广播接收机将已调幅信号535KHZ-一1605KHZ要变成为465KHZ中频信号,电视接收机将已调48.5M一870M 的图象信号要变成38MHZ的中频图象信号。 常用的振幅检波电路有包络检波和同步检波两类。输出电压直接反映调幅包络变化规律的检波电路,称为包络检波电路,它适用于普通调幅波的检波。通常根据信号大小的不同,将检波器分为小信号平方律检波和大信号峰值包络检波两信号检波。 目前, 在应用较广泛的电路仿真软件中, Pspice是应用较多的一种。Psp ice 能够把仿真与电路原理图的设计紧密得结合在一起。广泛应用于各种电路分析,可以满足电路动态仿真的要求。其元件模型的特性与实际元件的特性十分相似,因而它的仿真波形与实验电路的测试结果相近,对电路设计有重要的指导意义。 由此可见,混频电路是应用电子技术和无线电专业必须掌握的关键电路。 [3] 目录 引言 (2) 一.概述 (3) 二. 方案分析 (4) 三.单元电路的工作原理 (6) 1.LC正弦波振荡器 (6) 2.模拟乘法器电路 (8) 3.谐振电路 (9) 4.包络检波 (12) 四.电路性能指标的测试 (16) 五.课程设计体会..................................................................................................... 错误!未定义书签。参考文献..................................................................................................................... 错误!未定义书签。 班级:通信二班姓名:赵庆超学号:20071201297 7,版图设计中整体布局有哪些注意事项? 答:1版图设计最基本满足版图设计准则,以提高电路的匹配性能,抗干扰性能和高频工作性能。 2 整体力求层次化设计,即按功能将版图划分为若干子单元,每个子单元又可能包含若干子单元,从最小的子单元进行设计,这些子单元又被调用完成较大单元的设计,这种方法大大减少了设计和修改的工作量,且结构严谨,层次清晰。 3 图形应尽量简洁,避免不必要的多边形,对连接在一起的同一层应尽量合并,这不仅可减小版图的数据存储量,而且版图一模了然。 4 在构思版图结构时,除要考虑版图所占的面积,输入和输出的合理分布,较小不必要的寄生效应外,还应力求版图与电路原理框图保持一致(必要时修改框图画法),并力求版图美观大方。 8,版图设计中元件布局布线方面有哪些注意事项? 答:1 各不同布线层的性能各不相同,晶体管等效电阻应大大高于布线电阻。高速电路,电荷的分配效应会引起很多问题。 2 随器件尺寸的减小,线宽和线间距也在减小,多层布线层之间的介质层也在变薄,这将大大增加布线电阻和分布电阻。 3 电源线和地线应尽可能的避免用扩散区和多晶硅布线,特别是通过 较大电流的那部分电源线和地线。因此集成电路的版图设计电源线和地线多采用梳状布线,避免交叉,或者用多层金属工艺,提高设计布线的灵活性。 4 禁止在一条铝布线的长信号霞平行走过另一条用多晶硅或者扩散区布线的长信号线。因为长距离平行布线的两条信号线之间存在着较大的分布电容,一条信号线会在另一条信号线上产生较大的噪声,使电路不能正常工作。、 5 压点离开芯片内部图形的距离不应少于20um,以避免芯片键和时,因应力而造成电路损坏。 《射频集成电路设计基础》讲义 课程概述 关于射频(RF) 关于射频集成电路 无线通信与射频集成电路设计 课程相关信息 RFIC相关IEEE/IEE期刊和会议 关于射频 ? 射频= Radio Frequency (RF) → Wireless! ? Why Wireless? – 可移动(Mobile) – 个人化(Personalized) – 方便灵活(Self-configuring) – 低成本(在某些情况下) – and more ... ? Why Wired? <<>><>? <<>><>? ? 多高的频率才是射频? ? 为什么使用高频频率? 30-300kHz LF 中波广播530-1700 kHz 300kHz-3MHz MF 短波广播 5.9-26.1 MHz 3-30MHz HF RFID 13 MHz 30-300MHz VHF 调频广播88-108 MHz 我们关心的频段 300-1000MHz UHF (无线)电视54-88, 174-220 MHz 1-2 GHz L-Band 遥控模型72 MHz 2-4 GHz S-Band 个人移动通信900MHz, 1.8, 1.9, 2 GHz 4-8 GHz C-Band WLAN, Bluetooth (ISM Band) 2.4-2.5GHz, 5-6GHz 注1:本表主要参考国外标准 注2:ISM =Industrial, Scientific and Medical 关于射频集成电路 ? 是什么推动了RFIC的发展? – Why IC? – 体积更小,功耗更低,更便宜→移动性、个人化、低成本 – 功能更强,适合于复杂的现代通信网络 – 更广泛的应用领域如生物芯片、RFID等 ? Quiz: why not fully integrated? ? 射频集成电路设计最具挑战性之处在于,设计者向上必须 懂得无线系统的知识,向下必须具备集成电路物理和工艺 基础,既要掌握模拟电路的设计和分析技巧,又要熟悉射频 和微波的理论与技术。(当然,高技术应该带来高收益:) <<>><>? 实验一射频前端发射和接收器 一、实验目的: 1、了解射频前端发射器和接收器的基本结构与主要设计参数。 2、利用实验模组的实际测量了解射频前端发射器和接收器的基本特性。 二、预习内容: 1、预习放大器、滤波器、混频器、功率放大器的原理的理论知识。 2、预习放大器、滤波器、混频器、功率放大器的设计的原理的理论知识。 3、熟悉带通滤波器、变频器、信号发生器、低噪声放大器、中频放大器的 理论知识。 4、熟悉带通滤波器、变频器、信号发生器、低噪声放大器、中频放大器的 设计的理论知识。 三、实验设备: 四、理论分析: 基本结构与设计参数说明: 在无线通讯中,射频发射器担任着重要的角色。无论是话音还是数据信号要利用电磁波传送到远端,必须使用射频前端发射器。如图1-1(a)所示,它大抵可分成九个部分。 1.中频放大器(IF Amplifier) 2.中频滤波器(IF Bnadpass Filter) 3.上变频频混频器(Up-Mixer; Up Converter) 4.射频滤波器(RFBandpass Filter) 5.射频驱动放大器(RF Driver Amplifier) 6.射频功率放大器(RF Power Amplifier) 7.载波振荡器(Carrier Oscillator; Local Oscillator) 8.载波滤波器(LO BPF) 9.发射天线(Antenna) 其中放大器的基本原理与设计方法可参考主题六,而滤波器的基本原理与设 计方法已可参考主题五的说明。至于振荡器的部分,可于主题八与与主题九获得一些参考。 天线部分则可由主题十得到概念。 所以,在此单元中将就上变频器部分的基本原理做一说明。并介绍发射器的几个重要设计参数。 图1-1(a)基本射频前端发射器结构图 图1-1(b)单变频结构射频前端接收器 如图1-1(b)可见,射频前端接收器可分为天线(Antenna)、射频低噪声放大器(RF Low Noise Amplifier , LNA)、下变频器(Down-Mixer , Down Converter)、中频滤波器(Intermidate Frequency Bandpass Filter , IF BPF)、本地振荡器 (Local Oscillator , LO)。其工作原理是将发射端所发射的射频信号由天线接收后,经LNA 将功率放大,再送入下变频器与LO 混频后由中频滤波器将设计所要的部分(Baseband Processing Unit 、BPU)解调(Demodulation)出所需要的信号(Message Signals). 这类只经一个混频器上变频(或下变频)的电路构造称为单变频结构(Single Conversion configuration)。而在实际应用中也有双变频结构(Dual Conversion Configuration),甚至多变频结构(Multi-conversion Configuration),使用的时机视系统指标而定。因为BPU 的处理频率有所限制(一般在500MHz 以下),所以需要利用变频器(Mixer)及频道振荡器(Channel Oscillator)将射频信号由射频前端接收器下变频为中频段(Intermidate Frequency Band 、IF)信号后再送入BPU ,或是将BPU 送出的IF 信号用射频前端发射器上变频至射频段(Radio Frequency Band 、RF)信号经放大后再发射。 本单元以单变频结构来说明一个射频前端接收器的各设计参数. Signal From Unit BPU雷达射频集成电路的发展及应用

射频电路调试经验及问题分析

最详细解读射频芯片

RF 设计与应用----射频集成电路封装

2.4GHZ射频前端设计

WiFi产品射频电路调试经验

射频电路PCB的设计技巧

射频集成电路综述

集成电路设计基础复习

射频电路设计困境及对策

HY016射频设计6_射频匹配电路调试

GPS接收机射频前端电路原理与设计

射频发射机电路设计

射频电路和射频集成电路线路设计

射频通信电路课程设计报告

集成电路设计基础 课后答案

射频介绍

实验一 射频前端发射和接收器