正交鉴频器设计实验报告(demo)

16MHz 调频接收机的设计

无43 孙忆南2004011007

第一部分:正交鉴频器的设计装调

设计指标与要求:

使用MC1496 设计正交鉴相鉴频器,能够解调50mV e.m.f,调制信号1kHz,频偏20kHz,载频为1.709MHz 的调频信号,对于寄生调幅的抑制没有要求。提供的主要器件为MC1496,LM741,10x10 型50uH中周。

一、实验目的:

1.加深对相乘器工作原理的认识;

2.掌握正交鉴相鉴频器的工程设计方法;

3.掌握用频率特性测试仪调试移相网络和鉴频特性曲线的方法。

二、正交鉴频器的电路设计

2.1 正交鉴频器的工作原理

常见的鉴频器有双失谐鉴频器,比例鉴频器,正交鉴相鉴频器等。其核心都是将调频波转化为调频调幅波或调频调相波。其中,正交鉴相鉴频器性能较好,便于集成化,应用逐渐广泛,其他两种形式一般只在过去的分立元件电路中应用。

正交鉴相鉴频器由移相网络和鉴相器构成。

2.2 移相网络

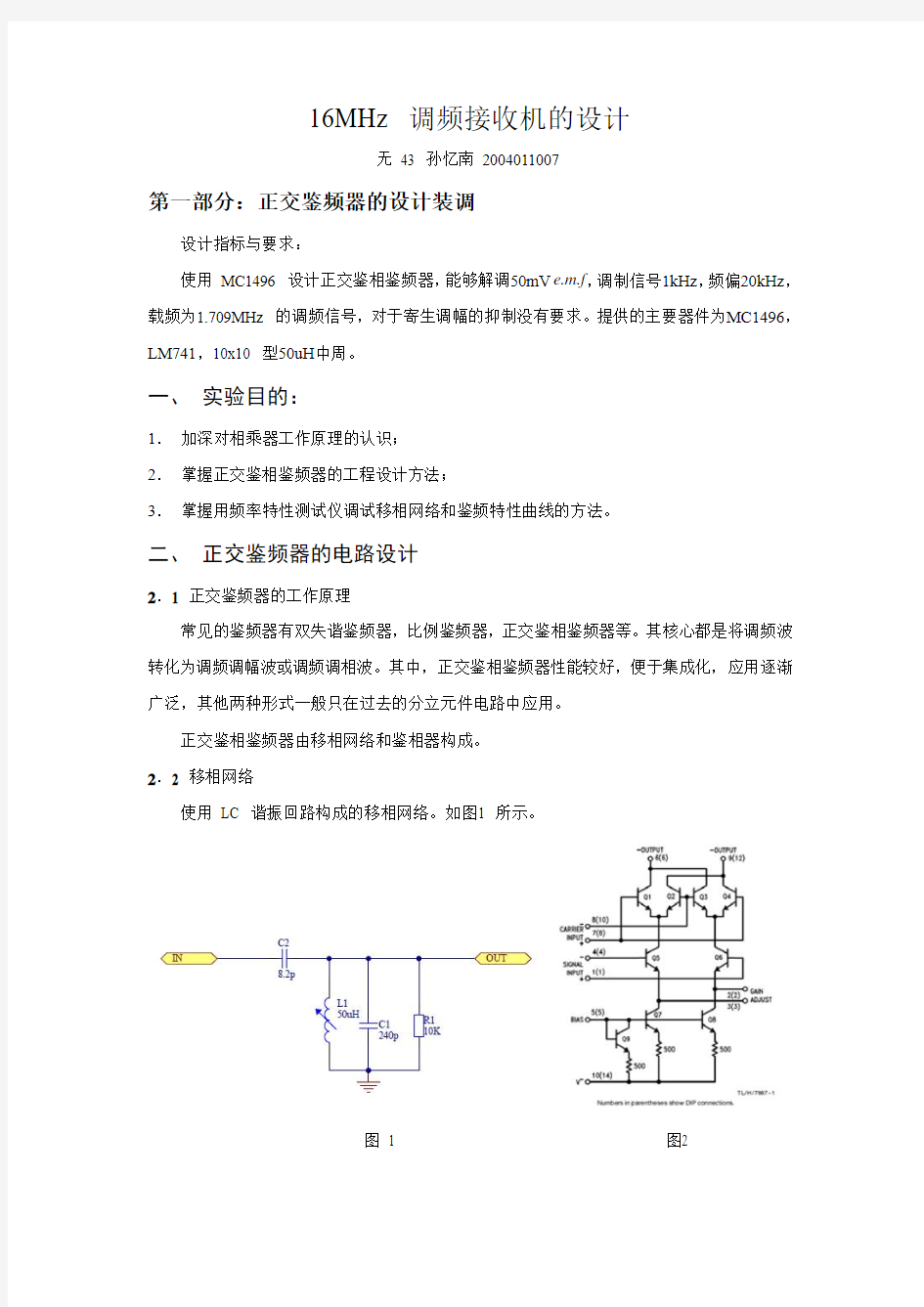

使用LC 谐振回路构成的移相网络。如图1 所示。

图1 图2

由电路分析,可以知道:≈)(jf H 常数,0022)(f f f Q f --≈

π?,)

(21210C C L f +=π完成了调频波到调频调相波的转换。 由 f 0 =1.704MHz ,L = 50μH ,计算得到C 1 ≈170 pF 。取C2=8.2pF 。

2.3 鉴相器

采用模拟相乘器构成。常用的模拟相乘器有LM1496。内部电路见图2。LM1496 内部没有偏置电路,需要外接,偏置电路见图3。Q9,Q8,Q7 构成镜像电流源,由5脚设置工作电流,一般为1mA 。外接电阻Ω=Ω--=k I V R S EE 8.65007

.08。1,4脚经小电阻接地,电位为0。

8,10脚接到R9,R14分压,电位为+6V 。输出端负载电阻取3.3K ,电位约为8.7V 。由此,可以判断各个晶体管均工作在放大区。2,3脚之间为增益调整电阻,取1K ,为中等的增益。

图3

2.4 移相网络和鉴相器的连接

对于 LM1496,1,4脚的输入阻抗较高,8,10脚的输入阻抗较低,因此将移相网络的输出接至1,4脚,这样对于移相网络的Q 值影响较小。由于乘法器的每个端均为双端平衡输入,因此将8脚,4脚交流接地,转为单端输入。1,4脚的输入利用了L1作为直流通路,避免了较小的偏置电阻R3的影响。

2.5 低放和电源

低放采用LM741接成差分放大器的形式,和LM1496 采用直流耦合,这样便于调试鉴相器的平衡。低放输入端采用简单的一阶RC 滤波,截止频率为

kHz p

k RC f c 104700*3.3*2121≈==ππ

低放的增益取为5倍,较低,以保证足够的动态范围。

电源采用7808三端稳压器,产生+8V 电压,供运放使用。该三端稳压器也可不用,使运放使用+12V,-8V 的不平衡的供电也是可以的。

三、电路调试与测试结果

3.1 调节W1,W2 使相乘器两输入端直流平衡。

3.2 调相移网络相移90度。

(1) 粗调:用扫频仪观察移相网络的谐振特性,调节L1使得谐振频率为中频频率。必要时,调整谐振电容C1的容量。实验中,加大C1至220pF。

(2) 细调:用信号发生器输入载频中心频率,细调L1,使运放输出电压为0,不经输出耦合电容。

3.3 测量鉴频器S 曲线

测试方法:(1) S 曲线图形:使用扫频仪测量。

(2) 零点频率,上下峰点频率、幅度:使用信号发生器和数字万用表点频法测量。

(3) 最大不失真频偏,使用信号发生器输出调频波,用示波器观察鉴频输出。

测量(2)(3)两项:信号发生器输出幅度为50mv e.m.f

3.3.1移相网络不并联电阻,R4 为无穷大。

零点频率:1.704MHz

上峰点频率,幅度:1.734MHz, 3.17V

下峰点频率,幅度:1.684MHz, -3.07V

最大不失真频偏:17kHz

鉴频灵敏度:158mV/kHz

3.3.2 移相网络并联10K 电阻,R4=10K。

零点频率:1.701MHz

上峰点频率,幅度:1.751MHz, 1.63V

下峰点频率,幅度:1.659MHz, -1.61V

最大不失真频偏:34kHz

鉴频灵敏度:38mV/kHz

3.3.3 为了满足设计要求:能无失真解调频偏20kHz信号。调整R4=18K。取得较好的效果。

零点频率:1.704MHz

上峰点频率,幅度:1.745MHz 2.07V

下峰点频率,幅度:1.663MHz, -2.05V

最大不失真频偏为25kHz

鉴频灵敏度:73mV/kHz

3.3.4调整移相网络参数,使得中频频率处的相移不为90 度。

对两种情况进行了实验:

(1) 减小C 20pF,使移相网络谐振频率偏移中频较大。不加回路阻尼电阻R4,测得零点频率1.784MHz;上峰点频率,幅度:1.809MHz, 3.31V;下峰点频率,幅度:1.761MHz, -3.12V。S 曲线在频率上发生偏移,形状基本不变。加入1.704MHz的调频信号,因为完全处在S 曲线的外侧,输出波形很小,且有失真。

(2) 微调L1,使谐振频率略有偏移。零点频率:1.710MHz,上峰点频率:1.739MHz,下峰点频率:1.690MHz。加入1.704MHz 的调频信号,并从零开始加大频偏,当频偏较小时,输出波形基本无失真,但是明显的叠加一个直流分量,这是因为载频已经偏离了S 曲线的对称中心。频偏加大后,由于单侧已经达到S曲线的峰顶,所以波形发生不对称的失真,最大不失真频偏为7.5KHz,明显减小。

3.3.5 解调信号输出

谐振回路并联18kHz调Q电阻。输入为解调50mV e.m.f,调制信号1kHz,频偏20kHz,载频为1.704MHz 的调频信号。输出波形如下图:

解调出的信号波形无失真,满足设计要求。

四、实验结论与体会

1.完成了正交鉴相鉴频器的设计,指标满足设计要求。

2.通过对相移网络不同参数的实验,可以知道:减小调Q电阻R4,可以降低相移网络的Q值,可以展宽解调S曲线的线性范围,可以无失真的解调更高频偏的信号,改善中心频率处的线性,同时会使鉴频灵敏度下降。调节谐振回路C1,L1,可以改变鉴频器的中心频率。

3.由于解调器位于最后一级,信号幅度大,同时由于在面包板上插接电路,所以更要特别注意电路的屏蔽与滤波。如果不注意的话,单独调试解调器不会出现问题,但是在联调的时候,就比较容易反馈到中放的输入端,产生自激。为此,采用如下的办法,所有的芯片的电源端,所有外接电源,乘法器的直流偏置都对地就近加滤波电容。所有带有高频信号的连线尽可能短,或以双绞线的形式传输信号。

第二部分:16MHz 调频接收机的整体设计和联调

组内分工情况:

高放: 林静 设计

混频和中放: 钱禹丞 设计

本机振荡器: 林延光 设计

正交鉴频器:

孙忆南 设计 组长: 孙忆南

一、设计任务和指标

设计一个由高频小信号放大器、本机振荡器、混频器、中频信号放大器和正交鉴相鉴频器构成的调频接收机。工作频率:16.455MHz ,灵敏度优于200uV(SNR=1),本振频率为14.7456MHz 。

二、整体设计

由于灵敏度要求为200uV ,鉴频器的最低解调电压为50mV ,这要鉴频前的总电压增益为dB V

mV 4825020050≈=μ。考虑到应留些设计余量,增益分配如下:高放20dB ,混频10dB ,中放25dB 。总和为55dB ,余量较大。

三、收发联调

1. 每级以1千欧电阻做负载,确保每一级工作正常。

2.连接各单元电路,检查各单元功能。

发现:本机振荡器停振,这是由于混频器,本振信号从射极输入,输入阻抗低,所需的本振功率较大,而本振采用单管振荡器,带负载能力不足,造成停振。这一情况,事先已经预料到,并且已经搭好一个射极跟随器组成的缓冲器,立即接入,问题解决。

中放自激,加强混频,中放,鉴频三级之间的去耦,同时,调节中放电路的布局,自激程度有减弱,但不能消除。于是在中放管的射极加入100欧的负反馈电阻,略降低该级的增益。自激消除。

3.整机联调

由于各级连接后,负载情况有变,同时,由于本振频率存在误差,造成中频频率和设计值有偏差,所以需要统一的对各级进行调谐。

(1) 将扫频仪的高频输出加在高放输入端,检波探头加在鉴频器前,外加16.455MHz频标,调节混频器、中放的输出回路,使之谐振在中频频率上,为了满足带宽要求,即获得更好的矩形系数,对两个回路采用较轻微的参差调谐。

(2) 去掉扫频仪的检波探头,直接加在鉴频器的输出,调节鉴频器的相移网络使得S 曲线的零点和16.455MHz的频标重合。

(3) 由于鉴频器的移相网络和中放的输出回路采用变压器和电容耦合,两个回路互相略有影响,所以重复(1)(2)一遍,使得S曲线上下对称,而且线性良好。

四、指标测试

整机灵敏度:60uV。

最大不失真频偏:大于25kHz。

临波道抑制:优于-30dB,偏离工作频率100KHz

镜像抑制:优于-25dB

可以接收到发射机发出的信号,波形清晰无失真,信噪比较好。

五、实验体会总结

1.合作完成了16MHz调频接收机的设计装调,性能指标满足设计要求,在实验中进一步体会接收机的系统概念,培养了团结协作的能力。

2.要注意各级之间的配合。如上文提到的联调时出现的本振停振,由于调试本振时采用1千欧电阻做负载,因此单独调试时不会出现问题。但是由于混频器的本振口输入阻抗低,因此联调时出现本振停振。这种情况是可以在系统整体设计时考虑到的,所以在整机联调前,

就设计了射极跟随器构成的缓冲级,解决了此问题。

3.如何保证电路的稳定工作。实验中,往往中频上更容易出现自激。这是因为,虽然高放工作频率高,但是只有一级,增益不大。而中频上,由于混频级,中放级,鉴频级对于中频都有增益,总增益估计在40dB左右,而且涉及的元件多,电路连线密集,而且有三个谐振回路,造成自激的可能性很大。对于一般的PCB版设计,一般采用大面积接地,各级直线排列。而对于面包板而言,大面积接地难以做到。所以在各级采用单点接地,输入输出信号使用单独的地线,地线不形成回路,所有的电源端,就近加滤波电容。所有带有高频信号的连线尽可能短,或以双绞线的形式传输信号。

哈工大FPGA设计与应用分频器设计实验报告

FPGA设计与应用 分频器设计实验报告 班级:1105103班 姓名:郭诚 学号:1110510304 日期:2014年10月11日

实验性质:验证性实验类型:必做开课单位:电信院学时:2学时 一、实验目的 1、了解Quartus II软件的功能; 2、掌握Quartus II的HDL输入方法; 3、掌握Quartus II编译、综合、适配和时序仿真; 4、掌握Quartus II管脚分配、数据流下载方法; 5、了解设计的资源消耗情况; 6、掌握分频器和计数器的实现原理; 7、掌握数码管的静态和动态显示原理 二、实验准备(1分) 2.1 EP2C8的系统资源概述 逻辑单元8,256 M4K RAM 块(4k比特+512校验比特) 36 总的RAM比特数165,888 嵌入式乘法器18 锁相环PLLs 2

2.2 工程所用到的FPGA引脚及功能说明 工程所用到的FPGA引脚及功能说明: PIN_23是时钟引脚; PIN_114 PIN_117 PIN_127 PIN_134是数码管的位选引脚; PIN_133 PIN_116 PIN_110 PIN_112 PIN_128 PIN_118 PIN_115是数码管段选信号引脚;实验所用的LED是共阴级连接 2.3 数码管的动态显示原理 动态显示是将所有数码管的8个显示笔划"a,b,c,d,e,f,g,dp"的同名端连在一起,另外为每个数码管的公共极COM增加位选通控制电路,位选通由各自独立的I/O 线控制,当输出字形码时,所有数码管都接收到相同的字形码,但究竟是那个数码管会显示出字形,取决于FPGA对位选通COM端电路的控制,所以只要将需要显示的数码管的选通控制打开,该位就显示出字形,没有选通的数码管就不会亮。通过分时轮流控制各个数码管的的COM端,就使各个数码管轮流受控显示,这就是动态驱动。在轮流显示过程中,每位数码管的点亮时间为1~2ms,由于人的视觉暂留现象及发光二极管的余辉效应,尽管实际上各位数码管并非同时点亮,但只要扫描的速度足够快,给人的印象就是一组稳定的显示数据,不会有闪烁感。

正交鉴频器实验报告

正交鉴相鉴频器 实验报告 一. 设计方案: 1. 实验原理: 先将调频波经过一个移相网络变换成调相调频波,然后再与原调频波一起加到一个相位检波器进行鉴频。 利用模拟乘法器的相乘原理可以实现乘积型相位检波: 输入信号 ()cos(sin )s sm c f v t V t m t ω=+Ω 移相后的信号为: ''' ()cos{sin [ ()]} 2 sin[sin ()] s sm c f sm c f v t V t m t V t m t π ω?ωω?ω=+Ω++=+Ω+ 得到的输出信号 '' 1()KV sin[2(sin )()] 2 1 V sin () 2 o sm sm c F sm sm v t V t m t K V ω?ω?ω=+Ω++ 其中第一项为高频分量,可以用滤波器滤掉,第二项是所需的频率分量。只要线性移相网络的相频特性()?ω在调频波的频率变化范围内是线性的,当 ()0.4rad ?ω≤时,sin ()()?ω?ω≈。因此,鉴频器的输出电压()o v t 的变化规 律与调频波瞬时频率的变化规律相同,从而实现了相位鉴频。 2. 各部分电路具体实现: 鉴相鉴频器主要由三部分组成:移相网络,模拟相乘器和低频放大器。具体电路实现如下: (1) 移相网络: v D (t)

用LC 谐振回路实现移相网络,使输入信号移相90°。谐振回路的谐振频率为中频频率2.455MHz 。 (2) 模拟相乘器 用MC1496构成相乘器,使输入的两路正交信号相乘。1,4管脚和8,10管脚间分别接有电位器R2和R5用来调节输入直流平衡。电源处C7,C8和L2构成 型滤波网络,R12和C9起级间去耦作用。 (3) 低频放大器: 用LM741运放来放大输入调制信号,同时运放还能起到低通滤波以及隔离的作用。通过调节相应的电阻值可以改变放大的倍数。在运放的两个输入端2脚和3脚加上两个隔直电容,可以滤去直流分量,以保证运放的工作点正确。R21和C15构成低通滤波器。 L2 R13R12

VHDL非整数分频器设计实验报告

非整数分频器设计 一、 输入文件 输入时钟CLK: IN STD_LOGIC 二、 设计思路 1. 方法一:分频比交错 (1) 确定K 值 先根据学号S N 确定M 和N :为了保证同学们的学号都不相同,取学号的后四位,即N S =1763 ()mod 1920(mod 17)0 17mod 17 S S S N N if N then M else M N =+=== 由以上公式,得N=(1763 mod 19)+20=35 M=(1763 mod 17)=12 然后根据下式计算分频比K 的值: 8()9N M M K N -+= = =8.34285714 (2) 确定交错规律 使在35分频的一个循环内,进行12次9分频和23次8分频,这样,输出F_OUT 平均为F_IN 的8.34285714分频。为使分频输出信号的占空比尽可能均匀,8分频和9分频应‘交替’进 (3) 设计框图:要求同步时序设计

(4)代码 在实体内定义两个进程(PROCESS P1和PROCESS P2),一个进程控制输出8/9分频,一个进程控制35分频周期比例输出。控制器输出FS_CTL信号控制输出是8分频还是9分频,分频器输出C_ENB信号来控制35分频计数器计数。 LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_UNSIGNED.ALL; USE IEEE.STD_LOGIC_ARITH.ALL; ENTITY DIV IS--定义实体,实体名DIV PORT(F_IN: IN STD_LOGIC;--输入时钟信号 F_OUT: OUT STD_LOGIC--输出时钟信号 ); END DIV; ARCHITECTURE A OF DIV IS SIGNAL CN1: INTEGER RANGE 0 TO 7;--8分频计数器 SIGNAL CN2: INTEGER RANGE 0 TO 8;--9分频计数器 SIGNAL CN: INTEGER RANGE 0 TO 34;--整体计数器 SIGNAL C_ENB: STD_LOGIC;--整体计数器时钟驱动信号 SIGNAL FS_CTL: STD_LOGIC;--控制8、9分频比例信号,高电平8分频,低电平9分频 BEGIN P1:PROCESS(F_IN)--8、9分频计数进程 BEGIN IF (F_IN'EVENT AND F_IN='1') THEN IF(FS_CTL='0') THEN--9分频 IF CN2=8 THEN--计数 CN2<=0; ELSE CN2<=CN2+1; END IF; IF CN2>4 THEN--控制输出,占空比0.5 F_OUT<='1'; ELSE F_OUT<='0'; END IF; IF CN2=8 THEN--控制整体计数器驱动信号 C_ENB<='1'; ELSE C_ENB<='0'; END IF; ELSE IF CN1=7 THEN--8分频计数,同上 CN1<=0; ELSE CN1<=CN1+1; END IF; IF CN1>3 THEN F_OUT<='1'; ELSE F_OUT<='0'; END IF; IF CN1=7 THEN C_ENB<='1'; ELSE C_ENB<='0'; END IF; END IF; END IF; END PROCESS P1; P2:PROCESS(C_ENB)--整体计数进程 BEGIN IF (C_ENB'EVENT AND C_ENB='1') THEN--由驱动信号驱动 IF CN=34 THEN--计数 CN<=0; ELSE CN<=CN+1; END IF; IF (CN=34 OR CN=2 OR CN=5 OR CN=8 OR CN=11 OR CN=14 OR CN=17 OR CN=20 OR CN=23 OR CN=26 OR CN=29 OR CN=32) THEN FS_CTL<='0'; ELSE FS_CTL<='1'; END IF;--8、9分频比例分配 ELSE CN<=CN; END IF; END PROCESS P2; END A;

正交鉴频电路课程设计

《高频电子线路》 课程设计报告 题目:正交鉴频电路的设计 专业:电子信息工程 班级:11电信一班 姓名:陈文董彬彬李丰朱越 梁富慧黄兴荣谷和伟 指导教师:冯锁 电气工程系 2013年12月12日

《高频电子线路》任务书

摘要 鉴频器使输出电压和输入信号频率相对应的电路。按用途可分为两类。第一类用于调频信号的解调。常见的有斜率鉴频器、相位鉴频器、比例鉴频器等,对这类电路的要求主要是非线性失真小,噪声门限低。第二类用于频率误差测量,如用在自动频率控制环路中产生误差信号的鉴频器。对这类电路的零点漂移限制较严,对非线性失真和噪声门限则要求不高。本设计使用LA1596为核心,设计正交鉴频器。 Multisim是美国国家仪器(NI)有限公司推出的以Windows为基础的仿真工具,适用于板级的模拟/数字电路板的设计工作。它包含了电路原理图的图形输入、电路硬件描述语言输入方式,具有丰富的仿真分析能力。工程师们可以使用Multisim交互式地搭建电路原理图,并对电路进行仿真。Multisim提炼了SPICE 仿真的复杂内容,这样工程师无需懂得深入的SPICE技术就可以很快地进行捕获、仿真和分析新的设计,这也使其更适合电子学教育。通过Multisim和虚拟仪器技术,PCB设计工程师和电子学教育工作者可以完成从理论到原理图捕获与仿真再到原型设计和测试这样一个完整的综合设计流程。 关键字:正交鉴频器;LM1596;解调;Multisim10

目录 第一章绪论............................................................................ 错误!未定义书签。第二章Multisim软件 . (6) 2.1 Multisim发展简介 (6) 2.2 Multisim 组成 (6) 2.3 仿真的内容 (7) 2.4 Multisim新特点 (7) 2.5 电路的构建及仿真 ............................................ 错误!未定义书签。第三章正交鉴频电路的设计. (9) 3.1鉴频器原理 (9) 3.2 正交鉴频器原理 (10) 3.3 鉴频特性 (11) 3.4正交鉴频器的工作原理图 (12) 3.5 设计原理数据分析 (13) 第四章仿真与调试 (15) 4.1仿真原理图 (15) 第五章总结 (18) 参考文献 (19)

分频器实验报告

分频器实验报告 分频器实验报告 start simulation直至出现 simulation as suessful,仿真结束。观察仿真结果。 时序仿真 图 : 六.实验过程所出现的问题及其解决 通过本次实验,初步掌握了语言的初步设计,收获颇多。但在实验过 程中也遇到了许多的问题,通过自己的独立思考和老师同学的相互讨 论对这个实验有了进一步的了解和认识。在最初建立工程的地方出现 了不少问题,因为没有详细阅读教材,导致无法成功建立工程运行程 序,最后认真熟读教材后,解决了问题。通过对错误的分析和解决, 让自己更好的掌握这一软件的基础操作,为下一次试验打下了见识的 基础。篇五: 八位十进制分频器实验报告 重庆交通大学信息科学与工程学院综合性实 验报告 姓名: 赵娅琳学号 10950214 班级:

通信工程专业201X级 2班 实验项目名称: 8位16进制频率及设计 实验项目性质: 设计性 实验所属课程: 数字设计基础 实验室 BEGIN IF CLKK'EVENT AND CLKK='1' THEN --1Hz时钟2分频 Div2CLK <= NOT Div2CLK; END IF; END PROCESS; PROCESS BEGIN IF CLKK='0' AND Div2CLK='0' THEN RST_CNT<='1'; --产生计数器清零信号 ELSE RST_CNT <='0'; END IF; END PROCESS; Load <= NOT Div2CLK; CNT_EN <= Div2CLK; END behav; 3、十进制计数模块

正交鉴频器设计实验报告(demo)

16MHz 调频接收机的设计 无43 孙忆南2004011007 第一部分:正交鉴频器的设计装调 设计指标与要求: 使用MC1496 设计正交鉴相鉴频器,能够解调50mV e.m.f,调制信号1kHz,频偏20kHz,载频为1.709MHz 的调频信号,对于寄生调幅的抑制没有要求。提供的主要器件为MC1496,LM741,10x10 型50uH中周。 一、实验目的: 1.加深对相乘器工作原理的认识; 2.掌握正交鉴相鉴频器的工程设计方法; 3.掌握用频率特性测试仪调试移相网络和鉴频特性曲线的方法。 二、正交鉴频器的电路设计 2.1 正交鉴频器的工作原理 常见的鉴频器有双失谐鉴频器,比例鉴频器,正交鉴相鉴频器等。其核心都是将调频波转化为调频调幅波或调频调相波。其中,正交鉴相鉴频器性能较好,便于集成化,应用逐渐广泛,其他两种形式一般只在过去的分立元件电路中应用。 正交鉴相鉴频器由移相网络和鉴相器构成。 2.2 移相网络 使用LC 谐振回路构成的移相网络。如图1 所示。 图1 图2

由电路分析,可以知道:≈)(jf H 常数,0022)(f f f Q f --≈ π?,) (21210C C L f +=π完成了调频波到调频调相波的转换。 由 f 0 =1.704MHz ,L = 50μH ,计算得到C 1 ≈170 pF 。取C2=8.2pF 。 2.3 鉴相器 采用模拟相乘器构成。常用的模拟相乘器有LM1496。内部电路见图2。LM1496 内部没有偏置电路,需要外接,偏置电路见图3。Q9,Q8,Q7 构成镜像电流源,由5脚设置工作电流,一般为1mA 。外接电阻Ω=Ω--=k I V R S EE 8.65007 .08。1,4脚经小电阻接地,电位为0。 8,10脚接到R9,R14分压,电位为+6V 。输出端负载电阻取3.3K ,电位约为8.7V 。由此,可以判断各个晶体管均工作在放大区。2,3脚之间为增益调整电阻,取1K ,为中等的增益。 图3 2.4 移相网络和鉴相器的连接 对于 LM1496,1,4脚的输入阻抗较高,8,10脚的输入阻抗较低,因此将移相网络的输出接至1,4脚,这样对于移相网络的Q 值影响较小。由于乘法器的每个端均为双端平衡输入,因此将8脚,4脚交流接地,转为单端输入。1,4脚的输入利用了L1作为直流通路,避免了较小的偏置电阻R3的影响。 2.5 低放和电源 低放采用LM741接成差分放大器的形式,和LM1496 采用直流耦合,这样便于调试鉴相器的平衡。低放输入端采用简单的一阶RC 滤波,截止频率为 kHz p k RC f c 104700*3.3*2121≈==ππ

EDA 实验2简单分频时序逻辑电路设计 实验报告

时序电路设计 实验目的: 1.掌握条件语句在简单时序模块设计中的使用。 2.学习在Verilog模块中应用计数器。 实验环境: Windows 7、MAX+PlusⅡ10等。 实验内容: 1.模为60的8421BCD码加法计数器的文本设计及仿真。 2.BCD码—七段数码管显示译码器的文本设计及仿真。 3.用For语句设计和仿真七人投票表决器。 4.1/20分频器的文本设计及仿真。 实验过程: 一、模为60的8421BCD码加法计数器的文本设计及仿真: (1)新建文本:选择菜单File下的New,出现如图5.1所示的对话框,在框中选中“Text Editor file”,按“OK”按钮,即选中了文本编辑方式。 图5.1 新建文本 (2)另存为V erilog编辑文件,命名为“count60.v”如图5.2所示。 (3)在编辑窗口中输入程序,如图5.3所示。

图5.2 另存为.V编辑文件图5.4 设置当前仿真的文本设计 图5.3 模为60的8421BCD码加法计数器的设计代码

(4)设置当前文本:在MAX+PLUS II中,在编译一个项目前,必须确定一个设计文件作为当前项目。按下列步骤确定项目名:在File菜单中选择Project 中的Name选项,将出现Project Name 对话框:在Files 框内,选择当前的设计文件。选择“OK”。如图5.4所示。 (5)打开编译器窗口:在MAX—plusⅡ菜单内选择Compiler 项,即出现如图5.5的编译器窗口。 图5.5 编译器窗口 选择Start即可开始编译,MAX+PLUS II编译器将检查项目是否有错,并对项目进行逻辑综合,然后配置到一个Altera 器件中,同时将产生报告文件、编程文件和用于时间仿真用的输出文件。 (6)建立波形编辑文件:选择菜单File下的New选项,在出现的New对话框中选择“Waveform Editor File”,单击OK后将出现波形编辑器子窗口。 (7)仿真节点插入:选择菜单Node下的Enter Nodes from SNF选项,出现如图5.6所示的选择信号结点对话框。按右上侧的“List”按钮,在左边的列表框选择需要的信号结点,然后按中间的“=>”按钮,单击“OK”,选中的信号将出现在波形编辑器中。 图5.6 仿真节点插入

高频电子线路课程设计.

目录 一设计总体思路及比较 (2) 二单元电路思路 (6) 输入回路 (6) 本机荡回路 (8) 中频滤波器匹配参数 (10) 限频电路 (12) 鉴频电路 (13) 低频放大电路 (14) 三总结体会 (15) 四总原理图 (16) 参考资料 (17)

第一章设计总体思路及方案比较 一.调频收音机的主要指标 调频接收机的主要指标有: 1工作频率范围 接收系统可以接受到的无线电波的频率范围称为接收机的工作频率范围。接受系统的工作频率必须与发射机的工作频率工作频率相对应。调频接收机的频率范围为88~108MH,是因为调频广播收音机的工作范围也为88~108MH。 2 灵敏度 接收系统接受微弱信号的能力称为灵敏度。一般用输入信号电压的大小来表示。接收的输入信号越小,灵敏度越高。调频接收机的灵敏度一般为5~30uv。 3选择性 接收系统从各种信号和干扰信号中选出所需信号,抑制不需要的信号的能力称为选择性,单位用dB表示,dB数越高,选择性越好。调频接收机的中频干扰应大于50dB。 4 频率特性 接收系统的频率响应范围称为频率特性或通频带。 5 输出功率 负载输出的最大不失真功率称为输出功率。

二调频接收机的系统方框图 调频接收机的系统方框图如所示,它是由输入回路,高频放大器,混频器,本机振荡,中频放大器,鉴频器,低频放大器等电路组成。其工作原理是:天线接受到的高频信号,经输入调谐回路选频为f1,再经高频放大器放大进入混频级。本机振荡器输出的另一高频f2也进入混频级,则混频级的输出为含有f1、f2、(f1+f2)、(f2-f1)等频率分量的信号。混频级的输出接调频回路选出中频信号(f2-f1),再经中频放大器放大,获得足够高增益,然后鉴频器解调出低频调制信号,由低频功放级放大。 三MC3362芯片特点 MC3362是低功耗窄带双变频超外差式调频接收机系统集成电路,它的片内包含两个本征,两个混频器,两个中放和正交鉴频等功能电路。MC3362的接收频率可达450MHz,采用内部本征时,也可

八位十进制分频器实验报告

重庆交通大学 信息科学与工程学院 综合性实验报告 姓 名: 赵娅琳 学 号 10950214 班 级: 通信工程专业2010级 2班 实验项目名称: 8位16进制频率及设计 实验项目性质: 设计性 实验所属课程: 数字设计基础 实验室(中心): 现代电子实验中心 指 导 教 师 : 李 艾 星 实验完成时间: 2012 年 6 月 18 日

教师评阅意见: 签名:年月日 实验成绩: 一、课题任务与要求 1、验证8位16进制频率计的程序; 2、根据8位16进制频率计的程序设计8位10进制频率计; 二、设计系统的概述 频率计的基本原理是用一个频率稳定度高的频率源作为基准时钟,对比测量其他信号的频率,通常情况下计算每秒内待测的脉冲个数,此时闸门时间为1秒,闸门时间也可以大于或小于1秒。频率信号易于传输,抗干扰性强,可以获得较好的测量精度。 数字频率计的关键组成部分包括一个测频控制信号发生器、一个计数器和一个锁存器,另外包括脉冲发生器、姨妈驱动电路和显示电路。 工作过程:系统正常工作时,脉冲信号发生器输入1HZ的标准信号,经过测频控制信号发生器的处理,2分频后即可产生一个脉宽为1秒的时钟信号,以此作为计数闸门信号。测量信号时,将被测信号通过计数器作为时钟。当技术闸门信号高平有效时,计数器开始计数,并将计数结果送入锁存器中。设置锁存器的好处是现实的数据稳定,不会由于周期的清零信号而不断闪烁。最后将所存的数值由外部的译码器并在数码管上显示。 三、单元电路的设计与分析(重点描述自己设计部分) 1、八位十进制计数顶层模块设计 (1)、此模块是元件例化语句将各个元件(测频控制模块、十进制计数模块、测频锁存器模块)连接形成一个整体,完成最终频率计所期望的功能。

数控分频器实验报告

《数控分频实验》 姓名:谭国榕班级:12电子卓越班学号:201241301132 一、实验目的 1.熟练编程VHDL语言程序。 2.设计一个数控分频器。 二、实验原理 本次实验我是采用书上的5分频电路进行修改,通过观察其5分频的规律进而修改成任意奇数分频,再在任意奇数分频的基础上修改为任意偶数分频,本次实验我分为了三个部分,前两部分就是前面所说的任意奇数分频和任意偶数分频,在这个基础上,再用奇数输入的最低位为1,偶数最低位为0的原理实现合并。 三、实验步骤 1.任意奇数分频 程序: LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_UNSIGNED.ALL; USE IEEE.STD_LOGIC_ARITH.ALL; ENTITY DIV1 IS PORT(CLK:IN STD_LOGIC; D:IN INTEGER RANGE 0 TO 255; K1,K2,K_OR:OUT STD_LOGIC ); END; ARCHITECTURE BHV OF DIV1 IS SIGNAL TEMP3,TEMP4:STD_LOGIC_VECTOR(7 DOWNTO 0); SIGNAL M1,M2:STD_LOGIC; --SIGNAL OUT1,OUT2,OUT3:STD_LOGIC; BEGIN PROCESS(CLK,TEMP3) BEGIN IF RISING_EDGE(CLK) THEN IF(TEMP3=D-1) THEN TEMP3<="00000000"; ELSE TEMP3<=TEMP3+1; END IF; IF(TEMP3=D-(D+3)/2) THEN M1<=NOT M1; ELSIF (TEMP3=D-2) THEN M1<=NOT M1; END IF; END IF; END PROCESS; PROCESS(CLK,TEMP4) BEGIN IF FALLING_EDGE(CLK) THEN IF(TEMP4=D-1) THEN TEMP4<="00000000"; ELSE TEMP4<=TEMP4+1; END IF; IF(TEMP4=D-(D+3)/2) THEN M2<=NOT M2; ELSIF (TEMP4=D-2) THEN M2<=NOT M2;

高频课程设计--调频接收机

一、设计方案及电路基本原理 1.设计目的 (1)了解调频接收机的工作原理及组成。 (2)按照给定的技术指标成对调频接收机的设计。 (2)掌握调频接收机的仿真方法。 2.设计思想及工作原理 电路的开始部分是由高频放大电路和本振信号混频,输出一个中频信号。因为这是超外差调频接收机,所以混频电路和调幅接收机有着明显的不同,在调频电路中,本振电路是独立的。在放大电路部分,采用场效应管共源极放大电路。本振电路才用LC 振荡电路,两个信号分别输入混频器,得到一个中频信号。为了得到高的增益,而整个电路的增益取决于中放,同时也抑制了邻近干扰。在中频放大电路的输出端,接一个限幅器,其目的是如果直接接鉴频器,很可能得到很多不需要的波形,用滤波器很难滤除,所以在鉴频器的输入端加一级限幅器,去除不需要的波,使输出更为纯净。鉴频器是将原调制信号解调出来,在本次设计中采用比例鉴频器。为了能够得到我们所需要的效果,在电路的最后采用低频放大电路。调频接收机的原理框图如图1所示。 图1 调频接收机原理框图 二、设计方案 1.单元电路设计 (1) 高频功率放大电路 输入回路 高频放大 混频 中频放大 鉴频 低频功放 本机震荡 控制器

如图2所示为共射级接法的晶体管高频小信号放大器。他不仅要放大高频信号,而且还要有一定的选频作用,因此晶体管的负载为LC 并联谐振回路。在高频情况下,晶体管本身的极间电容及连接导线的分布参数等会影响的频率和相位。晶体管的静态工作点由电阻2RA ,3RA , 4RA 及6RA 决定,其计算方法与低频单管放大器相同。 其工作原理为:从天线1ANTA 接收到的高频信号经过1CA 、1CCA 、1LA 组成的选频回路,选取信号为10.7s f MHz =的有用信号,经晶体管21/d B f f f QL =-=进行放大,由3CA 、1TA 初级组成的调谐回路,进一步滤除无用信号,将有用信号经变压器和1CB 耦合进入3361MC 。 ANTA1 KA1 RA11K +VCC RA25.1K RA318K RA410K RA61.5K RA51K LA122uh LEDA1 CA50.1uF CA3120p CA133p CA40.01u F CA2103 CCA1 R 50K QA13DG12C TA1 JB1 TTA2 TTA1 JA1 图2 高频功率放大电路原理图 (2)混频器及本机震荡 混频器的作用是将高频调制信号变换为中频调制信号,所改变的只是被调信号的载频,而信号的调制规律是不能改变的。混频器有不同类型,混频增益约为-10Db~30dB 左右。混频器的输出应和中放输入级匹配,混频电路可以采用如图3的二极管混频电路。 对本机振荡器的要求是:频率可调,并和输入回路及高放负载回路同步调整(统

实验一 QUARTUS II入门和分频器设计

实验报告 课程名称EDA技术与VHDL设计 实验项目Quartus II入门 实验仪器计算机、Quartus II 系别信息与通信工程学院 专业电子信息工程 班级/学号电信1201 / 2012010970 学生姓名张宗男 实验日期 成绩 指导教师

实验一 QUARTUS II入门和分频器设计 一、实验目的 1.掌握QUARTUS II工具的基本使用方法; 2.掌握FPGA基本开发流程和DE2开发板的使用方法; 3.学习分频器设计方法。 二、实验内容 1.运用QUARTUS II 开发工具编写简单LED和数码管控制电路并下载到DE2 实验开发板。2.在QUARTUS II 软件中用VHDL语言实现十分频的元器件编译,并用电路进行验证,画出仿真波形。 三、实验环境 1.软件工具:QUARTUS II 软件;开发语言:VHDL; 2.硬件平台:DE2实验开发板。 四、实验过程 1.设计思路 (1)、 18个开关控制18个LED灯,通过低位四个开关的‘1’‘0’控制LED灯上7段灯的显示(2)、 实现10分频IF(count="1001") THEN count<="0000"; clk_temp<=NOT clk_temp; 达到9的时候,把“0000”给到cout,然后clk_temp 信号翻转,从而实现10分频。 2.VHDL源程序 (1)、 LIBRARY ieee; USE ieee.std_logic_1164.all; ENTITY e_zhangzongnan IS PORT(SW :IN STD_LOGIC_VECTOR(0 TO 17); HEX0 :OUT STD_LOGIC_VECTOR(0 TO 6);

调频接收机课程设计(改)

《高频电子线路》课程设计说明书 调频接收机设计 院部:电气与信息工程学院 学生姓名:谢曾闻达、刘泽仁、姚一鸣 指导教师:刘海波 专业:通信工程 班级:通信1102班 学号: 完成时间:2013年12月

摘要 信息传递是人类社会生活的重要内容,没有通信,人类社会是不可想象的,从古到今的烽火到近代的旗语,都是人们寻找快速远距离的通信手段。 今年来,电子工业发展非常惊人,当然这些进步都成了人类生活不可缺少的东西,1937年莫尔斯发明的有线电报开创了利用电传递信息的新时代,1876年贝尔发明的电话已经成为我们日常生活中通信的重要工具,1918年,调幅无线广播、超外差接收机问世,1936年,商业电视广播开播··伴随着人类的文明、社会的进步和科学技术的发展,电信技术也是一日千里的速度飞速发展。然而无线通信在现在的生活中更是重要,小到我们常用的手机和各种电器的遥控器等,大到航天科技都离不开发射和接收设备。 本次设计中,其目的是得到一个调频接收机。在接收机的设计过程中,应将其分为选频网络、高频放大、变频、解调、低放和低频功放六个部分。整个电路的设计必须注意几个方面,选择性好的级,应尽可能靠近前面,因为在干扰都不大的地方把干扰抑制下去,效果最好。如干扰信号很大,则由于三极管的非线性,将产生严重的组合频率及其他非线性失真,这时滤除杂波比较困难。因此,在高级接收机中,输入电路常采用复杂的高级选择电路。为了使混频和本振分别调在最佳状态,采用单独的本振。总得来说,设计一部接收机时必须全面考虑,妥善处理一些相互牵制的矛盾,特别要抓住主要矛盾(稳定性、选择性、失真等),才能使得接收机有较好的指标。

EDA分频器实验教案

实验三:整数分频器的设计 一实验目的 了解利用类属设计可配置的重用设计技术。 二实验原理 利用类属n 可以改变分频器的分频系数,输出q的频率是输入信号clk频率的1/n。通过给n赋不同的值,就可以得到需要的频率。 三实验器材 EDA实验箱 四实验内容 1.参考教材第5章中5.3.1,完成整数分频器的设计。 2.修改5. 3.1中的分频系数n,观察仿真波形和实验箱输入/输出信号的变化。 3.在试验系统上硬件验证分频器的功能。 在实验三中,建议将实验箱的实验电路结构模式设定为模式7。输入信号clk由键7的输出来模拟,输入信号reset_n由键8模拟,输出信号q接至LED:D14。当然,也可以由实验者设定到其它功能相似的键或者LED。

代码:(参考教材第5章中5.3.1) library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; entity div is generic(n:integer:=8); port(clk,reset_n:in std_logic; q: out std_logic); end div; architecture behavl_div of div is signal count:integer range n-1 downto 0; begin process(reset_n,clk) begin if reset_n='0' then q<='0'; count<=n-1; elsif(clk'event and clk='1' and clk'last_value='0')then count<=count-1; if count>=(n/2)then q<='0'; else q<='1'; end if; if count<=0 then count<=n-1; end if; end if; end process; end behavl_div; 五实验注意事项 1.编写代码时一定要书写规范 2模式的选择和引脚的配置一定要合理 六实验报告 简述实验过程,将实验项目分析设计,仿真和测试写入实验报告。

实验12 斜率鉴频与相位鉴频器

实验12 斜率鉴频与相位鉴频器 —、实验准备 1.做本实验时应具备的知识点: FM波的解调 斜率鉴频与相位鉴频器 2.做本实验时所用到的仪器: 变容二极管调频模块 斜率鉴频与相位鉴频器模块 双踪示波器 万用表 二、实验目的 1.了解调频波产生和解调的全过程以及整机调试方法,建立起调频系统的初步概念; 2.了解斜率鉴频与相位鉴频器的工作原理; 3.熟悉初、次级回路电容、耦合电容对于电容耦合回路相位鉴频器工作的影响。 三、实验内容 1.调频-鉴频过程观察:用示波器观测调频器输入、输出波形,鉴频器输入、输出波形; 2.观察初级回路电容、次级回路电容、耦合电容变化对FM波解调的影响。 四、基本原理 从FM信号中恢复出原基带调制信号的技术称为FM波的解调,也称为频率检波技术,简称鉴频。鉴频器的解调输出电压幅度应与输入FM波的瞬时频率成正比,因此鉴频器实际上是一个频率—电压幅度转换电路。实现鉴频的方法有很多种,本实验介绍斜率鉴频和电容耦合回路相位鉴

频。 1.斜率鉴频电路 斜率鉴频技术是先将FM波通过线性频率振幅转换网络,使输出FM波的振幅按照瞬时频率的规律变化,而后通过包络检波器检出反映振幅变化的解调信号。实践中频率振幅转换网络常常采用LC并联谐振回路,为了获得线性的频率幅度转换特性,总是使输入FM波的载频处在LC并联回路幅频特性曲线斜坡的近似直线段中点,即处于回路失谐曲线中点。这样,单失谐回路就可以将输入的等幅FM波转变为幅度反映瞬时频率变化的FM波,而后通过二极管包络检波器进行包络检波,解调出原调制信号以完成鉴频功能。 图12-1为斜率鉴频与相位鉴频实验电路,图中13K02开关打 向“3”时为斜率鉴频。13Q01用来对FM波进行放大,13C2、13L02为频率振幅转换网络,其中心频率为9MHZ左右。13D03为包络检波二极管。13TP01、13TP02为输入、输出测量点。 2.相位鉴频器 本实验采用平衡叠加型电容耦合回路相位鉴频器,实验电路如图12-1所示,开关13K02拨向“1”时为相位鉴频。 相位鉴频器由频相转换电路和鉴相器两部分组成。输入的调频信号加到放大器13Q01的基极上。放大管的负载是频相转换电路,该电路是通过电容13C3耦合的双调谐回路。初级和次级都调谐在中心频率上。初级回路电压直接加到次级回路中的串联电容13C04、13C05的中心点上,作为鉴相器的参考电压;同时,又经电容13C3耦合到次级回路,作为鉴相器的输入电压,即加在13L02两端用表示。鉴相器采用两个并联二极管检波电路。检波后的低频信号经RC滤波器输出。

分频器的设计

分频器的设计 一、课程设计目的 1.学会使用电路设计与仿真软件工具Hspice,熟练地用网表文件来描述模拟电路,并熟悉应用Hspice内部元件库。通过该实验,掌握Hspice的设计方法,加深对课程知识的感性认识,增强电路设计与综合分析能力。 2.分频器大多选用市售成品,但市场上出售的分频器良莠不齐,质量上乘者多在百元以上,非普通用户所能接受。价格在几十元以下的分频器质量难以保证,实际使用表现平庸。自制分频器可以较少的投入换取较大的收获。 二.内容 分频器-概述 分频器是指使输出信号频率为输入信号频率整数分之一的电子电路。在许多电子设备中如电子钟、频率合成器等,需要各种不同频率的信号协同工作,常用的方法是以稳定度高的晶体振荡器为主振源,通过变换得到所需要的各种频率成分,分频器是一种主要变换手段。早期的分频器多为正弦分频器,随着数字集成电路的发展,脉冲分频器(又称数字分频器)逐渐取代了正弦分频器,即使在输入输出信号均为正弦波时也往往采用模数转换-数字分频-数模转换的方法来实现分频。正弦分频器除在输入信噪比低和频率极高的场合已很少使用。

分频器-作用 分频器是音箱中的“大脑”,对音质的好坏至关重要。功放输出的音乐讯号必须经过分频器中的各滤波元件处理,让各单元特定频率的讯号通过。要科学、合理、严谨地设计好音箱之分频器,才能有效地修饰喇叭单元的不同特性,优化组合,使得各单元扬长避短,淋漓尽致地发挥出各自应有的潜能,使各频段的频响变得平滑、声像相位准确,才能使高、中、低音播放出来的音乐层次分明、合拍,明朗、舒适、宽广、自然的音质效果。 在一个扬声器系统里,人们把箱体、分频电路、扬声器单元称为扬声器系统的三大件,而分频电路对扬声器系统能否高质量地还原电声信号起着极其重要的作用。尤其在中、高频部分,分频电路所起到的作用就更为明显。其作用如下: 合理地分割各单元的工作频段; 合理地进行各单元功率分配; 使各单元之间具有恰当的相位关系以减少各单元在工作中出现的声干涉失真; 利用分频电路的特性以弥补单元在某频段里的声缺陷; 将各频段圆滑平顺地对接起来。 分频器-分类 1)功率分频器:位于功率放大器之后,设置在音箱内,通过LC滤波网络,将功率放大器输出的功率音频信号分为低音,中音和高音,分别送至各自扬声器。连接简单,使用方便,但消耗功率,出现音频谷

高频课程报告--鉴频电路设计分解

课程设计任务书 学生姓名:专业班级:电子0802 指导教师:钟毅工作单位:信息工程学院 题目:鉴频电路设计 初始条件: 具较扎实的电子电路的理论知识及较强的实践能力;对电路器件的选型及电 路形式的选择有一定的了解;具备高频电子电路的基本设计能力及基本调试能 力;能够正确使用实验仪器进行电路的调试与检测。 要求完成的主要任务: 1. 采用二极管完成一个鉴频器的设计。 2. 设计FM-FM.AM变换电路并进行调试, 3. 输入调频波,观测鉴频器的输入、输出波形, 4. 完成课程设计报告(应包含电路图,清单、调试及设计总结)。 时间安排: 1.2011年6月3日分班集中,布置课程设计任务、选题;讲解课设具体实 施计划与课程设计报告格式的要求;课设答疑事项。 2.2011年6月4日至2011年6月9日完成资料查阅、设计、制作与调试; 完成课程设计报告撰写。 3. 2011年6月10日提交课程设计报告,进行课程设计验收和答辩。 指导教师签名:年月日 系主任(或责任教师)签名:年月日

目录 摘要 ............................................................... I Abstract .......................................................... I I 绪论 (1) 1频率解调原理分析 (2) 1.1理论分析 (2) 1.2变换电路分析 (3) 1.3包络检波 (3) 2电路设计 (4) 2.1变换电路设计 (4) 2.2检波器的设计 (4) 2.3检波器的失真 (5) 2.3.1惰性失真 (5) 2.3.1底部切削失真 (6) 3 FM-AM变换电路设计 (7) 3.1 整体电路设计 (7) 3.2载波产生电路设计 (7) 3.3 乘法器设计 (9) 3.4 电压跟随器设计 (10) 4电路实现与测试 (11) 4.1 实物制作 (11) 4.2 电路测试 (13) 4.2.1 FM—AM波形测量 (13) 4.2.2鉴频波形测量 (14) 4.2.3鉴频特性曲线 (15) 5 总结 (16) 参考文献 (17) 附录1总体电路图 (18) 附录2 PCB制版图 (19) 附录3 元件清单 (20)

实验报告1 简单分频器

课程名称:FPGA指导老师:_竺老师_______成绩:__________________ 实验名称:简单分频器的设计实验类型:_______同组学生姓名:__俞杰草______ 一、实验目的和要求(必填)二、实验内容和原理(必填) 三、主要仪器设备(必填)四、操作方法和实验步骤 五、实验数据记录和处理六、实验结果与分析(必填) 七、讨论、心得 一.实验目的 a)熟悉Xilinx ISE软件,学会设计,仿真,综合和下载。 b)熟悉实验板电路设定频率的方法。 二.实验内容 根据实验板上晶振的输入频率50MHz,如果直接用这么高的时钟频率来驱动LED的闪烁,人眼将无法分辨。因此本实验着重介绍如何通过分频计数器的方式将50MHz的输入频率降低为人眼可分辨的频率(10Hz以下),并在实验板的LED2~LED5上显示出来。 三.实验记录 【实验现象】 当将rst_n信号对应的开关拨下,led0熄灭,其他所有led亮。 当将rst_n信号对应的开关往上拨,有7盏led亮,1盏led灭,且灭的led从led0向led7,再跳回led0不断循环往复的移动。 【主要程序段分析】 reg[22:0]cnt; always@(posedge clk) if(rst_n)cnt<=23'd0; else cnt<=cnt+1'b1;//带复位键的位宽为24位的分频计数器,以降低闪烁频率reg[7:0]led; always@(posedge clk) if(rst_n) led<=8'b00000001;//按键复位 else if((cnt==23'h7fffff)&&(led==8'b10000000)) led<=8'b00000001;//循环一周后从D5开始下一周的循环 else if(cnt==23'h7fffff) led<=led<<1;//左移一位,右端补零 assign led_d2=~led[2]; assign led_d4=~led[4];

(相位鉴频器)电子测量实验指导书(科)

Xb08610209 陆斌 08电子信息(2)班 相位鉴频器 一、实验目的 1、熟悉相位鉴频电路的基本原理。 2、了解鉴频特性曲线(S 曲线)的正确调整方法。 3、将变容二极管调频器与相位鉴频器两实验板进行联机调试,进一步了解调频和解调全过程及整机调试方法。 二、实验原理 相位鉴频器是模拟调频信号解调的一种最基本的解调电路,它具有鉴频灵敏度高,解调线性好等优点。 1、鉴频概述 调频波的解调称为频率解调,简称鉴频;调相波的解调称为相位检波,简称 鉴相。它们的作用都是从已调波中检出反映在频率或相位变化上的调制信号。但是采用的方法不尽相同。由于在调频接收机中,当等幅调频信号通过鉴频前各级电路时,因电路频率特性不均匀而导致调频信号频谱结构的变化,从而造成调频信号的振幅发生变化。如果存在着干扰,还会进一步加剧这种振幅的变化。鉴频器解调这种信号时,上述寄生调幅就会反映在输出解调电压上,产生解调失真。因此,一般必须在鉴频前加一限幅器以消除寄生调幅,保证加到鉴频器上的调频电压是等幅的。限幅与鉴频一般是连用的,统称为限幅鉴频器。 鉴频器输出电压u 0随输入频率f (或频偏 )变化的特性称为鉴 频特性。在线性解调的理想情况下,鉴频特性为一直线,实际上会弯曲,呈“S”型,称为“S”曲线。 2、鉴频器指标 1)鉴频跨导(效率、灵敏度)S D :鉴频特性在f c 处的斜率,用它来评价鉴频能力。 单位为V/Hz 。S D 越大,表明鉴频器将输入瞬时频偏变换为输出解调电压的能力越强。 c f f f -=?

一般情况下,S D 为调制角频率的复值函数,即()D S j Ω,要求它的通频带大于调制信号的最高频率 m ax Ω 2)峰值带宽max B :鉴频器输出电压两峰值点所对应的频率差,即 max 21B f f =-,它近似表明鉴频器鉴频线性区的宽度。为了减小鉴频器的非线性 失真,要求鉴频特性近似线性的范围 m ax 2f ?大于2m f ?。 ③ 最大输出电压0m ax U :鉴频器输出的最大电压。 ④ 线性度要好与失真要小。 3.电容耦合双调谐回路相位鉴频器: 相位鉴频器的组成方框图如3-3示。图中的线性移相网络就是频—相变换网络,它将输入调频信号u1 的瞬时频率变化转换 为相位变化的信号u2,然后与原输入的调频信号一起加到相位检波器,检出反映频率变化的相位变化,从而实现了鉴频的目的。 图3-4的耦合回路相位鉴频器是常用的一种鉴频器。这种鉴频器的相位检波器部分是由两个包络检波器组成,线性移相网络采用耦合回路。为了扩大线性鉴频的范围,这种相位鉴频器通常都接成平衡和差动输出。 图3-4 耦合回路相位鉴频器 图3-5(a )是电容耦合的双调谐回路相位鉴频器的电路原理图,它是由调 o